Изобретение относится к технологии производства полупроводниковых схем, в частности к изготовлению интегральных схем с диэлектрической изоляцией транзисторных структур.

Известен способ изготовления полупроводниковых интегральных схем с диэлектрической изоляцией элементов. На монокристаллической кремниевой пластине образуется высоколегированный слой этого же типа проводимости, что и пластина, травятся разделительные канавки, на поверхность пластины с канавками наносится диэлектрический слой (изоляция), наращивается поликристаллическая кремниевая подложка, методом прецизионной шлифовки и полировки вскрываются монокристаллические кремниевые карманы. В карманах формируются транзисторные структуры.

Недостатком таких структур является высокое сопротивление коллекторной области из-за наличия между скрытыми высоколегированными контактами низколегированного материала, что приводит к большим напряжениям насыщения транзисторов и не позволяет использовать их в сильноточных мощных интегральных схемах.

Для снижения сопротивления коллекторной области формирование высоколегированных слоев того же типа проводимости, что и пластина, проводится после травления разделительных канавок. Это обеспечивает выход высоколегированных скрытых слоев к рабочей поверхности подложки по всему периметру в каждом кармане [2] . Однако при этом значительно возрастает площадь карманов.

Наиболее близким техническим решением является способ изготовления кремниевых транзисторных структур с диэлектрической изоляцией, включающий образование на исходной монокристаллической пластине высоколегированных скрытых слоев того же типа проводимости, что и пластина, травление разделительных канавок, нанесение на них диэлектрического слоя, наращивание на него поликристаллической кремниевой подложки, вскрытие монокристаллических карманов, формирование в монокристаллических кремниевых карманах транзисторных структур.

Выход высоколегированного скрытого слоя к рабочей поверхности в этом способе осуществляется путем проведения глубокой локальной диффузии примеси, создающей тот же тип проводимости, что и примесь скрытого слоя, через окна в маскирующем слое монокристаллических карманов.

Однако этот способ требует проведения дополнительной длительной высокотемпературной обработки подложки с монокристаллическими карманами, что увеличивает общую длительность высокотемпературных обработок и приводит к повышенной деформации подложки из-за большой разницы коэффициентов расширения материалов, из которых сформирована подложка с монокристаллическими кремниевыми карманами. Это снижает процент выхода годных в результате искажения геометрии элементов при фотолитографии на деформированной подложке или в результате боя при механическом воздействии во время фотолитографии.

Целью изобретения является увеличение процента выхода годных структур и упрощение технологии при изготовлении кремниевых транзисторных структур с диэлектрической изоляцией.

Цель достигается тем, что в способе изготовления кремниевых транзисторных структур с диэлектрической изоляцией, включающем образование на исходной монокристаллической пластине высоколегированных скрытых слоев того же типа проводимости, что и пластина, травление разделительных канавок, нанесение на них диэлектрического слоя, наращивание на него поликристаллической кремниевой подложки, вскрытие монокристаллических карманов, формирование в монокристаллических кремниевых карманах транзисторных структур, до образования высоколегированных скрытых слоев формируют на исходной монокристаллической пластине локальные высоколегированные области того же типа проводимости, что и скрытый слой, и через них выводят скрытые слои к рабочей поверхности монокристаллических карманов одновременно с проведением операций по формированию транзисторных структур.

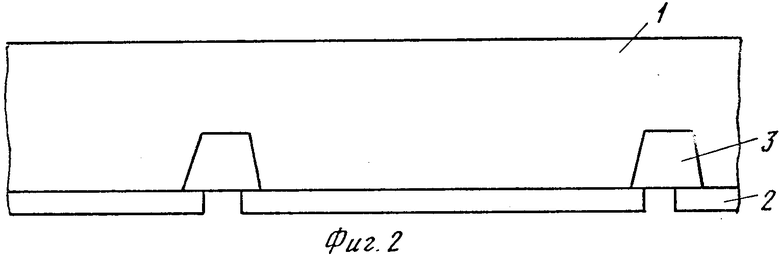

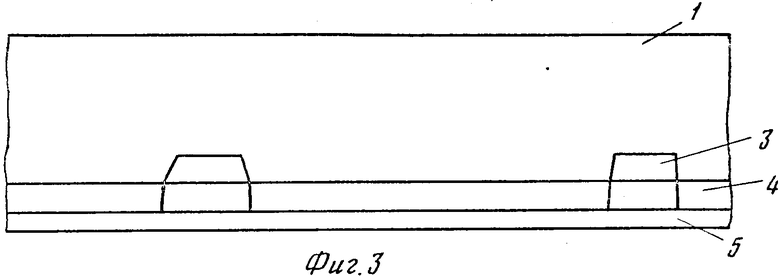

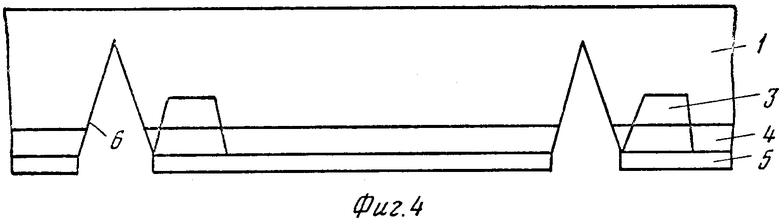

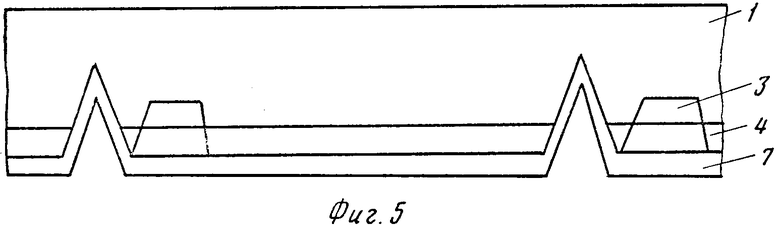

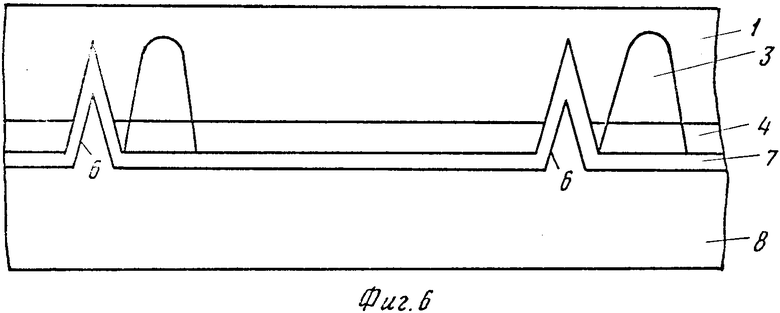

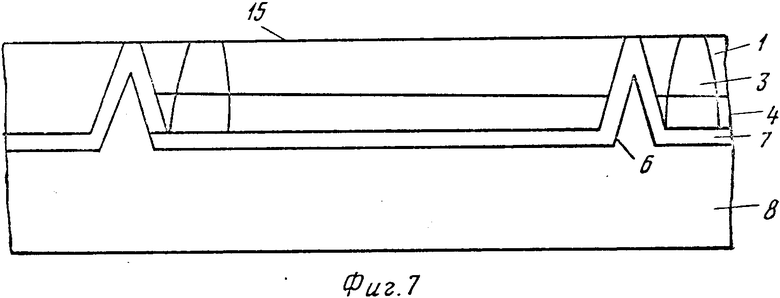

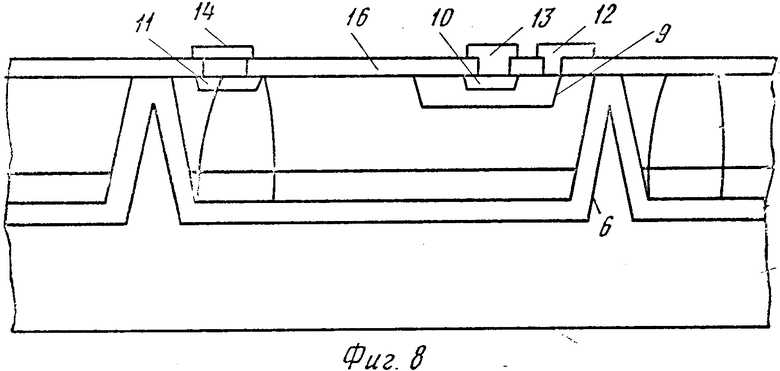

На фиг. 1 изображена монокристаллическая пластина полупроводникового материала 1; на фиг. 2 - создание в маске 2 локальных областей 3; на фиг. 3 - формирование скрытого высоколегированного слоя 4 и слоя диэлектрика 5; на фиг. 4 - вытравливание канавок 6; на фиг. 5 - нанесение диэлектрического слоя 7; на фиг. 6 - нанесение поликристаллической подложки 8; на фиг. 7 - формирование полупроводниковой структуры с диэлектрической изоляцией; на фиг. 8 - формирование транзисторной структуры с диэлектрической изоляцией, где 9 - монокристаллический карман, 10 - база, 11 - эмиттер, 12 - подлегированный контакт к коллектору, 13-15 - металлизированные электроды базы, эмиттера и коллектора, 16 - слой диэлектрика.

Пример 1. Создание локального вывода скрытого слоя с использованием разности коэффициентов диффузии примесей.

Пластину монокристаллического кремния 1 (фиг. 1) n-типа проводимости окисляют в режиме:

T 1150oC; время (t) окисления 15-35-20 мин

сухой О2 пар Н2О сухой О2

В окисле методом фотолитографии вскрывают окна и проводят локальное введение фосфора (фиг. 2) с использованием жидкого источника диффузии РСl3 в режиме:

T = 1100oC; t = 2 - (10 + 3) - (18 + 2) мин

сухой О2 продувка РСl3 сухой О2

При этом поверхностное сопротивление диффузионного слоя Psp ≅ 1,5 ом/ , глубина загонки фосфора Хjp ≥ 4 мкм. После стравливания окисла со всей поверхности пластины формируется введением сурьмы из легирующей композиции КСС-60-20Т высоколегированный слой 4 (фиг. 3) в режиме:

T = 1220oC; t = 80+10 мин в сухом О2 при этом Psb скрытого высоколегированного слоя ≅ 15,0 ом/ при глубине 2,5 мкм ≅ Хjsb ≅ ≅ 3,5 мкм. Rsp ≅ 1,0 ом/ ; Xjp ≅ 13 мкм.

Одновременно с формированием высоколегированного слоя создается маскирующий слой 5 (окисел кремния).

Коэффициент диффузии сурьмы, образующий слой 4, значительно меньше коэффициента диффузии фосфора, образующего локальный слой 3. В результате создается разность в глубинах проникновения примесей в соответствующих областях. В окисле 5 методом фотолитографии вскрывают окна и вытравливаются разделительные канавки 6 (фиг. 4). Наращивается диэлектрический слой 7 (пиролитическая пленка окисла (фиг. 5), подложка 8 (поликристаллический кремний (фиг. 6).

Одновременно с выполнением этих операций, которые осуществляются при 1180-1200оС в течение 4 ч, а также одновременно с формированием скрытого высоколегированного слоя происходит глубокая диффузия фосфора из локальных областей 3 и достигает глубины проникновения Xjp ≥ 25 мкм. При этом сурьма в открытом слое проникает в пластины до глубины 5 мкм ≅ Х ≅ 7 мкм. На фиг. 7 изображена структура с диэлектрической изоляцией локальным выводом скрытого слоя примеси к поверхности кармана.

Пример 2. Создание локального вывода скрытого слоя с использованием перевода областей кремния, в которых формируется локальный вывод, в пористое состояние.

Пластина монокристаллического кремния (фиг. 1) n-типа проводимости окисляется в режиме:

T = 1150oC; t = 15-35-20 мин

сухой О2 пар Н2О сухой О2

В окисле 2 методом фотолитографии вскрываются окна и пластина подвергается анодной обработке с рабочей стороны в условиях освещения светом. Для получения пористого слоя кремния толщиной 30 мкм электрохимический процесс проводят в электролите состава: 1 часть 48% НF, 3 части этиленгликоля, при плотности тока 5 ма/см2 в течение 15-20 мин (фиг. 2).

После стравливания пленки окисла со всей поверхности пластины формируется высоколегированный слой 4 в режиме:

T = 1060oC; t = 2 - (10 + 4) - (15 + 5) мин

сухой О2 продувка PCl3 сухой О2 при этом Rs = 2,0-3,5 ом/ , Хj = 2-2,5 мкм.

Увеличение эффективного коэффициента диффузии легирующей примеси в пористом кремнии обеспечивает проникновение атомов фосфора по всему объему пористого материала, т. е. в областях Si, переведенных в пористое состояние, глубина диффузии фосфора составляет более 30 мкм.

Пластина окисляется в режиме:

T = 1150oC; t = 15-40-20 мин

сухой О2 пар Н2О сухой О2 (фиг. 3). В результате окисления происходит уплотнение пористого кремния. В окисле 5 методом фотолитографии вскрываются окна и вытравливаются разделительные канавки 6 (фиг. 4). Далее проводятся операции, описанные в примере 1, начиная с наращивания диэлектрического слоя 7.

Пример 3. В пластину монокристаллического кремния проводят диффузию фосфора в режиме:

T = 1060oC; t = 2 - 10 + 4 - 15 + 5 мин

сухой О2 продувка РСl3 сухой О2

при этом диффузионные параметры:

Rs = 2,0 - 3,5 ом/ ; Xj = 2,0-2,5 мкм

С использованием известных методов маскирования фотолитографии области кремния 3, в которых формируется локальный вывод "скрытого" п+ слоя к поверхности КСДИ, бомбардируются моноэнергетическими протонами. Плотность потока протонов 5˙1011 см-2с-1, температура облучения 900оС, энергия бомбардирующих протонов 450 кЭВ. При этом разность глубин проникновения примеси в пластину в бомбардируемых и небомбардируемых протонами областях достигает ≈ 12 мкм (фиг. 3).

Пластина окисляется. В окисле 5 методом фотолитографии вскрываются окна и вытравливаются разделительные канавки 6 (фиг. 4).

Далее проводятся операции, описанные в примере 1, начиная с наращивания диэлектрического слоя 7. Последовательность операций до травления разделительных канавок 6 (фиг. 4) может быть изменена. Однако предложенная последовательность обеспечивает наибольшее время высокотемпературного воздействия на формирование профиля локального вывода, при создании высоколегированного слоя, изоляции, подложки и транзисторных структур.

Использование высокотемпературного воздействия на исходную монокристаллическую пластину кремния при образовании высокотемпературного "скрытого слоя", нанесении диэлектрического слоя на разделительные канавки и наращивании поликристаллической кремниевой подложки для проникновения атомов примеси, образующей локальные области выхода скрытого слоя, уменьшает общую длительность высокотемпературных обработок при изготовлении транзисторных структур, так как при этих операциях атомы примеси, формирующие локальные выходы, диффундируют на глубину более 25 мкм. Это исключает дополнительную операцию по формированию профиля локальных областей выхода, что, в свою очередь, приводит к экономии трудовых и материальных ресурсов и увеличивает процент выхода, так как при этом уменьшается деформация подложки с монокристаллическими карманами. (56) Патент США N 3391023, кл. 428-162, опублик. 1968.

Патент США N 3509433, кл. 357-49, опублик. 1970.

Патент США N 3412285, кл. 315-39, 61, опублик. 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1989 |

|

SU1702826A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ВЫСОКОВОЛЬТНЫХ ИНТЕГРАЛЬНЫХ СХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1990 |

|

SU1739805A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВЫХ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1983 |

|

SU1108966A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ ЭЛЕМЕНТОВ | 1990 |

|

SU1686982A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1991 |

|

RU2024108C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 1989 |

|

SU1702825A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ | 1982 |

|

SU1085439A1 |

| КОНСТРУКЦИЯ ИНТЕГРАЛЬНЫХ СХЕМ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ И СПОСОБ ИХ ИЗГОТОВЛЕНИЯ | 1980 |

|

SU824824A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1979 |

|

SU760837A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СТРУКТУР КРЕМНИЕВЫХ ИНТЕГРАЛЬНЫХ СХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ КОМПОНЕНТОВ | 1984 |

|

SU1222149A1 |

СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВЫХ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ, включающий образование на исходной монокристаллической пластине высоколегированных скрытых слоев того же типа проводимости, что и пластина, травление разделительных канавок, нанесение на них диэлектрического слоя, наращивание на него поликристаллической кремниевой подложки, вскрытие монокристаллических карманов, формирование в монокристаллических кремниевых карманах транзисторных структур, отличающийся тем, что, с целью упрощения технологии и увеличения процента выхода годных структур, до образования высоколегированных скрытых слоев или одновременно с ними формируют на исходной монокристаллической пластине локальные высоколегированные области того же типа проводимости, что и скрытый слой, и через них выводят скрытые слои к рабочей поверхности монокристаллических карманов одновременно с проведением операций по формированию транзисторных структур.

Авторы

Даты

1994-04-15—Публикация

1981-11-25—Подача