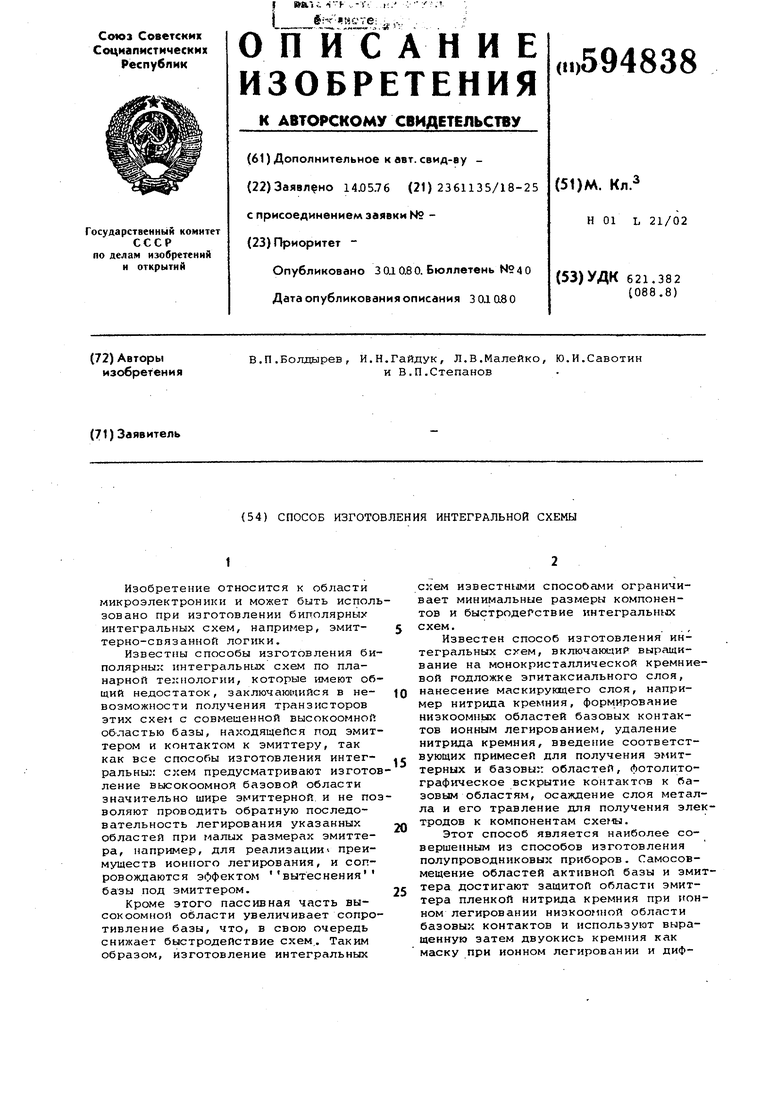

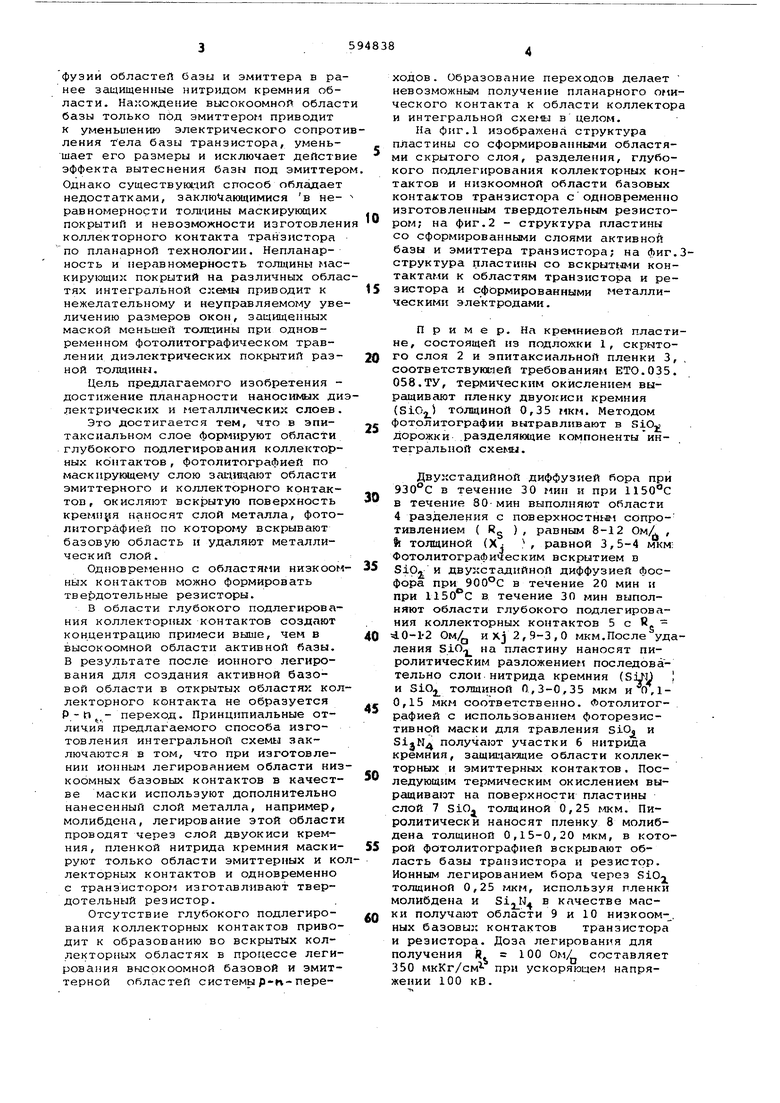

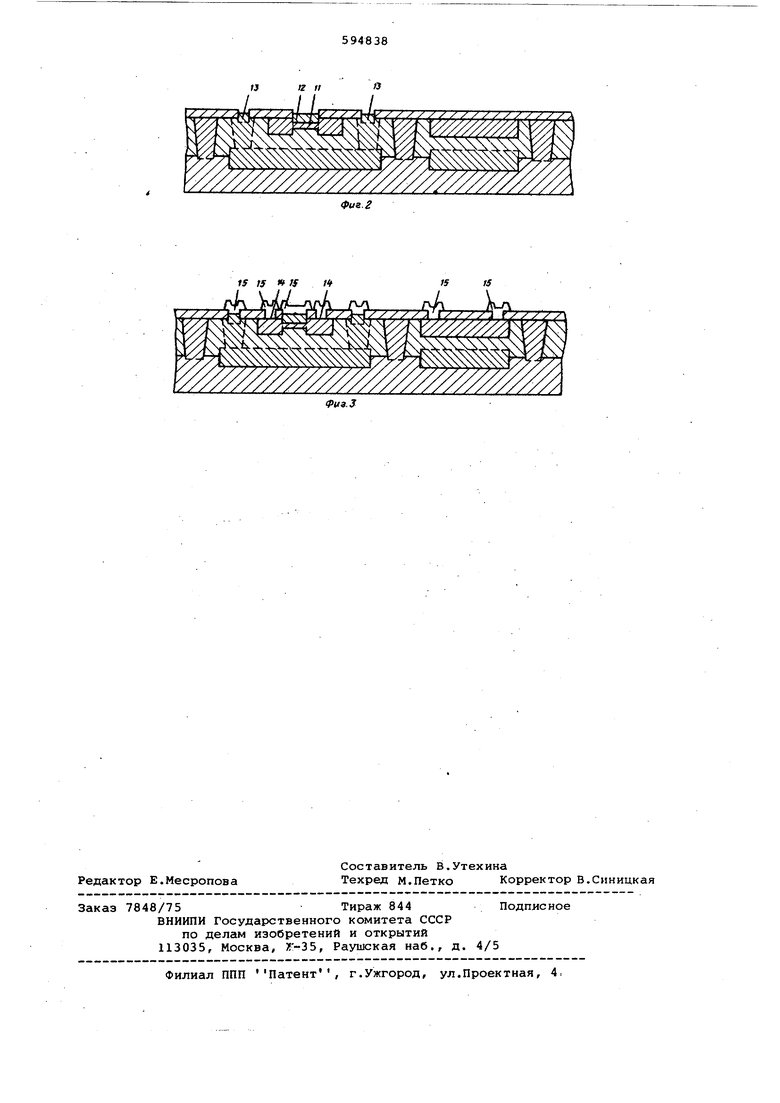

Изобретение относится к области микроэлектроники и может быть испол зовано при изготовлении биполярных интегральных схем, например, эмиттерно-связанной логики. Известны способы изготовления би полярных интегральных схем по планарноП технологии, которые имеют об щий недостаток, заключающийся в невозможности получения транзисторов этих схем с совмещенной высокоомной областью базы, находящейся под эмит тером и контактом к эмиттеру, так как все способы изготовления интегральных схем предусматривают изгото ление высокоомной базовой области значительно шире эмиттерной и не по воляют проводить обратную последовательность легирования указанных областей при малых размерах эмиттера, например, для реализации преимуществ ионвюго легирювания, и сопровождаются эффектом вытеснения базы под эмиттером. Кроме этого пассивная часть высокоомной области увеличивает сопро тивление базы, что, в свою очередь снижает быстродействие схем. Таким образом, изготовление интегральных схем известними спосооами ограничивает минимальные размеры компонентов и быстродействие интегральных схем. Известен способ изготовления интегральных схем, включающий выращивание на монокристаллической кремниевой подложке эпитаксиального слоя, нанесение маскирующего слоя, например нитрида кремния, формирование ниэкоомных областей базовых контактов ионным легированием, удаление нитрида кремния, введение соответствующих примесей для получения эмиттерных и базовы:: областей, фотолитографическое вскрытие контактов к базовым областям, осаждение слоя металла и его травление для получения электродов к компонентам схемы. Этот способ является наиболее совершенным из способов изготовления полупроводниковых приборов. Самосовмещение областей активной базы и змиттера достигают защитой области эмиттера пленкой нитрида кремния при ионном легировании низкоомной области базовых контактов и используют выращенную затем двуокись кремния как маску при ионном легировании и диффузий областеП базы и эмиттера в ра нее защищенные нитридом кремния области. Нахождение высокоомной облас базы только под эмиттером приводит к уменьшению электрического сопрот ления тела базы транзистора, уменьшает его размеры и исключает действ эффекта вытеснения базн под эмиттер Однако существующий способ обладает недостатками, заклю 1ающимися в неравномерности тол1чины маскирующих покрытий и невозможности изготовлен коллекторного контакта транзистора по планарноП технологии. Непланарность и перавнс лерность толщиньз мас кирующих покрытий на различных обла тях интегральной схемы приводит к нежелательному и неуправляемому уве личению размеров окон, защищенных маской меньшей толщины при одновременном фотолитографическом травлении диэлектрических покрытий разной толщины. Цель предлагаемого изобретения достижение планарности наносимых ди лектрических и металлических слоев. Это достигается тем, что в эпитаксиальном слое формируют области глубокого подлегирования коллекторных контактов, фотолитографией по мacкиpyющe y слою защищают области эмиттерного и коллекторного контактов, окисляют вскрытую поверхность кремния наносят слой металла, фотолитографией по которому вскрывают базовую область и удаляют металлический слой. Одновременно с областями низкоом ных контактов можно формировать твердотельные резисторы. В области глубокого подлегирования коллекторных контактов создают концентрацию примеси выще, чем в высокоомной области активной базы. В результате после ионного легирования для создания активной базоBofi области в открытых областях кол лекторного контакта не образуется Р-О - переход. Принципиальные отличия предлагаемого способа изготовления интегральной cxeMta заключаются в том, что при изготовлении ионным легированием области низ коомных базовых контактов в качестве маски используют дополнительно нанесенный слой металла, например, молибдена, легирование этой области проводят через слой двуокиси кремния, пленкой нитрида кремния маскируют только области эмиттерных и ко лекторных контактов и одновременно с транзистором изготавливают твердотельный резистор. Отсутствие глубокого подлегирования коллекторных контактов приводит к образованию во вскрытых коллекторных областях в процессе легирования высокоомной базовой и эмиттерной областей системы р-п-переходов. Образование переходов делает невозможным получение планарного омического контакта к области коллектора и интегральной схемы в целом. На фиг.1 изображена структура пластины со сформированными областями скрытого слоя, разделения, глубокого подлегирования коллекторных контактов и низкоомной области базовых контактов транзистора с одновременно изготовленным твердотельным резистором; на фиг.2 - структура пластины со сформированными слоями активной базы и эмиттера транзистора; на фиг.Зструктура пластины со вскрытыми контактами к областям транзистора и резистора и сформированными металлическими электродами. Пример. На кремниевой пластине, состоящей из подложки 1, скрытого слоя 2 и эпитаксиальной пленки 3, соответствуюиеП требованиям ETC.035. 058.ТУ, термическим окислением выращивают пленку двуокиси кремния (SiOj) толщиной 0,35 пкм. Методом фотолитографии вытравливают в SiOj дорожки разлелякхцие компонентыинтегральной схемы. Двухстадийной диффузией бора при 930°С в течение 30 мин и при 1150с в Te4eHife 80- мин выполняют области 4 разделения с поверхностным сопротивлеиием ( Rg ) , равнЕлм 8-12 Ом/ , fe толщиной (Xj : , равной 3,5-4 мкм; Фотолитографическим вскрытием в Sipj и двухстадийной диффузией фосфора при в течение 20 мин и при в течение 30 мин выполняют области глубокого подлегирования коллекторных контактов 5 с R. 40-12 Ом/ и XJ 2,9-3,0 мкм.После удаления SiO на пластину наносят пиролитическим разложением последовательно слои нитрида кремния (SiJlJ I и SiOj толщиной 0,3-0,35 мкм и 0,10,15 мкм соответственно. Фотолитографией с использованием фоторезистивной маски для травления SiO и SijN получают участки б нитрида кремния, эащшцаквдие области коллекторных и эмиттерных контактов. Последующим термическим окислением выращивают на поверхности пластины слой 7 SiOj толщиной 0,25 мкм. Пиролитически наносят пленку 8 молибдена толщиной 0,15-0,20 мкм, в которой фотолитографией вскрывают область базы транзистора и резистор. Ионным легированием бора через SiO толщиной 0,25 мкм, используя пленки молибдена и в качестве маски получают области 9 и 10 низкоом-. ных базовых контактов транзистора и резистора. Доза легирования для получения И 100 Ом/ составляет 350 мкКг/см при ускоряющем напряжении 100 кВ.

Применением азотноп и ортоЛосфорной кислот удаляют пленки молибдена и нитрида кремния.

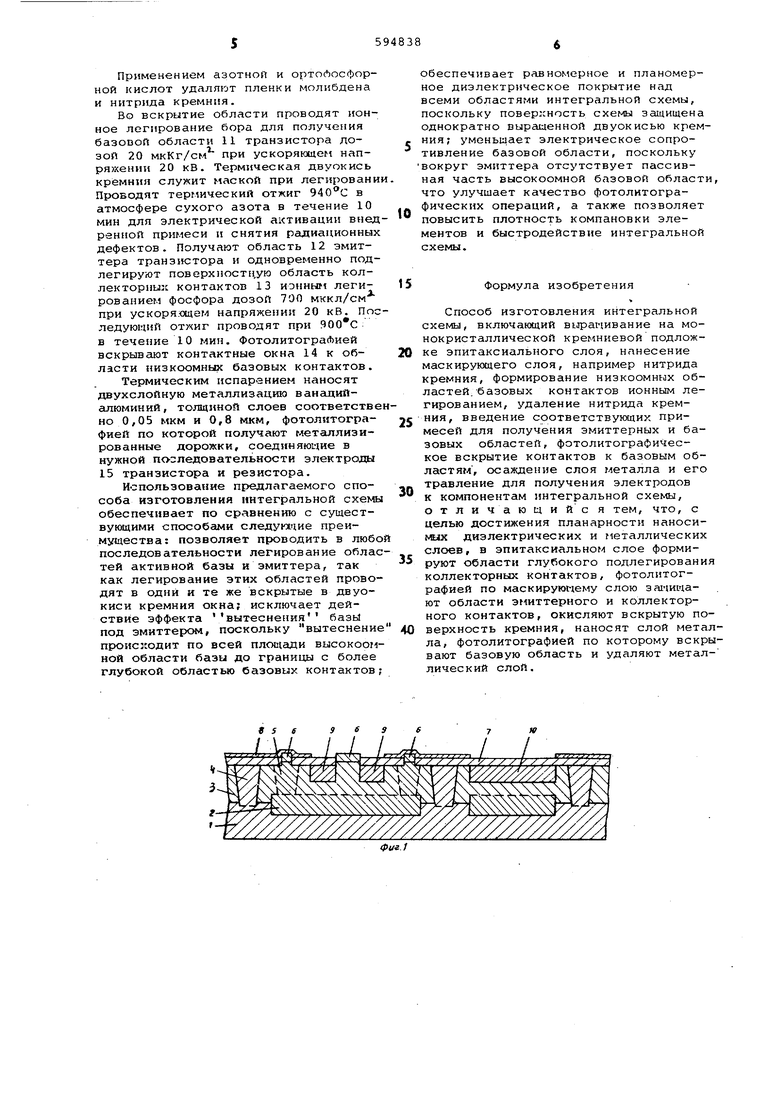

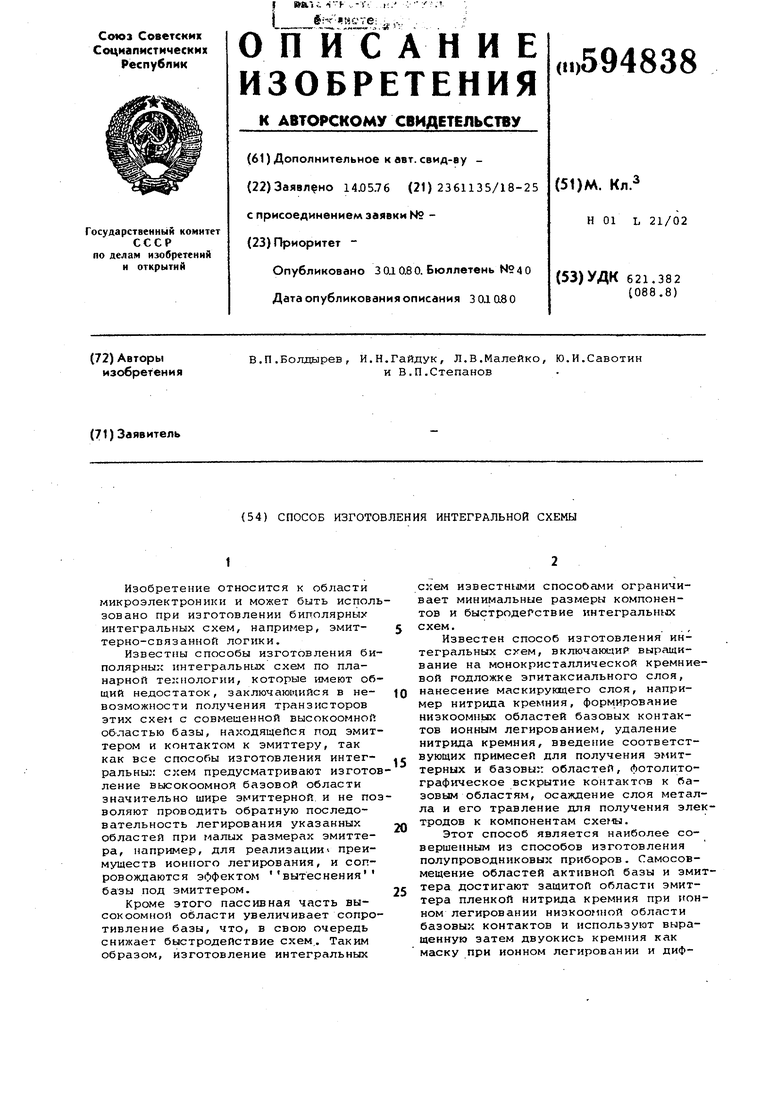

Во вскрытие области проводят ионное легирование бора для получения базовой области 11 транзистора дозоП 20 мкКг/см при ускоряющем напряжении 20 кВ. Термическая двуокись кремния служит маской при легировани Проводят термический отжиг в атмосфере сухого азота в течение 10 мин для электрической активации внедренной примеси и снятия радиационных дефектов. Получают область 12 эмиттера транзистора и одновременно подлегируют поверхпостн.ую область коллекторних контактов 13 ионныи легированием фосфора дозой 700 мккл/см при ускоря-ощем напряжении 20 кВ . ледующиП отжиг проводят при 900 С в течение 10 мин. ФотолитограЛией вскрывают контактные окна 14 к области низкоомных базовых контактов.

Термическим испарением наносят двухслойную металлизацию вангщийалюминий, толщиной слоев соответствено 0,05 мкм и 0,8 мкм, фотолитографией по которой получают металлизированные дорожки, соединяющие в нужной последовательности электроды 15 транзистора и резистора.

Использование предлагаемого способа изготовления интегральной схемы обеспечивает по сравнению с существующими способами следукхчие преимущества: позволяет проводить в любо последовательности легирование областей активной базы и эмиттера, так как легирование этих областей проводят в одни и те же вскрытые в двуокиси кремния окна; исключает действие эффекта вытеснения базы под эмиттером, поскольку вытеснение происходит по всей плoLчaди высокоомной области базы до границы с более глубокой областью базовых контактов

обеспечивает равномерное и планомерное диэлектрическое покрытие над всеми областями интегральной схемы, поскольку поверхность схемы защищена однократно выраыенной двуокисью кремния; уменьшает электрическое сопротивление базовой области, поскольку вокруг эмиттера отсутствует пассивная часть высокоомной базовой области, что улучшает качество фотолитографических операций, а также позволяет повысить плотность компановки элементов и быстродействие интегральной схемы.

5

Формула изобретения

V

Способ изготовления интегральной схемы, включающий выращивание на монокристаллической кремниевой подлож0ке эпитаксиального слоя, нанесение маскирующего слоя, например нитрида кремния, формирование низкоомных областей, -базовых контактов ионным легированием, удаление нитрида кремния, введение соответствующих при5месей для получения эмиттерных и базовых областей, фотолитографическое вскрытие контактов к базовым областям, осаждение слоя металла и его травление для получения электродов

0 к компонентам интегральной схемы, отличающийс я тем, что, с целью достижения планарности наносимых диэлектрических и металлических слоев, в эпитаксиальном слое форми5руют области глубокого поллегирования коллекторных контактов, фотолитографией по маскирующему слою зтчищают области э 1иттepнoгo и коллекторного контактов, окисляют вскрытую поверхность кремния, наносят слой метал0ла, фотолитографией по которому вскрывают базовую область и удаляют металлический слой.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1978 |

|

SU705934A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩАЮЩИХСЯ ПЛАНАРНЫХ ТРАНЗИСТОРОВ | 1978 |

|

SU723984A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ p-n-ПЕРЕХОДАМИ | 1981 |

|

SU1072666A1 |

| КОНСТРУКЦИЯ ИНТЕГРАЛЬНЫХ СХЕМ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ И СПОСОБ ИХ ИЗГОТОВЛЕНИЯ | 1980 |

|

SU824824A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ p-n-ПЕРЕХОДАМИ | 1983 |

|

SU1178269A1 |

| Способ изготовления высокочастотных транзисторных структур | 1983 |

|

SU1114242A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ P-N-ПЕРЕХОДАМИ | 1984 |

|

SU1215550A1 |

| Способ изготовления ВЧ транзисторных структур | 1979 |

|

SU766423A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ ТРАНЗИСТОРОВ | 1985 |

|

SU1371445A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ВЫСОКОВОЛЬТНОГО ИНТЕГРАЛЬНОГО ТРАНЗИСТОРА | 2012 |

|

RU2492546C1 |

№

/ jr у /

W/////,

У///////Л

II

XX X X У

tS ff If

S

15IS

},«,z

.

Авторы

Даты

1980-10-30—Публикация

1976-05-14—Подача