10

15

20

25

11341726

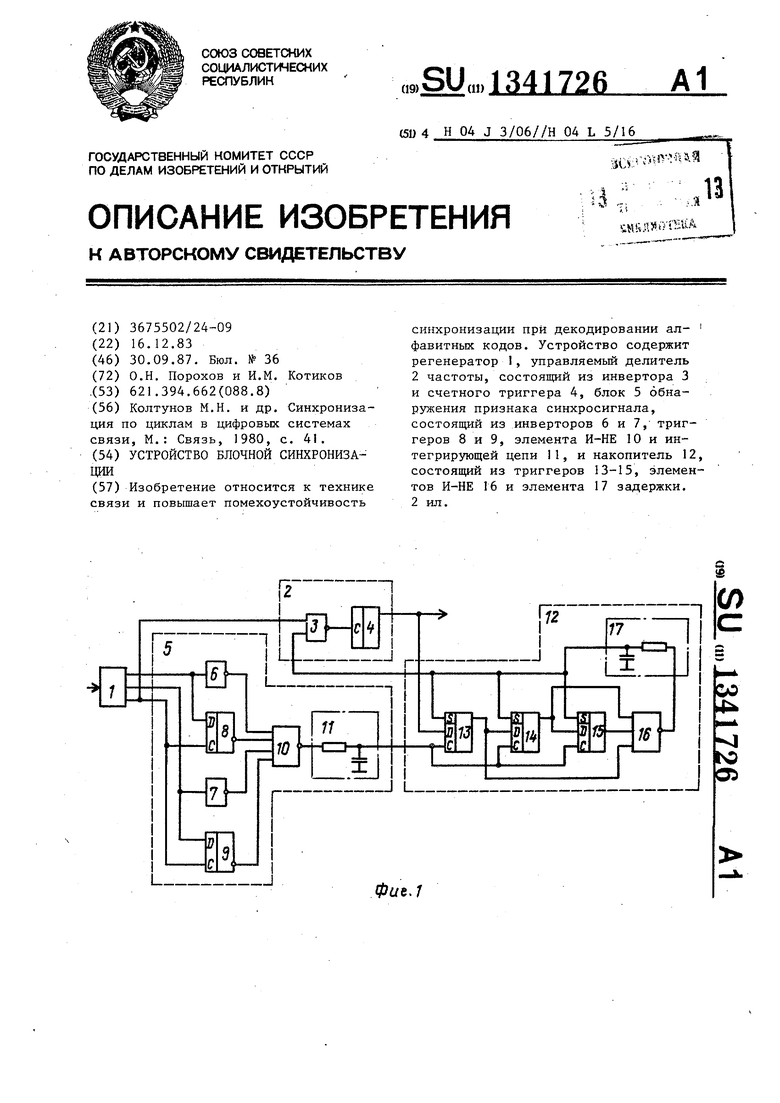

Изобретение относится к технике лы вязи и может быть использовано при екодировании алфавитных кодов в цифовых системах передачи с различными ередающими средствами.

Цель изобретения - повьшение поехоустойчивости синхронизации при екодировании алфавитных кодов.

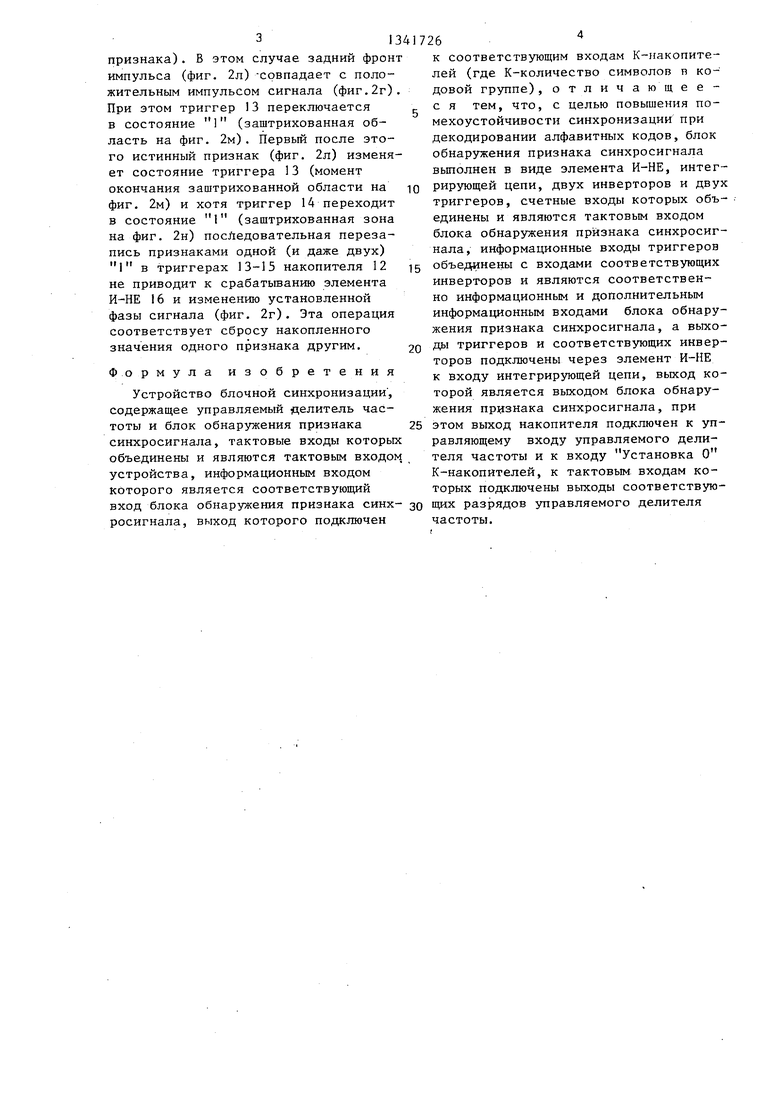

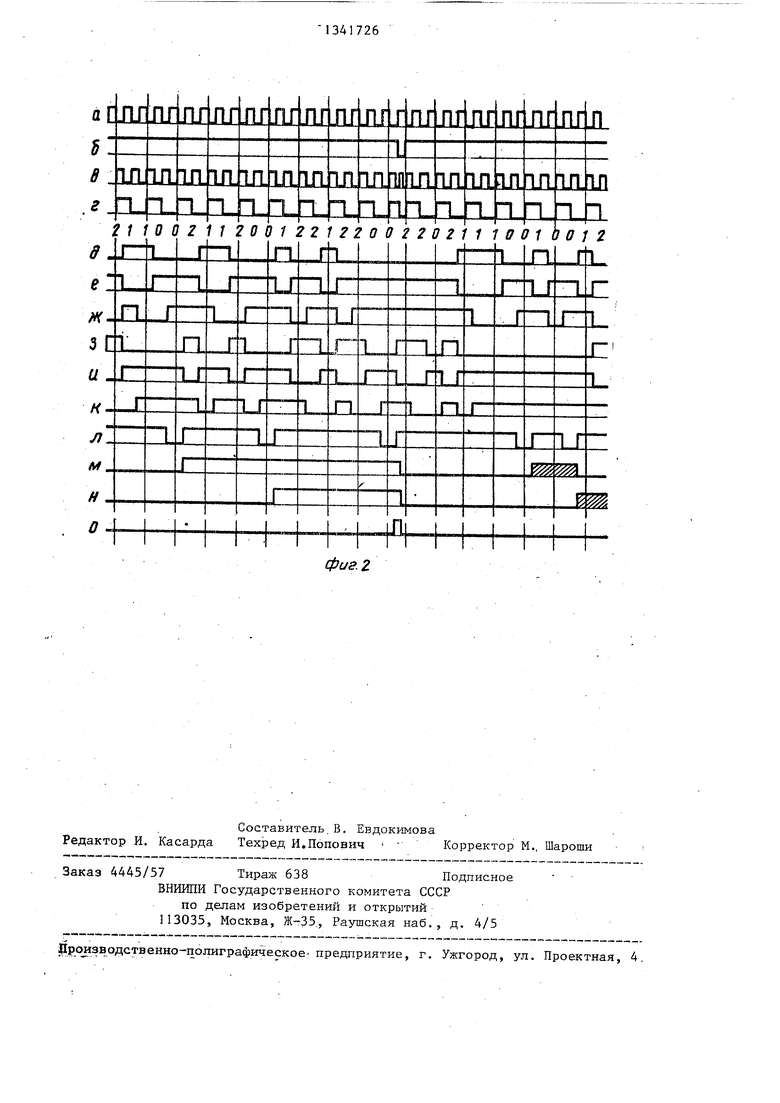

На фиг. 1 представлена структур- ая электрическая схема устройства лочной синхронизации; иа фиг. 2 - временные диаграммы , поясняющие работу устройства.

Устройство блочной синхронизации содержит регенератор ., управляемый делитель 2 частоты, состоящий из инвертора 3 и счетного триггера 4, блок 5 обнаружения признака синхросигнала, состоящий из первого и второго инверторов 6 и 7, триггеров 8 и 9, элемента И-НЕ 10 и интегрирующей депи 11, и накопитель 12, состоящий из триггеров 13-15, элемента И-НЕ 16 и элемента 17 задержки.

Устройство блочной синхронизации работает следующим образом.

В регенераторе 1 из принятого линейного сигнала формируется тактовый сигнал, случайные последовательности вторых и третьих троичных символов (фиг. 2а,д,з).С первого вы- хоДа регенератора 1 тактовый сигнал (фиг, 2а) подается на первый вход инвертора 3 управляемого делителя 2 частоты, а также на счетные входы Триггеров 8 и 9 блока 5 обнаружения. При отсутствии на другом входе инвертора 3 импульсов управления (фиг.2б), поступающих с выхода элемента 17 задержки, инвертированный тактовый сигнал (фиг. 2в) с выхода инвертора 3 подается на счетньш вход счетного триггера 4, на выходе которого в результате деления тактовой частоты на 2 с точностью до фазы формируется сигнал (фиг. 2г), который подается на вход триггера 13 накопителя 12.

Признаком тактового сигнала в коде ЗВ2Т считают моменты появления двух первых троичных символов 00, которые в отсутствие ошибок могут появляться только на границах тактовых интервалов при приеме следующих сочетаний троичных групп: 10 01, 10 02, 20 01, 20 02.

Последователь признаков синхросигнала (фиг. 2л) формируется в блоке 5 обнаружения. Вторые троичные симворат

6 g сим

ре

7 вы ны и,ж Иетчт тр со чи тр та ко вр

дл им ко на ин

пр ег ре пр мо ис на

по 13 тр с с по мо вх с н, .16 то де ме 2 ка За ро 5 ни зн

30

35

40

45

50

55

ле 00

0

5

20

25

лы

(фиг. 2д) с второго выхода регенератора I подаются на входы инвертора

6и триггера 8, а третьи троичные g символы (фиг. 2з) с третьего выхода

регенератора 1 - на входы инвертора

7и триггера 9. Единичные сигналы с выходов инверторов 6 и 7 и с инверсных выходов триггеров 8 и 9 (фиг.2е, и,ж,к) поступают на входы элемента ИНЕ 10, на выходе которого формируется при этом нулевой сигнал (фиг.2л), что связано с отсутствием второго и третьего троичных символов на двух соседних тактовых интервалах, а значит характеризует прием первых О троичных символов на двух соседних тактовых интервалах, т.е. признаков синхросигнала. Ввиду разбросов времени срабатьшания с микросхем

для устранения возможных дроблений импульсов последовательность признаков синхросигнала (фиг. 2л) подается на выход блока 5 обнаружения через интегрирующую цепь П.

При обнаружении первого истинного признака синхросигнала (фиг. 2л), его задний фронт (положительный переход) совпадает с положительным напряжением сигнала (фиг. 2г). Этот момент служит началом накопления истинных признаков синхросигнала в накопителе 12.

Признаки синхросигнала (фиг. 2л) подаются иа счетные входы триггеров 13-15 накопителя 12. Причем на вход триггера 13 подается сигнал (фиг. 2г) с выхода делителя 2 частоты. Сигнал с прямого выхода триггера (фиг. 2м) подается на вход триггера 14, с прямого выхода которого (фиг. 2н) - на вход триггера 15. При этом сигналы с выходов триггеров 13-15 (фиг.2м, н,о) поступают на входы элемента И-НЕ .16, управляющий сигнал с выхода которого (фиг. 2б) через элемент 17 задержки подается на второй вход элемента И-НЕ-3 управляемого делителя 2 частоты, а также на входы Установка О триггеров 13-15 (фиг. 2б,м,н,о). За счет этого изменяется фаза синх- роригнала (фиг. 2г) на выходе блока 5 обнаружения, осуществляется вхождение в синхронизм и сброс накопленных значений признаков.

30

35

40

45

50

55

Однако из-за ошибок возможно появление двух первых троичных символов 00 внутри кодовых групп (ложного

признака). В этом случае задний фронт импульса (фиг. 2л) -совпадает с положительным импульсом сигнала (фиг.2г). При этом триггер 13 переключается в состояние 1 (заштрихованная область на фиг. 2м). Первый после этого истинный признак (фиг. 2л) изменяет состояние триггера 13 (момент окончания заштрихованной области на фиг. 2м) и хотя триггер 14 переходит в состояние 1 (заштрихованная зона на фиг. 2н) последовательная перезапись признаками одной (и даже двух) 1 в триггерах 13-15 накопителя 12 не приводит к срабатыванию элемента И-НЕ 16 и изменению установленной фазы сигнала (фиг. 2г). Эта операция соответствует сбросу накопленного значения одного признака другим.

Ф о рмула изобретения

Устройство блочной синхронизации , содержащее управляемый делитель частоты и блок обнаружения признака синхросигнала, тактовые входы которых объединены и являются тактовым входом устройства, информационным входом которого является соответствующий вход блока обнаружения признака синх- росигнала, выход которого подключен

к соответствующим входам К-накопите- лей (где К-количество символов п кодовой группе),отличающее- с я тем, что, с целью повышения помехоустойчивости синхронизации при декодировании алфавитных кодов, блок обнаружения признака синхросигнала выполнен в виде элемента И-НЕ, интегрирующей цепи, двух инверторов и дву триггеров, счетные входы которых объединены и являются тактовым входом блока обнаружения признака синхросигнала, информационные входы триггеров объединены с входами соответствующих инверторов и являются соответственно информационным и дополнительным информационным входами блока обнаружения признака синхросигнала, а выходы триггеров и соответствующих инверторов подключены через элемент И-НЕ к ВХОДУ интегрирующей цепи, выход которой является выходом блока обнаружения признака синхросигнала, при этом выход накопителя подключен к управляющему входу управляемого делителя частоты и к входу Установка О К-накопителей, к тактовым входам которых подключены выходы соответствующих разрядов управляемого делителя частоты.

фиё.2

Составитель.в, Евдокимова Редактор И. Касарда Техред И.Попович Корректор М., Шароши

Заказ 4445/57 Тираж 638Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35., Раушская наб., д. 4/5

|1роизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1989 |

|

SU1795557A1 |

| Биимпульсный регенератор | 1986 |

|

SU1413727A2 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| Биимпульсный регенератор | 1982 |

|

SU1104670A2 |

| Преобразователь двоичного кода в трехпозиционный код | 1984 |

|

SU1317675A1 |

| Биимпульсный регенератор | 1980 |

|

SU892742A1 |

| Устройство символьной синхронизации | 1990 |

|

SU1775869A1 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1984 |

|

SU1228296A2 |

| Устройство для передачи и приема цифровых сигналов | 1980 |

|

SU978375A1 |

| Адаптивный регенератор | 1986 |

|

SU1363490A1 |

Изобретение относится к технике связи и повышает помехоустойчивость синхронизации при декодировании ал- фавитных кодов. Устройство содержит регенератор 1, управляемый делитель 2 частоты, состоящий из инвертора 3 и счетного триггера 4, блок 5 обнаружения признака синхросигнала, состоящий из инверторов 6 и 7, триггеров 8 и 9, элемента И-НЕ 10 и интегрирующей цепи II, и накопитель 12, состоящий из триггеров 13-15, элементов И-НЕ 16 и элемента 17 задержки. 2 ил.

| Колтунов М.Н | |||

| и др | |||

| Синхронизация по циклам в цифровых системах связи, М.: Связь, 1980, с | |||

| Механический грохот | 1922 |

|

SU41A1 |

Авторы

Даты

1987-09-30—Публикация

1983-12-16—Подача