Изобретение относится к электросвязи и может использоваться в цифровых системах передачи с различными передающими средами.

Целью изобретения является уроще- ние преобразователя путем исключения анализатора полярностей, блока балансировки и мультиплексора и повышение помехоустойчивости путем увеличений

триггеры 30 и 31 и интегрирующие цепи 32 и 33.

Преобразователь двоичного кода в трехпозиционный код работает следующим образом.

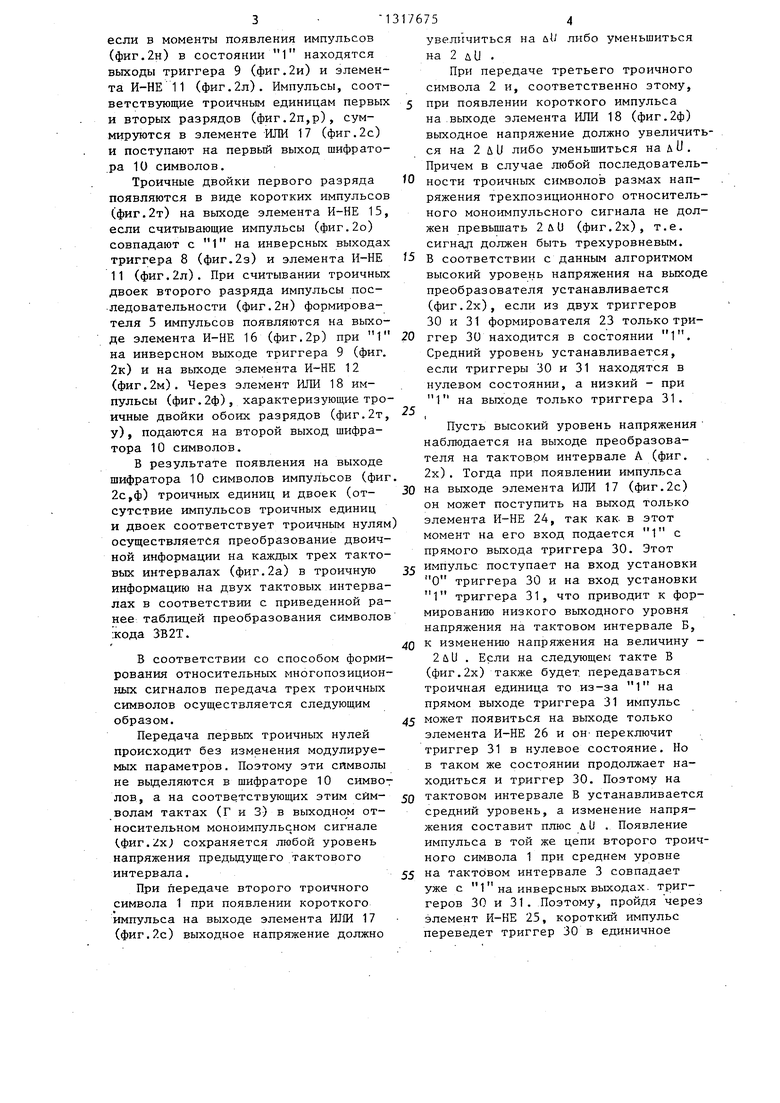

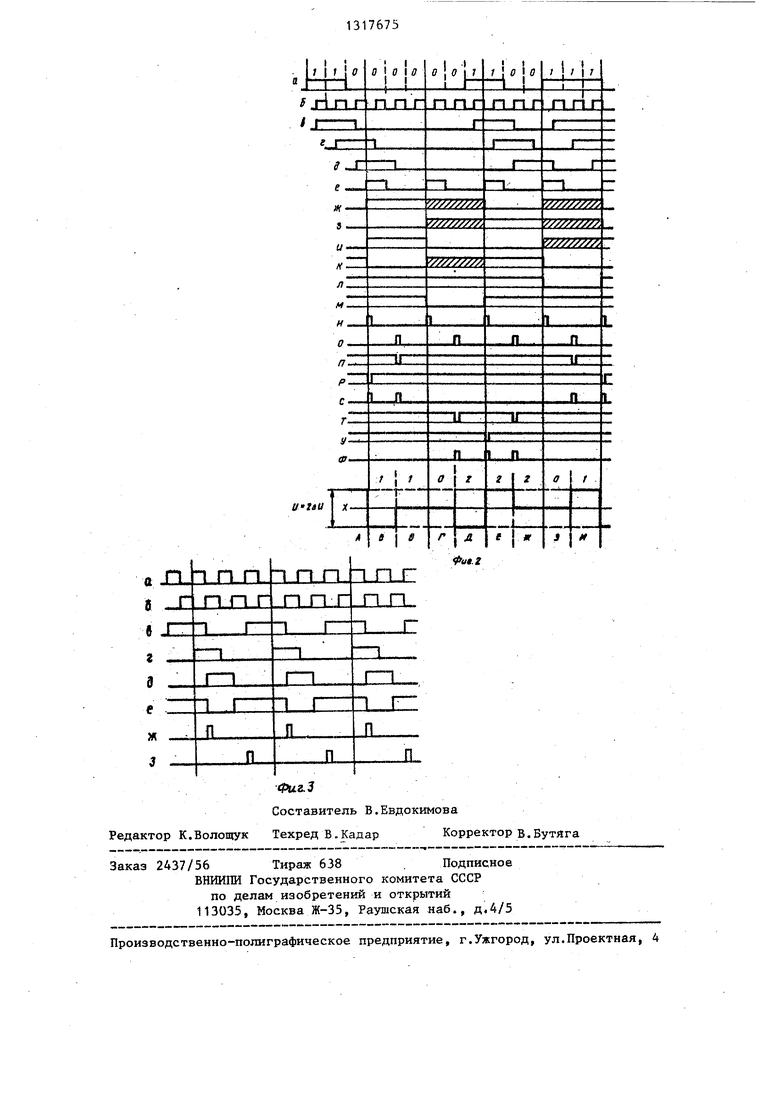

Двоичная информация (фиг.2 а) источника 1 поступает на вход последовательного регистра 2, на вход синхронизации которого подается такдлительности импульсов линейного сиг- Ш товьй сигнал с блока 3 синхронизации нала.(фиг 26) через инвертор 4. Благодаря

сдвигу двоичной информации тактовым сигналом на выходах последовательно регистра 2 одновременно присутствую три разряда двоичной информации (фиг.2в, г, д).

При делении на три двоичного так тового сигнала (фиг. 26) на первом

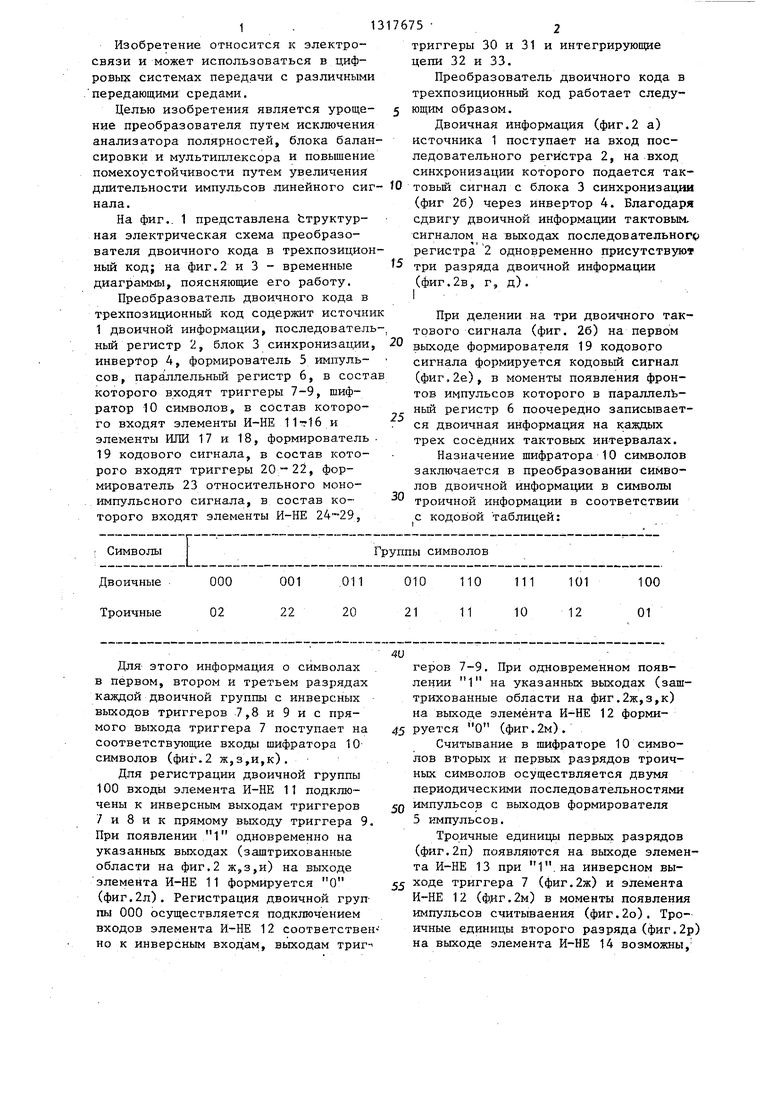

На фиг.. 1 представлена Ьтруктур- ная электрическая схема преобразователя двоичного кода в трехпозиционный код; на фиг.2 и 3 - временкше диаграммы, поясняющие его работу.

Преобразователь двоичного кода в трехпозиционный код содержит источник 1 двоичной информации, последователь-,

ньй регистр 2, блок 3 синхронизации, 20 выходе формирователя 19 кодового инвертор 4, формирователь 5 импуль- сигнала формируется кодовый сигнал сов, параллельный регистр 6, в состав которого входят триггеры 7-9, шифратор 10 символов, в состав которого входят элементы И-НЕ 11 716 и элементы ИЛИ 17 и 18, формирователь 19 кодового сигнала, в состав которого входят триггеры 20™ 22, фор25

(фиг.2е), в моменты появления фронтов импульсов которого в параллельный регистр 6 поочередно записывает ся двоичная информация на каждых трех соседних тактовых интервалах.

Назначение шифратора 10 символов заключается в преобразовании символов двоичной информации в символы троичной информации в соответствии с кодовой таблицей:

мирователь 23 относительного моноимпульсного сигнала, в состав которого входят элементы И-НЕ

Для этого информация о символах в первом, втором и третьем разрядах каждой двоичной группы с инверсных выходов триггеров 7,8 и 9 и с прямого выхода триггера 7 поступает на соответствующие входы шифратора 10- символов (фиг.2 ж,з,и,к).

Для регистрации двоичной группы 100 входы элемента И-НЕ 11 подключены к инверсным выходам триггеров 7 и 8 и к прямому выходу триггера 9. При появлении 1 одновременно на указанных выходах (заштрихованные области на фиг.2 ж,,з,и) на выходе элемента И-НЕ 11 формируется О (фиг.2л). Регистрация двоичной группы 000 осуществляется подключением входов элемента И-НЕ 12 соответствен но к инверсным входам, выходам тригтриггеры 30 и 31 и интегрирующие цепи 32 и 33.

Преобразователь двоичного кода в трехпозиционный код работает следующим образом.

Двоичная информация (фиг.2 а) источника 1 поступает на вход последовательного регистра 2, на вход синхронизации которого подается таксдвигу двоичной информации тактовым. сигналом на выходах последовательного регистра 2 одновременно присутствуют три разряда двоичной информации (фиг.2в, г, д).

При делении на три двоичного тактового сигнала (фиг. 26) на первом

выходе формирователя 19 кодового сигнала формируется кодовый сигнал

выходе формирователя 19 кодового сигнала формируется кодовый сигнал

(фиг.2е), в моменты появления фронтов импульсов которого в параллельный регистр 6 поочередно записывается двоичная информация на каждых трех соседних тактовых интервалах.

Назначение шифратора 10 символов заключается в преобразовании символов двоичной информации в символы троичной информации в соответствии с кодовой таблицей:

4Uгеров 7-9, При одновременном появлении 1 на указанных выходах (заштрихованные области на фиг.2ж,з,к) на выходе элемента И-НЕ 12 форми45 руется О (фиг.2м).

Считывание в шифраторе 10 символов вторых и первых разрядов троичных символов осуществляется двумя периодическими последовательностями

Q импульсов с выходов формирователя 5 импульсов.

Троичные единицы первых разрядов (фиг.2п) появляются на выходе элемента И-НЕ 13 при 1.на инверсном вы55 ходе триггера 7 (фиг.2ж) и элемента И-НЕ 12 (фяг.2м) в моменты появления импульсов считываения (фиг.2о). Троичные единицы второго разряда (фиг.2р на выходе элемента И-НЕ 14 возможны,

если в моменты появления импульсов (фиг,2н) в состоянии 1 находятся выходы триггера 9 (фиг.2и) и элемента И-НЕ 11 (фиг,2л). Импульсы, соответствующие троичным единицам первых и вторых разрядов (фиг.2п,р), суммируются в элементе ИЛИ 17 (фиг,2с) и поступают на первый выход шифратора 10 символов.

Троичные двойки первого разряда появляются в виде коротких импульсов (фиг,2т) на выходе элемента И-НЕ 15, если считывающие импульсы (фиг,2о) совпадают с 1 на инверсных выходах триггера 8 (фиг,2з) и элемента И-НЕ 11 (фиг,2л). При считывании троичных двоек второго разряда импульсы последовательности (фиг,2н) формирователя 5 импульсов появляются на выходе элемента И-НЕ 16 (фиг.2р) при 1 на инверсном выходе триггера 9 (фиг, 2к) и на выходе элемента И-НЕ 12 (фиг,2м), Через элемент ИЛИ 18 импульсы (фиг,2ф), характеризующие троичные двойки обоих разрядов (фиг,2т, у), подаются на второй выход шифратора 10 символов,

В результате появления на выходе шифратора 10 символов импульсов (фиг 2с,ф) троичных единиц и двоек (от- сутствие импульсов троичных единиц и двоек соответствует троичньм нулям осуществляется преобразование двоичной информации на каждых трех тактовых интервалах (фиг,2а) в троичную информацию на двух тактовых интервалах в соответствии с приведенной ранее таблицей преобразования символов ;кода ЗВ2Т,

В соответствии со способом формирования относительных многопозиционных сигналов передача трех троичных символов осуществляется следующим образом.

Передача первых троичных нулей происходит без изменения модулируемых параметров. Поэтому эти символы не вьщеляются в шифраторе 10 симвот лов, а на соответствующих этим символам тактах (Г и 3) в выходном относительном моноимпульсном сигнале (.фиг.2х) сохраняется любой уровень напряжения предыдущего тактового интервала.

При передаче второго троичного символа 1 при появлении короткого импульса на выходе элемента ИЛИ 17 (фиг,2с) выходное напряжение должно

fO

J5

3176754

увеличиться на ulJ либо уменьшиться на 2 л и .

При передаче третьего троичного символа 2 и, соответственно этому, при появлении короткого импульса на выходе элемента ИЛИ 18 (фиг,2ф) выходное напряжение должно увеличиться на 2 Д и либо уменьшиться на д U. Причем в случае любой последовательности троичных символов размах напряжения трехпозиционного относительного моноимпульсного сигнала не должен превьш1ать 2uU (фиг.2х), т.е. сигнад должен быть трехуровневым, В соответствии с данным алгоритмом высокий уровень напряжения на выходе преобразователя устанавливается (фиг.2х), если из двух триггеров 30 и 31 формирователя 23 только триггер 30 находится в состоянии 1. Средний уровень устанавливается, если триггеры 30 и 31 находятся в нулевом состоянии, а низкий - при 1 на выходе только триггера 31,

20

Пусть высокий уровень напряжения наблюдается на выходе преобразователя на тактовом интервале А (фиг, 2х), Тогда при появлении импульса на выходе элемента ИЛИ 17 (фиг,2с) он может поступить на вьпсод только элемента И-НЕ 24, так как. в этот момент на его вход подается 1 с прямого выхода триггера 30, Этот импульс поступает на вход установки О триггера 30 и на вход установки 1 триггера 31, что приводит к формированию низкого выходного уровня напряжения на тактовом интервале Б,

к изменению напряжения на величину 2uU . Если на следующеь: такте В (фиг,2х) также будет, передаваться троичная единица то из-за 1 на прямом выходе триггера 31 импульс

может появиться на выходе только элемента И-НЕ 26 и он- переключит триггер 31 в нулевое состояние. Но в таком же состоянии продолжает находиться и триггер 30, Поэтому на

тактовом интервале В устанавливается средний уровень, а изменение напряжения составит плюс л11 . Появление импульса в той же цепи второго троичного символа 1 при среднем уровне

на тактЬвом интервале 3 совпадает уже с 1 на инверсных выходах, триггеров 30 и 31, Поэтому, пройдя через элемент И-НЕ 25, короткий импульс переведет триггер 30 в единичное

10

51317675 состояние и установит высокий уровень выходного напряжения на очередном такте И. По сравнению с предыдущим тактом 3 (фиг.2х) напряжение изменится на величину + ли .

Если на тактовом интервале Д на выходе элемента ИЛИ 18 появится импульс (фиг.2ф), то из-за 1 на ин- версньпс выходах триггеров 30 и 31 он может появиться на выходе только элемента И-НЕ 28. Этот импульс переключит триггер 31 в единичн ое состояние и на тактовом интервале Д установится низкий уровень выходного напряжения.

По сравнению с тактом Г изменение напряжения составит -uU. Появление импульса на выходе элемента ИЛИ 18, который на следующем такте Е совпадет с 1 на прямом выходе триггера 31 и, соответственно, на втором входе элемента И-НЕ 29, пройдя через который импульс переключит триггер 30 в единичное состояние и сбросит триггер 31, что приведет к высокому уровную выходного напряжения на так- товом интервале Е и по сравнению с предыдущим тактом изменение напряжения составит +-2ill. Очередной имтроичных символов в двух разрядах из шифратора 10 символов необходим кодовый сигнал, период которого должен равняться периоду повторения троичных групп - 3Ti Формирование кодового сигнала происходит в формирователе 19 кодового сигнала.

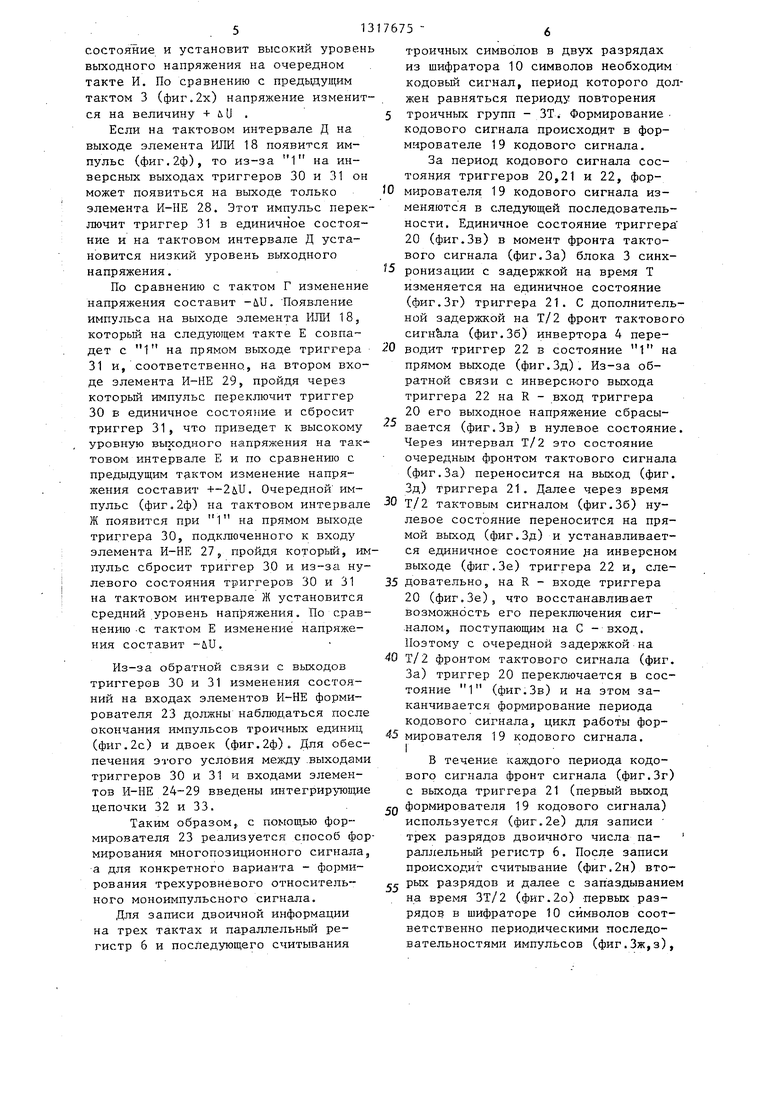

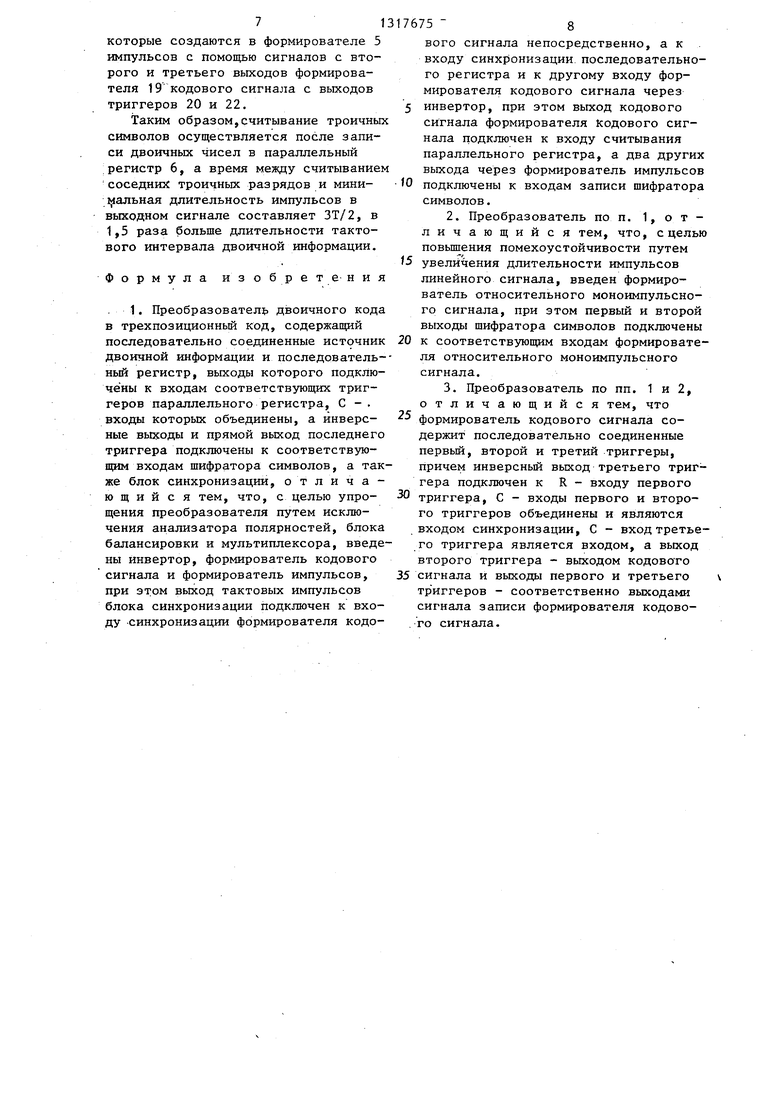

За период кодового сигнала состояния триггеров 20,21 и 22, формирователя 19 кодового сигнала изменяются в следующей последовательности. Единичное состояние триггера 20 (фиг.Зв) в момент фронта тактового сигнала (фиг.За) блока 3 синхронизации с задержкой на время Т изменяется на единичное состояние (фиг.Зг) триггера 21. С дополнительной задержкой на Т/2 фронт тактового сигнала (фиг.36) инвертора 4 переводит триггер 22 в состояние 1 на прямом выходе (фиг.Зд). Из-за обратной связи с инверсн-ого выхода триггера 22 на R - вход триггера 20 его выходное напряжение сбрасывается (фиг.Зв) в нулевое состояние. Через интервал Т/2 это состояние очередным фронтом тактового сигнала (фиг.За) переносится на выход (фиг. .д) триггера 21. Далее через время

15

20

пульс (фиг. 2ф) на тактовом интервале -30 Т/2 тактовым сигналом (фиг. 36) нуЖ появится при 1 на прямом выходелевое состояние переносится на прятриггера 30, подключенного к входумой выход (фиг.Зд) и устанавливаетэлемента И-НЕ 27, пройдя которьш, им-ся единичное состояние на инверсном пульс сбросит триггер 30 и из-за нулевого состояния триггеров 30 и 31 на тактовом интервале Ж установится

выходе (фиг.Зе) триггера 22 и, сле35 довательно, на R - входе триггера 20 (фиг.Зе), что восстанавливает возможность его переключения сигналом, поступающим на С - вход. Поэтому с очередной задержкой на

средний уровень напряжения. По сравнению -с тактом Е изменение напряжения составит -uU.

Из-за обратной связи с выходов триггеров 30 и 31 изменения состояний на входах элементов И-НЕ формирователя 23 должны наблюдаться после окончания импульсов троичных единиц (фиг.2с) и двоек (фиг.2ф). Для обеспечения этого условия между .выходами триггеров 30 и 31 и входами элементов И-НЕ 24-29 введены рштегрирующие цепочки 32 и 33.

Таким образом, с помощью формирователя 23 реализуется: способ формирования многопозиционного сигнала, а для конкретного варианта - формирования трехуровневого относительного моноимпульсного сигнала.

Для записи двоичной информации на трех тактах и параллельный регистр 6 и последующего считывания

троичных символов в двух разрядах из шифратора 10 символов необходим кодовый сигнал, период которого должен равняться периоду повторения троичных групп - 3Ti Формирование кодового сигнала происходит в формирователе 19 кодового сигнала.

За период кодового сигнала состояния триггеров 20,21 и 22, формирователя 19 кодового сигнала изменяются в следующей последовательности. Единичное состояние триггера 20 (фиг.Зв) в момент фронта тактового сигнала (фиг.За) блока 3 синхронизации с задержкой на время Т изменяется на единичное состояние (фиг.Зг) триггера 21. С дополнительной задержкой на Т/2 фронт тактового сигнала (фиг.36) инвертора 4 переводит триггер 22 в состояние 1 на прямом выходе (фиг.Зд). Из-за обратной связи с инверсн-ого выхода триггера 22 на R - вход триггера 20 его выходное напряжение сбрасывается (фиг.Зв) в нулевое состояние. Через интервал Т/2 это состояние очередным фронтом тактового сигнала (фиг.За) переносится на выход (фиг. .д) триггера 21. Далее через время

5

0

0 Т/2 тактовым сигналом (фиг. 36) нуся единичное состояние на инверсном

выходе (фиг.Зе) триггера 22 и, сле35 довательно, на R - входе триггера 20 (фиг.Зе), что восстанавливает возможность его переключения сигналом, поступающим на С - вход. Поэтому с очередной задержкой на

40 1/2 фронтом тактового сигнала (фиг. За) триггер 20 переключается в состояние 1 (фиг.Зв) и на этом заканчивается формирование периода кодового сигнала, цикл работы мирователя 19 кодового сигнала. I

В течение каждого периода кодового сигнала фронт сигнала (фиг.Зг) с выхода триггера 21 (первый выход

Q формирователя 19 кодового сигнала) используется (фиг.2е) для записи трех разрядов двоичного числа па- раллельньш регистр 6. После записи происходит считывание (фиг.2н) рых разрядов и далее с запаздывание на время ЗТ/2 (фиг.2о) -первых разрядов в шифраторе 10 символов соответственно периодическими последовательностями импульсов (фиг.3ж,з).

7

которые создаются в формирователе 5 импульсов с помощью сигналов с второго и третьего выходов формирователя 19 кодового сигнала с выходов триггеров 20 и 22.

Таким образом,считывание троичны символов осуществляется после записи двоичных чисел в параллельный регистр 6, а время между считывание соседних троичных разрядов и мини- «1альная длительность импульсов в выходном сигнале составляет ЗТ/2, в 1,5 раза больше длительности тактового интервала двоичной информации.

Формула изобретения

. 1. Преобразователь двоичного кода в трехпозиционный код, содержащий последовательно соединенные источник двоичной информации и последовательный регистр, выходы которого подключены к входам соответствующих триггеров параллельного регистра, С - . входы которых объединены, а инверсные выходы и прямой выход последнего триггера подключены к соответствующим входам шифратора символов, а также блок синхронизации, отличающийся тем, что, с целью упро- щения преобразователя путем исключения анализатора полярностей, блока балансировки и мультиплексора, введены инвертор, формирователь кодового сигнала и формирователь импульсов, при этом выход тактовых импульсов блока синхронизации подключен к входу -синхронизации формирователя кодо

8

O

5

0

вого сигнала непосредственно, а к . входу синхронизации последовательного регистра и к другому входу формирователя кодового сигнала через инвертор, при этом выход кодового сигнала формирователя Кодового сигнала подключен к входу считывания параллельного регистра, а два других выхода через формирователь импульсов подключены к входам записи шифратора символов.

2.Преобразователь по п. 1, о т - личающийся тем, что, с целью повьшгения помехоустойчивости путем

5 увеличения длительности импульсов линейного сигнала, введен формирователь относительного моноимпульсного сигнала, при этом первый и второй выходы шифратора символов подключены

0 к соответствующим входам формирователя относительного моноимпульсного сигнала.

3.Преобразователь по пп. 1 и 2, отличающийся тем, что формирователь кодового сигнала содержит последовательно соединенные первый, второй и третий триггеры, причем инверсньм выход третьего триггера подключен к R - входу первого триггера, С - входы первого и второго триггеров объединены и являются входом синхронизации, С - вход третьего триггера является входом, а выход второго триггера - выходом кодового

5 сигнала и выходы первого и третьего триггеров - соответственно выходами сигнала записи формирователя кодово- . го сигнала.

Редактор К.Волощук

Фи2.3

Составитель В.Евдокимова

Техред В.Кадар Корректор в. Бутяга

Заказ 2437/56 Тираж 638 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в трехпозиционный код | 1985 |

|

SU1368996A1 |

| Преобразователь двоичного кода в трехпозиционный код | 1989 |

|

SU1633499A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 1990 |

|

RU2022453C1 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| Преобразователь последовательного кода в параллельный | 1989 |

|

SU1795557A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Устройство для передачи и приема цифровых сигналов | 1988 |

|

SU1566499A1 |

Изобретение относится к электросвязи. Цель изобретения - упрощение преобразователя и повышение его помехоустойчивости . Преобразователь содержит источник 1 двоичной информации, послеДОНательньш регистр 2, блок 3 синхронизации, инвертор 4, формирователь 5 импульсов, параллельный регистр 6, состоящий из триггеров 7,8 и 9, шифратор 10 символов, состоящий из э-тов И-НЕ 11-16 и эл-тов РШИ 17 и 18, формирователь 19 кодового сигнала, состоящий из триггеров 20,21 и 22, формирователь 23 относительного моноимпульсного сигнала, состоящий из эл-тов И-НЕ 24-29, триггеров 30-31 и интегрирующих цепей 32.и 33. Такое выполнение преобразователя позволяет исключить его из состава анализатор полярности, блок балансировки и мультиплексор, что приводит к упрощению преобразователя. Повышение помехоустойчивости достигается путем увеличения длительности импульсов линейного сигнала с помощью введенного формирователя 23. Преобразователь отличается выполнением формирователя 19. 2 з.п. ф-лы, 3 ил. S (Л 2: со О5 сл

| Лев А.Ю | |||

| и др | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| - Радиотехника, 1984, № 4. | |||

Авторы

Даты

1987-06-15—Публикация

1984-02-27—Подача