Изобретение относится к технике связи, в частности к устройствам восстановления цифрового сигнала.

Цель изобретения - повьшение помехоустойчивости регенератора.

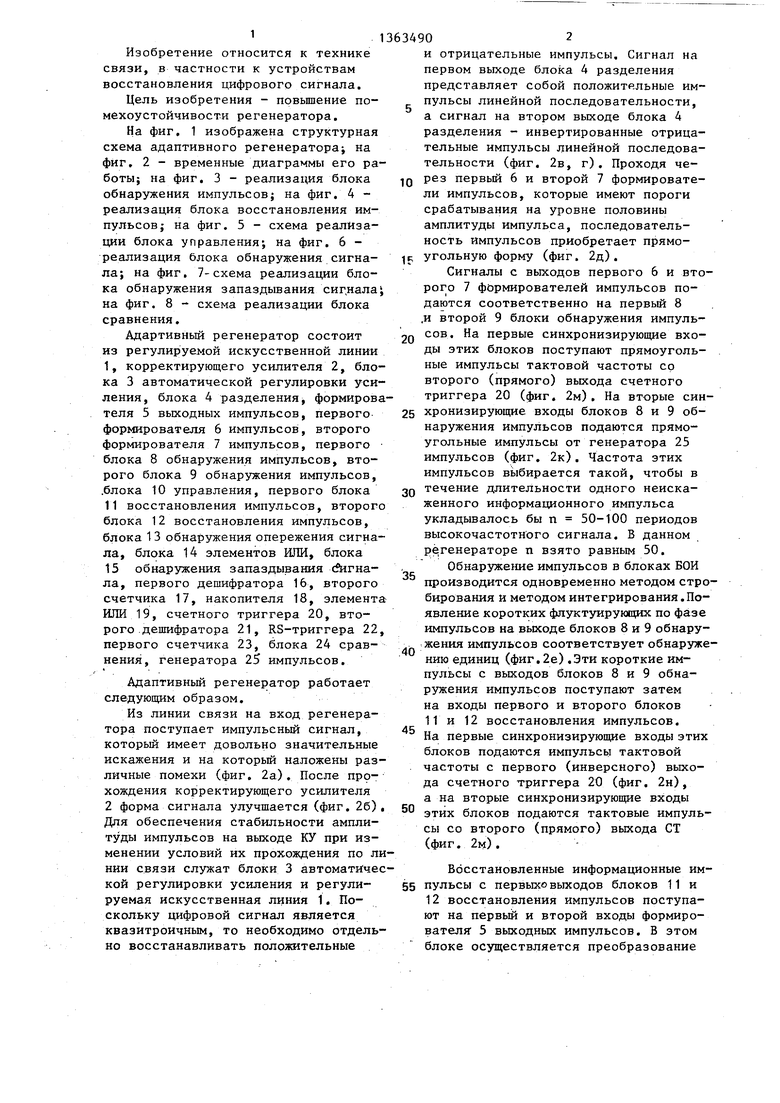

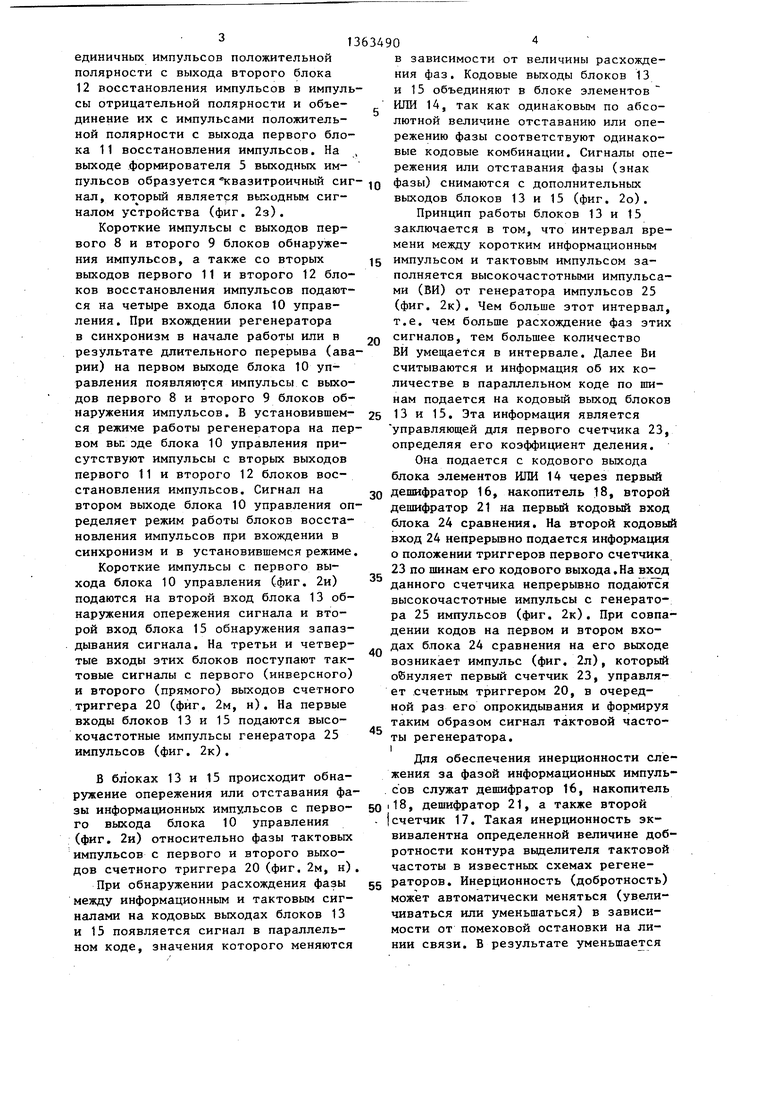

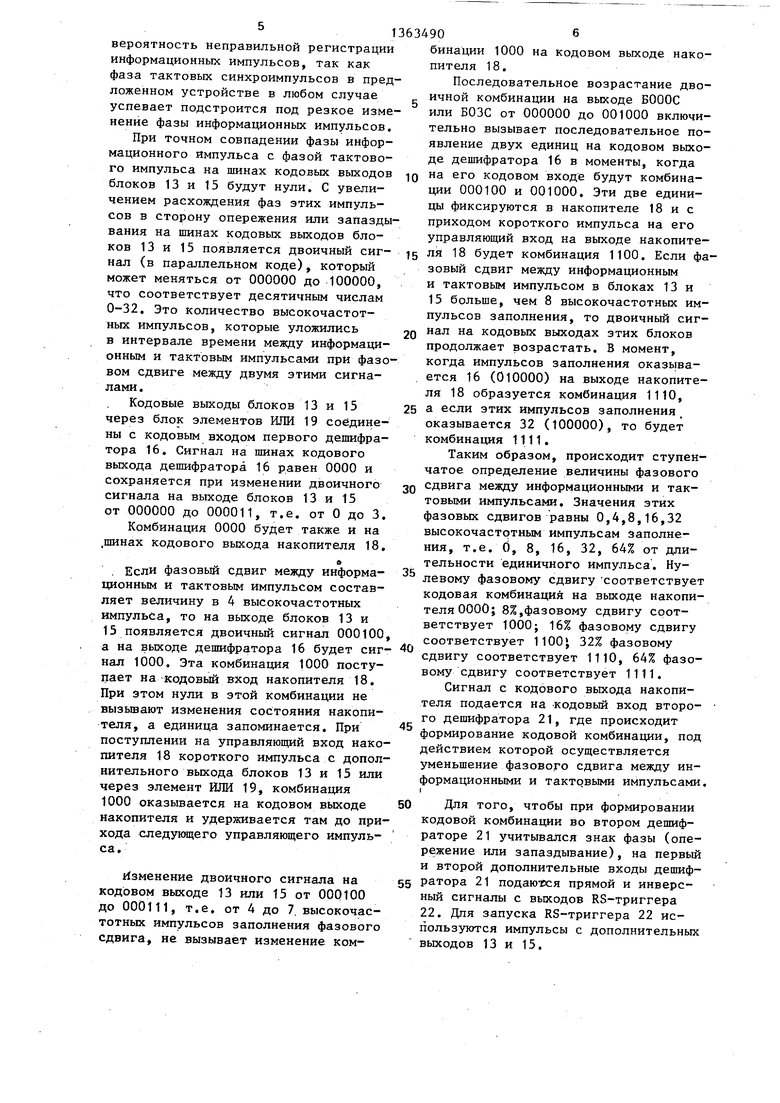

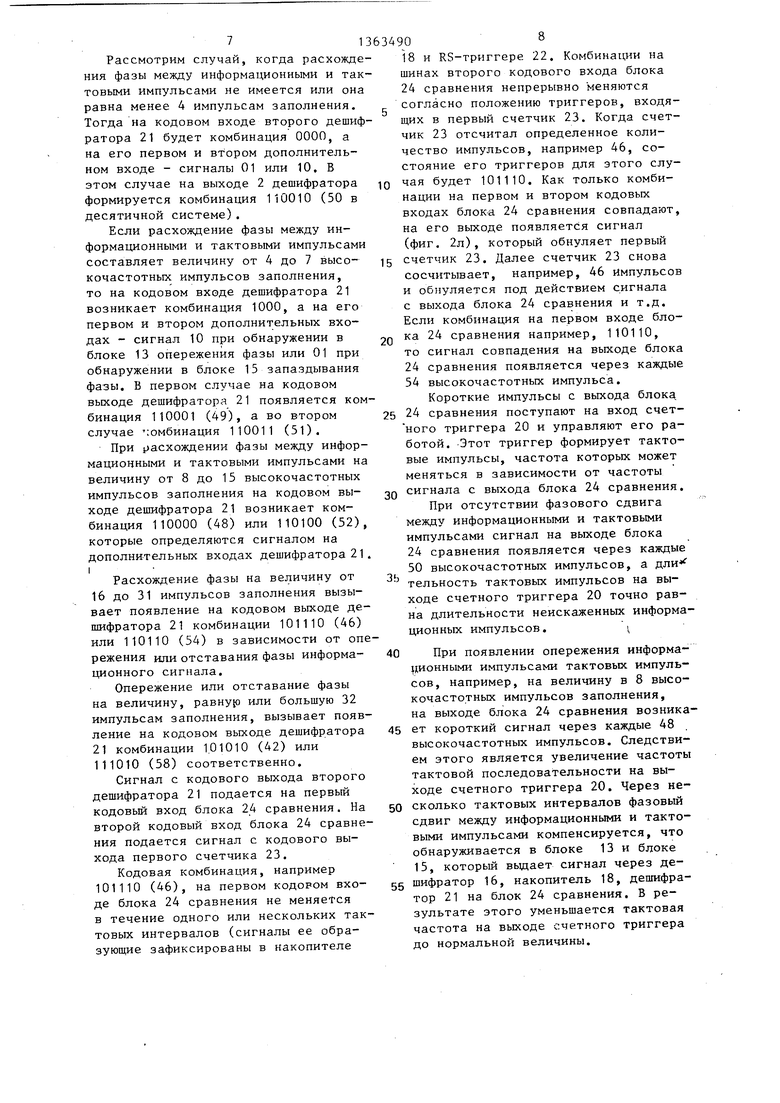

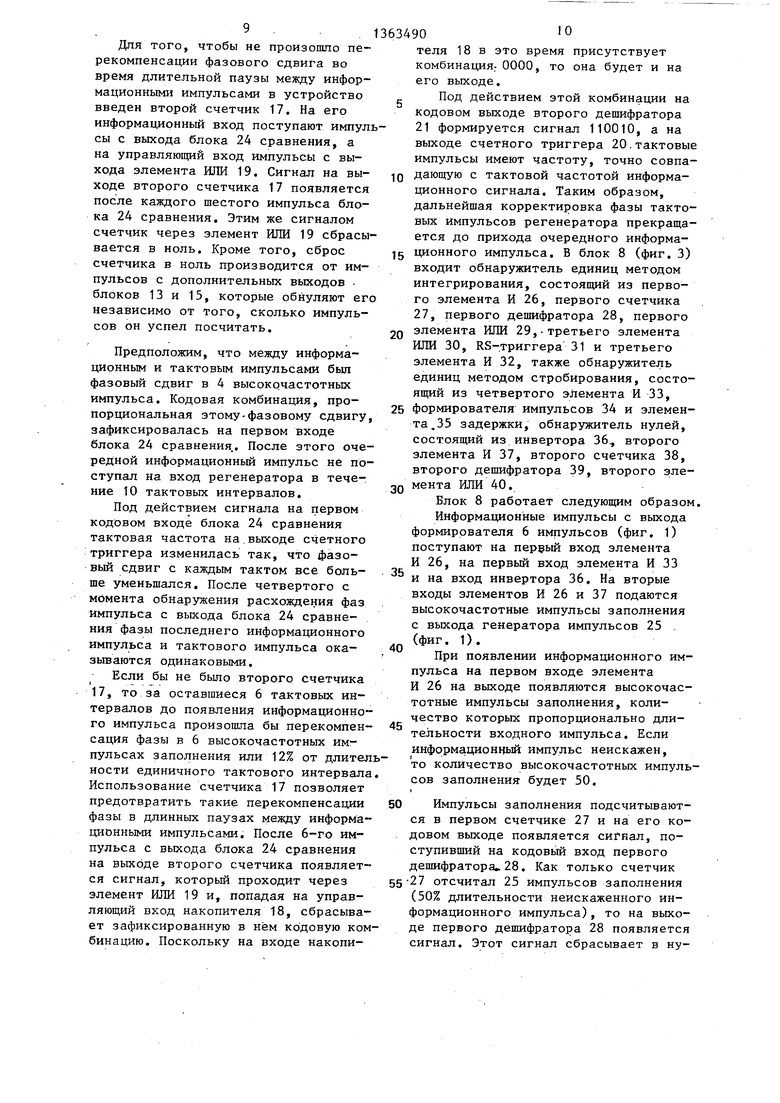

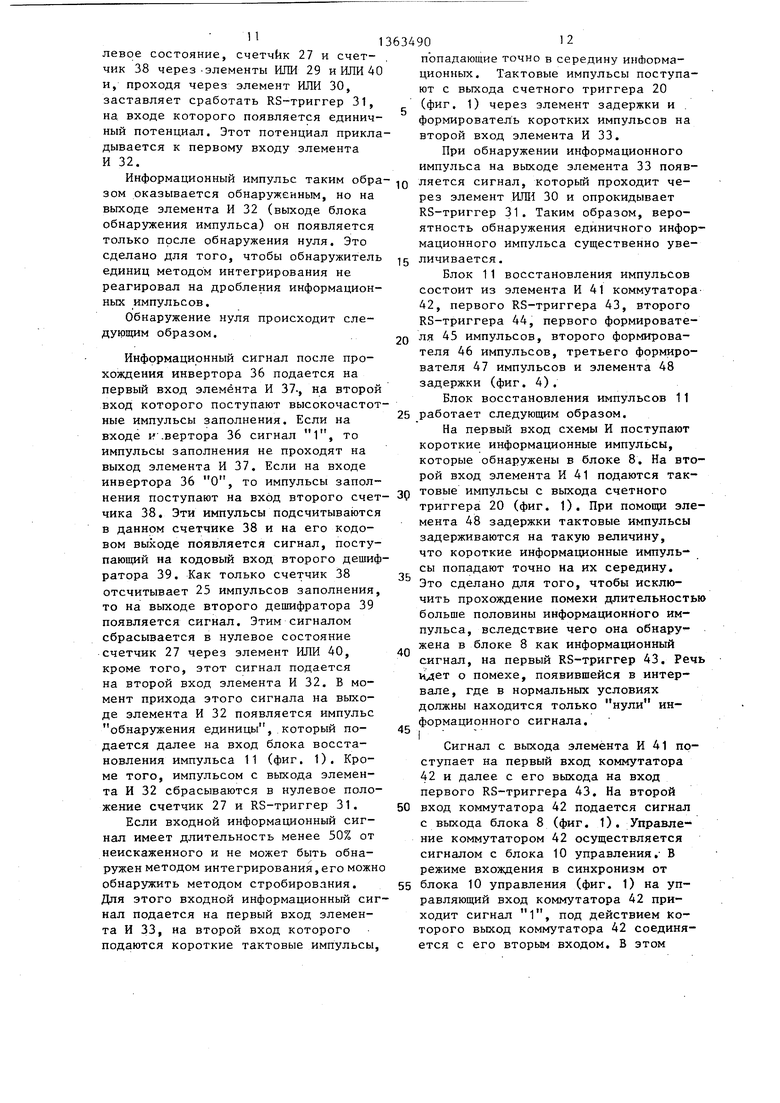

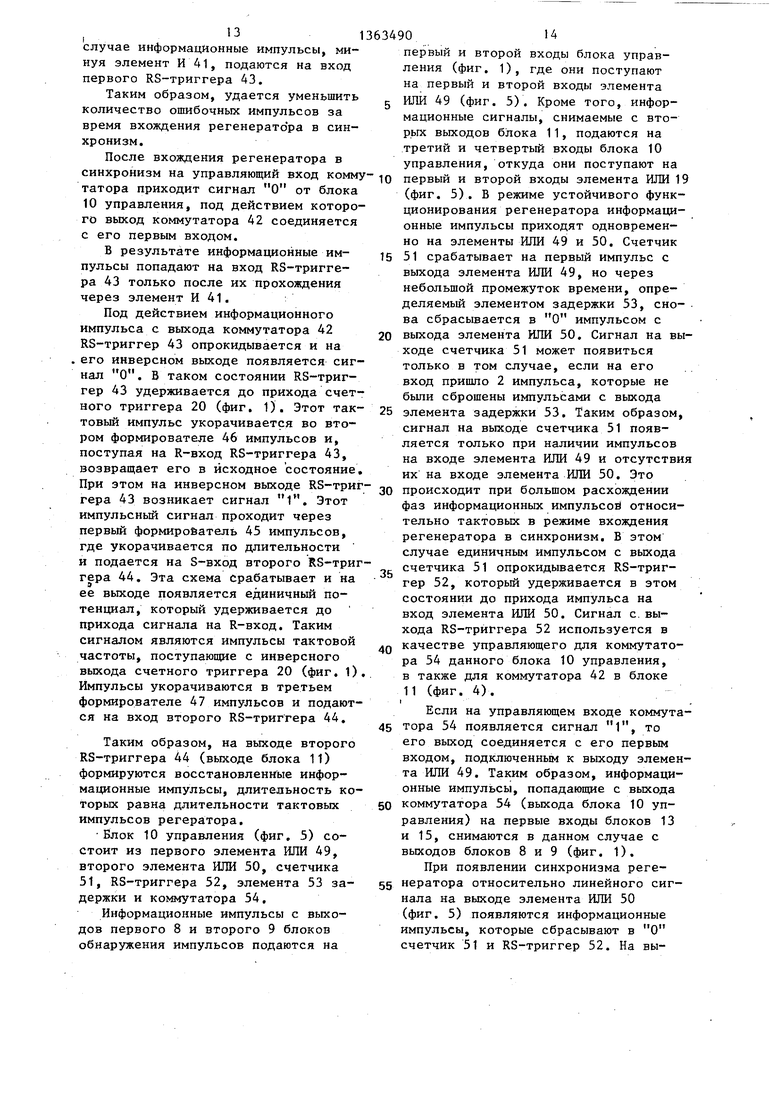

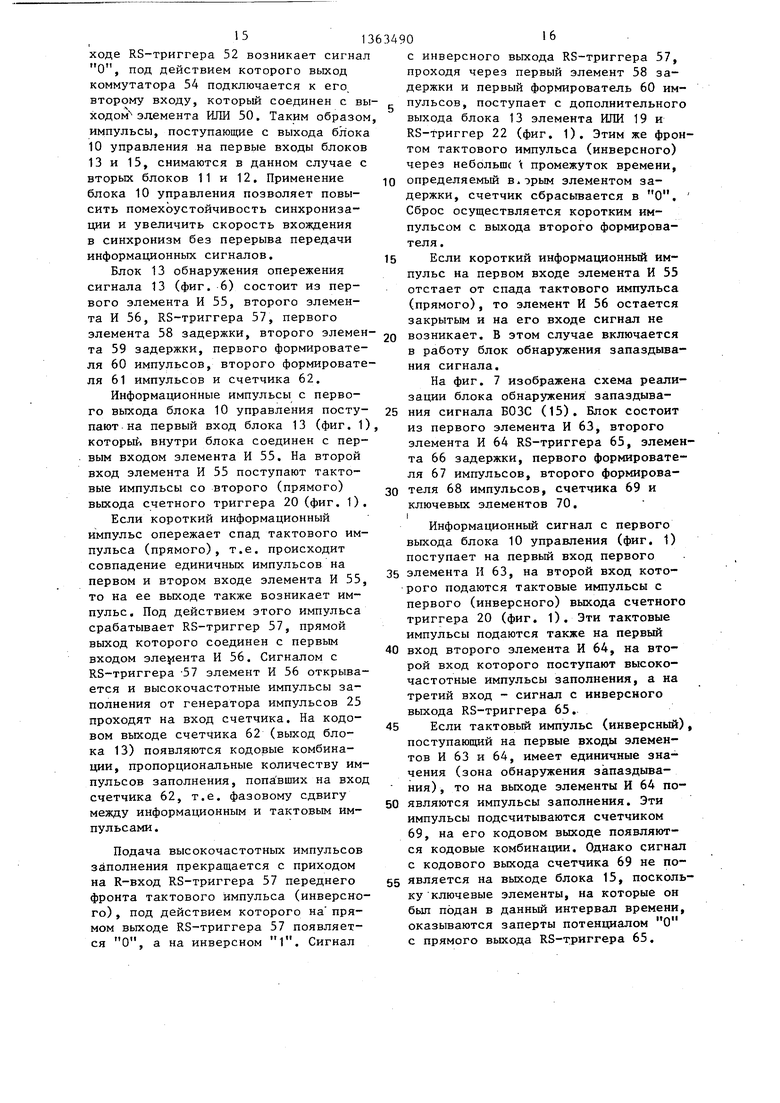

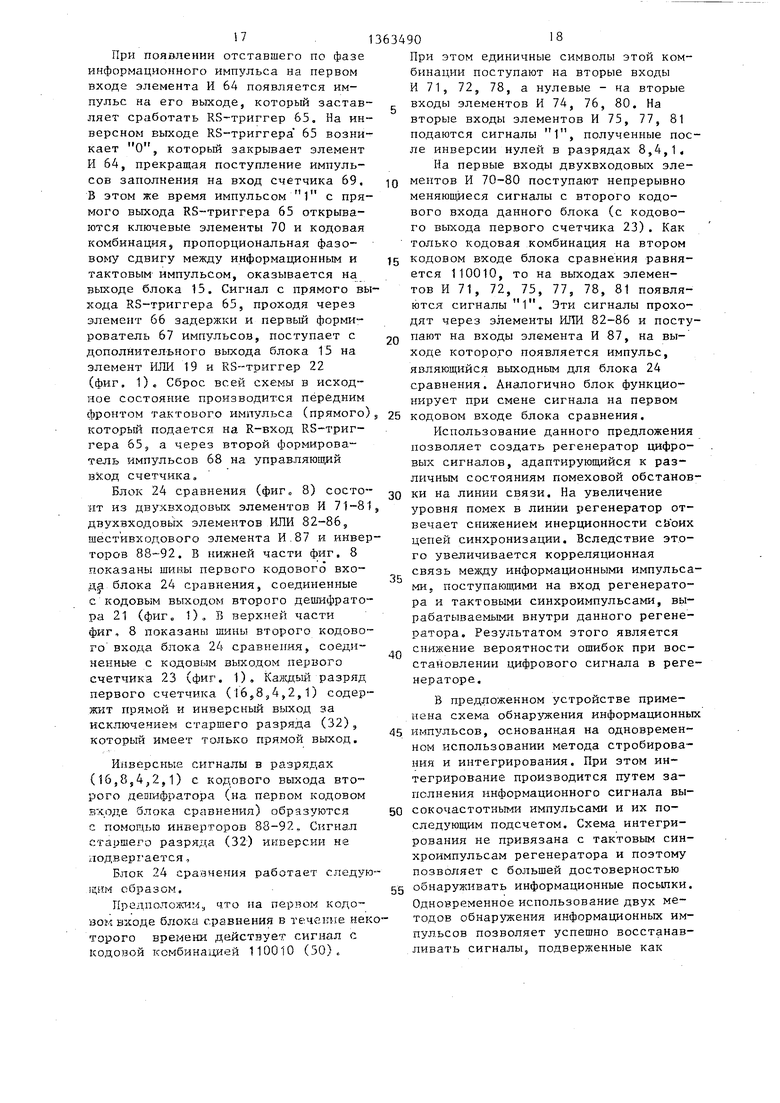

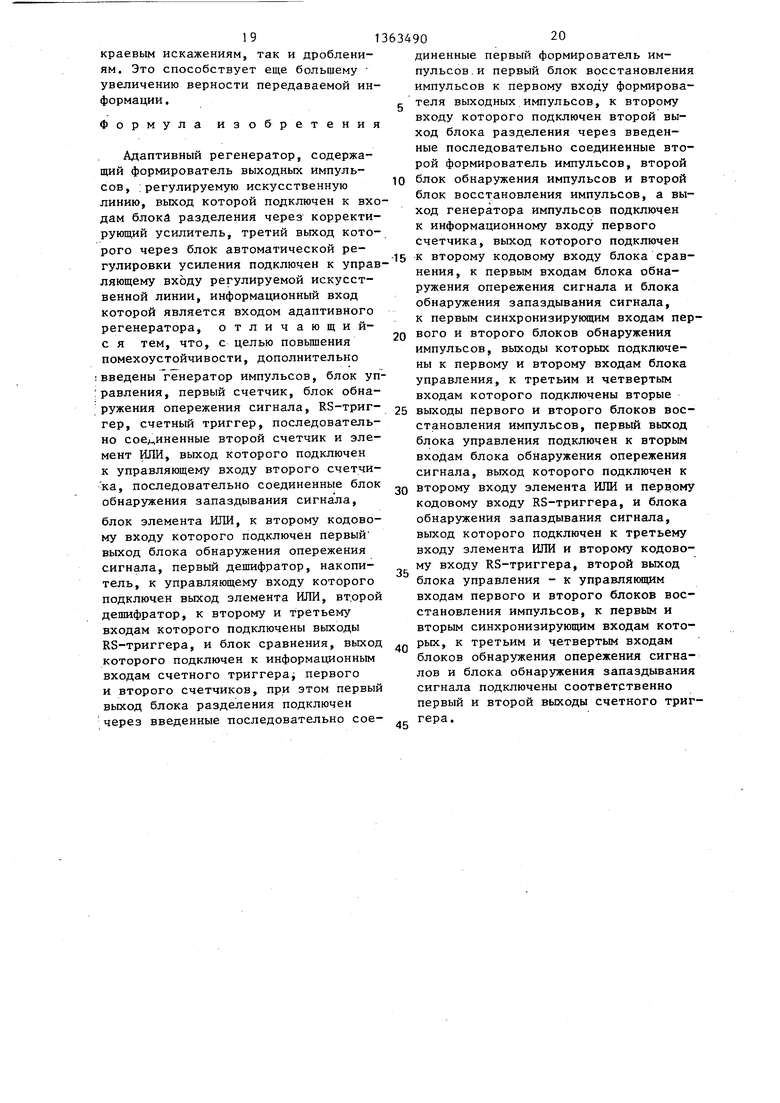

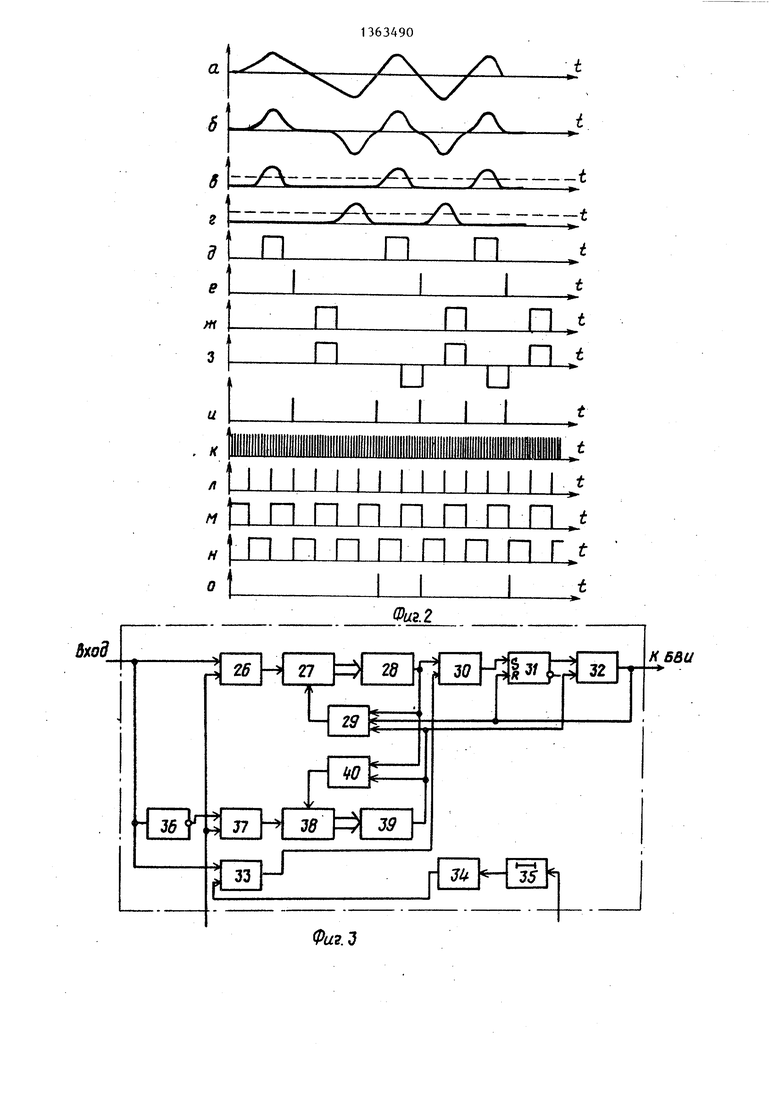

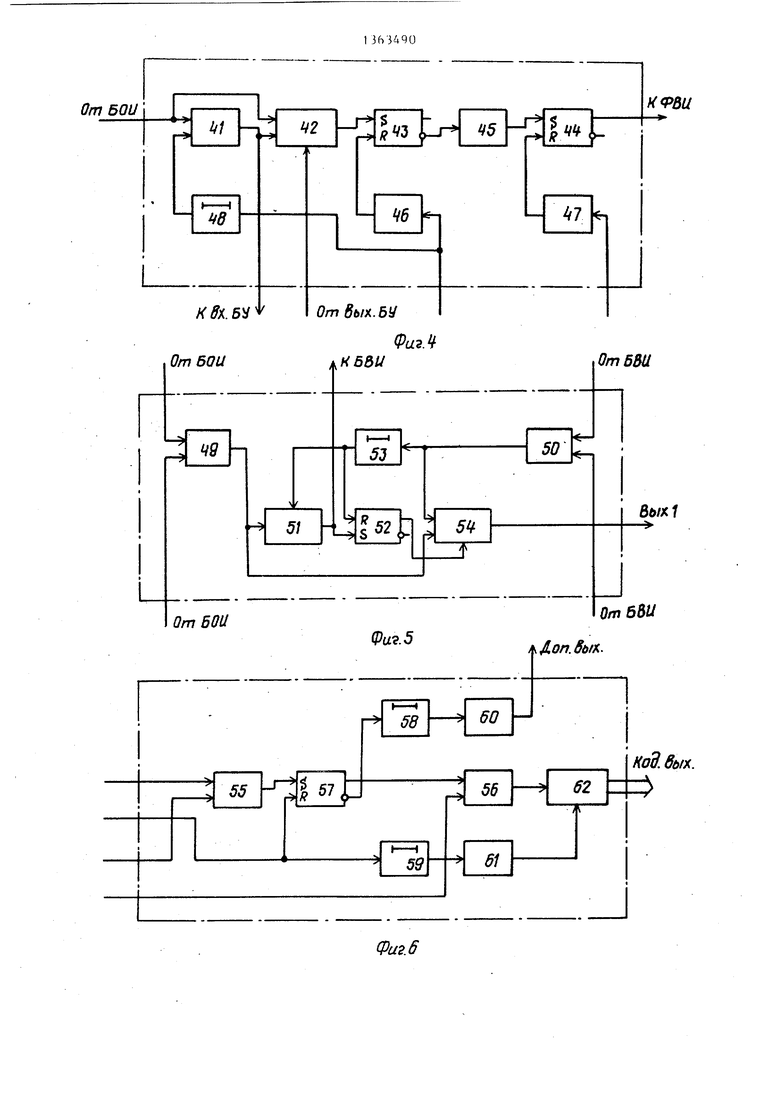

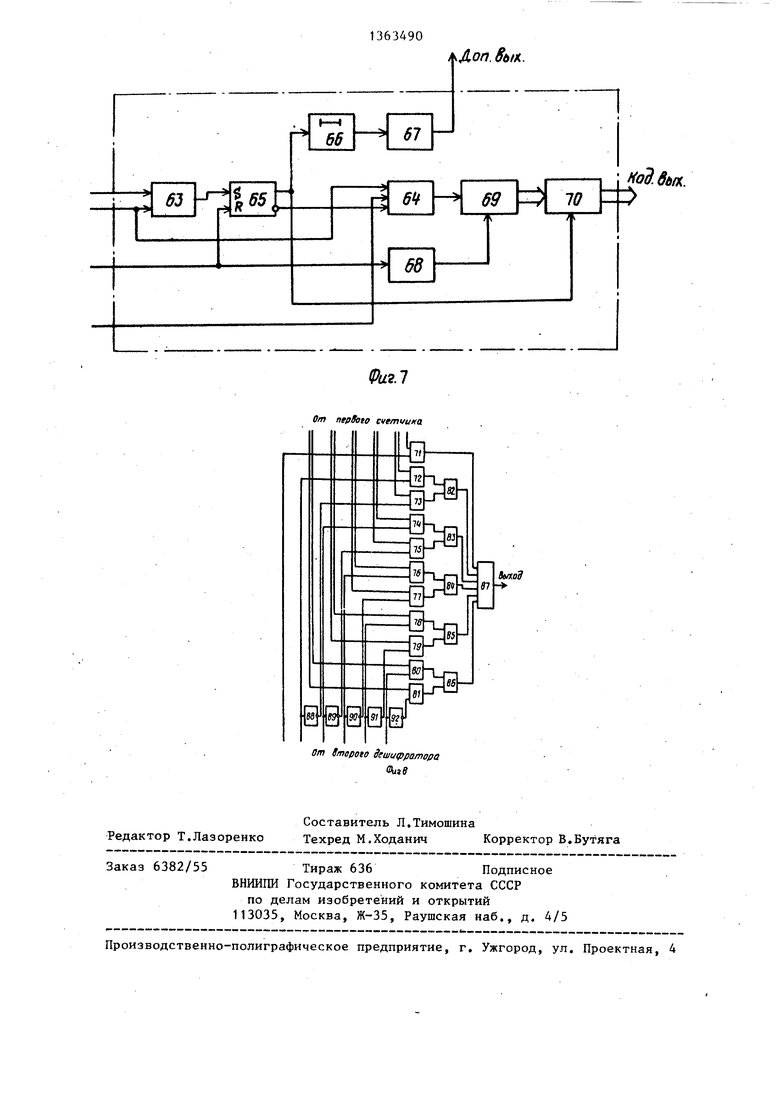

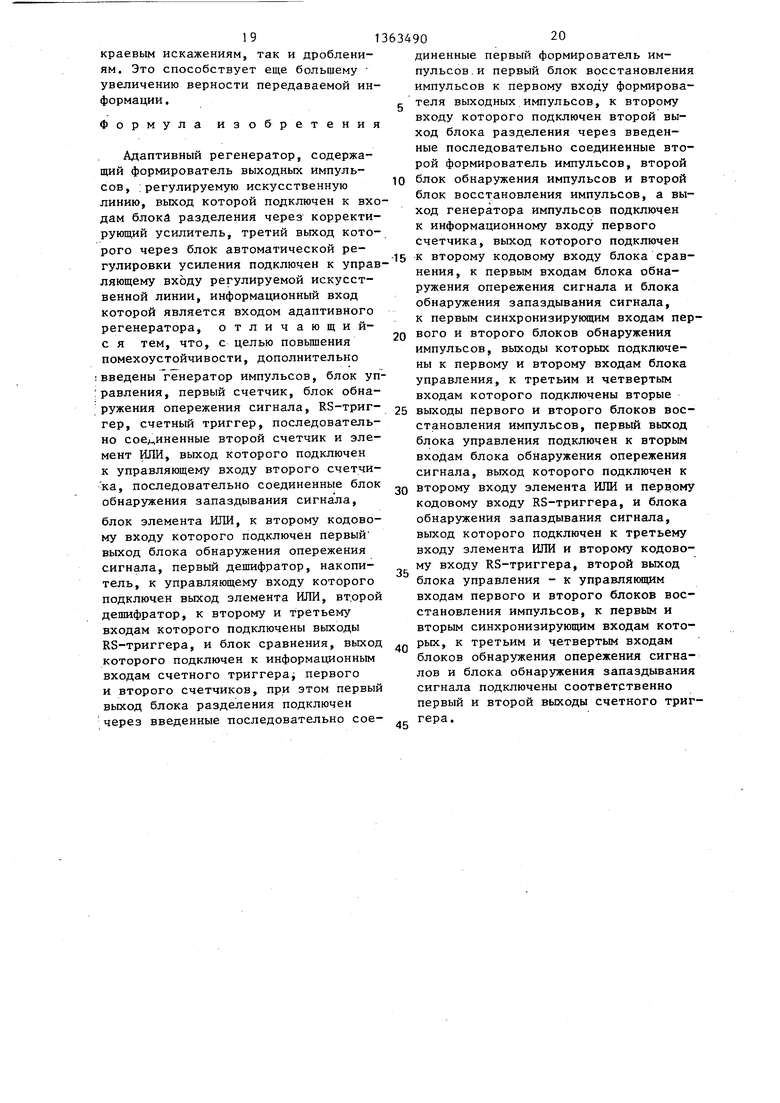

На фиг, 1 изображена структурная схема адаптивного регенератораj на фИг, 2 - временные диаграммы его работы; на фиг, 3 - реализация блока обнаружения импульсов; на фиг, 4 - реализация блока восстановления импульсов; на фиг. 5 - схема реализации блока управления; на фиг, 6 - реализация блока обнаружения сигнала; на фиг, 7-схема реализации блока обнаружения запаздывания сигнала на фиг. 8 - схема реализации блока сравнения,

Адартивный регенератор состоит из регулируемой искусственной линии 1, корректирующего усилителя 2, блока 3 автоматической регулировки усиления, блока 4 разделения, формирователя 5 выходных импульсов, первого- формирователя 6 импульсов, второго формирователя 7 импульсов, первого блока 8 обнаружения импульсов, второго блока 9 обнаружения импульсов, .блока 10 управления, первого блока 11 восстановления импульсов, второго блока 12 восстановления импульсов, блока 13 обнаружения опережения сигнала, блока 14 элементов ИЛИ, блока 15 ла

счетчика 17, накопителя 18, элемента ИЛИ 19, счетного триггера 20, второго .дешифратора 21, RS-триггера 22, первого счетчика 23, блока 24 сравнения, генератора 25 импульсов.

Адаптивный регенератор работает следующим образом.

Из линии связи на вход регенератора поступает импульсный сигнал, который имеет довольно значительные искажения и на который наложены различные помехи (фиг, 2а), После прохождения корректирующего усилителя 2 форма сигнала улучшается (фиг, 26) Для обеспечения стабильности амплитуды импульсов на выходе КУ при изменении условий их прохождения по линии связи служат блоки 3 автоматической регулировки усиления и регулируемая искусственная линия 1, Поскольку цифровой сигнал является квазитроичным, то необходимо отдельно восстанавливать положительные

обнаружения запаздывания йигна- I, первого дешифратора 16, второго

0

0

и отрицательные импульсы. Сигнал на первом выходе блока 4 разделения представляет собой положительные импульсы линейной последовательности, а сигнал на втором выходе блока 4 разделения - инвертированные отрицательные импульсы линейной последовательности (фиг, 2в, г). Проходя через первый 6 и второй 7 формирователи импульсов, которые имеют пороги срабатывания на уровне половины амплитуды импульса, последовательность Импульсов приобретает прямор угольную форму (фиг, 2д),

Сигналы с выходов первого 6 и второго 7 формирователей импульсов подаются соответственно на первый 8 ,и второй 9 блоки обнаружения импульсов. На первые синхронизируюпще входы этих блоков поступают прямоугольные импульсы тактовой частоты со второго (прямого) выхода счетного триггера 20 (фиг, 2м), На вторые син5 хронизирующие входы блоков 8 и 9 обнаружения импульсов подаются прямоугольные импульсы от генератора 25 импульсов (фиг, 2к), Частота зтих импульсов выбирается такой, чтобы в течение длительности одного неискаженного информационного импульса укладывалось бы п 50-100 периодов высокочастотного сигнала, В данном регенераторе п взято равным 50,

Обнаружение импульсов в блоках БОИ производится одновременно методом стро- бирования и методом интегрирования,Появление коротк:их флуктуирующих по фазе импульсов на выходе блоков 8 и 9 обнаружения импульсов соответствует обнаружению единиц (фиг, 2е) ,Эти короткие импульсы с выходов блоков 8 и 9 обнаружения импульсов поступают затем на входы первого и второго блоков

11и 12 восстановления импульсов.

На первые синхронизирующие входы этих блоков подаются импульсы тактовой частоты с первого (инверсного) выхода счетного триггера 20 (фиг, 2н), а на вторые синхронизирующие входы этих блоков подаются тактовые импульсы со второго (прямого) выхода СТ (фиг, 2м),

Восстановленные информационные им- 5 пульсы с первыховыходов блоков 11 и

12восстановления импульсов поступают на первый и второй входы формирователя 5 выходных импульсов, В этом блоке осуществляется преобразование

5

0

5

0

ничных импульсов положительной ярности с выхода второго блока восстановления импульсов в импульотрицательной полярности и объеение их с импульсами положительполярности с выхода первого бло11 восстановления импульсов. На оде формирователя 5 выходных имьсов образуется квазитроичный фазы) снимаются с , который является выходным сигв зависимости от ния фаз. Кодовые и 15 объединяют в ИЛИ 14, так как о лютной величине о режению фазы соот вые кодовые комби режения или отста

выходов блоков 13 Принцип работы заключается в том мени между коротк импульсом и такто полняется высокоч ми (ВИ) от генера (фиг. 2к). Чем бол т.е. чем больше ра сигналов, тем бол ВИ умещается в инт считываются и инфо личестве в паралле нам подается на ко 13 и 15, Эта инфор управляющей для пе определяя его коэф Она подается с блока элементов ИЛ дешифратор 16, нак дешифратор 21 на п блока 24 сравнения вход 24 непрерьшно о положении триггер 23 по вшнам его кодо данного счетчика н высокочастотные им ра 25 импульсов (ф дении кодов на пер дах блока 24 сравн возникает импульс обнуляет первый сч ет счетным триггер ной раз его опроки таким образом сигн ты регенератора.

20

25

30

налом устройства (фиг, 2з),

Короткие импульсы с выходов первого 8 и второго 9 блоков обнаружения импульсов, а также со вторых g выходов первого 11 и второго 12 блоков восстановления импульсов подаются на четыре входа блока 10 управления , При вхождении регенератора в синхронизм в начале работы или в результате длительного перерыва (аварии) на первом выходе блока 10 управления появляются импульсы с выходов первого 8 и второго 9 блоков обнаружения импульсов, В установившемся режиме работы регенератора на первом вьп эде блока 10 управления присутствуют импульсы с вторьк выходов первого 11 и второго 12 блоков восстановления импульсов. Сигнал на втором выходе блока 10 управления определяет режим работы блоков восстановления импульсов при вхождении в синхронизм и в установившемся режиме.

Короткие импульсы с первого выхода блока 10 управления (фиг. 2и) подаются на второй вход блока 13 обнаружения опережения сигнала и второй вход блока 15 обнаружения запаз- дывания сигнала. На третьи и четвертые входы этих блоков поступают тактовые сигналы с первого (инверсного) и второго (прямого) выходов счетного триггера 20 (фиг. 2м, н), На первые входы блоков 13 и 15 подаются высокочастотные импульсы генератора 25 импульсов (фиг. 2к),

В блоках 13 и 15 происходит обнаружение опережения или отставания фазы информационных импульсов с перво- 50 го выхода блока 10 управления (фиг. 2и) относительно фазы тактовых импульсов с первого и второго выходов счетного триггера 20 (фиг. 2м, н) .

При обнаружении расхождения фазы 55 между информационным и тактовым сигналами на кодовых выходах блоков 13 и 15 появляется сигнал в параллельном коде, значения которого меняются

36

40

45

фазы) снимаются с

20

25

30

g

50.

55

634904

в зависимости от величины расхождения фаз. Кодовые выходы блоков 13 и 15 объединяют в блоке элементов ИЛИ 14, так как одинаковым по абсолютной величине отставанию или опережению фазы соответствуют одинаковые кодовые комбинации. Сигналы опережения или отставания фазы (знак

дополнительных

выходов блоков 13 и 15 (фиг. 2о). Принцип работы блоков 13 и 15 заключается в том, что интервал времени между коротким информационным импульсом и тактовым импульсом заполняется высокочастотными импульсами (ВИ) от генератора импульсов 25 (фиг. 2к). Чем больше этот интервал, т.е. чем больше расхождение фаз этих сигналов, тем большее количество ВИ умещается в интервале. Далее Ви считываются и информация об их количестве в параллельном коде по шинам подается на кодовый выход блоков 13 и 15, Эта информация является управляющей для первого счетчика 23, определяя его коэффициент деления. Она подается с кодового выхода блока элементов ИЛИ 14 через первый дешифратор 16, накопитель 18, второй дешифратор 21 на первый кодовый вход блока 24 сравнения. На второй кодовый вход 24 непрерьшно подается информация о положении триггеров первого счетчика 23 по вшнам его кодового выхода.На вход данного счетчика непрерьшно подаются высокочастотные импульсы с генератора 25 импульсов (фиг. 2к), При совпадении кодов на первом и втором входах блока 24 сравнения на его выходе возникает импульс (фиг. 2л), который обнуляет первый счетчик 23, управляет счетным триггером 20, в очередной раз его опрокидывания и формируя таким образом сигнал тактовой частоты регенератора.

36

40

45

1

Для обеспечения инерционности слежения за фазой информационных импульсов служат дешифратор 16, накопитель I18, дешифратор 21, а также второй Iсчетчик 17. Такая инерционность эквивалентна определенной величине добротности контура выделителя тактовой частоты в известных схемах регенераторов. Инерционность (добротность) может автоматически меняться (увеличиваться или уменьшаться) в зависимости от помеховой остановки на линии связи. В результате уменьшается

вероятность неправильной регистрации информационных импульсов, так как фаза тактовых синхроимпульсов в предложенном устройстве в любом случае успевает подстроится под резкое изменение фазы информационных импульсов.

При точном совпадении фазы информационного импульса с фазой тактового импульса на шинах кодовых выходов блоков 13 и 15 будут нули. С увеличением расхождения фаз этих импульсов в сторону опережения или запаздывания на шинах кодовых выходов блоков 13 и 15 появляется двоичный сиг нал (в параллельном коде), который может меняться от 000000 до 100000, что соответствует десятичным числам 0-32. Это количество высокочастотных импульсов, которые уложились в интервале времени между информационным и тактовым импульсами при фазовом сдвиге между двумя этими сигналами.

Кодовые выходы блоков 13 и 15 через блок элементов ИЛИ 19 соединены с кодовым входом первого дешифратора 16. Сигнал на шинах кодового выхода дешифратора 16 равен 0000 и сохраняется при изменении двоичного сигнала на выходе блоков 13 и 15 от 000000 до 000011, т.е. от О до 3.

Комбинация 0000 будет также и на .шинах кодового выхода накопителя 18.

Если фазовый сдвиг между информа-

ционным и тактовым импульсом составляет величину в 4 высокочастотных импульса, то на выходе блоков 13 и 15 появляется двоичньй сигнал 000100 а на выходе дешифратора 16 будет сиг нал 1000. Эта комбинация 1000 поступает на кодовый вход накопителя 18. При этом нули в этой комбинации не вызьшают изменения состояния накопителя, а единица запоминается. При поступлении на управляющий вход накопителя 18 короткого импульса с дополнительного выхода блоков 13 и 15 или через элемент ИЛИ 19, комбинация 1000 оказывается на кодовом выходе накопителя и удерживается там до прихода следующего управляющего импульса.

изменение двоичного сигнала на кодовом выходе 13 или 15 от 000100 до 000111, т.е. от 4 до 7. высокочастотных импульсов заполнения фазового сдвига, не вызывает изменение ком5

п

5 Q

5

0 5 0

5

бинации 1000 на кодовом выходе накопителя 18.

Последовательное возрастание двоичной комбинации на выходе БОООС или БОЗС от 000000 до 001000 включительно вызывает последовательное появление двух единиц на кодовом вьжо- де дешифратора 16 в моменты, когда на его кодовом входе будут комбинации 000100 и 001000. Эти две единицы фиксируются в накопителе 18 и с приходом короткого импульса на его управляющий вход на выходе накопителя 18 будет комбинация 1100. Если фазовый сдвиг между информационным и тактовым импульсом в блоках 13 и 15 больше, чем 8 высокочастотных импульсов заполнения, то двоичный сигнал на кодовых выходах этих блоков продолжает возрастать. В момент, когда импульсов заполнения оказывается 16 (010000) на выходе накопителя 18 образуется комбинация 1110, а если этих импульсов заполнения оказывается 32 (100000), то будет комбинация 1111.

Таким образом, происходит ступенчатое определение величины фазового сдвига между информационными и тактовыми импульсами. Значения этих фазовых сдвигов равны 0,4,8,16,32 высокочастотным импульсам заполнения, т.е. О, 8, 16, 32, 64% от длительности единичного импульса. Нулевому фазовому сдвигу соответствует кодовая комбинация на выходе накопителя 0000; 8%,фазовому сдвигу соответствует 1000; 16% фазовому сдвигу соответствует 1100J 32% фазовому сдвигу соответствует 1110, 64% фазовому сдвигу соответствует 1111.

Сигнал с кодового выхода накопителя подается на «одовый вход второ- го дешифратора 21, где происходит формирование кодовой комбинации, под действием которой осуществляется уменьшение фазового сдвига между информационными и тактовыми импульсами, I

Для того, чтобы при формировании кодовой комбинации во втором дешифраторе 21 учитывался знак фазы (опережение или запаздывание), на первый и второй дополнительные входы дешифратора 21 подаю-вся прямой и инверс- ньй сигналы с выходов RS-триггера 22. Для запуска RS-триггера 22 используются импульсы с дополнительных выходов 13 и 15.

71

Рассмотрим случай, когда расхождения фазы между информационными и тактовыми импульсами не имеется или она равна менее 4 импульсам заполнения. Тогда на кодовом входе второго дешифратора 21 будет комбинация 0000, а на его первом и втором дополнительном входе - сигналы 01 или 10, В этом случае на выходе 2 дешифратора формируется комбинация 110010 (50 в десятичной системе).

Если расхождение фазы между информационными и тактовыми импульсами составляет величину от 4 до 7 высокочастотных импульсов заполнения, то на кодовом входе дешифратора 21 возникает комбинация 1000, а на его первом и втором дополнительных входах - сигнал 10 при обнаружении в блоке 13 опережения фазы или 01 при обнаружении в блоке 15 запаздывания фазы. В первом случае на кодовом выходе дешифратора 21 появляется комбинация 110001 (49), а во втором случае :омбинация 110011 (51).

При 4 асхождении фазы между информационными и тактовыми импульсами на величину от 8 до 15 высокочастотных импульсов заполнения на кодовом выходе дешифратора 21 возникает комбинация 110000 (48) или 110100 (52), которые определяются сигналом на

дополнительных входах дешифратора 21. I

Расхождение фазы на величину от

16 до 31 импульсов заполнения вызывает появление на кодовом выходе дешифратора 21 комбинации 101110 (46) или 110110 (54) в зависимости от опережения или отставания фазы информационного сигнала.

Опережение или отставание фазы на величину, равнур или большую 32 импульсам заполнения, вызывает появление на кодовом выходе дешифратора 21 комбинации 101010 (42) или 111010 (58) соответственно.

Сигнал с кодового выхода второго дешифратора 21 подается на первый кодовый вход блока 24 сравнения. На второй кодовый вход блока 24 сравнения подается сигнал с кодового выхода первого счетчика 23.

Кодовая комбинация, например 101110 (46), на первом кодовом входе блока 24 сравнения не меняется в течение одного или нескольких тактовых интервалов (сигналы ее образующие зафиксированы в накопителе

634908

18 и RS-триггере 22. Комбинации на шинах второго кодового входа блока 24 сравнения непрерывно меняются согласно положению триггеров, входящих в первый счетчик 23. Когда счетчик 23 отсчитал определенное количество импульсов, например 46, состояние его триггеров для этого слу1Q чая будет 101110. Как только комбинации на первом и втором кодовых входах блока 24 сравнения совпадают, на его выходе появляется сигнал (фиг. 2л), который обнуляет первый

15 счетчик 23. Далее счетчик 23 снова сосчитывает, например, 46 Импульсов и обнуляется под действием сигнала с выхода блока 24 сравнения и т.д. Если комбинация на первом входе бло2Q ка 24 сравнения например, 110110, то сигнал совпадения на выходе блока 24 сравнения появляется через каждые 54 высокочастотных импульса.

Короткие импульсы с выхода блока.

25 24 сравнения поступают на вход счет- ного триггера 20 и управляют его работой. Этот триггер формирует тактовые импульсы, частота которых может меняться в зависимости от частоты

2Q сигнала с выхода блока 24 сравнения.

При отсутствии фазового сдвига между информационньтш и тактовыми импульсами сигнал на выходе блока 24 сравнения появляется через каждые

50 высокочастотных импульсов, а

Чь

тельность тактовых импульсов на выходе счетного триггера 20 точно равна длительности неискаженных информационных импульсов. 1,

40 При появлении опережения информационными импульсами тактовых импульсов, например, на величину в 8 высокочастотных импульсов заполнения, на выходе блока 24 сравнения возника45 ет короткий сигнал через каждые 48 высокочастотных импульсов. Следствием этого является увеличение частоты тактовой последовательности на выходе счетного триггера 20. Через не50 сколько тактовых интервалов фазовый сдвиг между информационными и тактовыми импульсами компенсируется, что обнаруживается в блоке 13 и блоке 15, который вьодает сигнал через де55 шифратор 16, накопитель 18, дешифратор 21 на блок 24 сравнения. В результате этого уменьшается тактовая частота на выходе счетного триггера до нормальной величины.

Для того, чтобы не произошло перекомпенсации фазового сдвига во время длительной паузы между информационными импульсами в устройство введен второй счетчик 17. На его информационный вход поступают импульсы с выхода блока 24 сравнения, а на управляющий вход импульсы с выхода элемента ИЛИ 19. Сигнал на выходе второго счетчика 17 появляется после каждого шестого импульса блока 24 сравнения. Этим же сигналом счетчик через элемент ИЛИ 19 сбрасывается в ноль. Кроме того, сброс счетчика в ноль производится от импульсов с дополнительных выходов . блоков 13 и 15, которые обнуляют его независимо от того, сколько импульсов он успел посчитать.

Предположим, что между информационным и тактовым импульсами был фазовый сдвиг в 4 высокочастотных импульса. Кодовая комбинация, пропорциональная этому-фазовому сдвигу, зафиксировалась на первом входе блока 24 сравнения.. После этого очередной информационный импульс не поступал на вход регенератора в течение 10 тактовых интервалов.

Под действием сигнала на первом кодовом входе блока 24 сравнения тактовая частота на.выходе счетного триггера изменилась так, что фазо- вьй сдвиг с каждым тактом все больше уменьшался. После четвертого с момента обнаружения расхождения фаз импульса с выхода блока 24 сравнения фазы последнего информационного импульса и тактового импульса оказываются одинаковыми.

Если бы не было второго счетчика 17, то за оставшиеся 6 тактовых интервалов до появления информационного импульса произошла бы перекомпенсация фазы в 6 высокочастотных импульсах заполнения или 12% от длителности единичного тактового интервала Использование счетчика 17 позволяет предотвратить такие перекомпенсации фазы в длинных паузах между информационными импульсами. После 6-го импульса с выхода блока 24 сравнения на вькоде второго счетчика появляется сигнал, который проходит через элемент ИЛИ 19 и, попадая на управляющий вход накопителя 18, сбрасывает зафиксированную в нём кодовую комбинацию. Поскольку на входе накопи-

20

. 363490 О

теля 18 в это время присутствует комбинация; 0000, то она будет и на его выходе.

Под действием этой комбинации на кодовом выходе второго дешифратора 21 формируется сигнал 110010, а на выходе счетного триггера 20.тактовые импульсы имеют частоту, точно совпа- 1Q дающую с тактовой частотой информационного сигнала. Таким образом, дальнейшая корректировка фазы тактовых импульсов регенератора прекращается до прихода очередного информа- 15 ционного импульса. В блок 8 (фиг. 3) входит обнаружитель единиц методом интегрирования, состоящий из первого элемента И 26, первого счетчика 27, первого дешифратора 28, первого элемента ИЛИ 29,-третьего элемента ИЛИ 30, RS-триггера 31 и третьего элемента И 32, также обнаружитель единиц методом стробирования, состоящий из четвертого элемента И 33, 25 формирователя импульсов 34 и элемента,35 задержки, обнаружитель нулей, состоящий из инвертора 36, второго элемента И 37, второго счетчика 38, второго дешифратора 39, второго элемента ИЛИ 40.

Блок 8 работает следующим образом.

Информационные импульсы с выхода формирователя 6 импульсов (фиг. 1) поступают на переый вход элемента И 26, на первый вход элемента И 33 и на вход инвертора 36. На вторые входы элементов И 26 и 37 подаются высокочастотные импульсы заполнения с выхода генератора импульсов 25 , (фиг. 1).

При появлении информационного импульса на первом входе элемента И 26 на выходе появляются высокочастотные импульсы заполнения, количество которых пропорционально длительности входного импульса. Если информационный импульс неискажен, то количество высокочастотных импульсов заполнения будет 50.

30

35

40

45

50 Импульсы заполнения подсчитываются в первом счетчике 27 и на его кодовом выходе появляется сигнал, поступивший на кодовый вход первого дешифратора,28. Как только счетчик

5527 отсчитал 25 импульсов заполнения (50% длительности неискаженного информационного импульса), то на выходе первого дешифратора 28 появляется сигнал. Этот сигнал сбрасывает в нулевое состояние, счетчик 27 и счетчик 38 через-элементы ИЛИ 29 и ИЛИ 40 и, проходя через элемент ИЛИ 30, заставляет сработать RS-триггер 31, на входе которого появляется единичный потенциал. Этот потенциал прикладывается к первому входу элемента И 32.

Информационный импульс таким обра зом оказывается обнаруженным, но на выходе элемента И 32 (выходе блока обнаружения импульса) он появляется только после обнаружения нуля. Это сделано для того, чтобы обнаружитель единиц методом интегрирования не реагировал на дробления информационных импульсов.

Обнаружение нуля происходит следующим образом.

Информационный сигнал после прохождения инвертора 36 подается на первый вход элемента И 37-, на второй вход которого поступают высокочастотные импульсы заполнения. Если на входе и .вертора 36 сигнал 1, то импульсы заполнения не проходят на выход элемента И 37, Если на входе инвертора 36 О, то импульсы заполнения поступают на вход второго счетчика 38. Эти импульсы подсчитываются в данном счетчике 38 и на его кодовом выходе появляется сигнал, поступающий на кодовый вход второго дешифратора 39. Как только счетчик 38 отсчитывает 25 импульсов заполнения, то на выходе второго дешифратора 39 появляется сигнал. Этим сигналом сбрасывается в нулевое состояние счетчик 27 через элемент ИЛИ 40, кроме того, этот сигнал подается на второй вход элемента И 32. В момент прихода этого сигнала на выходе элемента И 32 появляется импульс обнаружения единицы, который подается далее на вход блока восстановления импульса 11 (фиг. 1). Кроме того, импульсом с выхода элемента И 32 сбрасываются в нулевое положение счетчик 27 и RS-триггер 31.

Если входной информационный сигнал имеет длительность менее 50% от неискаженного и не может быть обнаружен методом интегрирования,его можно обнаружить методом стробировлния. Для этого входной информационный сигнал подается на первый вход элемента И 33, на второй вход которого подаются короткие тактовые импульсы.

5

0

попадающие точно в середину информационных. Тактовые импульсы поступают с выхода счетного триггера 20 (фиг. 1) через элемент задержки и . формирователь коротких импульсов на второй вход элемента И 33.

При обнаружении информационного импульса на выходе элемента 33 появляется сигнал, который проходит через элемент ИЛИ 30 и опрокидывает RS-триггер 31. Таким образом, вероятность обнаружения единичного информационного импульса существенно увеличивается.

Блок 11 восстановления импульсов состоит из элемента И 41 коммутатора- 42, первого RS-триггера 43, второго RS-триггера 44, первого формирователя 45 импульсов, второго формирователя 46 импульсов, третьего формирователя 47 импульсов и элемента 48 задержки (фиг. 4).

Блок восстановления импульсов 11 5 работает следующим образом.

На первый вход схемы И поступают короткие информационные импульсы, которые обнаружены в блоке 8. На второй вход элемента И 41 подаются тактовые импульсы с выхода счетного триггера 20 (фиг. 1). При помощи элемента 48 задержки тактовые импульсы задерживаются на такую величину, что короткие информационные импульсы попадают точно на их середину. Это сделано для того, чтобы исключить прохождение помехи длительностью больше половины информационного импульса, вследствие чего она обнаружена в блоке 8 как информационный

0

5

0

сигнал, на первый RS-триггер 43. Речь

45

адат о помехе, появившейся в интервале, где в нормальных условиях должны находится только нули информационного сигнала.

Сигнал с выхода элемента И 41 поступает на первый вход коммутатора 42 и далее с его выхода на вход первого RS-триггера 43. На второй

вход коммутатора 42 подается сигнал с выхода блока 8 (фиг. 1). Управление коммутатором 42 осуществляется сигналом с блока 10 управления.- В режиме вхождения в синхронизм от

блока 10 управления (фиг. 1) на управляющий вход коммутатора 42 приходит сигнал 1, под действием которого выход коммутатора 42 соединяется с его вторым входом. В этом

13

случае информационные импульсы, минуя элемент И 41, подаются на вход первого RS-триггера 43.

Таким образом, удается уменьшить количество ошибочных импульсов за время вхождения регенерато ра в синхронизм.

После вхождения регенератора в

первый и второй входы блока управления (фиг. 1), где они поступают на первый и второй входы элемента g ИЛИ 49 (фиг. 5). Кроме того, информационные сигналы, снимаемые с вторых выходов блока 11, подаются на третий и четвертый входы блока 10 управления, откуда они поступают на

синхронизм на управляющий вход комму- первый и второй входы элемента ИЛИ 19 татора приходит сигнал О от блока 10 управления, под действием которого выход коммутатора 42 соединяется с его первым входом.

В результате информационные импульсы попадают на вход RS-триггера 43 только после их прохождения через элемент И 41. :

Под действием информационного импульса с выхода коммутатора 42 RS-триггер 43 опрокидывается и на его инверсном выходе появляется сигнал О. В таком состоянии RS-триггер 43 удерживается до прихода счетного триггера 20 (фиг. 1). Этот тактовый импульс укорачивается во втором формирователе 46 импульсов и, поступая на R-вход RS-триггера 43, возвращает его в исходное состояние. При этом на инверсном выходе RS-трнг- гера 43 возникает сигнал 1. Этот импульсньШ сигнал проходит через первый формирователь 45 импульсов, где укорачивается по длительности и подается на S-вход второго RS-триггера 44, Эта схема срабатывает и на ее выходе появляется единичный потенциал, который удерживается до прихода сигнала на R-вход. Таким сигналом являются импульсы тактовой частоты, поступающие с инверсного выхода счетного триггера 20 (фиг. 1).. Импульсы укорачиваются в третьем формирователе 47 импульсов и подаются на вход второго RS-триггера 44,

Таким образом, на выходе второго RS-триггера 44 (выходе блока 11) формируются восстановленн ые информационные импульсы, длительность которых равна длительности тактовых импульсов регератора.

Блок 10 управления (фиг. 5) состоит из первого элемента ИЛИ 49, второго элемента ИЛИ 50, счетчика 51, RS-триггера 52, элемента 53 задержки и коьй«1утатора 54.

Информационные импульсы с выходов первого 8 и второго 9 блоков обнаружения импульсов подаются на

(фиг. 5). В режиме устойчивого функционирования регенератора информационные импульсы приходят одновременно на элементы ИЛИ 49 и 50. Счетчик

15 51 срабатывает на первый импульс с выхода элемента ИЛИ 49, но через небольшой промежуток времени, определяемый элементом задержки 53, сно- . ва сбрасывается в О импульсом с

20 выхода элемента ИЛИ 50. Сигнал на выходе счетчика 51 может появиться только в том случае, если на его вход пришло 2 импульса, которые не были сброшены импульсами с выхода

25 элемента задержки 53. Таким образом, сигнал на выходе счетчика 51 появляется только при наличии импульсов на входе элемента ИЛИ 49 и отсутствия их на входе элемента ИЛИ 50. Это

30 происходит при большом расхождении фаз информационных импульсой относительно тактовых в режиме вхождения регенератора в синхронизм. В этом случае единичным импульсом с выхода счетчика 51 опрокидывается RS-триггер 52, который удерживается в этом состоянии до прихода импульса на вход элемента ИЛИ 50. Сигнал с. выхода RS-триггера 52 используется в качестве управляющего для коммутатора 54 данного блока 10 управления, в также для коммутатора 42 в блоке 11 (фиг. 4).

г

Если на управляющем входе коммута- 45 тора 54 появляется сигнал 1, то его выход соединяется с его первым входом, подключенньм к выходу элемента ИЛИ 49. Таким образом, информационные импульсы, попадающие с выхода 50 коммутатора 54 (выхода блока 10 управления) на первые входы блоков 13 и 15, снимаются в данном случае с выходов блоков 8 и 9 (фиг. 1).

При появлении синхронизма реге- 55 нератора относительно линейного сигнала на выходе элемента ИЛИ 50 (фиг. 5) появляются информационные импульсы, которые сбрасывают в О счетчик 51 и RS-триггер 52. На выЗВ

40

1363490

14

первый и второй входы блока управления (фиг. 1), где они поступают на первый и второй входы элемента ИЛИ 49 (фиг. 5). Кроме того, информационные сигналы, снимаемые с вторых выходов блока 11, подаются на третий и четвертый входы блока 10 управления, откуда они поступают на

первый и второй входы элемента ИЛИ 1

первый и второй входы элемента ИЛИ 19

(фиг. 5). В режиме устойчивого функционирования регенератора информационные импульсы приходят одновременно на элементы ИЛИ 49 и 50. Счетчик

51 срабатывает на первый импульс с выхода элемента ИЛИ 49, но через небольшой промежуток времени, определяемый элементом задержки 53, сно- . ва сбрасывается в О импульсом с

выхода элемента ИЛИ 50. Сигнал на выходе счетчика 51 может появиться только в том случае, если на его вход пришло 2 импульса, которые не были сброшены импульсами с выхода

элемента задержки 53. Таким образом, сигнал на выходе счетчика 51 появляется только при наличии импульсов на входе элемента ИЛИ 49 и отсутствия их на входе элемента ИЛИ 50. Это

происходит при большом расхождении фаз информационных импульсой относительно тактовых в режиме вхождения регенератора в синхронизм. В этом случае единичным импульсом с выхода счетчика 51 опрокидывается RS-триггер 52, который удерживается в этом состоянии до прихода импульса на вход элемента ИЛИ 50. Сигнал с. выхода RS-триггера 52 используется в качестве управляющего для коммутатора 54 данного блока 10 управления, в также для коммутатора 42 в блоке 11 (фиг. 4).

г

Если на управляющем входе коммута- тора 54 появляется сигнал 1, то его выход соединяется с его первым входом, подключенньм к выходу элемента ИЛИ 49. Таким образом, информационные импульсы, попадающие с выхода коммутатора 54 (выхода блока 10 управления) на первые входы блоков 13 и 15, снимаются в данном случае с выходов блоков 8 и 9 (фиг. 1).

При появлении синхронизма реге- нератора относительно линейного сигнала на выходе элемента ИЛИ 50 (фиг. 5) появляются информационные импульсы, которые сбрасывают в О счетчик 51 и RS-триггер 52. На вы

ходе RS-триггера 52 возникает сигнал О, под действием которого выход коммутатора 54 подключается к его второму входу, который соединен с выходом элемента ИЛИ 50. Таким образом импульсы, поступающие с выхода бл ока 10 управления на первые входы блоков 13 и 15, снимаются в данном случае с вторых блоков 11 и 12, Применение блока 10 управления позволяет повысить помехоустойчивость синхронизации и увеличить скорость вхождения в синхронизм без перерыва передачи информационных сигналов.

Блок 13 обнаружения опережения сигнала 13 (фиг. 6) состоит из первого элемента И 55, второго элемента И 56, RS-триггера 57, первого

15 Если короткий информационный импульс на первом входе элемента И 55 отстает от спада тактового импульса (прямого), то элемент И 56 остается закрытым и на его входе сигнал не

элемента 58 задержки, второго элемен- 2о возникает, В этом случае включается

та 59 задержки, первого формирователя 60 импульсов, второго формирователя 61 импульсов и счетчика 62.

Информационные импульсы с первого выхода блока 10 управления поступают на первый вход блока 13 (фиг. 1), который, внутри блока соединен с первым входом элемента И 55, На второй вход элемента И 55 поступают тактовые импульсы со второго (прямого) выхода счетного триггера 20 (фиг. 1).

Если короткий информационный импульс опережает спад тактового импульса (прямого), т.е. происходит совпадение единичньсх импульсов на первом и втором входе элемента И 55, то на ее выходе также возникает импульс. Под действием этого импульса срабатывает RS-триггер 57, прямой выход которого соединен с первым входом эле 1ента И 56. Сигналом с RS-триггера -57 элемент И 56 открывается и высокочастотные импульсы заполнения от генератора импульсов 25 проходят на вход счетчика. На кодовом выходе счетчика 62 (выход блока 13) появляются кодовые комбинации, пропорциональные количеству импульсов заполнения, попа вших на вход счетчика 62, т.е. фазовому сдвигу между информационным и тактовым импульсами.

Подача высокочастотных импульсов заполнения прекращается с приходом на R-вход RS-триггера 57 переднего фронта тактового импульса (инверсного) , под действием которого на прямом выходе RS-триггера 57 появляется О, а на инверсном 1. Сигнал

в работу блок обнаружения запаздывания сигнала.

На фиг. 7 изображена схема реализации блока обнаружения запаздыва25 ния сигнала БОЗС (15), Блок состоит из первого элемента И 63, второго элемента И 64 RS-триггера 65, элемен та 66 задержки, первого формирователя 67 импульсов, второго формирова-

30 теля 68 импульсов, счетчика 69 и

ключевых элементов 70, I

Информационный сигнал с первого

выхода блока 10 управления (фиг, 1) поступает на первый вход первого

35 элемента И 63, на второй вход которого подаются тактовые импульсы с первого (инверсного) выхода счетного триггера 20 (фиг, 1), Эти тактовые импульсы подаются также на первый

40 вход второго элемента И 64, на второй вход которого поступают высокочастотные импульсы заполнения, а на третий вход - сигнал с инверсного выхода RS-триггера 65,

45 Если тактовый импульс (инверсный) поступающий на первые входы элементов И 63 и 64, имеет единичные значения (зона обнаружения запаздывания) , то на выходе элементы И 64 по-

50 являются импульсы заполнения. Эти импульсы подсчитываются счетчиком 69, на его кодовом выходе появляются кодовые комбинации. Однако сигнал с кодового выхода счетчика 69 не по55 является на выходе блока 15, посколь ку ключевые элементы, на которые он был подан в данный интервал времени, оказываются заперты потенциалом О с прямого выхода RS-триггера 65,

с инверсного выхода RS-триггера 57, проходя через первый элемент 58 задержки и первый формирователь 60 им- пульсов, поступает с дополнительного выхода блока 13 элемента ШШ 19 и RS-tpиггep 22 (фиг. 1). Этим же фронтом тактового импульса (инверсного) через небольшс i промежуток времени,

определяемый в.орым элементом задержки, счетчик сбрасывается в О, Сброс осуществляется коротким импульсом с выхода второго формирователя.

Если короткий информационный импульс на первом входе элемента И 55 отстает от спада тактового импульса (прямого), то элемент И 56 остается закрытым и на его входе сигнал не

в работу блок обнаружения запаздывания сигнала.

На фиг. 7 изображена схема реализации блока обнаружения запаздыва5 ния сигнала БОЗС (15), Блок состоит из первого элемента И 63, второго элемента И 64 RS-триггера 65, элемента 66 задержки, первого формирователя 67 импульсов, второго формирова-

0 теля 68 импульсов, счетчика 69 и

ключевых элементов 70, I

Информационный сигнал с первого

выхода блока 10 управления (фиг, 1) поступает на первый вход первого

5 элемента И 63, на второй вход которого подаются тактовые импульсы с первого (инверсного) выхода счетного триггера 20 (фиг, 1), Эти тактовые импульсы подаются также на первый

0 вход второго элемента И 64, на второй вход которого поступают высокочастотные импульсы заполнения, а на третий вход - сигнал с инверсного выхода RS-триггера 65,

5 Если тактовый импульс (инверсный), поступающий на первые входы элементов И 63 и 64, имеет единичные значения (зона обнаружения запаздывания) , то на выходе элементы И 64 по-

0 являются импульсы заполнения. Эти импульсы подсчитываются счетчиком 69, на его кодовом выходе появляются кодовые комбинации. Однако сигнал с кодового выхода счетчика 69 не по5 является на выходе блока 15, поскольку ключевые элементы, на которые он был подан в данный интервал времени, оказываются заперты потенциалом О с прямого выхода RS-триггера 65,

При появлении отставшего по фазе информационного импульса на первом входе элемента И 64 появляется импульс на его выходе, который заставляет сработать RS-триггер 65, На инверсном выходе RS-триггера 65 возникает О, который закрывает элемент И 64, прекращая поступление импульсов заполнения на вход счетчика 69. В этом же время импульсом 1 с прямого выхода RS-триггера 65 открываются ключевые элементы 70 и кодовая комбинация, пропорциональная фазовому сдвигу между информационным и тактовым импульсом, оказывается на выходе блока 15. Сигнал с прямого выхода RS-триггера 65, проходя через элемент 66 задержки и первый формирователь 67 импульсов, поступает с дополнительного выхода блока 15 на элемент ИЛ-1 19 и КЗ-триггер 22 (фиг. 1). Сброс всей схемы в исходное состояние производится передним фронтом тактового импульса (прямого) которь й подается на R-вход RS-триггера 65, а через второй формирователь импульсов 68 на управляющий вход счетчика.

Блок 24 сравнения (фиг 8) состоит из двухвходовых элементов И 71-81 двухвходовых элементов ИЛИ 82-86, шестивходового элемента И.87 и инверторов 88-92. В нижней части фиг. 8 показаны шины первого кодового вхо- д блока 24 сравнения, соединенные с кодовым выходом второго дешифратора 21 (фиг„ 1). В верхней части фиг, 8 показаны шины второго кодового входа блока 24 сравнения, соеди- неннью с кодовым выходом первого счетчика 23 (фиг. 1). Калсдый разряд первого счетчика (1658,4,2,1) содержит прямой и инверсный выход за исключением старшего разряда (32), который имеет только прямой выход.

Инверсные сигналы в разрядах (16,8,4,2,1) с кор,ового выхода вто рого депмфратора (на первом кодовом входе блока сравнения) образуются с помоЕ ью инверторов 88-9., Сигнал старшего разряда (32) инверсии не подвергается.

Блок 24 сра;внения работает следую 15ИМ образом.

Пред пол слот:-,, что на первом кодовом входе блока сравнения в течение некторого времени действует сигнал с кодовой комбинацией 110010 (50).

При этом единичные символы этой комбинации поступают на вторые входы И 71, 72, 78, а нулевые - на вторые входы элементов И 74, 76, 80. На вторые входы элементов И 75, 77, 81 подаются сигналы 1, полученные после инверсии нулей в разрядах 8,4,1. На первые входы двухвходовых элементов И 70-80 поступают непрерывно меняющиеся сигналы с второго кодового входа данного блока (с кодового выхода первого счетчика 23). Как ToxibKo кодовая комбинация на втором

кодовом входе блока сравнения равняется 110010, то на выходах элементов И 71, 72, 75, 77, 78, 81 появляются сигналы 1. Эти сигналы проходят через элементы ИЛИ 82-86 и поступают на входы элемента И 87, на вы- ходе которого появляется импульс, являющийся выходным для блока 24 сравнения. Аналогично блок функционирует при смене сигнала на первом

кодовом входе блока сравнения.

Использование данного предложения позволяет создать регенератор цифровых сигналов, адаптирующийся к различным состояниям помеховой обстановки на линии связи. На увеличение

уровня помех в линии pereaepfaTop отвечает снижением инерционности сй оих цепей синхронизации. Вследствие этого увеличивается корреляционная связь меяоду информационными импульсами, поступающими на вход регенератора и тактовыми синхроимпульсами, вырабатываемыми внутри данного регенератора. Результатом этого является снижение вероятности ошибок при восстановлении цифрового сигнала в регенераторе.

В предложенном устройстве применена схема обнаружения информационных

импульсов, основанная на одновременном использовании метода стробирова- ния и интегрирования. При этом интегрирование производится путем заполнения информационного сигнала высокочастотныг-ш импульсами и их последующим подсчетом. Схема интегрирования не привязана с тактовым синхроимпульсам регенератора и поэтому позволяет с большей достоверностью

обнаруживать информационные посыпки. Одновременное использование двух методов обнаружения информационных импульсов позволяет успешно восстанавливать сигналы, подверженные как

191

краевым искажениям, так и дроблениям. Это способствует еще большему увеличению верности передаваемой информации .

Формула изобретения

Адаптивный регенератор, содержащий формирователь выходных импульсов, : регулируемую искусственную линию, выход которой подключен к вхо дам блока разделения через корректирующий усилитель, третий выход которого через блок автоматической регулировки усиления подключен к управ ляющему входу регулируемой искусственной линии, информационный вход которой является входом адаптивного регенератора, отличающи й- с я тем, что, с целью повьппения помехоустойчивости, дополнительно

:введены генератор импульсов, блок уп равления, первый счетчик, блок обнаружения опережения сигнала, RS-триг- гер, счетный триггер, последовательно соединенные второй счетчик и элемент ИЛИ, выход которого подключен к управляющему входу второго счетчи- ка, последовательно соединенные блок обнаружения запаздывания сигнала,

блок элемента ИЛИ, к второму кодовому входу которого подключен первый выход блока обнаружения опережения сигнала, первый дешифратор, накопитель, к управляющему входу которого подключен выход элемента ИЛИ, вт.орой дешифратор, к второму и третьему входам которого подключены вькоды RS-триггера, и блок сравнения, выход которого подключен к информационным входам счетного триггера первого и второго счетчиков, при этом первый выход блока разделения подключен через введенные последовательно сое

6349020

диненные первый формирователь импульсов, и первый блок восстановления импульсов к первому входу формироваg теля выходных импульсов, к второму входу которого подключен второй выход блока разделения через введенные последовательно соединенные второй формирователь импульсов, второй

10 блок обнаружения импульсов и второй блок восстановления импульсов, а выход генератора импульсов подключен к информационному входу первого счетчика, выход которого подключен -15 к второму кодовому входу блока сравнения, к первым входам блока обнаружения опережения сигнала и блока обнаружения запаздывания сигнала, к первым синхронизирующим входам пер20 вого и второго блоков обнаружения импульсов, выходы которых подключены к первому и второму входам блока управления, к третьим и четвертым входам которого подключены вторые

25 выходы первого и второго блоков восстановления импульсов, первый выход блока управления подключен к вторым входам блока обнаружения опережения сигнала, выход которого подключен к

30 второму входу элемента ИЛИ и первому кодовому входу RS-триггера, и блока обнаружения запаздывания сигнала, выход которого подключен к третьему входу элемента ИЛИ и второму кодовому входу RS-триггера, второй выход блока управления - к управляющим входам первого и второго блоков восстановления импульсов, к первым и вторым синхронизирующим входам кото,„ рых, к третьим и четвертым входам блоков обнаружения опережения сигналов и блока обнаружения запаздывания сигнала подключены соответственно первый и второй выходы счетного триг45

Фи2.:}

Фиу.5

JLon.Bbtf.

Код.вш.

Фиг. 6

Лоп. был.

Нод.в

to/x.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения фазового дрожания | 1987 |

|

SU1469556A1 |

| Формирователь сигналов со сдвигом фазы | 1986 |

|

SU1396239A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1425770A2 |

| Устройство для фазирования аппаратуры передачи информации циклическим кодом | 1973 |

|

SU478450A1 |

| Устройство синхронизации М-последовательности по задержке | 1986 |

|

SU1398106A1 |

| СЕЛЕКТОР ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2085028C1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛОВ | 2009 |

|

RU2422982C2 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

Изобретение относится к технике связи, в частности к устр-вам восстановления цифрового сигнала. Целью изобретения является повышение помехоустойчивости регенератора. Для достижения цели в устр-во введены г-р импульсов 25, блок управления 10, счетчики 23, 17, блок обнаружения опережения сигнала 13, RS-триггер 22, счетный триггер 20, элемент ИЛИ 19, блок обнаружения запаздывания сигнала 15, блок элементов ИЛИ 14, два дешифратора 16, 21, накопитель 18, блок сравнения 24, два формирователя импульсов 6,7, два блока восстановления импульсов 11, 12, блок обнаружения импульсов 9. На увеличение уровня помех в линии регенератор отвечает снижением инерционности своих цепей синхронизации. Вследствие этого увеличивается корреляционная связь между информационными импульсами и тактовыми синхроимпульсами. В результате снижается вероятность ошибок при восстановлении цифрового сигнала в регенераторе. Одновременное использование двух методов обнаружения информационных импульсов позволяет успешно восстанавливать сигналы, подверженные как краевым искажениям, так и дроблениям. Это способствует еще большему увеличению верности передаваемой информации. 5,1 ил. сл со о со 4;: СО фиг /

От ntpfoto cvfrnuuxa

Ч Л«в

От Smopoto dtwutppofnopu IHute

Редактор Т.Лазоренко

Составитель Л.Тимошина

Техред М.Ходанич Корректор В.Бутяга

Заказ 6382/55Тираж 636Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Иванов Ю.П., Левин Л.С | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Радио и связь, 1983, с | |||

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| рпс | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-12-30—Публикация

1986-06-19—Подача