9,накопитель синхроннформации (НС)

10,блок памяти (БП) 11, элемент задержки 12 и элемент запрета 13 Дпя представленных вариантов структурных искажений передаваемой кодовой комбинации достаточно двух приемов, чтобы полностью восстановить синхроструктуру самосинхронизирующейся последовательности. Одновременно с восстановлением в БП 11 происходит накопление элементой двоичной последовательности, соответствующих значащим моментам, приняИзобретение относится к средствам связи и может быть использовано в каналах связи в составе аппаратуры передачи данных и является усовершенствованием изобретения по авт.св. № 836814.

Цель изобретения - повышение помехоустойчивости.

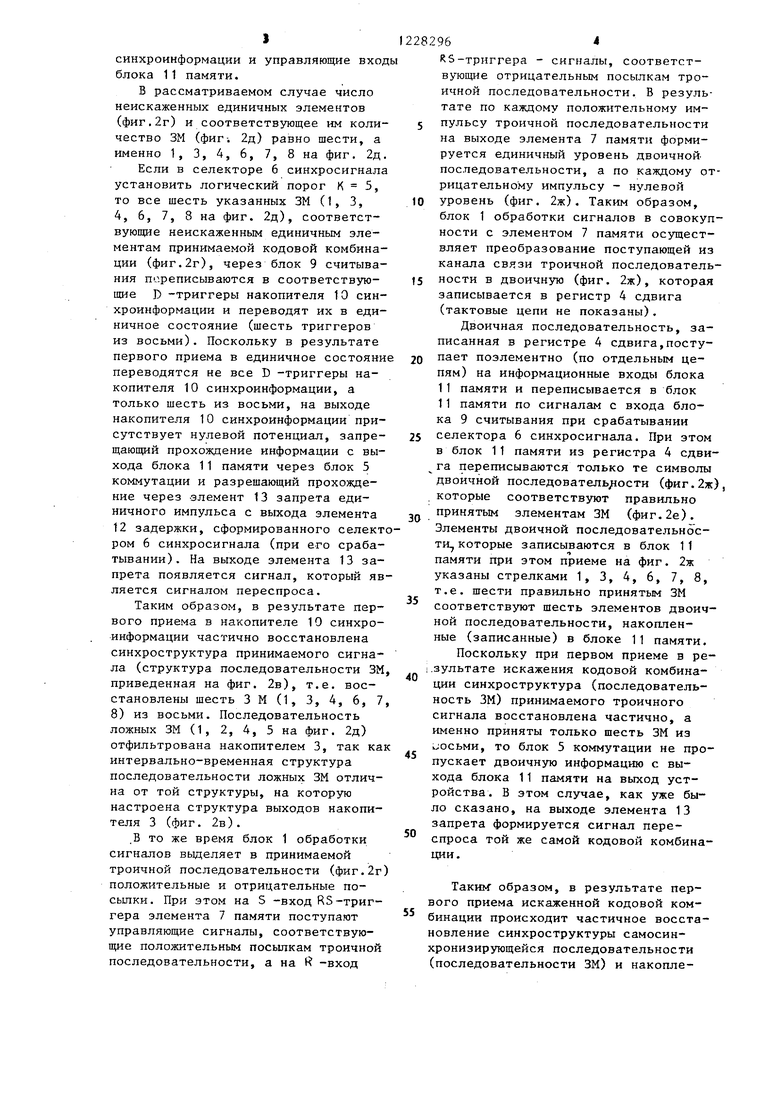

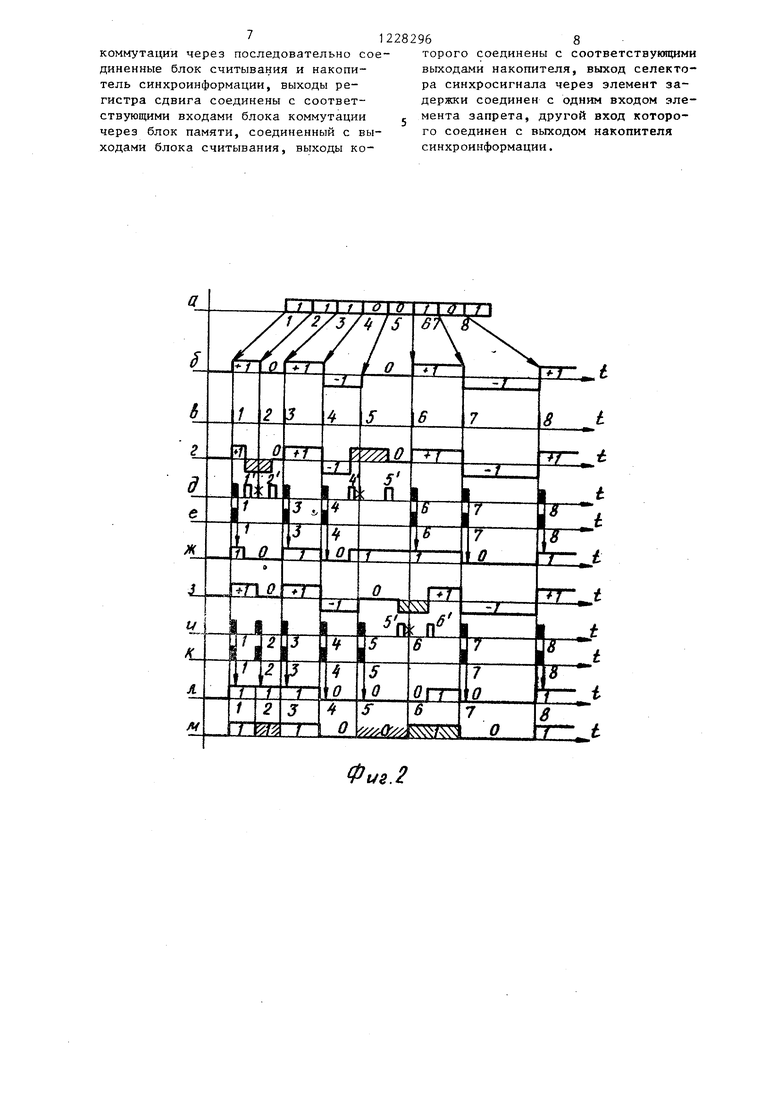

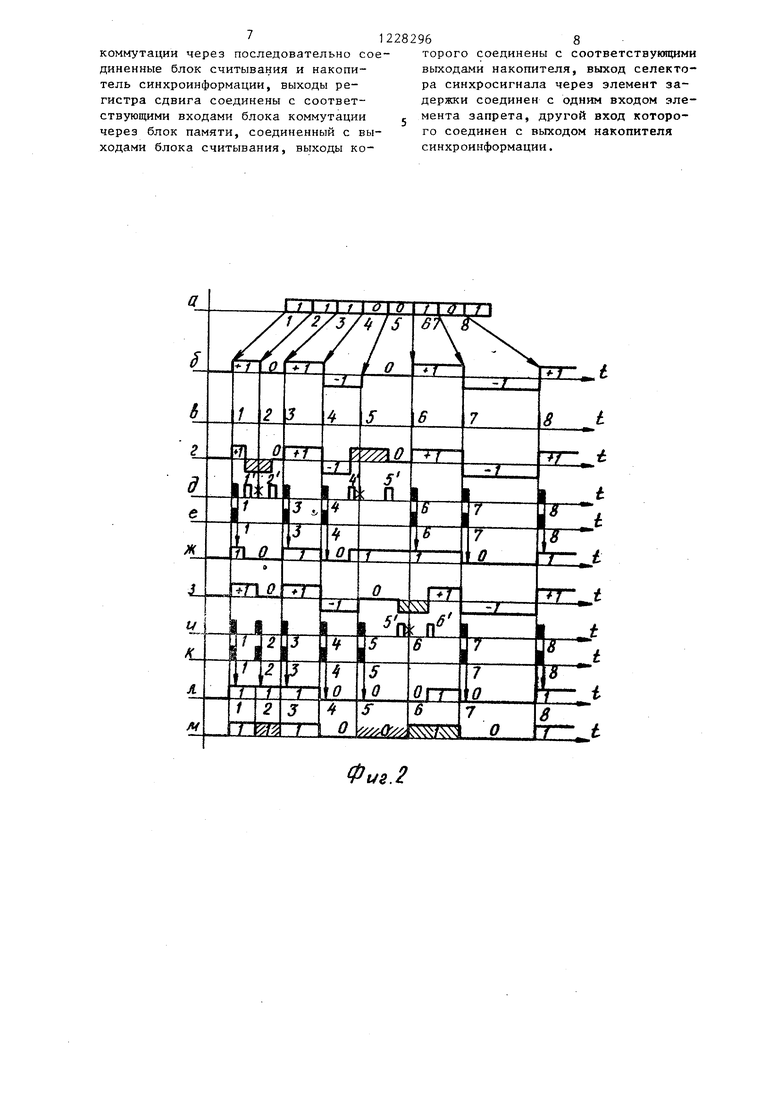

На фиг.1 изображена структурная электрическая схема предлагаемого устройства{ на фиг,2 - временные диаграммы, поясняющие работу устройства, на фиг.З - блок обработки сигнала, пример выполнения, на фиг.4 - приемник, пример выполнения.

Устройство для приема самоеин- хронизир:лощейся дискретной информации содержит блок 1 обработки сигнала, приемник 2, накопитель 3,регистр 4 сдвига, блок 5 коммутации,, селектор 6 синхросигнала, элемент 7 памяти, декодер 8, блок 9 считывания накопитель 10 синхроинформации, блок 11 памяти, элемент 12 задержки,элемент 13 запрета.

. Устройство работает следующим образом.

На вход устройства поступает са- мосинхронизирующаяся импульсная троичная последовательность (z Л (фиг.2б), сформированная на чике из двоичной последовательности

: X „ - Y,

{AjJ (фиг.2а) по закону; K-a VK-i VK-i; х„--у„.о, где к соответствует порядковому номеру значащего момента (ЗМ) передаваемого сигнала. Дпя определенности считают, что информация пе28296

TbW без искажений. После переприема в НС 10 полностью восстанавливается синхроструктура сигнала. На выходе НС 10 появляется единичный уровень и на управляющий вход блока коммутации 5 поступает сигнал разрешения прохождения информации с выходов БП 11 на вход декодера 8, где информация преобра.зуется в знак сообщения и вьщается потребителю. Цель достигается введением БС 9,НС 10, БП.11, элемента задержки 12 и элемента запрета 13. 4 ил.

i

0

3

0

5

редается бейтами. В этом случае количество ЗМ, приходящееся на один зрак, равно h 8 (фиг.2в).

Е усть в результате первой передачи кодовой комбинации (фиг.2г) оказались искаженными 2-й и 5-й единичные элементы (на фиг.2г заштрихованы) .

В приемнике 2 происходит вьзделе- ние ЗМ (фронтов) приходящего сигнала и формирование по каждойу выделенному ЗМ прямоугольного импульса заданной длительности (фиг.2д). В результате действия помех в канале связи в приемнике 2 наряду с правильно вьщеленными ЗМ происходит выделение ЗМ искаженных единичных элементов, что приводит к появлению ложных ЗМ и подавлению истинных ЗМ. На фиг. 2д правильно принятые ЗМ обозначены сплошными прямоугольни- (1, 3, 4, 6, 7, 8) ложные ЗМ контурными (1, 2, 4, 5), а подавленные ЗМ - перечеркнуты (2, 5).

Импульсная последовательность с выхода приемника 2 поступает на вход накопителя 3. При одновременном появлении на выходах накопителя 3 единичных ш- пульсов, число которых превьштет логический порог К. происходит срабатывание селектора 6 синхросигнала, на выходе которого формируется единичный импульс,посту- пающ1-1Й на управляющий вход блока У считывания, осуществляющего через элементы И блока 9 считывание рабочих импульсов с выхода накопителя 3 и передачу их на входы накопителя 10

I

синхроинформации и управляющие вход блока 11 памяти.

В рассматриваемом случае число неискаженных единичных элементов (фиг.2г) и соответствующее им количество ЗМ (фиг-. 2д) равно шести, а именно 1, 3, 4, 6, 7, 8 на фиг. 2д

Если в селекторе 6 синхросигнала установить логический порог К 5, то все шесть указанных ЗМ (1, 3, 4, 6, 7, 8 на фиг. 2д), соответствующие неискаженным единичным элементам принимаемой кодовой комбинации (фиг.2г), через блок 9 считывания переписываются в соответствующие D -триггеры накопителя 10 синхроинформации и переводят их в единичное состояние (шесть триггеров из восьми). Поскольку в результате первого приема в единичное состояни переводятся не все D -триггеры накопителя 10 синхроинформации, а только шесть из восьми, на выходе накопителя 10 синхроинформации присутствует нулевой потенциал, запрещающий прохождение информации с выхода блока 11 памяти через блок 5 коммутации и разрешающий прохождение через -элемент 13 запрета единичного импульса с выхода элемента 12 задержки, сформированного селектром 6 синхросигнала (при его срабатывании). На выходе элемента 13 запрета появляется сигнал, который является сигналом переспроса.

Таким образом, в результате первого приема в накопителе 10 синхроинформации частично восстановлена синхроструктура принимаемого сигнала (структура последовательности ЗМ приведенная на фиг. 2в), т.е. восстановлены шесть ЗМ (1, 3, 4, 6, 7 8) из восьми. Последовательность ложных ЗМ (1, 2, 4, 5 на фиг. 2д) отфильтрована накопителем 3, так ка интервально-временная структура последовательности ложных ЗМ отлична от той структуры, на которую настроена структура выходов накопителя 3 (фиг. 2в).

.В то же время блок 1 обработки сигналов вьщеляет в принимаемой троичной последовательности (фиг.2г положительные и отрицательные посылки. При этом на S -вход RS-триггера элемента 7 памяти поступают управляющие сигналы, соответствующие положительным посылкам троичной последовательности, а на R -вход

28296

RS-триггера - сигналы, соответствующие отрицательным посылкам троичной последовательности. В результате по каждому положительному им- 5 пульсу троичной последовательности на выходе элемента 7 памяти формируется единичный уровень двоичной последовательности, а по каждому отрицательному импульсу - нулевой

10 уровень (фиг. 2ж). Таким образом,

блок 1 обработки сигналов в совокупности с элементом 7 памяти осуществляет преобразование поступающей из канала связи троичной последователь}5 ности в двоичную (фиг. 2ж), которая записывается в регистр 4 сдвига (тактовые цепи не показаны).

Двоичная последовательность, записанная в регистре 4 сдвига,посту20 пает поэлементно (по отдельным цепям) на информационные входы блока 11 памяти и переписывается в блок 11 памяти по сигналам с входа блока 9 считывания при срабатывании

25 селектора 6 синхросигнала. При этом

в блок 11 памяти из регистра 4 сдви- га переписываются только те символы

двоичной последовательности (фиг.2ж), , которые соответствуют правильно

2JJ принятьм элементам ЗМ (фиг.2е). Элементы двоичной последовательности которые записываются в блок 11 памяти при этом приеме на фиг. 2ж указаны стрелками 1, 3, 4, 6, 7, 8, т.е. шести правильно принятым ЗМ соответствуют шесть элементов двоичной последовательности, накопленные (записанные) в блоке 11 памяти.

Поскольку при первом приеме в ре- .зультате искажения кодовой комбинации синхроструктура (последовательность ЗМ) принимаемого троичного сигнала восстановлена частично, а именно приняты только шесть ЗМ из ;осьми, то блок 5 коммутации не пропускает двоичную информацию с выхода блока 11 памяти на выход устройства. В этом случае, как уже было сказано, на выходе элемента 13 запрета формируется сигнал переспроса той же самой кодовой комбинации.

Таким образом, в результате первого приема искаженной кодовой ком- бинации происходит частичное восстановление синхроструктуры самосинхронизирующейся последовательности (последовательности ЗМ) и накопле5

0

5

ние правильно принятых символов принимаемой кодовой комбинации.

При повторной передаче той же самой кодовой комбинации структура искажения в общем случае может быть отлична от-структуры искажения кодовой комбинации при первой передаче, например как показано на фиг. 2э поражен только шестой элемент троичной последовательности,. а все ос- тальные не искажены.

Прием троичной последовательности, приведенной на фиг. 2з, происходит аналогично как и при первом приеме. На фиг. 2и приведена после- довательность сигналов нормированной длительности на выходе приемника 2, На фиг,, 2к приведены правильно принятые сигналы нормированной длительности. На фиг. 2л приведена двоич- ная последовательность на выходе элемента 7 памяти,и записанная в регистр А сдвига, стрелками-отмечены те символы двоичной последовательности, которые были считаны с выходов регистра сдвига 4 в соответствующие D-триггеры блока 11 памяти при срабатывании селектора 6 синхросигнала

При первом приеме кодовой комбинации, как уже отмечалось, в накопи- тель 10 синхроинформации записаны 1, 3, 4, 6, 7, 8 значащие моменты, а соответствующие им элементы двоичной последовательности записаны в блок 11 памяти. При повторном приеме той же самой кодовой комбинации в накопитель 10 синхроинформации

записаны 1, 2, 3, 4, 5, 7, 8 значащие моменты, а соответствующие им

элементы двоичной последовательности записаны в блок 11 памяти. Таким образом, для рассматриваемых вариантов структурных искажений передаваемой кодовой комбинации (фиг,2г, фиг. 2з) оказывается достаточным двух приемов для того, чтобы пол- носТью восстановить синхроструктуру самосинхронизирующейся последовательности (фиг. 26). На самом деле,- 2-й и 5-й значащие моменты, подавленные при первой передаче (фиг. 2д),,прк повторой передаче приняты без искажений (фиг. 2и), а 6-й значащий момент, подавленный помехами при повторной передаче (фиг. 2и), принят без искажений после первой передачи (фиг. 2д) и запомнен соответствующим D -триггером накопителя 10 син хроинформации.

5 O

5 0 5

Q

5

5

Одновреме Нно с восстановлением синхроструктуры пpини ae югo сигнала (последовательности ЗМ на фиг. 2в) в блоке 11 памяти происходит накопление элементов двоичной последова- , тельности, соответствующих значащим моментам, принятым без искажений. Так в результате первого приема в блок 11 памяти записаны 1, 3, 4, 6, 7, 8 двоичные элементы (фиг. 2ж), а в результате переприема дополнительно записаны 2, 5 элементы.

После переприема в накопителе 10 синхроинформации полностью восстановлена синхроструктура сигнала,т.е. все J) -триггеры накопителя 10 синхроинформации находятся в единичном: состоянии, на выходе накопителя 10 синхроинформации появляется единичный уровень и на управляющий вход блока 5 коммутации поступает сигнал разрешения прохождения информации с выходов блока 11 памяти на вход декодера 8, где информация преобразуется в знак сообщения и выдается потребителю. Сигнал переспроса в этом случае не формируется,так как единичный уровень с выхода накопителя 10 синхроинформации блокирует по запрещающему входу элемент 13 запрета.

После считывания информации с выходов блока 1 1 памяти TJ -триггеры накопителя 10 синхроинформации устанавливаются в исходное (нулевое) состояние (цепи установки триггеров в нулевое состояние не приведены).

На фиг. 2м приведены эпюры напряжений двоичного сигнала, записанного в блоке 11 памяти. Единичные элементы последовательности, пораженные в каналы при первом и втором приемах и восстановленные в результате накопления, на фиг. 2м заштрихованы:.

Формула изобретения

Устройство для приема самосинхронизирующейся дискретной информации по авт.св. 836814, отличающееся, тем, что, с целью повышения помехоустойчивости, введены блок считывания, накопитель синхроинформации, блок памяти, элемент задержки и элемент запрета, причем выход селектора синхросигнала подключен к управляющему входу блока

71

коммутации через последовательно сое диненные блок считывания и накопитель синхроинформации, выходы регистра сдвига соединены с соответствующими входами блока коммутации через блок памяти, соединенный с выходами блока считывания, выходы ко2282968

торого соединены с соответствующими выходами накопителя, выход селектора синхросигнала через элемент задержки соединен с одним входом эле- , мента запрета, другой вход которого соединен с выходом накопителя синхроинформации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема самосинхронизирующейся дискретной информации | 1982 |

|

SU1080252A2 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1982 |

|

SU1030989A2 |

| Устройство для приема самосинхронизирую-щЕйСя диСКРЕТНОй иНфОРМАции | 1979 |

|

SU836814A1 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1980 |

|

SU924902A2 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

Изобретение относится к средствам связи и м.б. использовано в каналах связи в составе аппаратуры передачи данных. По отношению к осн.авт.св. № 836814 повышается помехоустойчивость. Устройство содержит блок обработки сигнала 1, приёмник 2, накопитель 3, регистр сдвига 4, блок коммутации 5, селектор синхросигнала 6, элемент памяти 7, декодер В, блок считывания (БС) с « ISJ

bl/0f f)

fo)

I

ifon(-}

фиг.З

Приемник

F1

Одно6ибра/77Ор

Составитель И. Лазарева Редактор Н. Киштулинец Техред Н.Бонкало Корректор А. Обручар

Заказ 2298/59Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035,.Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

.

| Устройство для приема самосинхронизирую-щЕйСя диСКРЕТНОй иНфОРМАции | 1979 |

|

SU836814A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-04-30—Публикация

1984-09-24—Подача