фиг.1 .

Изобретение относится к технике связи, в частности к технике передачи сигналов с использованием кодов видаЗВ4В, и может использоваться при разработке цифровых систем передачи информации по электрическим и оптическим кабелям.

Известен декодер кода ЗВ4В, недостатком которого декодера является низкая помехоустойчивость, обусловленная высоким коэффициентом размножения ошибок при декодировании (1,55).

Наиболее близким по технической сущности к предлагаемому устройству является устройство блочной синхронизации. Устройство содержит регенератор, блок обнаружения признака синхросигнала, управляемый делитель частоты и накопитель.

Недостатком известного декодера является низкая помехоустойчивость, связанная с достаточно высоким коэффициентом размножения ошибок, а также невозможность декодирования сигнала ЗВ2Т(0)-ОТБС.

Целью изобретения является повышение помехоустойчивости за счет минимизации коэффициента размножения ошибок.

Это достигается тем, что в декодере баг- лансного кода, содержащий регенератор, тактовый выход которого подключен к тактовому входу первого управляемого делителя частоты, блок обнаружения признаков троичного синхросигнала, первый выход которого подключен к первому входу первого накопителя, введены формирователь относительного троичного сигнала, формирователь троичного сигнала, параллельный регистр, формирователь двоичного сигнала, умножитель частоты, параллельно-последовательный регистр, второй накопитель, второй управляемый делитель частоты, первый-третий формирователи импульсов и блок определения признаков двоичного синхросигнала, информационный и тактовый входы которого подключены соответственно к информационному и тактовому выходам регенератора, прямой выход первого управляемого делителя частоты подключен к тактовым входам второго управляемого делителя частоты, формирователя относительного троичного сигнала, формирователя троичного сигнала, блока обнаружения признаков троичного синхросигнала и второму тактовому входу блока определения признаков двоичного синхросигнала, счетный выход, выход сброса и информационные выходы которого подключены соответственно к счетному входу сброса второго накопителя и информационным входам формирователя относительного троичного сигнала, выходы

которого подключены к информационным входам блока обнаружения признаков троичного синхросигнала, вторые входы которого подключены к информационным входам параллельного регистра, выходы которого подключены к соответствующим входам формирователя двоичного сигнала, выходы которого подключены к информационным входам параллельно-последователь0

ного регистра, выход которого является

выходом декодера, балансного кода, выход вто- ( р ого накопителя через третий формирователь импульсов подключен к управляющему входу перврго управляемого делителя час5 тоты, инверсный выход которого подключен к третьему тактовому входу блока определения признаков двоичного синхросигнала, выходы первого накопителя, умножителя частоты и второго формирователя импуль0 сов подключены соответственно к входу первого формирователя импульсов, первому и второму тактовым входам параллельно- последовательного регистра, выход Первого формирователя импульсов подключен к уп5 равляющему входу второго управляемого делителя частоты, выход которого подключен к тактовому входу параллельного регистра, второму входу первого накопителя и входам умножителя частоты и второго фор0 мирователя импульсов.

Кроме того, блок обнаружения признаков троичного синхросигнала содержит последовательно соединенные последовательный регистр, соединенный информационными и

5 тактовым входами с информационными и тактовым входам блока обнаружения признаков троичного синхросигнала, а информационными выходами с вторыми выходами блока обнаружения признаков троичного

0 синхросигнала, и дешифратор, выход которого соединен с первым выходом блок обнаружения признаков троичного синхросигнала, кроме того блок определения признаков двоичного синхросигнала содержит последова5 тельно соединенные последовательный регистр, соединенный входами с соответствующими информационными и первым тактовым входами блока определения признаков двоичного синхросигнала, и параллельный

0 регистр, соединенный вторым и третьим выходами с информационными выходами блока определения признаков двоичного синхросигнала, первый и второй обнаружители нарушения чередования полярностей

5 троичных нулей, соединенные выходами соответственно с выходом сброса и счетным выходом блока определения признаков двоичного синхросигнала, первым информаци- оннымвходом соединенные соответственно с первым и третьим выходами параллельного регистра, вторыми информационными входами соединенные с вторым выходом параллельного регистра, причем тактовый вход параллельного регистра соединен с тактовым входом первого обнаружителя нарушений чередования полярностей троичных нулей и с вторым тактовым входом блока определения признаков двоичного синхросигнала, а тактовый вход второго обнаружителя нарушения чередования полярностей троичных нулей соединен с третьим тактовым входом блока определения признаков двоичного сигнала.

Кроме того, каждый обнаружитель нарушения чередования полярностей троичных нулей содержит два канала, состоящих из последовательно соединенных схем совпадения, первого и второго триггеров и формирователя импульсов, а также элемент ИЛИ, выход которого соединен с выходом обнаружителя нарушения чередования полярностей троичных нулей, причем два инвертирующих входа схемы совпадения одного канала и два входа совпадения другого канала соединены с информационными входами обнаружителя нарушения чередования полярностей троичных кулей, третьи входы обоих схем совпадения соединены с тактовым входом обнаружителя нарушения чередования полярностей троичных нулей, выход схемы совпадения первого канала соединен с тактовым входом второго триггера этого канала и с входом установки в нуль первого триггера второго канала, и выход схемы совпадения второго канала подключен к тактовому входу второго триггера этого канала и к входу установки в нуль первого триггера первого канала, информационный вход которого, как и информационный вход первого триггера второго канала подключены к шине питания, кроме того выход формирователя импульсов первого- канала соединен с первым входом элемента ИЛИ и с входом установки в нуль второго триггера этого канала, а выход формирователя импульсов второго канала подключен к второму входу элемента ИЛИ и к входу установки в нуль второго триггера этого канала.

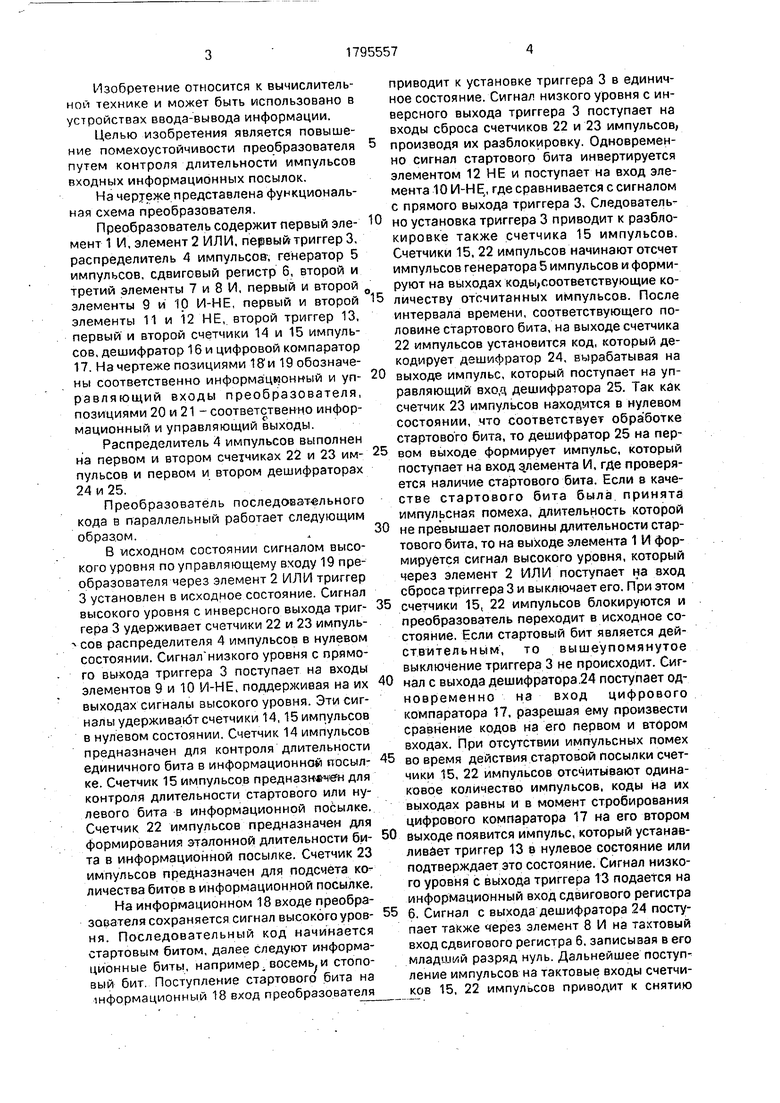

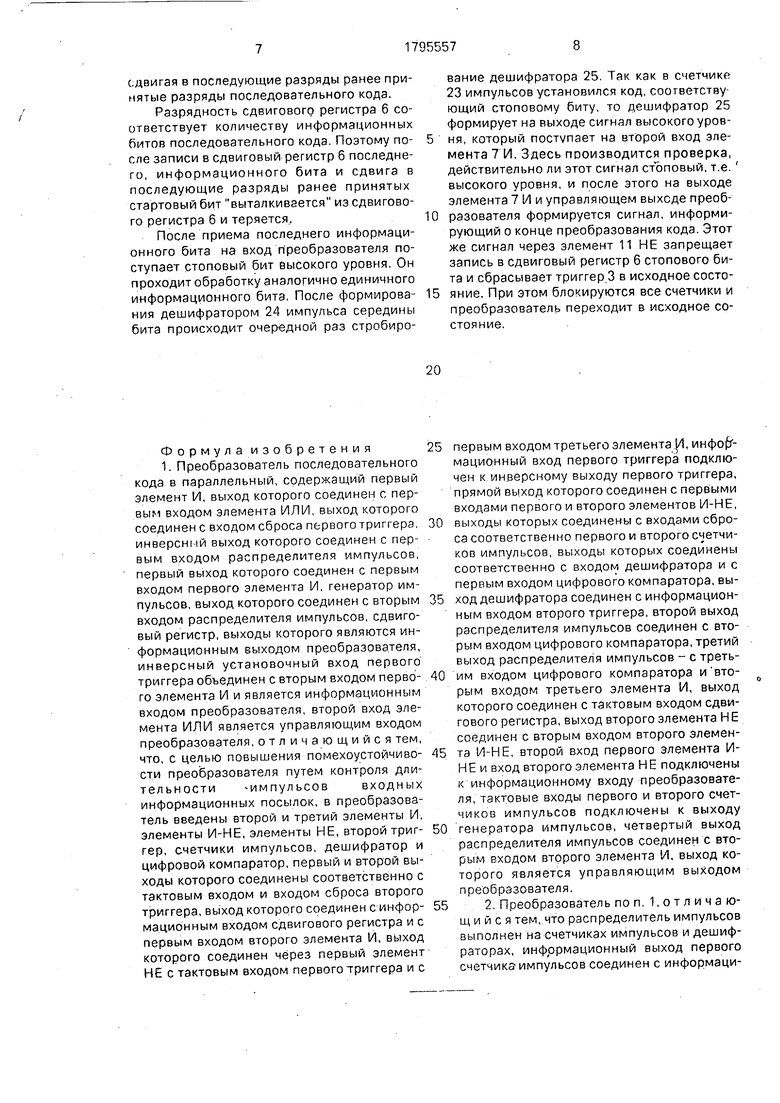

На фиг. 1 приведена структурная электрическая схема декодера балансного кода; на фиг. 2.0 и 2.1 - временные диаграммы, поясняющие работу декодера; на фиг. 3 - один из возможных вариантов структурной электрической схемы обнаружителя нарушений чередования полярностей троичных нулей; на фиг. 4 - один из возможных вариантов структурной электрической схемы формирователя относительного троичного сигнала: на фиг. 5 - формирователь троичного сигнала.

Декодер балансного кода (фиг. 1) содер-. жит регенератор 1, тактовый выход которого подключен к .тактовому входу первого управляемого делителя 2 частоты,блокЗ обна- 5 ружения признаков троичного синхросигнала, первый выход подключен к первому входу первого накопителя 4, формирователь 5 относительного троичного сигнала, формирователь 6 троичного сигна0 ла, параллельный регистр 7, формирователь 8 двоичного сигнала, умножитель 9 частоты, параллельно-последовательный регистр 10, второй накопитель 11, второй управляемый делитель 12 частоты, первый, второй, третий

5 формирователи 13. 14, 15 импульсов и блок 16 определения признаков двоичного синхросигнала,

В декодере балансного кода информационный и первый тактовый входы блока 16

0 определения признаков двоичного синхросигнала подключены соответственно к информационному и тактовому выходам регенератора 1, прямой выход первого управляемого делителя 2 частоты подключен к

5. тактовым входам второго управляемого де - лителя частоты 12, формирователя 5 относи- тельноготроичного сигнала, формирователя 6 троичного сигнала, блока 3 обнаружения признаков троичного синх0 росигнала и второму тактовому входу блока 16 определения признаков двоичного синхросигнала. Счетный выход, выход сброса и информационные выходы блока 16 определения признаков двоичного синхросигнала

5 подключены соответственно к счетному входу и входу сброса второго накопителя 11 и информационным входам формирователя 5 относительного троичного сигнала, выходы которого подключены к информационным

0 входам формирователя 6 троичного сигнала, выходы которого в свою очередь подключены к информационным входам блока 3 обнаружения признаков троичного сигнала, вторые выходы которого подключены к информационным входам параллельного регистра 7, выходы которого подключены к соответствующим входам формирователя 8 двоичного сигнала, выходы которого подключены к информационным входам парал0 лельно-последовательного регистра 10, выход которого является выходом декодера балансного кода.

Выход второго накопителя 11 через третий формирователь 15 импульсов подклю5 чем к управляющему входу первого управляемого делителя 2 частоты, инверсный выход которого подключен к третьему тактовому входу блока 16 определения признаков двоичного синхросигнала, выходы первого накопителя 4. умножителя 9 частоты и второго формирователя 14 импульсов подключены соответственно ко входу первого формирователя 13 импульсов, первому и второму тактовым входам параллельно- последовательного регистра 10, выход первого формирователя 13 импульсов подключен к управляющему входу второго управляемого делителя 12 частоты, выход которого подключен к тактовому входу параллельного регистра 7, второму входу первого накопителя 4 и входам умножителя 9 частоты и второго формирователя 14 импульсов.

Блок обнаружения признаков троичного синхросигнала 3 содержит последовательно соединенные последовательный регистр 17, соединенный информационными и тактовым входами с информационными и тактовым входами блока обнаружения признаков троичного синхросигнала 3, а информационными выходами с вторыми выходами блока 3 обнаружения признаков троичного синхросигнала и дешифратор 18, выход которого соединен с первым выходом блока 3 обнаружения признаков троичного синхросигнала.

Декодер балансного кода содержит также блок 16 определения признаков двоичного синхросигнала, в который входят последовательно соединенные последовательный регистр 19, соединенный входами с соответствующими информационным и первым тактовым входом блока 16 определения признаков двоичного синхросигнала, и параллельный регистр 20, соединенный вторым и третьим выходами с информационными выходами блока 16 определения признаков двоичного синхросигнала, первый и второй обнаружители 21 и 22 нарушения чередования полярностей троичных нулей, соединенные выходами соответственное выходом сброса и счетным выходом блока 16 определения признаков двоичного синхросигнала, первым информационным входом соединённые соответственно с первым и третьим выходами параллельного регистра 20, вторыми информационными входами соединенные с вторым выходом параллельного регистра 20. причем такто- в, параллельного регистра 20 соединен с тактовым входом первого обнаружителя 21 нарушений чередования полярностей троичных нулей и с вторым тактовым входом блока 16 определения признаков двоичного синхросигнала, а тактовый вход второго обнаружителя 22 нарушения чередования полярностей троичных нулей соединен с третьим тактовым входом блока 16 определения признаков двоичного сигнала.

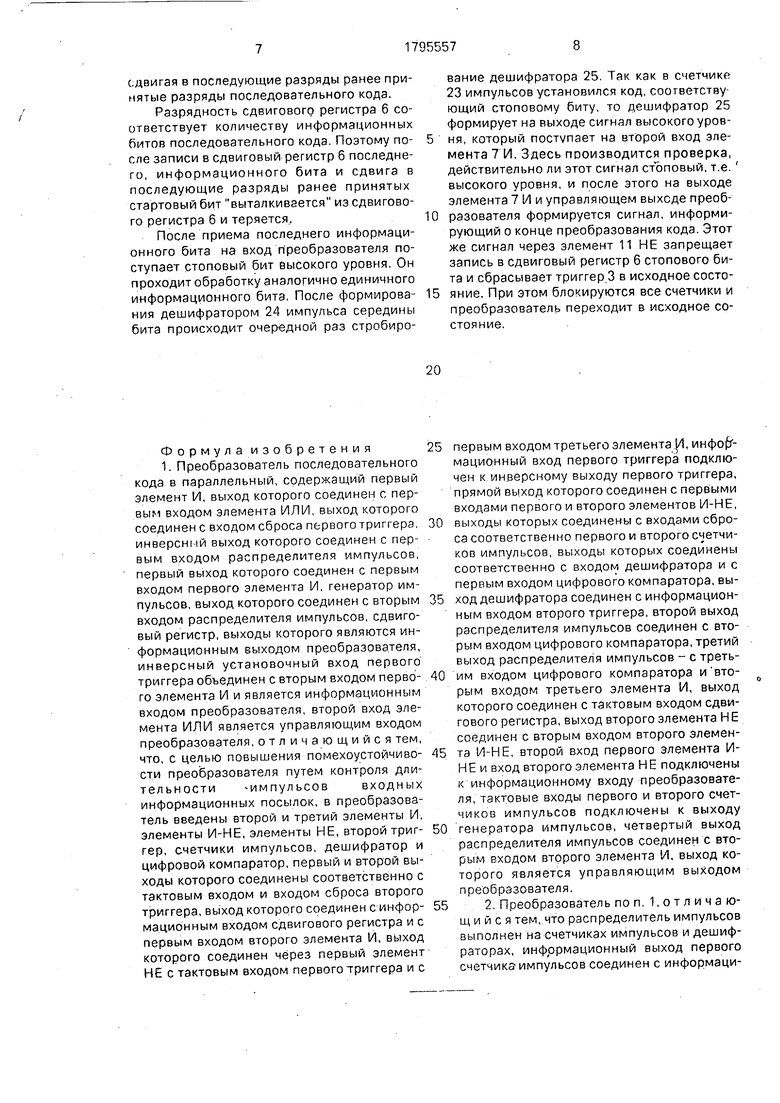

Обнаружители 21 и 22 нарушения чередования полярностей троичных нулей содержит два канала, состоящих из последовательно соединенных схем совпадения 23 (24), первого и второго триггеров 25 (26) и 27 (28) и формирователя 29 (30) импульсов, а также элемент ИЛИ 31, выход которого соединен с выходом обнаружителя 21 (22) нарушения чередования полярно0 стей троичных нулей, причем два инвертирующих входа схемы 23 совпадения одного канала и два входа схемы 24 совпадения другого канала соединены с информационными входами обнаружителя 21 (22)наруше5 ния чередования полярностей троичных нулей , третьи входы схем 23 и 24 совпадения соединены с тактовым входом обнаружителя 21 (22) нарушения чередования полярностей троичных нулей, выход схемы

0 23 совпадения первого канала соединен с тактовым входом второго триггера 27 этого канала и с входом установки в нуль первого триггера 26 второго канала и выход схемы 24 совпадения второго канала подключен к

5 тактовому входу второго триггера 28 этого канала и к входу установки в нуль первого триггера 25 первого канала, информационный вход которого, как и информационный вход первого триггера 26 второго канала,

0 подключены к шине питания, кроме того выход формирователя импульсов первого канала соединен с первым входом элемента 31 ИЛИ и с входом установки в нуль второго 27 триггера этого канала, и выход формиро5 вателя 30 импульсов второго канала подключен к второму входу элемента ИЛИ 31 и к входу установки в нуль второго триггера 28 этого канала.

Для пояснения принципа работы пред0 ложенного декодера балансного кода приводится алгоритм формирования сигнала ЗВ2Т(0)-ОТБС.

. Исходный двоичный сигнал разделяется на передающей стороне на группы, со5 стоящие из 3-х двоичных символов (3В) и каждая группа преобразуется в троичную группу, содержащую 2 символа, в соответствии с кодовой таблицей (табл. 1), обладающей при выбранном алгоритме

0 минимальным коэффициентом размножения ошибок.

Сущность относительного метода формирования троичных символов заключается в суммировании по модулю три данного тро5 ичного символа кода ЗВ2Т и предыдущего троичного (относительного символа кода ЗВ2Т(0).

Формирование троичных символов из относительных троичных символов осуществляется в соответствии с табл. 2.

При передачи троичных символов методом ОТБС каждый троичный символ переда- ется двумя двоичными символами.

Оптимальным (с точки зрения минимизации коэффициента размножения ошибок) алгоритмом ТОБС (относительный трехпози- ционный биимпульсный сигнал) является следующий: при передаче троичного нуля оба двоичных символа одинаковы и отличаются от двоичных символов предыдущего троичного нуля; при передаче троичной единицы каждый двоичный символ отличается от -предыдущего; при передаче троичной двойки первый двоичный символ совпадает с предыдущим двоичным символом, а второй - отличается.

Как следует из приведенного алгоритма формирования сигнала ЗВ2Т(0)-ОТБС, в этом сигнале заложено чередование пар двоичных символов, так как троичный нуль может быть представлен в виде 11 или 00. Если же границы групп, состоящих из двух символов, будут смещены на один тактовый интервал, то будут возникать нарушения чередований пар двоичных символов 11 и 00. Этот признак положен в основу синхронизации сигнала ОТВС для правильного определения троичных символов в принятом сигнале.

Как следует из табл. 1 во вторичном сигнале запрещена передача кодовой группы 00, Поэтому для определения на приемной стороне границ кодовых групп в троичном сигнале используется появление запрещенной группы 00, которая может быть только при следующих сочетаниях троичных групп 10-01, 20-01, 10-02,20-02,что в свою очередь является признаком для второго вида синхронизации.

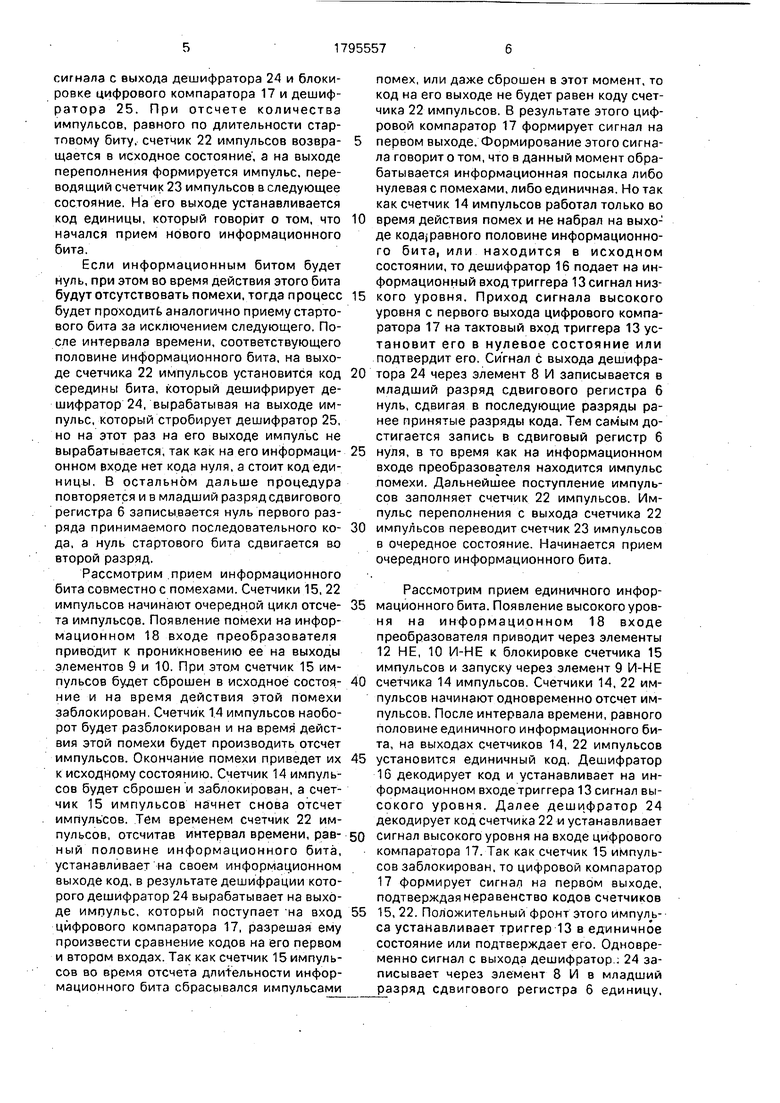

Цифровой сигнал ЗВ2Т(0)-ОТБС (фиг. 2а) с выхода регенератора (Per.) 1 и выделенный в нем тактовый сигнал (фиг. 26) поступают соответственно на информационный и тактовый входы последовательного регистра (ПсР) 19. Тактовый сигнал поступает также на вход первого управляемого делителя частоты (ДЧ) 2, работающего по заднему фронту сигнала тактовой частоты.

Сигналы с выходов ПсР 19 (фиг. 2в,г,д) подаются на информационные входы параллельного регистра (ПрР) 20, а с его выходов (фиг. 2ж,з,и) - на входы обнаружителей 21 и 22 нарушения чередования полярностей троичных нулей (ОНЧП).

Сигнал с прямого выхода первого ДЧ 2 (фиг. 2е) поступает на тактовые входы ПрР 20 и первого ОНЧП 21, а с инверсного выхода - на тактовый вход второго ОНЧП 22.

ОНЧП 21 и 22 могут быть выполнены по схеме, приведенной на фиг. 3 работают следующим образом.

Как отмечалось выше, троичный нуль 5 передается в сигнале ОТБС двумя импульсами 11 и 00 поочередно. Причем при безошибочной работе это чередование сохранится и на приемной стороне, а на границе групп это чередование будет

0 нарушаться, что является признаком для определения границ групп в сигнале ОТБС на приемной стороне.

При совпадении символов А и В (В и С) (фиг. 1, 3) на выходах схем совпадения 23 и

5 24 появляются отклики длительностью равной половине тактового интервала сигнала с выхода первого ДЧ 2. Эти отклики (фиг. 2к,л,м,н) поступают на тактовые входы соответствующих триггеров 25-28 и на устано0 вочные входы соответствующих триггеров 25 и 26. В случае, если нарушения чередования полярностей отсутствуют, каждый отклик устанавливает в 1 соответствующий триггер 26 или 25. При этом сигнал на выхо5 де ОНЧП отсутствует.

При нарушении чередования полярностей пар 11 или 00, т.е. при появлении подряд двух откликов на выходе одной из СС 23 или 24 (фиг. 2м,н), вторым откликом

0 1 записывается в соответствующий триггер 27 или 28, а на выходе ОНЧП 21, 22 формируются узкие импульсы (фиг, 2о,п), сигнализирующие о нарушении чередования полярностей пар 11, и 00 в сигнале

5 ОТБС.

При наличии синхронизма в первом ОНЧП 21 обнаруживаются нарушения чередования полярностей пар импульсов, происходящих внутри групп из-за ошибок в

0 приеме символов, а во втором ОНЧП 22 - на границах групп. При этом вероятность появления нарушений внутри групп пропорциональна коэффициенту ошибок в системе передачи, а вероятность появления наруше-,.

5 ний на границах групп имеет порядок , т.е. очень высока.

Отклики с выхода второго ОНЧП 22 поступают на счетный вход второго накопителя 11, а с выхода первого ОНЧП 21 на вход

0 сброс. Этим обеспечивается практически бесконечная защищенность устройства синхронизации от сбоев из-за ошибок в ЦСП.

При сбое синхронизма на выходе первого ОНЧП 21 появятся отклики соответствую5 щие нарушениям на границах групп, а на выходе второго ОНЧП 22 - внутри групп. Поэтому второй накопитель НАК 11 быстро накопит заданное количество откликов и на его выходе сформируется сигнал, из которого третий формирователь импульсов (ФИ) 15

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| Преобразователь двоичного кода в трехпозиционный код | 1989 |

|

SU1633499A1 |

| Устройство блочной синхронизации | 1983 |

|

SU1341726A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Преобразователь двоичного кода в трехпозиционный код | 1984 |

|

SU1317675A1 |

| Устройство для передачи и приема цифровых сигналов | 1988 |

|

SU1566499A1 |

| Преобразователь двоичного кода в трехпозиционный код | 1985 |

|

SU1368996A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

Изобретение относится к технике связи, в частности, к технике передачи сигналов с использованием кодов вида ЗВ4В, и может использоваться при разработке цифровых систем передачи информации по электрическим и оптическим кабелям, Целью изобретения является повышение помехоустойчивости за счет минимизации коэффициента размножения ошибок. В декодер, содержащий регенератор 1, управляемый делитель частоты на два 7, блок 12 обнаружения признаков тройного синхросигнала и накопитель 15, введекы блок 2 определения признаков двоичного синхросигнала, формирователь 9 от- носительного троичного сигнала, формирователь 10 троичного сигнала, второй управляемый 8 делитель частоты на два, второй накопитель 11, формирователи 16, 17 и 21 импульсов, параллельные регистры 18 и 22, формирователь двоичного сигнала 19 и умножитель частоты на три. 3 з.п, ф-лы, 5 ил., 12 табл.

| Мурадян A.f.i Гинзбург С.А | |||

| Системы передачи информации по оптическому кабелю | |||

| М.: Связь, 1980,- с | |||

| Способ закалки пил | 1915 |

|

SU140A1 |

| Устройство блочной синхронизации | 1983 |

|

SU1341726A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-02-15—Публикация

1989-12-19—Подача