25

.1 .129035

Изобретени е относится к специалиированным средствам вычислительной ехники и предназначено для опредеения коэффициентов дискретного пребразования Фурье при работе в реаль- j ном масштабе времени.

Целью изобретения является упрощение устройства.

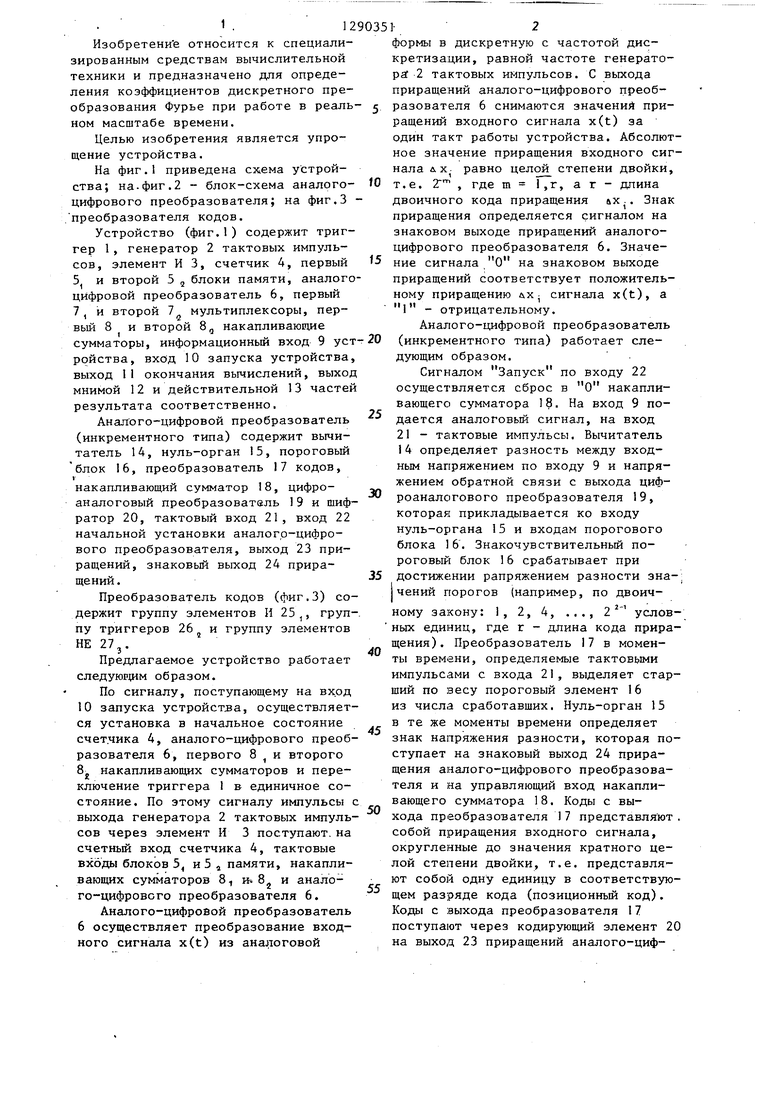

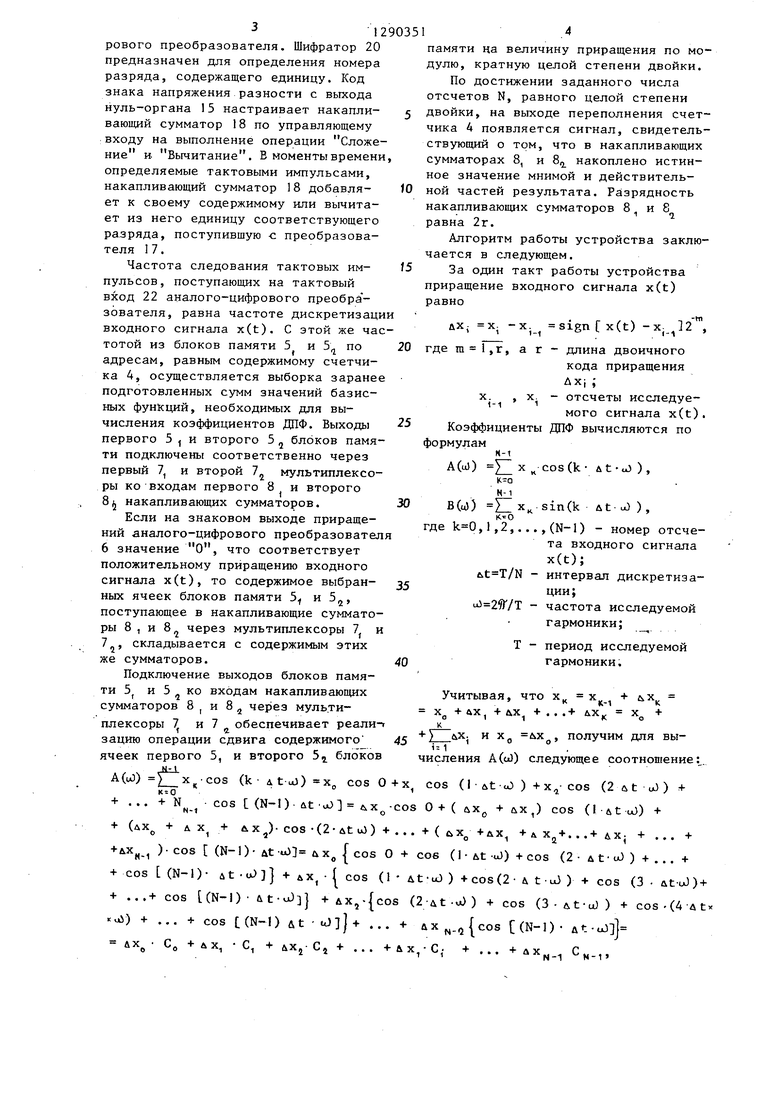

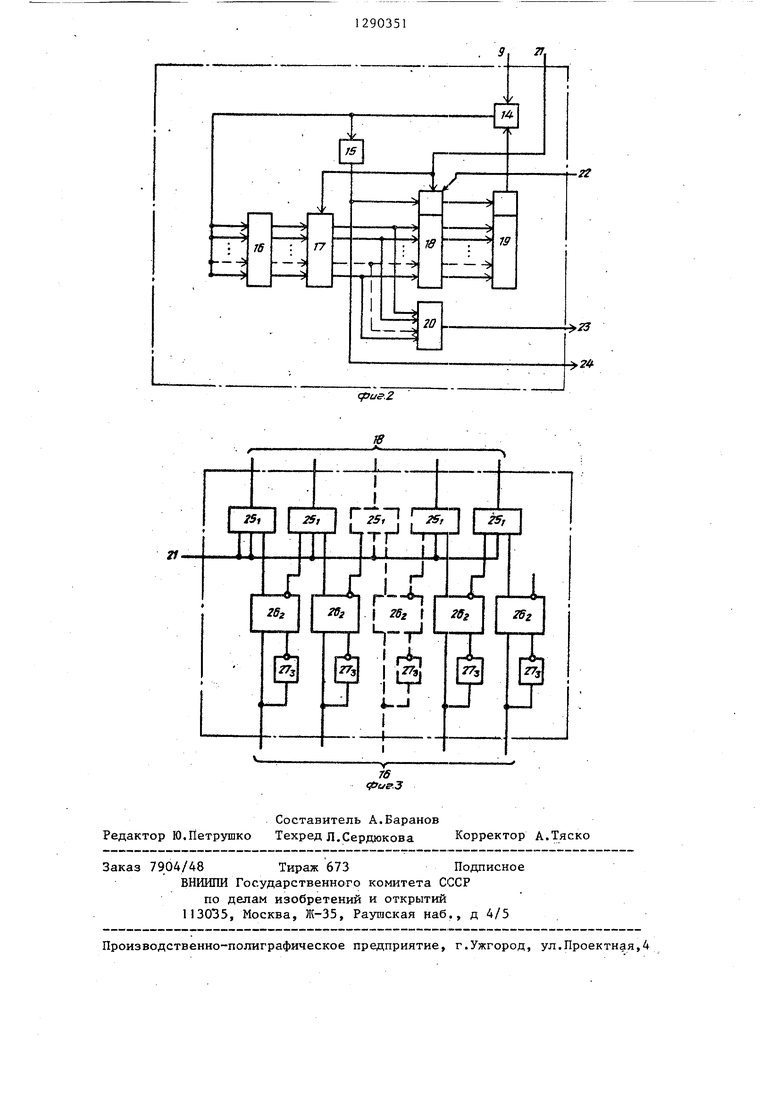

На фиг.1 приведена схема устройства; на-фиг.2 - блок-схема аналого- Ю цифрового преобразователя; на фиг.З - преобразователя кодов.

Устройство (фиг.1) содержит триггер 1, генератор 2 тактовых импульсов, элемент И 3, счетчик 4, первый 5 5 и второй 5 g блоки памяти, аналого- цифровой преобразователь 6, первый 7, и второй 7 мультиплексоры, первый 8 и второй 8,, накапливающие сумматоры, информационный вход 9 уст-20 ройства, вход 10 запуска устройства, выход 11 окончания вычислений, выход мнимой 12 и действительной 13 частей результата соответственно.

Аналого-цифровой преобразователь (инкрементного типа) содержит вычи- татель 14, нуль-орган 15, пороговый блок 16, преобразователь 17 кодов,

г

накапливающий сумматор 18, цифро- у, аналоговый преобразователь 19 и шифратор 20, тактовый вход 21, вход 22 начальной установки аналого-цифрового преобразователя, выход 23 приращений, знаковый выход 24 приращений .

Преобразователь кодов (фиг.З) содержит группу элементов Н 25,, груп-. пу триггеров 26 , и группу элементов НЕ 27,.

Предлагаемое устройство работает следуюрщм образом.

По сигналу, поступающему на вход 10 запуска устройства, осуществляется установка в начальное состояние счет.чика 4, аналого-цифрового преобразователя 6, первого 8 и второго 8jj накапливающих сумматоров и переключение триггера 1 в единичное состояние. По этому сигналу импульсы с выхода генератора 2 тактовых импульсов через элемент И 3 поступают, на счетный вход счетчика 4, тактовые входы блоков 5 и 5 J памяти, накапливающих сумматоров 8, ич8 и аналого-цифрового преобразователя 6.

Аналого-цифровой преобразователь 6 осуществляет преобразование входного сигнала x(t) из аналоговой

45

50

55

5

35

5 0

,

Р

5

0

5

2 формы в дискретную с частотой дискретизации, равной частоте генерато- paf 2 тактовых импульсов. С выхода приращений аналого-цифрового преобразователя 6 снимаются значений приращений входного сигнала x(t) за один такт работы устройства. Абсолютное значение приращения входного сигнала U.K- равно целой степени двойки, т.е. , где m i,r, а г - дпина двоичного кода приращения &х. Знак приращения определяется сигналом на знаковом выходе приращений аналого- цифрового преобразователя 6. Значение сигнала О на знаковом выходе приращений соответствует положительному приращению лх- сигнала x(t), а 1 - отрицательному.

Аналого-цифровой преобразователь (инкрементного типа) работает следующим образом.

Сигналом Запуск по входу 22 осуществляется сброс в О накапливающего сумматора 18, На вход 9 подается аналоговый сигнал, на вход 21 - тактовые импульсы. Вычитатель 14 определяет разность между вход- HbJM напряжением по входу 9 и напряжением обратной связи с выхода циф- роаналогового преобразователя 19, которая прикладывается ко входу нуль-органа 15 и входам порогового блока 16. Знакочувствительный по- роговьш блок 16 срабатывает при достиж€ нии рапряжением разности зна-. чений порогов (например, по двоичному закону: 1, 2, 4, .,., условных единиц, где г - длина кода приращения). Преобразователь 17 в моменты времени, определяемые тактовыми импульсами с входа 21, выделяет старший по весу пороговый элемент 16 из числа сработавших. Нуль-орган 15 в те же моменты времени определяет знак напряжения разности, которая поступает на знаковый выход 24 приращения аналого-цифрового преобразователя и на управляющий вход накапливающего сумматора 18. Коды с выхода преобразователя 17 представляют, собой приращения входного сигнала, округленные до значения кратного целой степени двойки, т.е. представляют собой одну единицу в соответствующем кода (позиционньй код). Коды с выхода преобразователя 17 поступают через кодирующий элемент 20 на выход 23 приращений аналого-цифрового преобразователя. Шифратор 20 предназначен для определения номера разряда, содержащего единицу. Код знака напряжения разности с выхода нуль-органа 15 настраивает накапливающий сумматор 18 по управляющему входу на выполнение операции Сложение и. Вычитание, В моменты времени, определяемые тактовыми импульсами, накапливающий сумматор 18 добавляет к своему содержимому или вычитает из него единицу соответствующего разряда, поступившую -с преобразователя 1 7.

Частота следования тактовых импульсов, поступающих на тактовый вход 22 аналого-цифрового преобра - зователя, равна частоте дискретизации входного сигнала x(t). С этой же частотой из блоков памяти 5 и 5 по адресам, равным содержимому счетчика 4, осуществляется выборка заранее подготовленных сумм значений базисных функций, необходимых для вычисления коэффициентов ДПФ. Выходы первого 5 , и второго 5 блоков памяти подключены соответственно через первый 7, и второй 7 мультиплексо30

ры ко входам первого 8 и второго 8/J накапливающих сумматоров.

Если на знаковом выходе приращений аналого-цифрового преобразователя

6значение О, что соответствует положительному приращению входного сигнала x(t), то содержимое выбран- 35 ных ячеек блоков памяти 5, и 5, поступающее в накапливающие сумматоры 8 , и 8 через мультиплексоры 7 и

7, складывается с содержимым этих

же сумматоров.40

Подключение выходов блоков памяти 5 и 5 ко входам накапливающих сумматоров В , и 8 2 через мультиплексоры 7 7 , обеспечивает реали-г зацию операции сдвига содержимого 45 ячеек первого 5, и второго 5 блоков ,н-. к

памяти ча величину приращения по модулю, кратную целой степени двойки.

По достижении заданного числа отсчетов N, равного целой степени 5 двойки, на выходе переполнения счетчика 4 появляется сигнал, свидетельствующий о том, что в накапливающих сумматорах 8, и 8,j накоплено истинное значение мнимой и действитель- 10 ной частей результата. Разрядность накапливающих сумматоров 8 и 8 равна 2г.

Алгоритм работы устройства заключается в следующем.

5 За один такт работы устройства приращение входного сигнала x(t) равно

йх х. -х. signf x(t) ,

20 где m l,r, a r - длина двоичного

кода приращения Дх; ;

X. , X. - отсчеты исследуемого сигнала x(t).

Коэффициенты ДПФ вычисляются по формулам

М-1

А(и)) X cos (k At cJ),

K-Q N-1

В(ц)) 11 x sin(k ut-u} ),

K O

где ,l,2,...,(N-1) - номер отсчета входного сигнала x(t);

- интервал дискретизации;

- частота исследуемой гармоники;

Т - период исследуемой гармоники.

Учитывая, что х х + X| Хд ftx, + л,х + . . .+ й.х х +

+ и

Ь 1

лХд, получим для вычисления А(о)) следующее соотношение:. ) (k-4tu))x cosO+x cos (I &t о) ) +х.-cos (2ut oJ)

+ N cos (N-1). ut 00 0 + ( йХд + UX,) COS (I -utiA)) +

+ (ДХ + л X + ЛХ)- COS (2-&tlO) + ... + ( c,x +ДХ + Д X,j+...+ iXj + ... + + ЛХ ) COS (N- 1 ) At ) u Хд I COS 0 + сое ( 1 &t -u)) + COS (2- ut-oO) +,.. +

+ COS (N-1)- ut -u)} -f ДХ, 1 COS (1 At-u) ) +cos(2- & t-ix3 ) + cos (3 ut-uJ) + « ...+ COS (N-1) ut-u)} + &x,-{cos (2-it-a) ) + COS (3 - At-tO ) + cos -(4 dt

) + ... + COS (N-1) &t uJ -f ... + ЛХ .{COS (N-1) ut-oJ

AX.

C« 4- Д X,

C, + ЛХ,- C,

памяти ча величину приращения по модулю, кратную целой степени двойки.

По достижении заданного числа отсчетов N, равного целой степени двойки, на выходе переполнения счетчика 4 появляется сигнал, свидетельствующий о том, что в накапливающих сумматорах 8, и 8,j накоплено истинное значение мнимой и действитель- ной частей результата. Разрядность накапливающих сумматоров 8 и 8 равна 2г.

Алгоритм работы устройства заключается в следующем.

За один такт работы устройства приращение входного сигнала x(t) равно

йх х. -х. signf x(t) ,

где m l,r, a r - длина двоичного

кода приращения Дх; ;

X. , X. - отсчеты исследуемого сигнала x(t).

Коэффициенты ДПФ вычисляются по формулам

М-1

А(и)) X cos (k At cJ),

K-Q N-1

В(ц)) 11 x sin(k ut-u} ),

K O

где ,l,2,...,(N-1) - номер отсчета входного сигнала x(t);

- интервал дискретизации;

- частота исследуемой гармоники;

Т - период исследуемой гармоники.

Учитывая, что х х + X| Хд ftx, + л,х + . . .+ й.х х +

+ и

Ь 1

лХд, получим для вычисления А(о)) следующее соотношение cos (I &t о) ) +х.-cos (2ut oJ)

+ лх,-С.

+ лх. С„.,,

5 .12903516

где GO { cos О cos (1 At «J) + . . .+ cos t (N-1) - л t ii) cos (k,, -it lO )0,

- M-1

C { cos (1 Д t цз) +cos(2 л t-u) +.... cos (N-1)- &t oO } 5IIcos (k -ut-o)),

K, i .

N-1

C. I COS (N-2) - ut-uil + COS (N-1) utMx)| cos (k &tu)),

- 1/ я

. C , cos (N-1) &t u) ,

Аналогично HI для B(u3) выполняются следующие вычисления: B(u)) лх„- 3„ +д X,- S, + &x,j- S -ь...+ u X, -S. +,...+ д x ,- S, ,

где S- 1 sin 0 + sin (1 л t -u) ) + sin (2-&t-(jJ )+...+ sin (N-1) & t чх)|

N-1 °I

ZII sin (k At u)) 0,

N-1

r

S, sin(- ut u))+sin(2 &t u))+sin(3 &t-a))+.. .+sin(N-l ) t-u)f nisin(k -bt-u)) ,

f ,5„ sin (2 ut-u )+ sin (3 it-cJ) + sin (4 At )+...+sin t (N-i) д t/

M-1

) n;;sin (k, дta)),

N-a

N-1

(sin L (N-2) л t u) + sin L (N-1.) u. t uJ El sin (k ut u) ) , . .- к«-г«-2

sin sin L (N-)- Таким образом, в блоках памяти 5, и 5 записаны значения сумм 8 и С соответственно для всех значений .30

Формула изобрете. ния

нуль-орган, вычитатель, третий накапливающий сумматор, цифроаналого- вый преобразователь и шифратор, выход которого подключен к управляющим входам первого и второго мультиплексоров, выходы которых подключены к информационным входам соответственно первого и второго накапливающих сумматоров, знаковые входы которых объединены с знаковьм входом третьего накапливающего сумматора и подключены к выходу нуль-органа, вход которого объединен с входом порогового блока и подключен к выходу вычитателя, первый вход которого подключен к выходу цифроаналогового преобразователя, вход которого подключен к выходу третьего накапливают 1дего сумматора, информационный вход которого соединен с входом шифратора и подключен к выходу преобразователя кодов, информационный вход которого подключен к выходу порогового блока, информационньм выход счетчика подключен к адресным входам первого и второго блоков постоянной памяти, выходы которых подключены к информационным входам соответственно первого и второго мультиплексоров, выход элемента И подключен к управляющим входам первого и второго блоков постоянной памяти и тактовым входам преобразователя кодов и третьего на

I. Устройство для вычисления ко- Iэффициёнтов Фурье, содержащее триггер, выход которого подключен к первому входу элемента И, выход которого подключен к тактовым входам. первого и второго накапливающих сумматоров и счетному входу счетчика, выход переноса которого является выходом окончания вычислений устрой- ства и подключен к входу установки в ноль триггера, вход установки в ,единицу которого соединен с устано- вочными входами счетчика, первого и второго накапливающих сумматоров и является входом запуска устройства, второй вход элемента И подключен к выходу генератора тактовых им- пульсов, а выходы первого и второго накапливающих сумматоров являются выходами соответственно реальной и мнимой частей результата устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит два блока постоянной памяти, два мультиплексора, пороговый блок, преобразователь кодов.

0

5

0 5 0 г

нуль-орган, вычитатель, третий накапливающий сумматор, цифроаналого- вый преобразователь и шифратор, выход которого подключен к управляющим входам первого и второго мультиплексоров, выходы которых подключены к информационным входам соответственно первого и второго накапливающих сумматоров, знаковые входы которых объединены с знаковьм входом третьего накапливающего сумматора и подключены к выходу нуль-органа, вход которого объединен с входом порогового блока и подключен к выходу вычитателя, первый вход которого подключен к выходу цифроаналогового преобразователя, вход которого подключен к выходу третьего накапливают 1дего сумматора, информационный вход которого соединен с входом шифратора и подключен к выходу преобразователя кодов, информационный вход которого подключен к выходу порогового блока, информационньм выход счетчика подключен к адресным входам первого и второго блоков постоянной памяти, выходы которых подключены к информационным входам соответственно первого и второго мультиплексоров, выход элемента И подключен к управляющим входам первого и второго блоков постоянной памяти и тактовым входам преобразователя кодов и третьего на.712

капливающего сумматора, установочный вход которого подключен к входу запуска устройства, информационным входом которого является второй вход вьгчитателя. .

2. Устройство по п.1, о т л и - чающееся тем, что преоб- разователь кодов содержит N (N - разрядность кодов) элементов .НЕ, N триггеров и N элементов И, причем выход i-ro (i 1 ,N) элемента НЕ подключен к первому установочному входу 1-го триггера, прямой выход которого подключен к перво

1 8 ;

му входу i-ro элемента И, инверсный выход j-ro (j 1,N-I) триггера подключен к второму входу (j+1)- го элемента И, а второй установочный вход i-ro триггера соединен с входом i-ro элемента И, третьи входы всех элементов И соединены с вторым входом первого элемента И и являются тактовым входом преобразователя, выходы всех элементов И объединены и являются выходом преобразователя, вторые установочные входы всех триггеров объединены и являются информационным входом преобразователя.

70

f

л

:( f

f Si/

81

Xb Nk

8

f12

cpuffl

/7J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1332330A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1273944A1 |

| Устройство для фильтрации симметричных составляющих | 1985 |

|

SU1343362A1 |

| Преобразователь перемещения в код | 1988 |

|

SU1531221A1 |

| Устройство для выполнения преобразования Фурье | 1987 |

|

SU1424027A1 |

| Устройство для многоканального интерполирования функций | 1986 |

|

SU1377878A1 |

| Функциональный преобразователь угла поворота вала в код | 1982 |

|

SU1080174A1 |

| Цифровой измеритель симметричных составляющих | 1985 |

|

SU1255964A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

Изобретение относится к специализированным средствам йычислительной техники, предназначено для определения коэффициентов дискретного преобразования Фурье при работе в реальном масштабе времени. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что устройство для вычисления коэффициентов Фурье содержит триггер, генератор тактовых импульсов, элемент И, счетчик, два блока постоянной памяти, два мультиплексора, три накапливающих сумматора, вычислитель, нуль-орган, цифроаналоговый преобразователь, шифратор, преобразователь кодов, пороговый блок и соответствующие связи между узлами устройства. 1 з.п. ф-лы, 3 ил. с (Л to со о 00 ел

Составитель А.Баранов Редактор Ю.Петрушко Техред л.Сердюкова Корректор А.Тяско

Заказ 7904/48 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д 4/5

Производственио-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Устройство для вычисления коэффициентов фурье | 1975 |

|

SU537349A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ю.М.Смирнов, Г.Н.Воробьев, Проектирование специализированных информационно-вычислительных систем | |||

| М.: Высшая школа, 1984, с | |||

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

Авторы

Даты

1987-02-15—Публикация

1985-07-22—Подача