Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах для программного управления технологическими процессами, например, в системах числового программного управления.

Цель изобретения - расширение области применения устройства.

Сущность изобретения заключается в сокращении объема памяти многоальтернативного ветвления и расширении области применения устройства путем введения дисциплины предварительного кодирования членов совершенной дизъюнктивной нормальной формы (СДНФ) реализуемой системы булевых функций или кодов вариантов

ветвления рангов п , где п - разрядность обрабатываемых логических условий.

Суть новой дисциплины заключается в вводе в группу регистров информации членов. СД1№ (подчленов СДНФ), кодов вариантов (части кодов вариантов) ветвления при инициализации, либо при перенастройке устройства1, в сравнении этой информации с информацией на группе старших разрядов логических условий и формировании сигнала идентификации одной из схем сравнения группы схем сравнения, либо таковой сигнал на формируется; в формировании на выходе группы элементов И с тремя состояниями на выходе кода идентификации информации, либо единственного кода меидентифи- кации , в реализации дисциплины многоальтернативного ветвления, аналогичной известной, причем часть разрядов (младшие разряды) логических условий через мультиплексор непосредственно приводит в дальнейшем к адресации памяти, а другая часть (старшие разряды), подвергнутая предварительному кодированию, адресует в дальнейшем память косвенно, в соответствии с присвоенными группой входов старших адресов ветвления кодами.

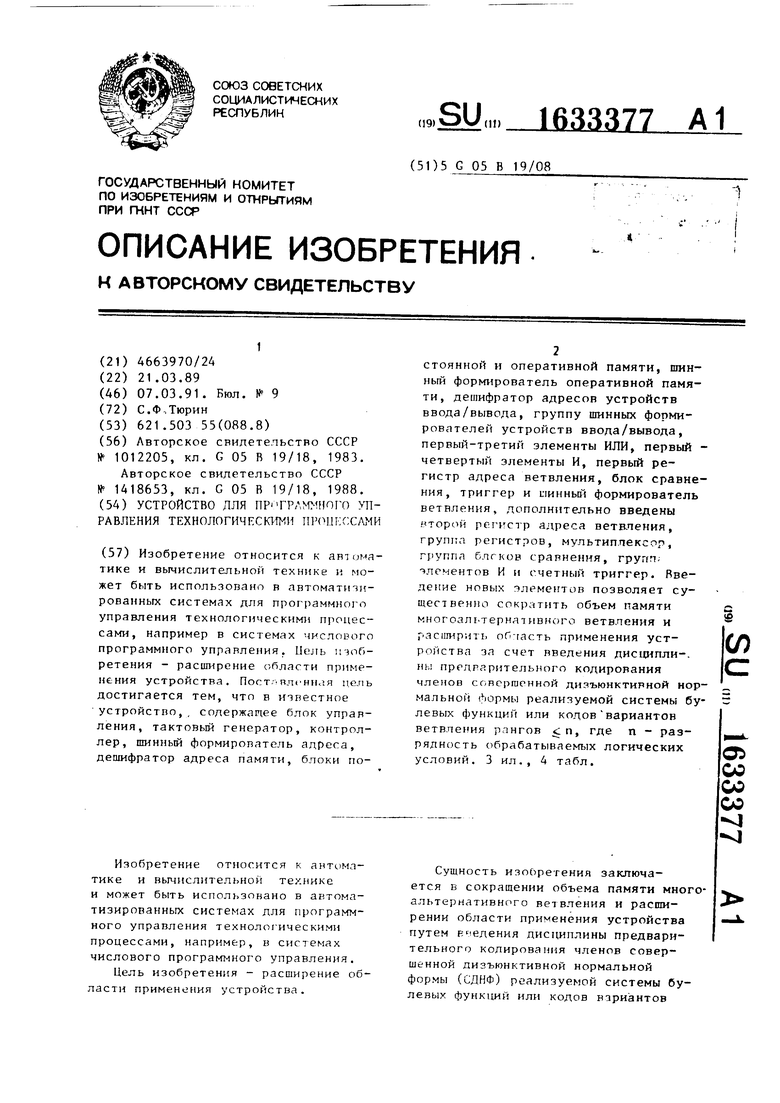

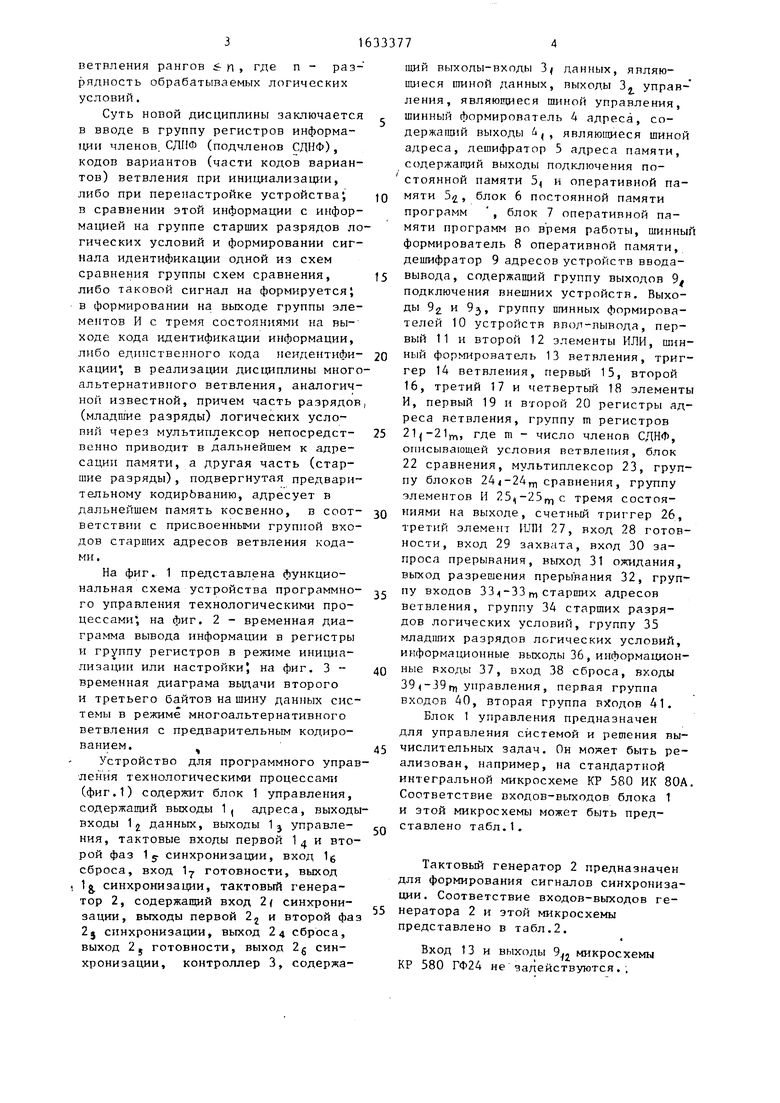

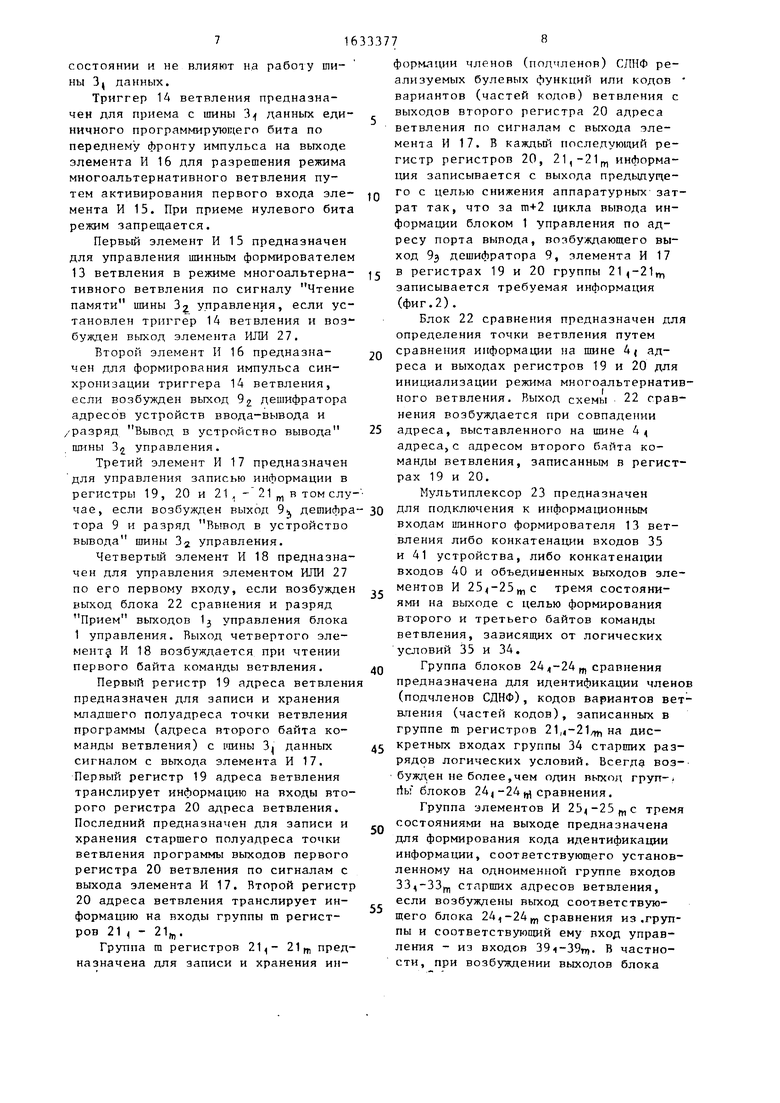

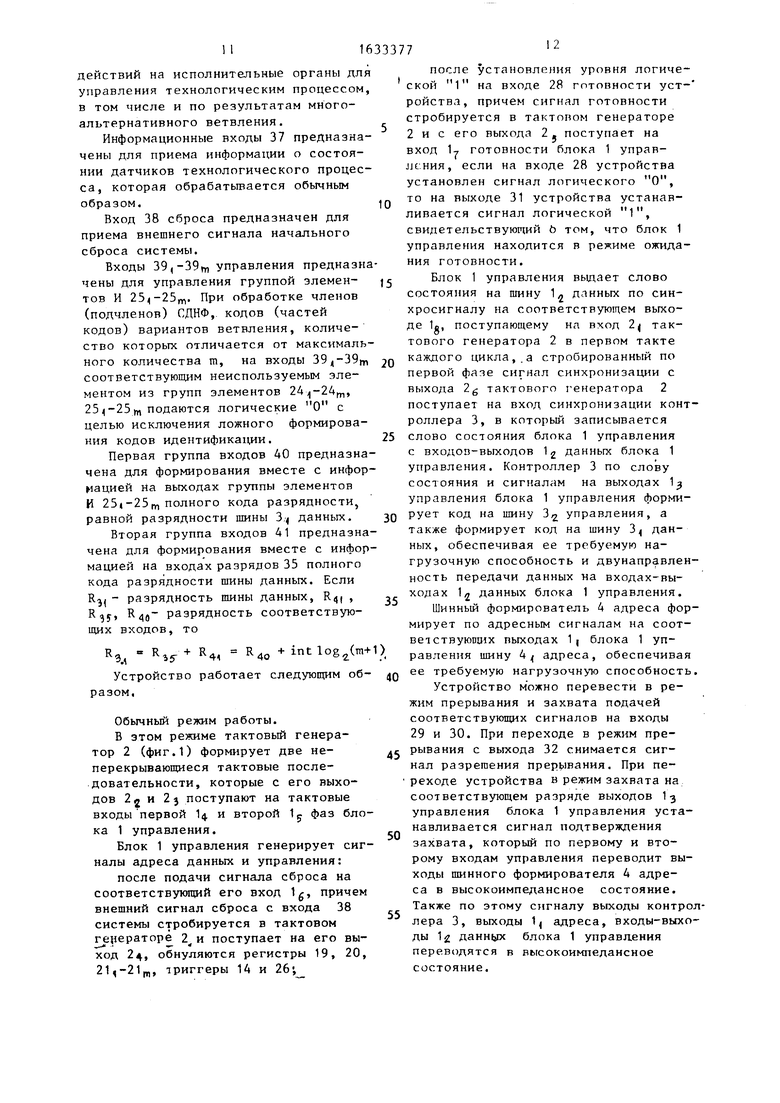

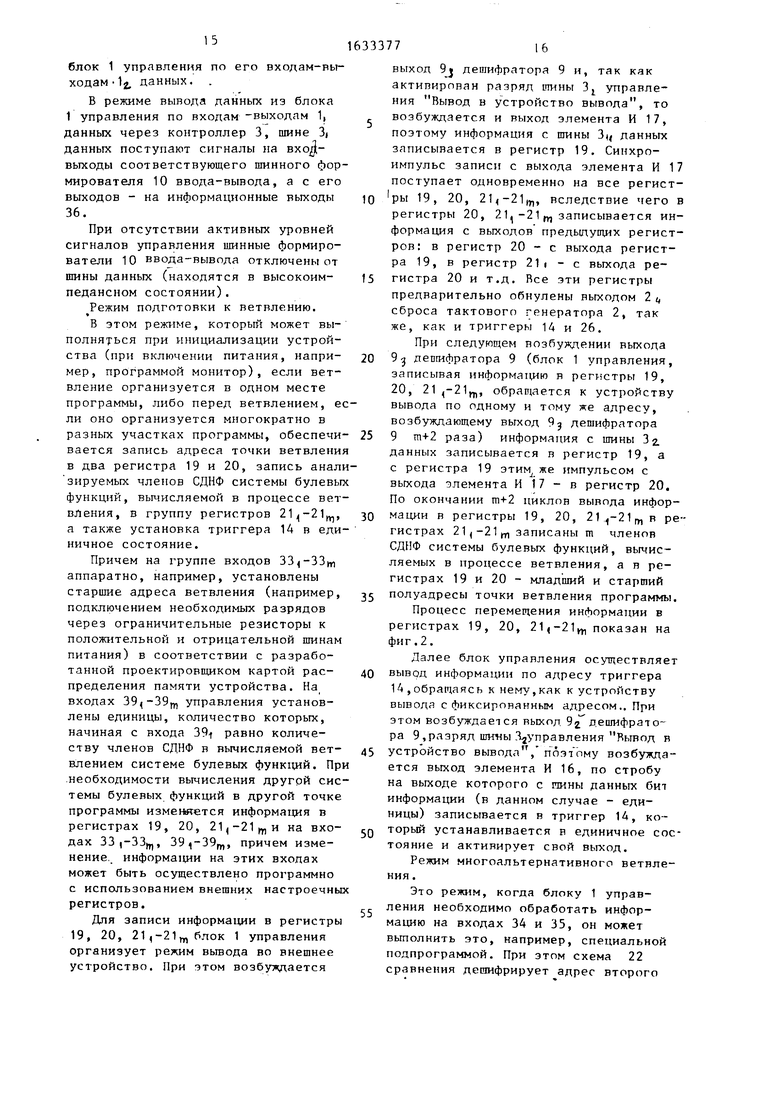

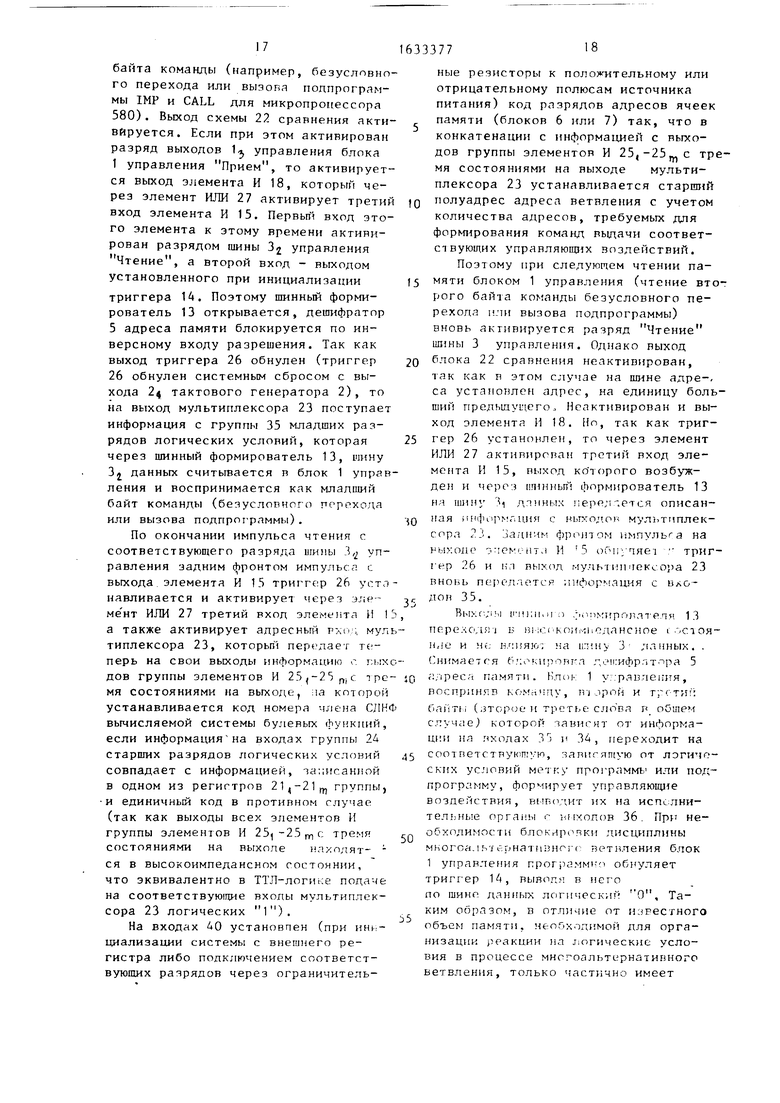

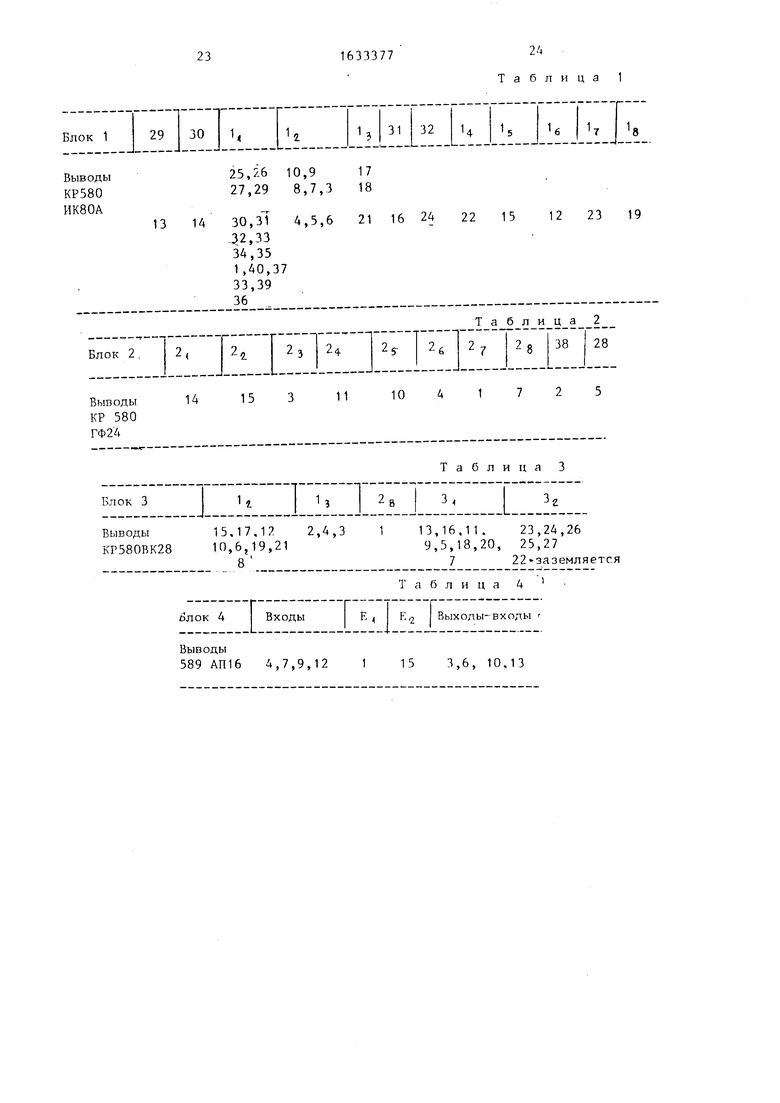

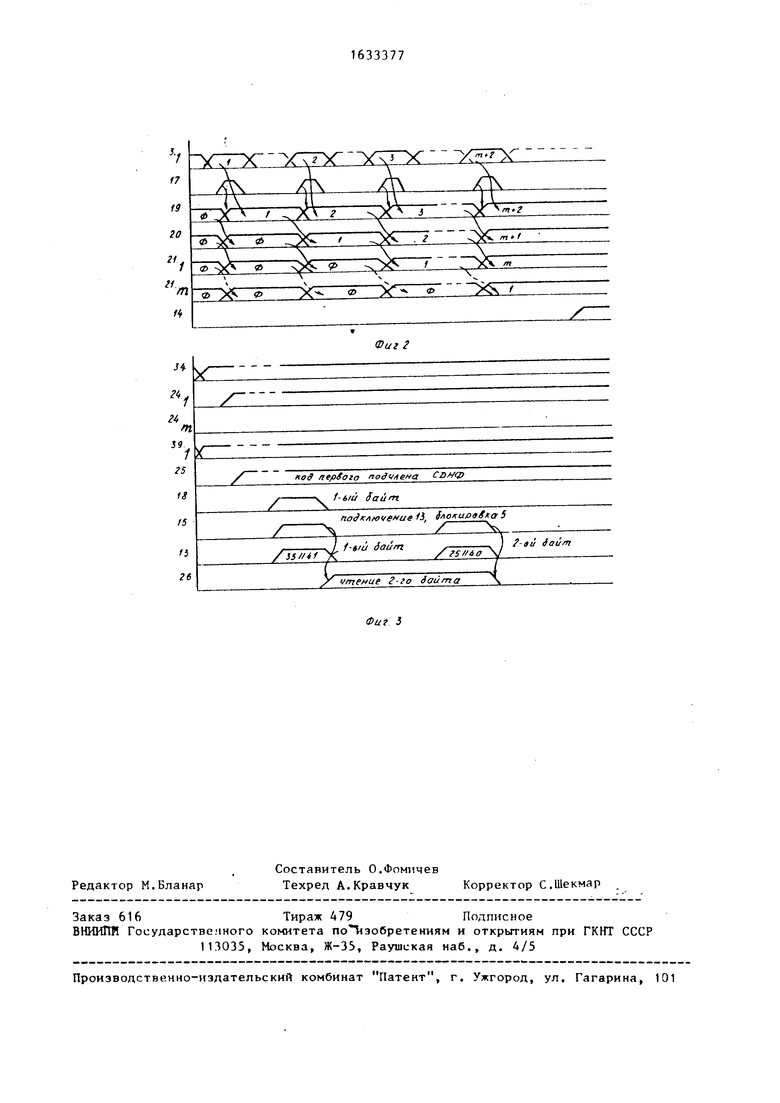

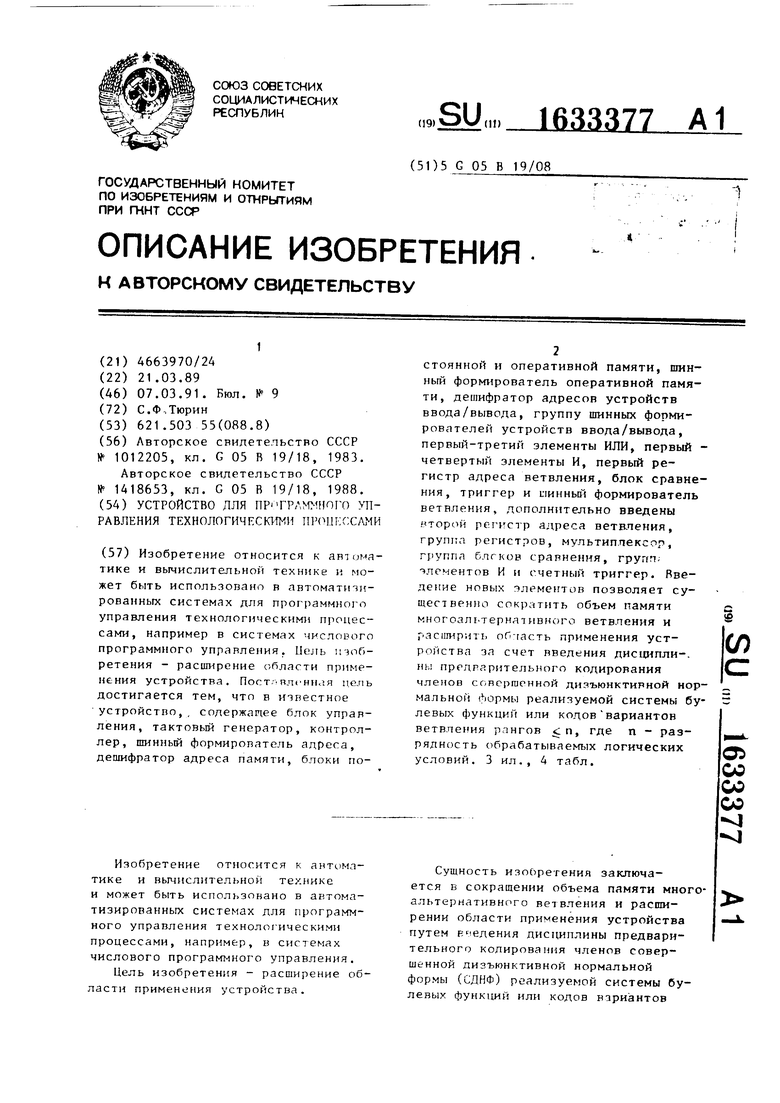

На фиг. 1 представлена функциональная схема устройства программного управления технологическими процессами , на фиг. 2 - временная диаграмма вывода информации в регистры и группу регистров в режиме инициализации или настройки на фиг. 3 - временная диаграма выдачи второго и третьего байтов на шину данных системы в режиме многоальтернативного ветвления с предварительным кодированием. ,

Устройство для программного управления технологическими процессами (фиг.1) содержит блок 1 управления, содержащий выходы 1 адреса, выходы входы 12 данных, выходы 1j управления, тактовые входы первой 1 и второй фаз 1 у синхронизации, вход 1g сброса, вход 17 готовности, выход 1 1 синхронизации, тактовый генератор 2, содержащий вход 2( синхронизации, выходы первой 2г и второй фаз 2j синхронизации, выход 2$ сброса, выход 25 готовности, выход 2g синхронизации, контроллер 3, содержащий выходы-входы 3 данных, являющиеся шиной данных, выходы 3 управления, являющиеся шиной управления,

шинный формирователь 4 адреса, содержащий выходы являющиеся шиной адреса, дешифратор 5 адреса памяти, содержащий выходы подключения постоянной памяти 5, и оперативной памяти 5, блок 6 постоянной памяти программ , блок 7 оперативной памяти программ во время работы, шинный формирователь 8 оперативной памяти, дешифратор 9 адресов устройств ввода5 вывода, содержащий группу выходов 9, подключения внешних устройств. Выходы 9г и 9з, группу шинных формирователей 10 устройств впол-пывода, первый 11 и второй 12 элементы ИЛИ, шин0 ный формирователь 13 ветвления, триггер 14 ветвления, первый 15, второй 16, третий 17 и четвертый 18 элементы И, первый 19 и второй 20 регистры адреса ветвления, группу m регистров

5 21|-21т, где т - число членов СДНФ, описывающей условия ветвления, блок 22 сравнения, мультиплексор 23, группу блоков сравнения, группу элементов И 25 -25тс тремя состоя0 ниями на выходе, счетный триггер 26, третий элемент ИЛИ 27, вход 28 готовности, вход 29 захвата, вход 30 запроса прерывания, выход 31 ожидания, выход разрешения прерывания 32, груп5 ПУ входов 33ц-33mстарших адресов ветвления, группу 34 старших разрядов логических условий, группу 35 младших разрядов логических условий, информационные выходы 36, информацион0 ные входы 37, вход 38 сброса, входы управления, первая группа входов 40, вторая группа входов 41.

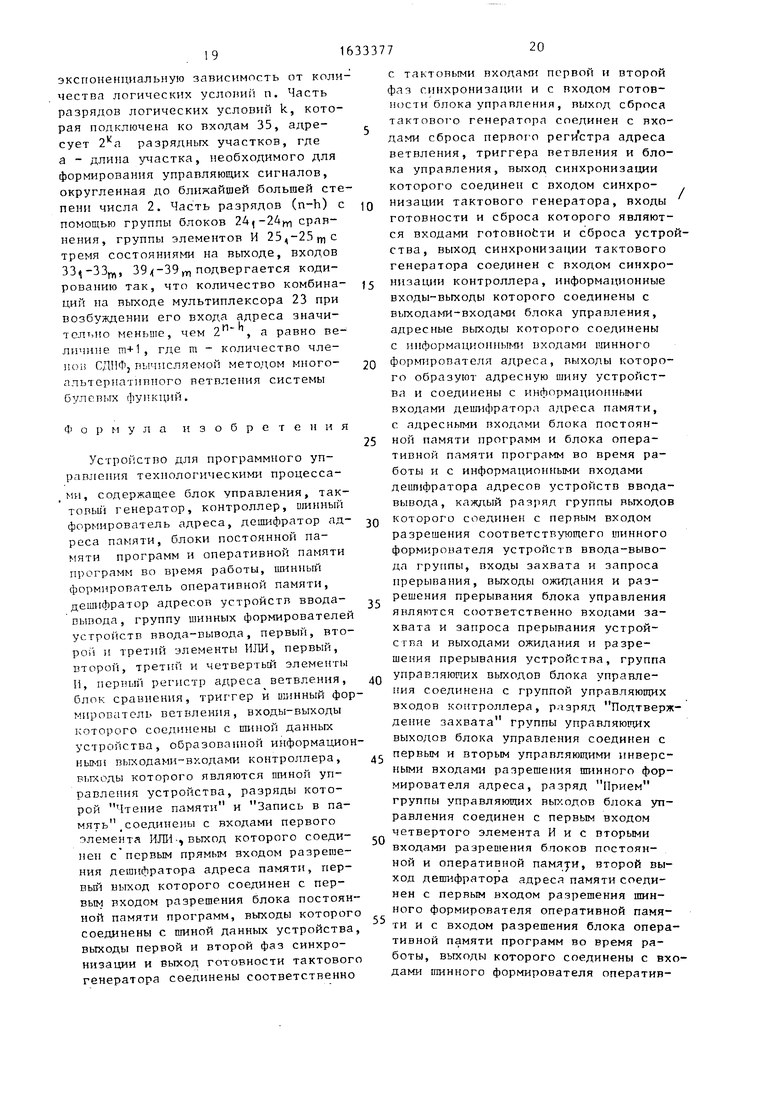

Блок 1 управления предназначен для управления системой и решения вы5 числительных задач. Он может быть реализован, например, на стандартной интегральной микросхеме КР 580 ИК 80А. Соответствие входов-выходов блока 1 и этой микросхемы может быть пред50

ставлено табл.1.

Тактовый генератор 2 предназначен для формирования сигналов синхронизации. Соответствие входов-выходов ге- нератора 2 и этой микросхемы представлено в табл.2.

Вход 13 и выходы 9 микросхемы КР 580 ГФ24 не задействуются.,

Контроллер 3 предназначен для формирования шины управления и для организации двунаправленной передачи данных по шине 3 данных.

Соответствие входов-выходов этой микросхемы и входов-выходов контроллера 3 может быть представлено табл.3.

входы .шинного формирователя В оперативной памяти и с его входов-выходов на шину 3, данных системы.

Запись в память.

При этом активирован только первый вход разрешения шинного формирователя. Данные с шины 3| данных системы поступают на его входы-выходы,

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для обмена данными | 1984 |

|

SU1239724A2 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах для программного управления технологическими процессами, например в системах числового программного управления. Цель изобретения - расширение области применения устройства. Поставленная цель достигается тем, что в известное устройство,, содержащее блок управления, тактовый генератор, контроллер, шинный формирователь адреса, дешифратор адреса памяти, блоки постоянной и оперативной памяти, шинный формирователь оперативной памяти, дешифратор адресов устройств ввода/вывода, группу шинных формирователей устройств ввода/вывода, первый-третий элементы ИЛИ, первый - четвертый элементы И, первый регистр адреса ветвления, блок сравнения, триггер и шинный формирователь ветвления, дополнительно введены .«торой регистр адреса ветвления, группа регистров, мультиппексор, группа блгков сравнения, групп- элементов И и счетный триггер. Введение новых элементов позволяет существенно сократить объем памяти многоальтернативного ветвления и расширить об-гасть применения устройства за счет введения дисципли-. ни пррдрарительного кодирования членов совершенной дизъюнктивной нормальной реализуемой системы булевых функций или кодов вариантов ветвпения рангов :п, где п - разрядность обрабатываемых логических условий. 3 ил., 4 табл. SS (Л о со со со i j

Шинный формирователь 4 адреса пред-jg а с выходов - на входы данных блока 7

назначен для увеличения нагрузочной способности шины 4( адреса и для отключения своих входов-выходов от нее путем перевода их в высокоимпедансны состояния по сигналу Подтверждение захвата, который поступает на его первый и второй разрешающий входы от блока 1 управления.

Шинный формирователь 4 адреса может быть реализован, например, на стандартных интегральных микросхемах 589 АП16.

Соответствие входов-выходов блока 4 и входов-выходов этой микросхемы может быть представлено табл.4.

Выходы 2, 5, 11, 14 не используются.

Дешифратор 5 адреса памяти предназначен для дешифрации информации на шине 4| адреса по разрешающему гиг- налу на его первом входе управления, если второй неактивирован, и формирования сигналов выборки кригталлч для подключения блоков постоянное п или оперативной 7 памяти.

Блок 6 постоянной памяти гр- дназ- начен для долговременного х- ачення программ и данных. Блок 7 опер-пия- ной памяти предназначен для хрлн -нин программ, данных и для записи их только во время работы устройства, а также для организации стека.

Режим работы блока 7 оперативной памяти определяется сочетанием разрешающего сигнала и сигнала записи.

Шинный формирователь 8 оперативной памяти предназначен для увеличения нагрузочной способности шины 3| данных системы и для организации подключения к ней входов и выходов блок 7 оперативной памяти в зависимости о управляющих сигналов в еледую где х режимах.

Чтение памяти.

При этом активированы первьй и второй входы разрешения шинного формирователя 8. Данные с выходов блока 7 оперативной памяти поступают на

5

0

5

0

5

0

5

0

5

оперативной памяти,,

Дешифратор 9 адресов устройств ввода-вывода предназначен д))я дешифрации по разрешающему сигналу адресной информации на шине 4 t адреса системы для подключения к шине 3 данных для подключения к шине 3 i данных соответствующего шинного формирователя 10 ввода-вывода по входам-выходам, для управления элементами И 17 и 16.

Шинные формирователи 10 ввода/вывода предназначены для увеличения нагрузочной способности шины 3/ данных системы, для ввода данных с информационных входов 37, при этом активированы оба разрешающих входа одного из шинных формирователей 10 ввода-вывода, который пнбран дешифратором 9 .ч устройств ввода-вывода, г также для вывода данных из блока 1 уп- ра;лемия на информационные вых,: 36. При j-гом активирован первый разрешающий вход одного из ыинных формирователей 10 внода-рнпода соответствую- вдш выходом дс-шифр.т ора 9 адресов уст роист в вьода- гчлшда .

Первый -элемент 11ТГИ 1 1 предназначен для выработки разрешающего сиг- нгла i-a порвый управления детиф- 5 адрес i памяти, если на шине Ъq управления имеется один из сигналов Чтение памяти, Запись в память.

Второй элемент ИЛИ 12 предназначен- для выработки сигнала для дешифратора 9 адресов устройств ввода-вывода, если на тине Ъ управления имеется один из сигналов Вывод в устройство вывода, Ввод из устройства впопа.

Шинный формирователь 13 ветвления предназначен для увеличения нагрузочной способности шины 3| данных и подключения к ней сигналов с выхода мультиплексора 23 при активировании его входа разрешения. В противном случае выходы шинного формирователя 13 находятся в высокоимпедансьом

состоянии и не влияют на работу шины 3 данных.

Триггер 14 ветвления предназначен для приема с шины 3 данных единичного программирующего бита по переднему фронту импульса на выходе элемента И 16 для разрешения режима многоальтернативного ветвления путем активирования первого входа элемента И 15. При приеме нулевого бита режим запрещается.

Первый элемент И 15 предназначен для управления шинным формирователем

16333778

формации членов (подчленов) СЛНФ реализуемых булевых функций или кодов вариантов (частей кодов) ветвления с выходов второго регистра 20 адреса ветвления по сигналам с выхода элемента И 17. В каждый последующий регистр регистров 20, 21,-21т информация записывается с выхода предыдущего с целью снижения аппаратурных затрат так, что за т+2 цикла вывода информации блоком 1 управления по адресу порта вывода, возбуждающего выход 9з дешифратора 9, элемента И 17

10

13 ветвления в режиме многоальтерна- 15 в регистрах 19 и 20 группы

тивного ветвления по сигналу Чтение памяти шины Ъ управления, если установлен триггер 14 ветвления и возбужден выход элемента ИЛИ 27.

Второй элемент И 16 предназначен для формирования импульса синхронизации триггера 14 ветвления, если возбужден выход 92 дешифратора адресов устройств ввода-вывода и /разряд Вывод в устройство вывода шины Зг управления.

Третий элемент И 17 предназначен для управления записью информации в регистры 19, 20 и 21,,- 21 m в том слу- 20

25

записывается требуемая информация (фиг.2).

Блок 22 сравнения предназначен определения точки ветвления путем сравнения информации на шине 4( а реса и выходах регистров 19 и 20 инициализации режима многоальтерн ного ветвления. Выход схемы 22 с нения возбуждается при совпадении адреса, выставленного на шине 4 адреса,с адресом второго байта ко манды ветвления, записанным в рег рах 19 и 20.

Мультиплексор 23 предназначен

чае, если возбужден выход 9$ дешифра- 30 Для подключения к информационным

тора 9 и разряд Вывод в устройство вывода шины 32 управления.

Четвертый элемент И 18 предназначен для управления элементом ИЛИ 27 по его первому входу, если возбужден выход блока 22 сравнения и разряд Прием выходов 13 управления блока 1 управления. Выход четвертого элемента И 18 возбуждается при чтении первого байта команды ветвления.

Первый регистр 19 адреса ветвления предназначен для записи и хранения младшего полуадреса точки ветвления программы (адреса второго байта команды ветвления) с шины 3 данных сигналом с выхода элемента И 17. Первый регистр 19 адреса ветвления транслирует информацию на входы второго регистра 20 адреса ветвления. Последний предназначен для записи и хранения старшего полуадреса точки ветвления программы выходов первого регистра 20 ветвления по сигналам с выхода элемента И 17. Второй регистр 20 адреса ветвления транслирует информацию на входы группы га регистров 21 - 21Й.

Группа m регистров 21п предназначена для записи и хранения ин35

40

входам шинного формирователя 13 в вления либо конкатенации входов 3 и 41 устройства, либо конкатенаци входов 40 и объединенных выходов ментов И 25 -25тс тремя состоян ями на выходе с целью формировани второго и третьего байтов команды ветвления, зависящих от логически условий 35 и 34.

Группа блоков 24„-24m сравнени предназначена для идентификации ч (подчленов СДНФ), кодов вариантов вления (частей кодов), записанных группе m регистров 21,«-21 на дис 45 кретных входах группы 34 старших рядов логических условий. Всегда бужден не более,чем один выход тру пы блоков сравнения.

Группа элементов И т состояниями на выходе предназначе для формирования кода идентификац информации, соответствующего уста ленному на одноименной группе вхо 33,-33т старших адресов ветвления если возбуждены выход соответству щего блока 24,-24m сравнения из .г пы и соответствующий ему вход упр ления - из входов 39i-39n). В част сти, при возбуждении выходов блок

50

55

0

5

записывается требуемая информация (фиг.2).

Блок 22 сравнения предназначен для определения точки ветвления путем сравнения информации на шине 4( адреса и выходах регистров 19 и 20 для инициализации режима многоальтернативного ветвления. Выход схемы 22 сравнения возбуждается при совпадении адреса, выставленного на шине 4 адреса,с адресом второго байта команды ветвления, записанным в регистрах 19 и 20.

Мультиплексор 23 предназначен

Для подключения к информационным

входам шинного формирователя 13 ветвления либо конкатенации входов 35 и 41 устройства, либо конкатенации входов 40 и объединенных выходов элементов И 25 -25тс тремя состояниями на выходе с целью формирования второго и третьего байтов команды ветвления, зависящих от логических условий 35 и 34.

Группа блоков 24„-24m сравнения предназначена для идентификации членов (подчленов СДНФ), кодов вариантов ветвления (частей кодов), записанных в группе m регистров 21,«-21 на дис- кретных входах группы 34 старших разрядов логических условий. Всегда возбужден не более,чем один выход труп- пы блоков сравнения.

Группа элементов И тремя состояниями на выходе предназначена для формирования кода идентификации информации, соответствующего установленному на одноименной группе входов 33,-33т старших адресов ветвления, если возбуждены выход соответствующего блока 24,-24m сравнения из .группы и соответствующий ему вход управления - из входов 39i-39n). В частности, при возбуждении выходов блока

24 ,,-24 сравнения группы на объединенных выходах группы элементов И 25,-25тс тремя состояниями на выко- де могут выставляться коды (установленные предварительно на входах 33ц- 33), веса которых соответствуют номеру блока сравнения, считая с нулевого, группа блоков 241-24tnc возбужденным выходом (О,1,2...т-1). Разрядность выходов группы элементов равна величине intlop, 2(го+1) , где int - ближайшее большее целое число.

1 При невозбуждении выхода на одном из блоков 24,-24т сравнения группы онуленные выходы группы элементов И 25(-25ynнаходятся в высокоимпеданс- ном состоянии, что воспринимается соответствующим входом мультиплек- сора 23 как в ТТЛ-логике - логической 1.

Счетный триггер 26 предназначен для управления мультиплексором 23 по сигналам с выхода элемента И 15. При чтении блоком 1 управления первого байта команды ветвления (т.е. команды перехода, имеющей трехбайтовую структуру, например команды IMP, CALL, LDA и др. для микропроцессора 580) счетный триггер 26 обнулен начальным сбросом. Адрес второго баптл такой команды ветвления деши рируе; блок 22 сравнения. Импульс ч-:ени второго байта по его заднему фроь гу с выхода элемента И 15 запоминает счетный триггер 26, обеспечивая переключение мультиплексора 23 и управление элементом И 15 через э м - мент ИЛИ 27, что необходим. для ключения третьего байта через шинный формирователь 13, так как адрес. третьего байта не дешифрируется блоком 22 сравенния. По окончании импульса чтения третьего байта триггер 26 обнуляется.

Третий элемент ИЛИ 27 преднаэна- чен для управления элементом И 15 по его третьему входу либо сигналом с выхода элемента И 18 (чтение второго байта команды ветвления), либо сигналом с выхода счетного триггера 26 (чтение третьего байта команды вления).

Вход 28 готовности предназначен для приема внешнего-сигнала готовности, например,с внешних медленнодействующих накопителей. Вход захвата лредназ- начен для приема внешнего сигнала заЮ

5 0

5

0.

5

0

5

0

5

хвата,, например, в внешних быстродействующих накопителях.

Вход 30 запроса прерывания предназначен для приема внешнего сигнала прерывания, например, при аварии электропитания.

Выход 31 ожидания предназначен для формирования сигнала ожидания, являющегося реакцией на невозбужденный вход 28 готовности.

Выход 32 разрешения прерывания предназначен для формирования сигнала разрешения прерывания с внутреннего триггера блока 1 управления. Группа входов 33,, -33 т старших адресов ветвления предназначена для формирования кода идентификации члена (подключена) СДНФ реализующей системы булевых функций или кода (части кода) варианта ветвления на объединенных выходах элементов И 25/)-25rt. Информация на входах 33ц- 33 может быть установлена жестко путем распайки (подключением к шинам Плюс, Минус источника питания через ограничительные резисторы) либо мягко - с выходов регистров, ко- торые также могут программироваться блоком 1 управления с помощью технических средств, внешних по отноке- нию к уетройстяу.

Разрядность БХОДМП t лвна intlog 4U ,

Группа 34 гтярпи/ разрядов логических условий пред назначена для подключения г оптво тиумней части раэ- ря.оп лпгнче к;;, условий к первым, опъс ди н-мп ь - группам входов блоков 2 (-24 ,,, сравнения . Логические услони - .. т быть как внешними, т.е. непосредственно состояние дискретных д;м И1:ол технологического процесгч, так и внутренними - полученными в резупьтше работы блока 1 управления к выведенные на регистры, например, для получения в дальнейшем некоторых автоматных отображений.

Группа 35 мласгаих разрядов логических условий предназначена для приема соответствующей части разрядив логических условий, которые могут быть такими же, как описано. Информация на входах 34 и 35 изменяется с такой периодичностью, что блок 1 управления успевает обрабатывать ее любые и::мрнения.

Информационные выходы 36 предназначены для выдачи управляющих воз-

действий на исполнительные органы для управления технологическим процессом, в том числе и по результатам многоальтернативного ветвления.

Информационные входы 37 предназначены для приема информации о состоянии датчиков технологического процесса, которая обрабатывается обычным образом.

Вход 38 сброса предназначен для приема внешнего сигнала начального сброса системы.

Входы 39,-39т управления предназначены для управления группой элемен- тов И . При обработке членов (подчленов) СДНФ, кодов (частей кодов) вариантов ветвления, количество которых отличается от максимального количества га, на входы 39д-39т соответствующим неиспользуемым элементом из групп элементов 241-24т, подаются логические О с целью исключения ложного формирования кодов идентификации.

Первая группа входов 40 предназначена для формирования вместе с инфор- иацией на выходах группы элементов И полного кода разрядности, равной разрядности шины 34 данных.

Вторая группа входов 41 предназначена для формирования вместе с информацией на входах разрядов 35 полного кода разрядности шины данных. Если R - разрядность шины данных, R4( , RH R49 разрядность соответствующих входов, то

R,

RVT +

R,

Шинный формирователь 4 адреса фор мирует по адресным сигналам на соответствующих выходах 1| блока 1 упЧА 4° 62. Устройство работает следующим образом,

Обычный режим работы.

В этом режиме тактовый генератор 2 (фиг.1) формирует две неперекрывающиеся тактовые последовательности, которые с его выходов 2 и 2j поступают на тактовые входы первой 1ф и второй 1 фаз блока 1 управления.

Блок 1 управления генерирует сигналы адреса данных и управления:

после подачи сигнала сброса на соответствующий его вход 1, причем внешний сигнал сброса с входа 38 системы стробируется в тактовом генераторе 2t и поступает на его выход 24, обнуляются регистры 19, 20, 21,-21т, триггеры 14 и 26,

4о + int 1°§2. + .. равления шину 4 ,, адреса, обеспечивая

40

45

50

55

ее требуемую нагрузочную способность

Устройство можно перевести в режим прерывания и захвата подачей соответствующих сигналов на входы 29 и 30. При переходе в режим прерывания с выхода 32 снимается сигнал разрешения прерывания. При переходе устройства в режим захвата на соответствующем разряде выходов 1 управления блока 1 управления устанавливается сигнал подтверждения захвата, который по первому и второму входам управления переводит выходы шинного формирователя 4 адреса в высокоимпедансное состояние. Также по этому сигналу выходы контро лера 3, выходы 1 адреса, входы-выхо ды 1g данных блока 1 управления переводятся в высокоимпедансное состояние.

0

5

30

20

25

35

после установления уровня логиче- 1 ской 1 на входе 28 готовности уст- ройства, причем сигнал готовности стробируется в тактовом генераторе 2 и с его выхода 2. поступает на вход 1-, готовности блока 1 управления, если на входе 28 устройства установлен сигнал логического О, то на выходе 31 устройства устанавливается сигнал логической 1, свидетельствующий о том, что блок 1 управления находится в режиме ожидания готовности.

Блок 1 управления выдает слово состояния на шину 12 данных по синхросигналу на соответствующем выходе 1g, поступающему нп вход 2 тактового генератора 2 в первом такте каждого цикла,.а стробированный по первой фате сигнал синхронизации с выхода 2g тактового генератора 2 поступает на вход синхронизации контроллера 3, в который записывается слово состояния блока 1 управления с входов-выходов 1g данных блока 1 управления. Контроллер 3 по слову состояния и сигналам на выходах 1 управления блока 1 управления формирует код на шину 32 управления, а также формирует код на шину 3 данных, обеспечивая ее требуемую нагрузочную способность и двунаправлен- ность передачи данных на входах-выходах 1 данных блока 1 управления.

Шинный формирователь 4 адреса формирует по адресным сигналам на соответствующих выходах 1| блока 1 уп. равления шину 4 ,, адреса, обеспечивая

ее требуемую нагрузочную способность.

Устройство можно перевести в режим прерывания и захвата подачей соответствующих сигналов на входы 29 и 30. При переходе в режим прерывания с выхода 32 снимается сигнал разрешения прерывания. При переходе устройства в режим захвата на соответствующем разряде выходов 1 управления блока 1 управления устанавливается сигнал подтверждения захвата, который по первому и второму входам управления переводит выходы шинного формирователя 4 адреса в высокоимпедансное состояние. Также по этому сигналу выходы контроллера 3, выходы 1 адреса, входы-выходы 1g данных блока 1 управления переводятся в высокоимпедансное состояние.

Блок 1 управления считывает и выполняет программу, записанную в блоке 6 постоянной памяти, либо в блоке 7 оперативной памяти . При этом дешифратор 5 адреса памяти дешифрирует адрес, выставленный на шине f адреса, если на шине Зг управления выставлен один из сигналов Чтение памяти, Запись в память, при этом активируется выход первого элемента ИЛИ 11 и первый вход разрешения деширатора 5. Второй инверсный вход разрешения активирован выходом элемента И 15. Еслу на шине 4( адреса сие- т.емы выставлен адрес постоянной памяти, то активизируется выход 51 дешифратора 5 и первый вход управления блока 6 постоянной памяти.

Если на шине 4 адреса выставлен адрес блока 7 оперативной памяти, то активизируется выход 5 дешифратора 5, вход управления блока 7 оперативной памяти и первый вход управления шинного формирователя 8 оперативной памяти,

Выходы блока 6 постоянной памяти подключаются к шине 3,, данных, если активирован, кроме первого входа управления, второй вход управления сигналом Прием с соответствующего разряда выходов 1j управления блока 1 управления. Данные считываются из блока 6 постоянной памяти в блок 1 управления по шине 32 данных входы-выходы данных контроллера 3 на входы-выходы 12 данных блока 1 управления в соответствии с адресами, поступакщими на ее адресные вхо- ды с шины ki адреса.

Для считывания данных из блока 7 оперативной памяти, кроме активирования его входа управления, на вход записи подается сигнал логического О с соответствующего разряда шины 32 управления Запись в память, а второй вход управления шинного формирователя 8 блока оперативной памяти активизируется разрядом выходов 1з управления блока 1 управления Прием. Это переводит шинный формирователь 8 памяти в режим приема, т.е. организуется передача данных с выходов блока 7 оперативной памяти на шину J данных. Данные считываются из блока 7 оперативной памяти в блок 1 управления по шине 3, данных в соответствии с адресами, по

|д

ро 25

30 4Q

35

50

5

ступаюрщми на ее адресные входы с шины 4 адреса.

Блок 1 управления может записывать данные в блок 7 оперативной памяти, при этом шинный формирователь 8 оперативной памяти по второму входу управления, с которого снимается активный уровень сигнала соответствующим разрядом выходов 13 управления блока 1 управления, переводится в режим ввода данных с шины 3| данных. Блок 7 оперативной памяти 7 по входу записи, который активизируется соответствующим разрядом Запись в память шины 32 управления, переводится в режим записи. Данные с шины 3, данных записываются в блок 7 оперативной памяти в соответствии с адресными сигналами, поступающими на ее адресные входы с шины 4,1 адреса.

При отсутствии активных уровней управляющих сигналов выходы блока 6 постоянной памяти и выходы-входы шинного формирователя 8 оперативной памяти находятся в высокоимпедансном состоянии и отключены от шины 3 данных.

Устройство вводит данные с информационных входов 37 или выводит данные на информационные выходы 3. Де- пгифрат op Q адреса устройства в) дл- вывода дешифрирует адрес, выставленный на шине 4 адреса, РСЛИ активирован его вход управлении выходом второго элемента ИЛИ 1 при активи- ронлнии его входов одним из сигналов Ввод из устройства ввода, Вывод в устройство вывода на соответствующих разрядах шины Зг управления.

Выходы дешифратора 9 адреса устройств ввода-вывода активируют второй вход разрешения одного из шинных формирователей 10 ввода-вывода, соответствующего адресу, поступающему на адресные вхгды дешифратора 9 адреса устройств ввода-вывода.

Режим работы (ввод или вывод) шинных формирователей 10 ввода-вывода определяется сигналом на вторых входах разрешения, т.е. соответствующим разрядом Ввод из устройства ввода шины 32 управления. В режиме ввода данные с информационных входов 37 поступают на входы соответствующего шинного формирователя Ю ввода- вывода, а с его входов-выходов - на шину 3 данных через контроллер 3 в

блок 1 управления по его входам-выходам -Ijj, данных. .

В режиме вывода данных из блока 1 управления по входам -выходам 1, данных через контроллер 3, шине 3( данных поступают сигналы на вхо$- выходы соответствующего шинного формирователя 10 ввода-вывода, а с его выходов - на информационные выходы 36.

При отсутствии активных уровней сигналов управления шинные формирователи 10 ввода-вывода отключены от шины данных (находятся в высокоим- педансном состоянии).

Режим подготовки к ветвлению. В этом режиме, который может выполняться при инициализации устройства (при включении питания, например, программой монитор), если ветвление организуется в одном месте программы, либо перед ветвлением, если оно организуется многократно в разных участках программы, обеспечи- вается запись адреса точки ветвления в два регистра 19 и 20, запись анали зируемых членов СДНФ системы булевых функций, вычисляемой в процессе ветвления, в группу регистров , а также установка триггера 14 в единичное состояние.

Причем на группе входов аппаратно, например, установлены старшие адреса ветвления (например, подключением необходимых разрядов через ограничительные резисторы к положительной и отрицательной шинам питания) в соответствии с разработанной проектировщиком картой распределения памяти устройства. На входах управления установлены единицы, количество которых, начиная с входа 39,, равно количеству членов СДНФ в вычисляемой ветвлением системе булевых функций. Пр необходимости вычисления другой системы булевых функций в другой точке программы изменяется информация в регистрах 19, 20, 21,-21m и на входах ,,,, 391-39т, причем изменение информации на этих входах может быть осуществлено программно с использованием внешних настроечны регистров.

Для записи информации в регистры 19, 20, 21ч-21т блок 1 управления организует режим вывода во внешнее устройство. При этом возбуждается

0

5

выход 9j дешифратора 9 и, так как активирован разряд тины Зг управления Вывод в устройство вывода, то возбуждается и выход элемента И 17, поэтому информация с шины 3( данных записывается в регистр 19. Синхроимпульс записи с выхода элемента И 17 поступает одновременно на все регист- ры 19, 20, 214-21т, вследствие чего в регистры 20, 21,-21т записывается информация с выходов предыдущих регистров: в регистр 20 - с выхода регистра 19, в регистр 21i - с выхода регистра 20 и т.д. Все эти регистры предварительно обнулены выходом 2 , сброса тактового генератора 2, так же, как и триггеры 14 и 26.

При следующем возбуждении выхода 9 з дешифратора 9 (блок 1 управления, записывая информацию в регистры 19, 20, 21 -21,, обращается к устройству вывода по одному и тому же адресу, возбуждающему выход 9 дешифратора 9 т+2 раза) информация с шины 3 данных записывается в регистр 19, а с регистра 19 этим же импульсом с выхода элемента И 17 - в регистр 20. По окончании т+2 циклов вывода инфор- 0 мации в регистры 19, 20, 211-21гмв регистрах 21,-21m записаны m членов СДНФ системы булевых функций, вычисляемых в процессе ветвления, а в регистрах 19 и 20 - младший и старший полуадресы точки ветвления программы.

Процесс перемещения информации в регистрах 19, 20, показан на фиг.2.

Далее блок управления осуществляет вывод информации по адресу триггера 14,обращаясь к нему,как к устройству вывода с фиксированным адресом.. При этом возбуждается выход 9 дешифратора 9,разряд шины управления Вывод в устройство вывода, поэтому возбуждается выход элемента И 16, по стробу на выходе которого с пины данных бит информации (в данном случае - единицы) записывается в триггер 1Д, который устанавливается в единичное состояние и активирует свой выход.

Режим многоальтернативного ветвления .

Это режим, когда блоку 1 управления необходимо обработать информацию на входах 34 и 35, он может выполнить это, например, специальной подпрограммой. При этом схема 22 сравнения дешифрирует адрес второго

5

0

5

0

5

17

байта команды (например, безусловного перехода или вызова подпрограммы IMP и CALL для микропроцессора 580). Выход схемы 22 сравнения активируется. Если при этом активирован разряд выходов Ц управления блока 1 управления Прием, то активируется выход элемента И 18, который через элемент ИЛИ 27 активирует трети вход элемента И 15. Первый вход этого элемента к этому времени активирован разрядом шины 32 управления Чтение, а второй вход - выходом установленного при инициализации триггера 14. Поэтому шинный формирователь 13 открывается, дешифратор 5 адреса памяти блокируется по инверсному входу разрешения. Так как выход триггера 26 обнулен (триггер 26 обнулен системным сбросом с выхода 2$ тактового генератора 2), то на выход мультиплексора 23 поступае информация с группы 35 младших разрядов логических условий, которая через шинный формирователь 13, шину 3 данных считывается в блок 1 упраления и воспринимается как младший байт команды (безусловного перехода или вызова подпрограммы).

По окончании импульса чтения с соответствующего разряда шины управления задним фронтом импульса L выхода элемента И 15 триггер 26 устнавливается и активирует через элемент ИЛИ 27 третий вход элемента И а также активирует адресный , му типлексора 23, который передает теперь на свои выходы информацию о ти дов группы элементов И 25(-25п,с трмя состояниями на выходе, ia которо устанавливается код номера члена СД вычисляемой системы булевых функций если информация на входах группы 24 старших разрядов логических условий совпадает с информацией, записанной в одном из регистров 21д-21т группы и единичный код в противном случае (так как выходы всех элементов И группы элементов И 25(-25тс тремя состояниями на выхоле находят- ся в высокоимпедансном состоянии, что эквивалентно в ТТЛ-логике подач на соответствукщие входы мультиплексора 23 логических 1).

На входах ДО установпен (при ши циализации системы с внешнего регистра либо подключением соответствующих разрядов через ограничитель

o

5

0

5

ные резисторы к положительному или отрицательному полюсам источника питания) код разрядов адресов ячеек памяти (блоков 6 или 7) так, что в конкатенации с информацией с выходов группы элементов И 25,-25m с тремя состояниями на выходе мультиплексора 23 устанавливается старший полуадрес адреса ветвления с учетом количества адресов, требуемых для формирования команд выдачи соответствующих управляющих воздействий.

Поэтому при следующем чтении памяти блоком 1 управления (чтение второго байта команды безусловного перехода пли вызова подпрограммы) вновь активируется разряд Чтение шины 3 управления. Однако выход блока 22 сравнения неактивнрован, так как в этом случае на шине адре-. са установлен адрес, на единицу больший предыду1дего, Неактивирован и выход элемента И 18. Но, так как триггер 26 установлен, то через элемент ИЛИ 27 активирован третий вход элемента И 15, выход ко т орого возбужден и через тшнын формирователь 13

и ч шину

1 дччннх передается описан

ная информация с ньгходоь мулътмплек-

с о р л

1 I

ia/uiHN фронтом импулыа на

0

5

0

5

нмчоде ;.-:ег-м ни И 5 ,,аяе трнг- iер 26 и HI мупьтппаексора 23 вноьь перепаотся информация с Ьло- дон 35.

Выхг,-1Ч 1-м.п.и ) ; опмироят епя 13 перелодн1 v n ,( кои.подписное i -стояние, и HI ьг:няю; на irnny 3 данных. . Снимается (.окпр тпгл деч ифртт ра 5 адреса памяти. Hnoi- 1 у равнения, восприняв ком-1 щу, BJ трои и ту тяг: баить (зт&рое и третье слова г оОшем ) которой чависят от информации на входах 1Г; г 34, переходит на соответствующую, зависящую от логических условий метку программа или подпрограмму, формирует управляющие воздействия, вмвочит их на испслни- тельные органы с ьмхолов 36 При необходимости бпокиропки дисциплины мьогоальjгрнатпвнп ( ветвления блок 1 управления программк 1 обнуляет триггер 14, выводя в него по шине данных логически 0, Таким образом, в отпичие от и.)гесгного объем памяти, необходимой для организации реакции на логические условия в процессе мнггоальтернативного ветвления, только частично имеет

экспоненциальную зависимость от количества логических условии п. Часть разрядов логических условий k, которая подключена ко входам 35, адре- сует 2ка разрядных участков, где а - длина участка, необходимого для формирования управляющих сигналов, округленная до ближайшей большей степени числа 2. Часть разрядов (n-h) с помощью группы блоков сравнения, группы элементов И 25,-25тс тремя состояниями на выходе, входов , подвергается кодированию так, что количество комбина- цин на выходе мультиплексора 23 при возбуждении его входа адреса значительно меньше, чем 2й , а равно величине т+1, где т - количество членов СДНФ, вычисляемой методом много- альтернативного ветвления системы булевых функций.

Формула изобретения

Устройство для программного управления технологическими процесса- ми, содержащее блок управления, тактовый генератор, контроллер, шинный формирователь адреса, дешифратор ад- -JQ реса памяти, блоки постоянной памяти программ и оперативной памяти программ во время работы, шинный формирователь оперативной памяти, дешифратор адресов устройств ввода- 35 вывода, группу шинных формирователей устройств ввода-вывода, первый, второй и третий элементы ИЛИ, первый, второй, третий и четвертый элементы И, первый регистр адреса ветвления, ДО блок сравнения, триггер и шинный формирователь ветвления, входы-выходы которого соединены с шиной данных устройства, образованной информационными выходами-входами контроллера, д5 выходы которого являются шиной управления устройства, разряды которой Чтение памяти и Запись в память соединены с входами первого элемента ИЛИ-, выход которого соеди- CQ пен с первым прямым входом разрешения дешифратора адреса памяти, первый выход которого соединен с первым входом разрешения блока постоянной памяти программ, выходы которого соединены с шиной данных устройства, выходы первой и второй фаз синхронизации и выход готовности тактового генератора соединены соответственно

Q 5 0

5

/

JQ 35 ДО д5 CQ

с тактовыми входами первой и второй фат синхронизации и с входом готовности блока управления, выход сброса тактового генератора соединен с входами сброса первого реги стра адреса ветвления, триггера ветвления и блока управления, выход синхронизации которого соединен с входом синхронизации тактового генератора, входы готовности и сброса которого являются входами готовности и сброса устройства, выход синхронизации тактового генератора соединен с входом синхронизации контроллера, информационные входы-выходы которого соединены с выходами-входами блока управления, адресные выходы которого соединены с информационными входами шинного формирователя адреса, выходы которого образуют адресную шину устройства и соединены с информационными входами дешифратора адреса памяти, с адресными входами блока постоянной памяти программ и блока оперативной памяти программ во время работы и с информационными входами дешифратора адресов устройств ввода- вывода, каждый разряд группы выходов которого соединен с первым входом разрешения соответствующего шинного формирователя устройств ввода-вывода группы, входы захвата и запроса прерывания, выходы ожидания и разрешения прерывания блока управления являются соответственно входами захвата и запроса прерывания устройства и выходами ожидания и разрешения прерывания устройства, группа управляющих выходов блока управления соединена с группой управляющих входов контроллера, разряд Подтверждение захвата группы управляющих выходов блока управления соединен с первым и вторым управляющими инверсными входами разрешения шинного формирователя адреса, разряд Прием группы управляющих выходов блока управления соединен с первым входом четвертого элемента И и с вторыми входами разрешения бпоков постоянной и оперативной памяти, второй выход дешифратора адреса памяти соединен с первым входом разрешения шинного формирователя оперативной памяти и с входом разрешения блока оперативной памяти программ во время работы, выходы которого соединены с входами шинного формирователя оперативной памяти, выходы-входы которого соединены с шиной данных устройства, выходы шинного формирователя оперативной памяти соединены с информа- ционными входами блока оперативной памяти программ во время работы, разряды шины управления Ввод из устройства ввода и Вывод в устройство вывода соединены с входами второго элемента ИЛИ, выход которого соедине с входом разрешения дешифратора адреса устройств ввода-вывода, первый управляющий выход которого соединен I с первым входом второго элемента И, выход которого соединен с синхро- входом триггера ветвления, выход которого соединен с первым входом первого элемента И, выход которого соединен с входом разрешения шинного формирователя ветвления и с вторым инверсным входом разрешения дешифратора адреса памяти, информационные входы дешифратора адресов устройств ввода-вывода соединены с ад- ресной шиной, а его второй управляющий выход соединен с первым входом третьего элемента И, выход которого соединен с входом записи перпого регистра адреса ветвления, индчрмлци- онные входы которого соединены г шиной данных, а выходы - со старшими разрядами второй группы информационных входов блока сравнения, первая группа информационных входов ко ю.ю- го соединена с адресной шинсм, а выход - с вторым входом четвертого элемента И, выход которого с печи - нен с первым входом третьего чдемен- та ИЛИ, выход которого соединен с в г рым входом первого элемент И, вы- ходы-входы шинных формирователей устройств ввода-вывода соединены с гаи- ной данных, информационные входи и выходы которых являются информа- ционными входами и выходами устройства, разряд шины управления Вывод в устройство вывода соединен с вторыми входами второго и третьего элементов И, разряд Впод из устройства ввода шины управления соединен с вторыми входами разрешения шинных формирователей устройств вьода-ныв - да группы, разряд Запись в память шины управления соединен с входом записи блока оперативной памяти ппт- грамм во время работы, разряд Чтение памяти шины управления соединен

с третьим входом первого элемента И, младший разряд шины данных соединен с информационным входом триггера ветвления, отличающееся тем, что, с целью расширения области применения устройства, в него введены второй регистр адреса ветвления,, группа регистров, мультиплексор, группа блоков сравнения, группа элементов И и счетный триггер, выход которого соединен с вторым входом третьего элемента ИЛИ и с адресным входом мультиплексора, выходы которого соединены с информационными входами шинного Формирователя ветвления выход сброса тактового генератора соединен с входами сброса счетного триггера, второго регистра адреса ветвления и регистров группы, выходы первого регистра адреса ветвления соединены с информационными входами второго регистра адреса ветвления, выходы которого соединены с младшими разрядами второй группы информационных входов, и с информационными входами первого регистра группы, входы поспелуощгго регистра группы соединены г информлии чнымп выходами пре дмдуп 1 о регистр i ч нылоты реп . трон

ГруППН L (ЧДИЯРНЛ СОи-ГЧРТЧ Г ЬОННР С ТИП РЬ-МИ ПЛОД WTf vnilhl,

первые1 ,ы кгторь- являются . путао 1 старших рч ф-voH п П;ч,ччких V..UH. уггроигтьл, a bMx;v i. е,инс v-I с :- ветсгпен;) с пепы. чь у ятян. ними вхотями leM .HiuH И , , ртгры упраьпямцие в.«. лн ьотгрых РВЛЯР;СЯ входами управтгния /стройстпа, i ны- :.ori,,i eOfeiH ieHbi г . адшнмя iffti вторгЛ гг/ппы н- ультиппе ч-оря, старшие отпяль вторсш группы входон которого янтяклся пс-ряг й группой HV о- дов копов разряангпи, младшие и старшие разряды пгррой группы входов м льтитекггр,- ияцян -ся гоогтетстнен- но группой входов мтлдших рлчря:;ов лггичегкил слог;11 устрой тва i вто- рсп группой вхоч. р кодов разрядности, rpvnpa рхолоп т:(менгстч И груп- пи ялляотгя группч старип х сздррсор ветвления устрой.-тра, вьг- ход третьего ЭТРМГНТЛ И соединен с входами записи втор го регистра ад- ресл ветвления и ре.игтроя группы, выход чемент i И соединен со счеч ь;м вводом счетногс триггера

23

Выводы

589 АП16 А,7,9,12

1633377

24 Таблица

153,6, 10,13

1 4- Г

я т

21

т

/г/

D

Г.

1ч

Л

i

„j

г

ir

/

г

Ь

|c.

Xi

i; j

J

39,

тг

2/.

/77 1-Т1

59т

Фиг 1

код neptoio поделена CSHQ)

f-бш faii т

подключение ti, faonup

байт

чтение Z-го дай т а

подключение ti, faonupaSxa S

байт

2-ли iauft

чтение Z-го дай т а

| Устройство программного управления | 1981 |

|

SU1012205A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-03-07—Публикация

1989-03-21—Подача