Изобпетение относится к вычислительной технике и может быть использовано при динамическом распределении нагрузки в сетях ЭВМ.

Цель изобретения - повышение быстродействия „

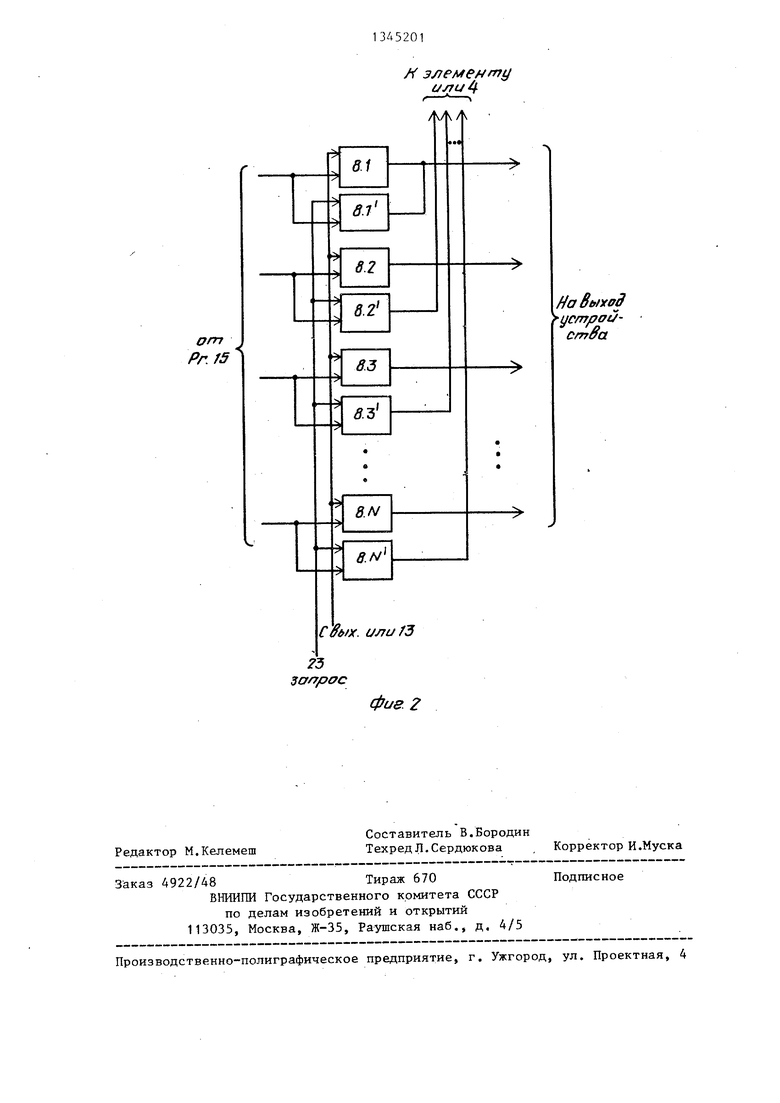

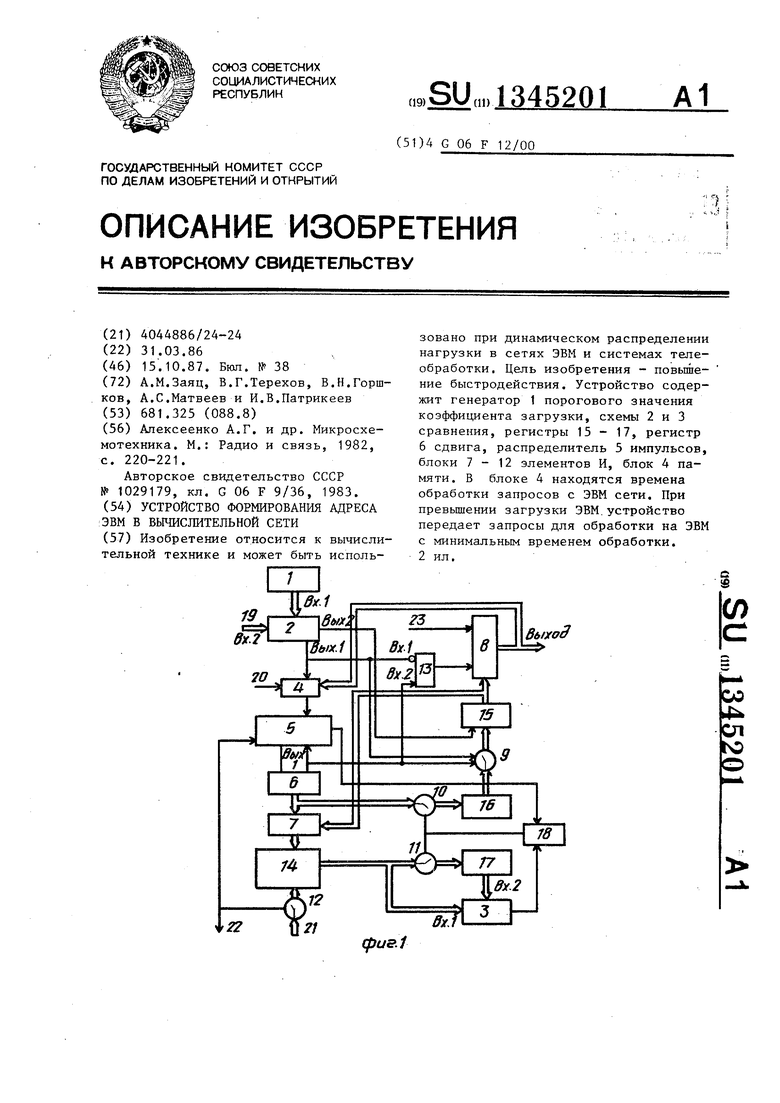

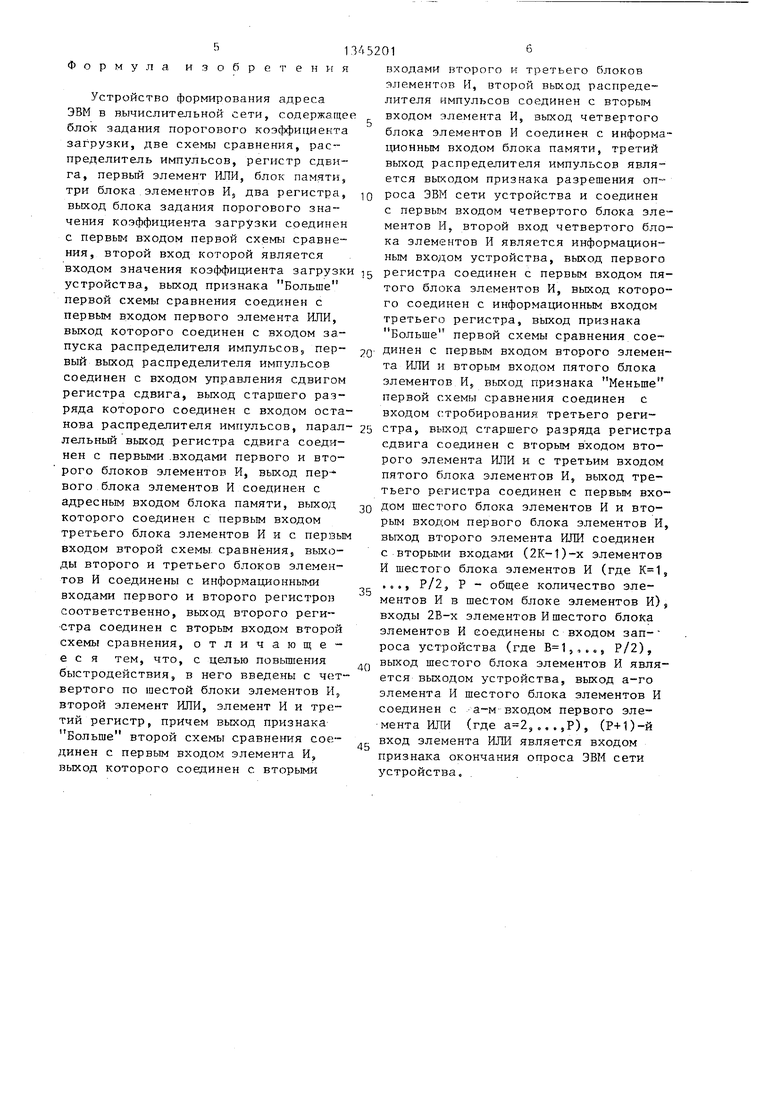

На фиг.1 приведена структурная схема устройства; на фиг. 2 - струк- турнйя схема шестого блока элементов И,

Устройство (фиг.1) содерлсит блок 1 задания порогового значения коэс1к)и циента загрузки, схемы 2 и 3 сравнения, элемент ИЛИ 4, распределитель 5 импульсов, регистр 6 сдвига, блоки 7-12 элементов И, элемент HItti 13, блок 14 памяти, регистры 15 - 17, элемент И 18, вход 19 значения коэффициента загрузки, вход 20 окончания опроса ЭВМ сети, информационные взсоды 21 устройства сети, выход 22 разрешения опроса ЭВМ сети, входы 23 запроса устройства. Первый вход элемента ИЛИ 13 инверсньй.

Вычислительная сеть содержит N ЭВМ. У каждой ЭВМ-может быть устройство формирования адреса. В случае нормальной работы ближайшей ЭВМ устройство пересыпает к ней запросы от .связанных с ним терминалов. Устрой- :ство формирования адреса содержит блок памяти, состоящий из NT ячеек, в которых в порядке возрастания номеров ЭВМ записаны времена обработки ими запросов,- за исключением ближайшей к устройству ЭВМ. По мере необходимости информация в блоке памяти обновляется.

Устройство работает следугаи им образом.

Схема 2 сравнения сравнивает код текущего значения коэффициента загрузки ближайшей ЭВМ, поступающей на вход 19, с пороговым значением, вьща- ваемый блоком 1. Если текущее значение коэффициента загрузки, ближайшей к устройству ЭВМ, оказалось меньше или равно пороговому, то на выходе 1 схемы 2 сравнения - низкий уровень, на выходе 2 схемы 2 сравнения - высокий уровень и в регистр 15 записано число 100...О (разрядностью N), что соответствует адресу ближайшей к устройству ЭВМ. При появлении сигнала запроса на входе 23 считывается адрес ближайшей ЭВМ с регистра ,15 на выход устройства. При этом с выхода блока 8 элементов И на элемент ИЛИ 4

0

5

0

0

не пост-улает, так как первьп выход блока 8 элементов И к элементу ИЛИ 4 не подключен.

На выходе элемента ИЛИ 13 всегда находится 1 за исключением случая, когда с выхода 1 схемы 2 сравнения поступает с игнал 1, а с выхода переполнения регистра 6 сдвига - О,

Если текущее значение кода загрузки превьпиает пороговое, единичный сигнал с выхода признака Больше схемы 2 сравнения подается на элемент ИЛИ 4,. на вход блока 9 элементов И, на инверсный вход элемента ИЛИ 13, нулевой сигнал с выхода 2 схемы 2 сравнения подается на первый разряд регистра 15. Вследствие этого в пер- вьм разряд регистра 15 записывается О, возможна вьщача адреса ЭВМ сети с регистра 16 на регистр 15, запускается распределитель 5 через элемент ИЛИ 4, блокируется выдача адреса ЭВМ сети через блок 8 элементов И вторым 5 управляющим входом, так как после запуска распределителя 5 на прямой вход элемента ИЛИ 13 подается О. Распределитель 5 вырабатывает сигналы, по которым производится сдвиг первоначального значения регистра 6 сдвига, т.е. 1 в младшем разряде, сигналами с которого производится последова- - тельное считывание из блока 14 памяти времен обработки запросов в сети для каткдой ЭВМ, сравнение этих величин, выбор минимального из них и параллельное формирование в регистре 16 адреса ЭВМ с минимальным временем обработки запроса.

На первом выходе распределителя 5 форм1- руется сигнал, по которому производится сдвиг первоначального значения в регистре 6 сдвига, которое является адресом ячейки запомина- клцего устройства и частью формируемого адреса ЭВМ сети.

Значение, полученное на выходах блока 14, сравнивается схемой 3 сравнения со значением, записанным в регистре 17 (перед началом формирования адреса ЭВМ в регистр 17 заносится код 11...1). На первом шаге число, записанное в регистр 17, больше числа, считанного из блока 14 памяти, и на выходе схемы 3 сравнения формируется сигнал, При поступлении сигнала с второго выхода распределителя 5 элемент И 18 открывает блоки 10 и 11, обеспечивая этим запись в регистры

5

0

5

0

5

16 и 17 соответственно значения с выходов регистра 6 и блока 14. Таким образом, в регистре 17 находится значение времени обработки запроса в первой ЭВМ сети, а в регистр 16 за- писана часть формируемого адреса первой ЭВМ сети (10...0). Распределитель 5 вьфабатывает сигналы, по которым производится сдвиг первоначального значения сдвига регистра 6, сигналами с которого производится последовательное считьгоание из блока 14 времен обработки запросов в сети для каждой ЭВМ, сравнение этих величин, выбор минимального из них и параллельное формирование в регистре 16 адреса ЭВМ с минимальным временем обработки запроса.

На первом выходе распределителя 5 формируется сигнал, пс которому гтро- изводится сдвиг первоначального значения в регистре 6 сдвига, которое является адресом ячейки блока 14 и частью формируемого адреса ЭВМ сети.

Значение, полученное на выходе блока 14, сравнивается схемой 3 со значением, записанным в регистр 17 (перед началом формирования адреса ЭВМ в регистр 17 заносится код 11 ...1). На первом шаге, число, записан ное в регистр 17, больше числа, считанного из блока 14, и на выходе схемы 3 сравнения формируется сигнал. При поступлении сигнала с третьего выхода распределителя 5 эле- мент И 18 открывает блоки 10 и 11, обеспечивая этим запись в регистры 16 и 17 соответственно значения с выходов регистра 6 и блока 14. Таким образом, в регистре 17 находится значение времени обработки запроса EI первой ЭВМ сети, а в регистре 16 за- писана часть формируемого адреса первой ЭВМ сети (10...0).

Далее с первого выхода распредели теля 5 осуществляется выдача очередного сигнала, по которому производится сдвиг значения регистра 6 и считывание времени обработки запроса из блока 14 памяти для следующей ЭВМ се ти. Информация с выходов блока 14 вновь сравнивается с записанной в регистре 17 и при поступлении сигнала с второго вькода распределителя 5 в случае, если содержимое регистра 17 больще, в регистрах 16 и 17 информация обновляется. В противном случае сигнал с выхода элемента И 18 не поступит в блоки 10 и 115 элементы И не

открываются и информация Б регистрах 16 и 17 сохраняется.

Эта последовательность операций повторяется до тех пор, пока список ЭВМ исчерпан. В противном случае сигнал с последнего выхода регистра 6 останавливает распределитель 5, производит запись адреса ЭВМ с-минимальным временем обработки на регистр 15, открьшает блок 8 элементов И по второму управляющему входу. При поступлении запроса на вход 23 устройства производится считьгоание адреса ЭВМ с минимальным временем обработки. Таким образом, при поступлении запроса на выходе схемы сразу формируется адрес ЭВМ с минимальным временем обработки, куда данный запрос направляется на обработку, т.е. повьппа- ется быстродействие устройства. При формировании на выходе устройства адреса ЭВМ сети, за исключением ближайшей, производится запуск распределителя 5 через элемент ИЛИ 4 и подго-. товка адреса ЭВМ с минимальным временем обработки на регистре 15. Причем на ЭВМ, к которой был послан предьщу- щий запрос на обработку, последующий запрос не посылается, так как формирование ее адреса запрещается путем подачи содержимого регистра 15 на схему запрета блока 7 элементов И. Это не позволяет перегружать ЭВМ с малым временем обработки запросами при большой частоте их поступления.

Так как время обработки запроса в каждой ЭВМ - величина постоянная, то по мере необходимости происходит обновление содержимого блока 14 памяти. В то время, когда не происходит поиск ЭВМ с минимальным временем обработки, распределитель 5 формирует ,разрешающий сигнал на третьем выходе, |по которому в блок 14 памяти через блок 12 элементов И с информационньпс входов 21 устройства производится запись новой информации о времени обработки от ЭВМ сети (сигнал разрешения обновления информации поступает с выхода 22 устройства). По окончании записи информации производится запуск распределителя 5 сигналом Конец обновления с входа 20 через элемент ИЛИ 4 на регистр 16, если ближайшая ЭВМ не перегружена, или на регистр 15, в противном случае устанавливается адрес ЭВМ с минимальным временем обработки.

51

Формула изoбpeгeи fя

Устройство формирования адреса ЭВМ в вычислительной сети, содержаще блок задания порогового коэффициента загрузки, две схемы сравнения, распределитель Импульсов, регистр сдвига, первый элемент ИЛИ, блок памяти, три блока,элементов И два регистра, выход блока задания порогового значения коэффициента загрузки соединен с первым входом первой схемы сравнения, второй вход которой является входом значения коэффициента загрузк устройства, выход признака Больше первой схемы сравнения соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом запуска распределителя импульсов, первый выход распределителя импульсов соединен с входом управления сдвигом регистра сдвига, выход старшего разряда которого соединен с входом останова распределителя импульсов, параллельный выход регистра сдвига соединен с первыми .входами первого и второго блоков элементов И, выход пер- вого блока элементов И соединен с адресным входом блока памяти, выход которого соединен с первым входом третьего блока элементов И и с первым входом второй схемы, сравнения, выходы второго и третьего блоков элементов И соединены с информационными входами первого и второго регистров соответственно, выход второго реги- -стра соединен с вторым входом второй схемы сравнения, отличающееся тем, что, с целью повьшгения быстродействия, в него введены с четвертого по шестой блоки элементов И, второй элемент ИЛИ, элемент И и третий регистр, причем выход признака Больше второй схемы сравнения соединен с первым входом элемента И, выход которого соединен с вторыми

52016

входами второго и третьего блоков элементов И, второй выход распределителя импульсов соединен с вторым входом элемента И, выход четвертого блока элементов И соедине-н с информа- 11Д1ОННЫМ входом блока памяти, третий выход распределителя импульсов является выходом признака разрешения оп0 роса ЭВМ сети устройства и соединен с первым входом четвертого блока элементов И. второй вход четвертого блока элементов И является информационным входом устройства, выход первого

5 регистра соединен с первым входом пятого блока элементов И, выход которого соединен с информационньгм входом третьего регистра, выход признака Больше первой схемы сравнения,соеQ- динен с первым входом второго элемента ИЛИ и вторым входом пятого блока элементов И, выход признака Меньше первой схемы сравнения соединен с входом стробирования третьего реги5 стра, выход старшего разряда регистра сдвига соединен с вторым входом второго элемента ИЛИ и с третьим входом пятого блока элементов И, выход третьего регистра соединен с первым вхо0 дом шестого блока элементов И и вторым входом первого блока элементов И, выход второго элемента ИЛИ соединен с вторыми входами (2К-1)-х элементов И ше.стого блока элементов И (где , ..., Р/2 Р - общее количество элементов И в шестом блоке элементов И), входы 2В-Х элементов И шестого блока элементов И соединены с входом зап-- роса устройства (где ,.., Р/2),

5

выход шестого блока элементов И является выходом устройства, выход а-го элемента И шестого блока элементов И соединен с -а-м входом первого эле- мента ИЛИ (где ,,..,Р), (Р+1)-й вход элемента ИЛИ яв.пяется входом признака окончания опроса ЭВМ сети устройства.

от Pr.f5

загграс

Редактор М.Келемеш

Заказ 4922/48Тираж 670

ВНИИПИ Государственного комитета СССР

ПС делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Y элементу г/У7б 4

HaBirixod

ycm/jot/ства

фие. 2

Составитель В.Бородин

Техред Л, Сердюкова , Корректор И.Муска

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования адреса ЭВМ локальной вычислительной сети | 1988 |

|

SU1520527A1 |

| Устройство для формирования адреса ЭВМ в вычислительной сети | 1981 |

|

SU1029179A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1300543A2 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для обмена информацией между ЭВМ и терминалом | 1984 |

|

SU1416993A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1986 |

|

SU1403069A1 |

| Устройство для формирования адреса | 1979 |

|

SU830387A1 |

Изобретение относится к вычислительной технике и может быть использовано при динамическом распределении нагрузки в сетях ЭВМ и системах телеобработки. Цель изобретения - повьше- ние быстродействия. Устройство содержит генератор 1 порогового значения коэффициента загрузки, схемы 2 и 3 сравнения, регистры 15 - 17, регистр 6 сдвига, распределитель 5 импульсов, блоки 7-12 элементов И, блок 4 памяти. В блоке 4 находятся времена обработки запросов с ЭВМ сети. При превышении загрузки ЭВМ.устройство передает запросы для обработки на ЭВМ с минимальным временем обработки. 2 ил. г2 (Л (риг.1

| Алексеенко А.Г | |||

| и др | |||

| Микросхемотехника | |||

| М.: Радио и связь, 1982, с | |||

| Ветряный много клапанный двигатель | 1921 |

|

SU220A1 |

| Устройство для формирования адреса ЭВМ в вычислительной сети | 1981 |

|

SU1029179A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-15—Публикация

1986-03-31—Подача