4

О СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешними устройствами | 1988 |

|

SU1536392A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для обработки запросов | 1989 |

|

SU1688248A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для прерывания программ | 1985 |

|

SU1277109A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для сопряжения двух ЭВМ | 1986 |

|

SU1363230A1 |

| Устройство для сопряжения источников информации с вычислительной машиной | 1984 |

|

SU1179358A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах сбора и обработки информации для обмена.между процессором вычислительной машины и внешними устройствами. Целыр изобретения является расширение области применения за счет обеспечения одновременного двустороннего обмена данными между ЭВМ и внешними устройствами. Устройство содержит блок управления, блок обработки запросов, блок памяти, два коммутатора, узел маскирования, дешифратор, шесть регистров, триггер, элемент ИЛИ. 2 з.п. ф-лы 3 ил. $

0

;о

Изобретение относится к вьмисли- тельной технике и может быть использовано в системах сбора и обработки информации для обмена между процессором вычислительной машины с внешними устройства (ВУ),

Цель изобретения - расширение области применения устройства за счет обеспечения одновременного дву- стороннего обмена данными между ЭВМ и ВУ.

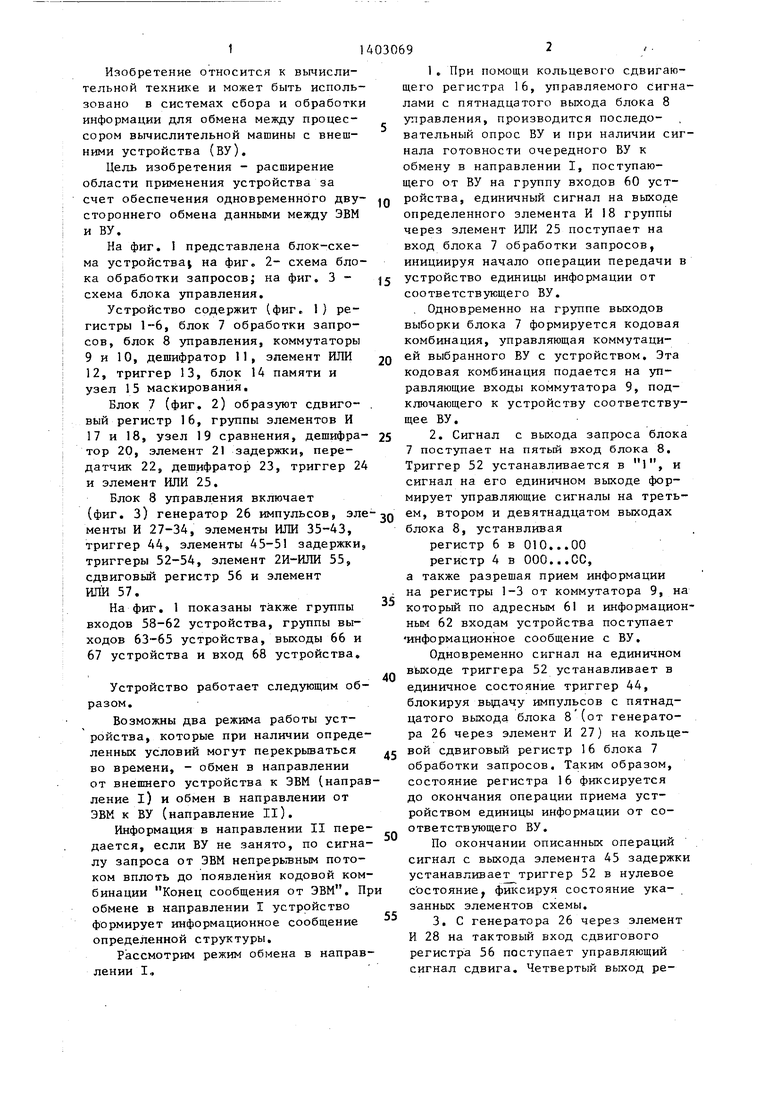

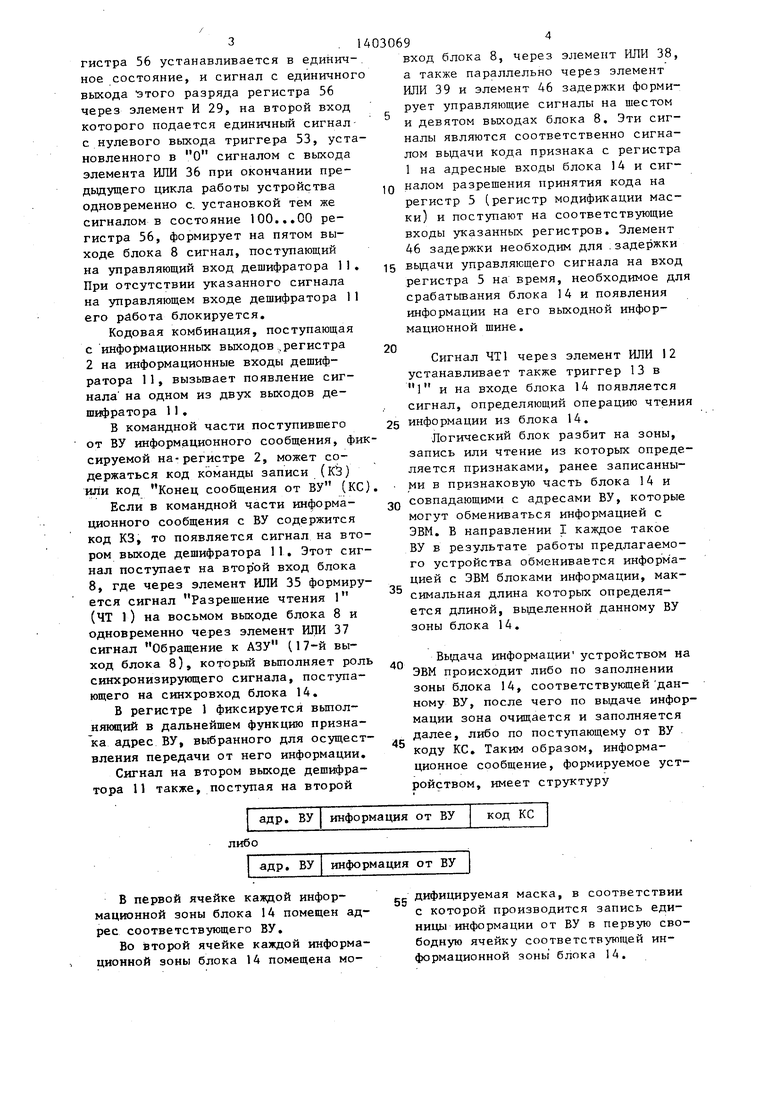

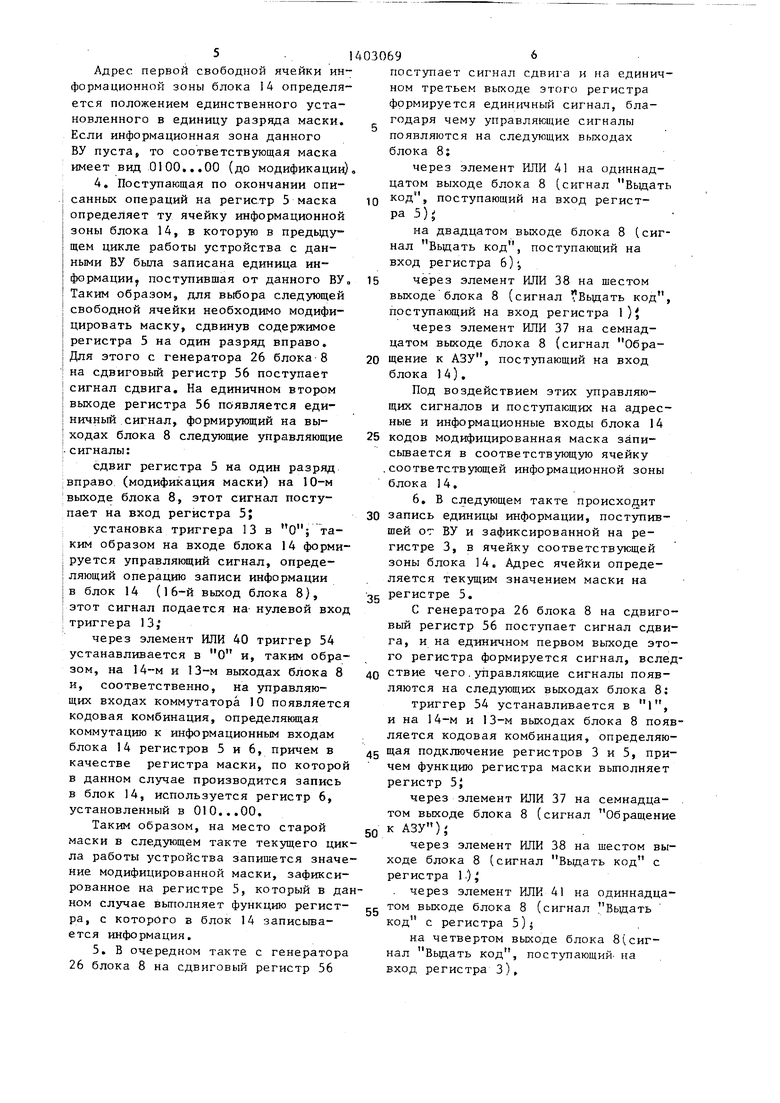

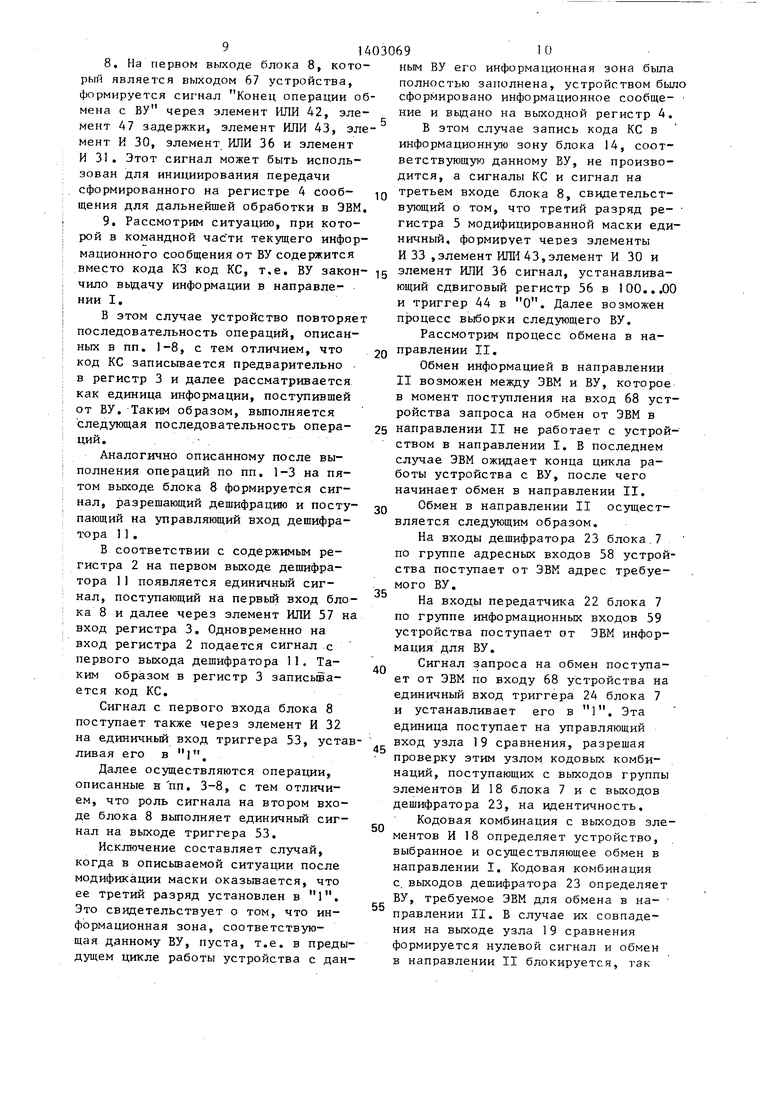

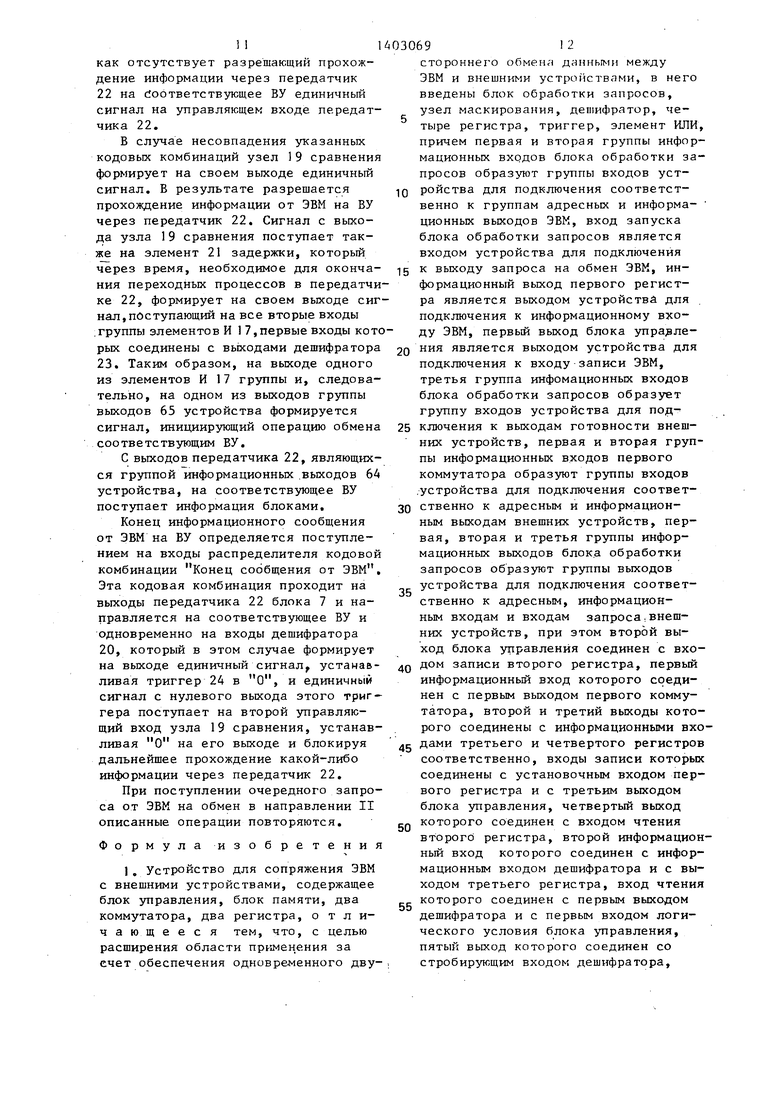

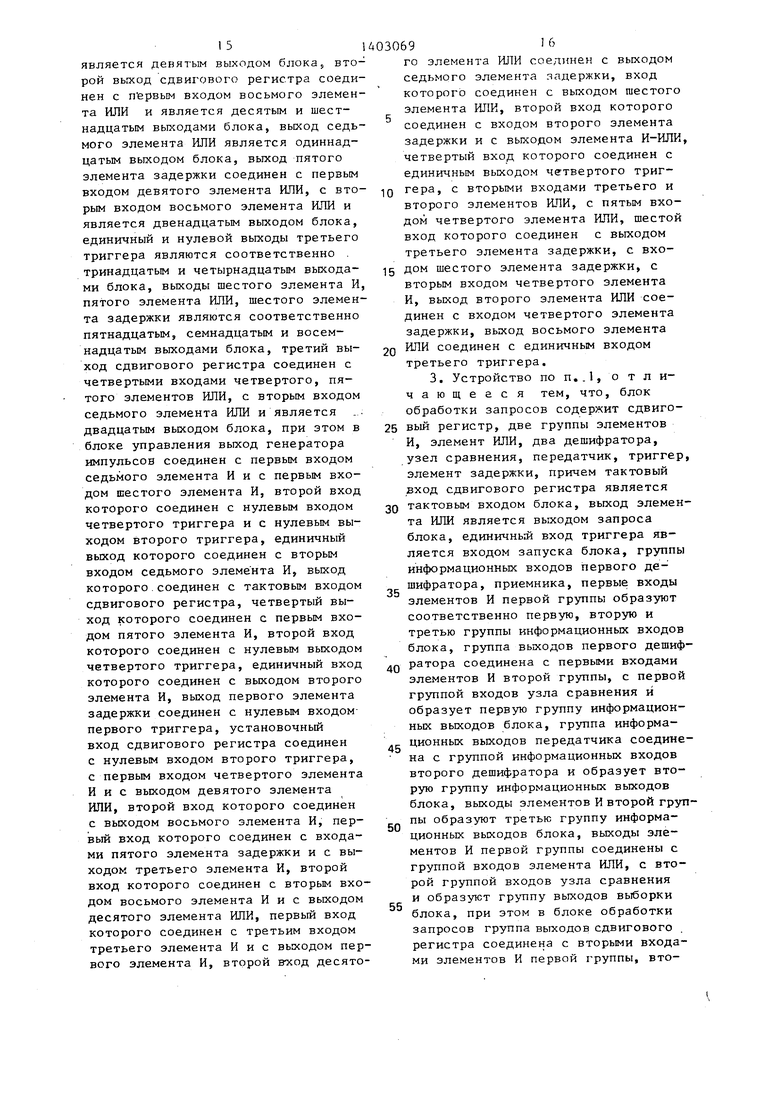

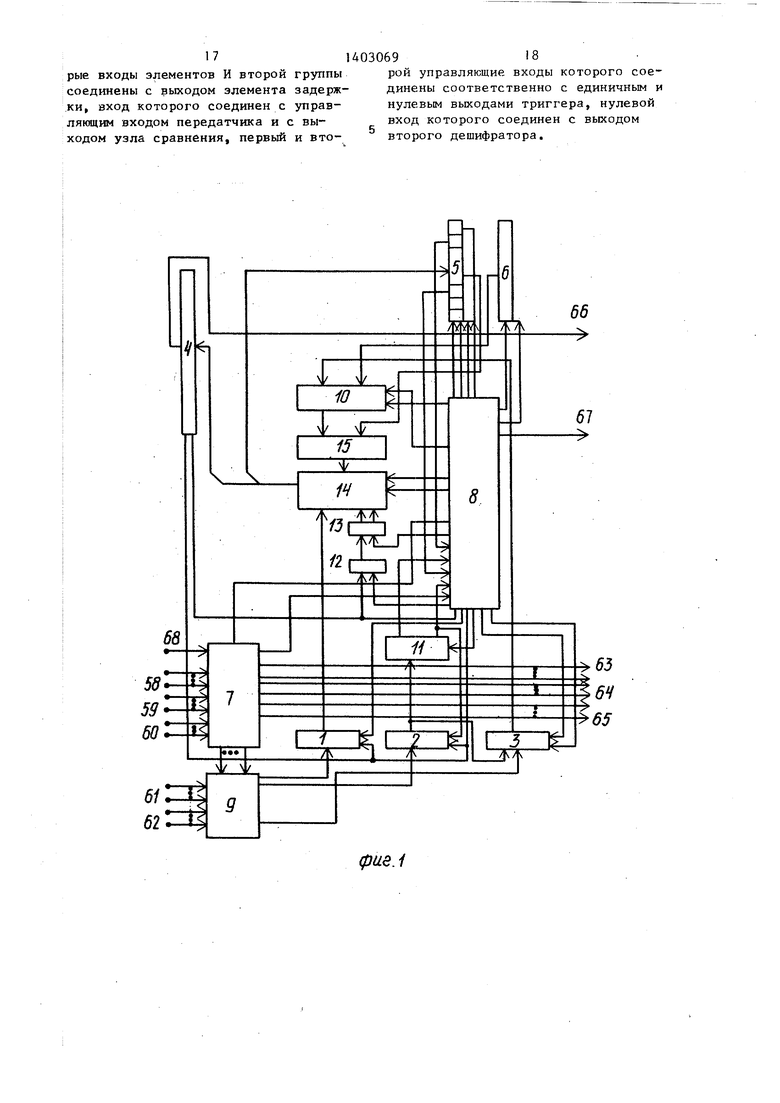

На фиг. 1 представлена блок-схема устройства на фиг« 2- схема блока обработки запросов; на фиг. 3 - схема блока управления.

Устройство содержит (фиг. 1) регистры 1-6, блок 7 обработки запросов, блок 8 управления, коммутаторы 9 и 10, дешифратор 11, элемент РШИ 12, триггер 13, блок 14 памяти и узел 15 маскирования.

Влок 7 (фиг. 2) образуют сдвиго- вый регистр 16, группы элементов И 17 и 18, узел 19 сравнения, дешифра- тор 20, элемент 21 задержки, передатчик 22, дешифратор 23, триггер 24 и элемент ИЛИ 25.

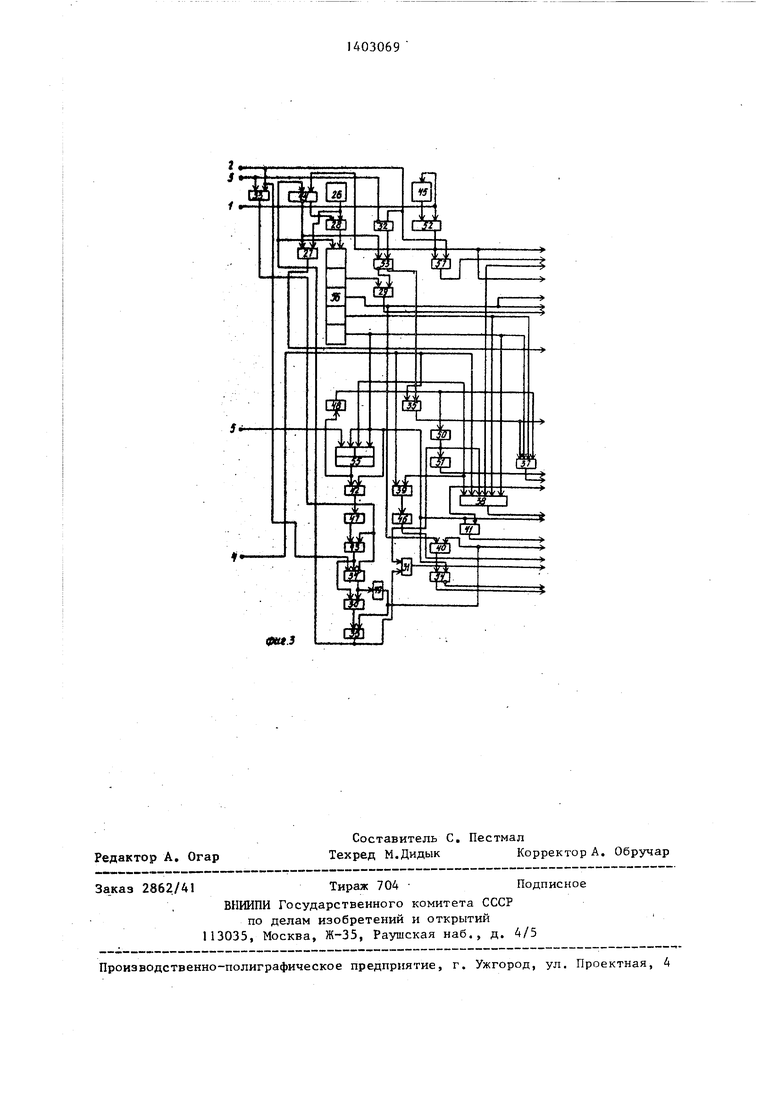

Влок 8 управления включает (фиг. 3) генератор 26 импульсов, эле менты И 27-34, элементы ИЛИ 35-43, триггер 44, элементы 45-51 задержки, триггеры 52-54, элемент 2И-ИЛИ 55, сдвиговый регистр 56 и элемент ИЛИ 57.

На фиг. 1 показаны также группы

входов 58-62 устройства, группы выходов 63-65 устройства, выходы 66 и 67 устройства и вход 68 устройства.

Устройство работает следующим образом.

Возможны два режима работы устройства, которые при наличии определенных условий могут перекрьшаться во времени, - обмен в направлении от внешнего устройства к ЭВМ (напраление I) и обмен в направлении от ЭВМ к ВУ (направление II).

Информация в направлении II передается, если ВУ не занято, по сигналу запроса от ЭВМ непрерьжным потоком вплоть до появления кодовой комбинации Конец сообщения от ЭВМ. П обмене в направлении I устройство формирует информационное сообщение определенной структуры.

Рассмотрим режим обмена в направлении 1„

S

с

0

5

, Одновременно на группе выходов выборки блока 7 формируется кодовая комбинация, управляющая коммутацией выбранного ВУ с устройством. Эта кодовая комбинация подается на управляющие входы коммутатора 9, подключающего к устройству соответству- щее ВУ.

регистр 6 в 010...00

регистр 4 в 000...00, а также разрешая прием информации на регистры 1-3 от коммутатора 9, на который по адресным 61 и информационным 62 входам устройства поступает информационное сообщение с ВУ.

Одновременно сигнал на единичном вЬкоде триггера 52 устанавливает в единичное состояние триггер 44, блокируя вьщачу импульсов с пятнадцатого выхода блока 8 (от генератора 26 через элемент И 27) на кольцевой сдвиговый регистр 16 блока 7 обработки запросов. Таким образом, состояние регистра 16 фиксируется до окончания операции приема устройством единицы информации от соответствующего ВУ.

По окончании описанных операций сигнал с выхода элемента 45 задержки устанавливает триггер 52 в нулевое состояниеJ фиксируя состояние указанных элементов схемы.

Кодовая комбинация, поступающая с информационных выходов.регистра 2 на информационные входы дешифратора 11, вызьшает появление сигнала на одном из двух выходов дешифратора 11 .

В командной части поступившего от ВУ информационного сообщения, фиксируемой на-регистре 2, может содержаться код команды записи (КЗ) или код Конец сообщения от ВУ (КС

Если в командной части информационного сообщения с ВУ содержится код КЗ, то появляется сигнал на втором выходе дешифратора 11. Этот сигнал поступает на второй вход блока 8, где через элемент ИЛИ 35 формируется сигнал Разрешение чтения 1 (ЧТ 1) на восьмом выходе блока 8 и одновременно через элемент ИЛИ 37 сигнал Обращение к АЗУ (17-й выход блока 8), который вьшолняет роль синхронизирующего сигнала, поступающего на синхровход блока 14.

В регистре 1 фиксируется выполняющий в дальнейшем функцию признака адрес ВУ, выбранного для осуществления передачи от него информации.

Сигнал на втором выходе дешифратора 11 также, поступая на второй

В первой ячейке каждой информационной зоны блока 14 помещен адрес соответствующего ВУ.

Во второй ячейке каждой информационной зоны блока 14 помещена мо

вход блока 8, через элемент ИЛИ 38, а также параллельно через элемент ИЛИ 39 и элемент 46 задержки формирует управляющие сигналы на шестом и девятом выходах блока 8, Эти сигналы являются соответственно сигналом вьщачи кода признака с регистра 1 на адресные входы блока 14 и сигналом разрешения принятия кода на регистр 5 (регистр модификации маски) и поступают на соответствующие входы указанных регистров. Элемент 46 задержки необходим для .задержки вьщачи управляющего сигнала на вход регистра 5 на время, необходимое для срабатьгоания блока 14 и появления информации на его выходной информационной шине.

Сигнал ЧТ1 через элемент ИЛИ 12 устанавливает также триггер 13 в 1 и на входе блока 14 появляется сигнал, определяющий операцию чтения

информации из блока 14.

Логический блок разбит на зоны, запись или чтение из которых определяется признаками, ранее записанны- ми в признаковую часть блока 14 и

совпадающими с адресами ВУ, которые могут обмениваться информацией с ЭВМ. В направлении I каждое такое ВУ в результате работы предлагаемого устройства обменивается информ а- цией с ЭВМ блоками информации, максимальная длина которых определяется длиной, выделенной данному ВУ зоны блока 14.

Вьдача информации устройством на ЭВМ происходит либо по заполнении зоны блока 14, соответствующей данному ВУ, после чего по выдаче информации зона очищается и заполняется далее, либо по поступающему от ВУ коду КС. Таким образом, информационное сообщение, формируемое устойством, имеет структуру

дифицируемая маска, в соответствии с которой производится запись единицы информации от ВУ в первую свободную ячейку соответствующей информационной зоны блока 14.

Адрес первой свободной ячейки информационной зоны блока 14 определяется положением единственного установленного в единицу разряда маски. Если информационная зона данного ВУ пуста, то соответствующая маска имеет вид 0100,,.00 (до модификаци1

сдвиг регистра 5 на один разряд вправо (модификация маски) на 10-м выходе блока 8, этот сигнал поступает на вход регистра 5;

установка триггера 13 в таким образом на входе блока 14 формируется управляющий сигнал, определяющий операцию записи информации в блок 14 (16-й выход блока 8), этот сигнал подается на нулевой вход триггера 13,

через элемент ИЛИ 40 триггер 54 устанавливается в О и, таким образом, на 14-м и 13-м выходах блока 8 и, соответственно, на управляющих входах коммутатора 10 появляется кодовая комбинация, определяющая коммутацию к информационным входам блока 14 регистров 5 и 6, причем в качестве регистра маски, по которой в данном случае производится запись в блок 14, используется регистр 6, установленный в 010,..00.

Таким образом, на место старой маски в следующем такте текущего цикла работы устройства запишется значение модифицированной маски, зафиксированное на регистре 5, который в даном случае выполняет функцию регистра, с которого в блок 14 записьта- ется информация,

5, В очередном такте с генератора 26 блока 8 на сдвиговый регистр 56

0

5

0

поступает сигнал сдвига и на единичном третьем выходе этого регистра формируется единичный сигнал, благодаря чему управляющие сигналы появляются на следующих выходах блока 8;

через элемент ИЛИ 41 на одиннадцатом выходе блока 8 (сигнал Вьщать код, поступающий на вход регистра 5)

на двадцатом выходе блока 8 (сигнал Вьщать код, поступающий на вход регистра 6),

через элемент ИЛИ 38 на шестом выходе блока 8 (сигнал Вьщать код, поступающий на вход регистра 1)

через элемент ИЛИ 37 на семнадцатом выходе блока 8 (сигнал Обращение к АЗУ, поступающий на вход блока 14),

Под воздействием этих управляющих сигналов и поступающих на адресные и информационные входы блока 14 5 кодов модифицированная маска запи- сьшается в соответствующую ячейку .соответствующей информационной зоны блока 14,

С генератора 26 блока 8 на сдвиговый регистр 56 поступает сигнал сдвига, и на ед1шичном первом выходе этого регистра формируется сигнал, вследствие чего.управляющие сигналы появляются на следующих выходах блока 8:

триггер 54 устанавливается в 1, и на 14-м и 13-м выходах блока 8 появляется кодовая комбинация, определяю- g щая подключение регистров 3 и 5, причем функцию регистра маски выполняет регистр 5J

через элемент ИЛИ 37 на семнадцатом выходе блока 8 (сигнал Обращение 50 к АЗУ)J

через элемент ИЛИ 38 на шестом выходе блока 8 (сигнал Выдать код с регистра 1.)

. через элемент ИЛИ 41 на одиннадцатом выходе блока 8 (сигнал Вьздать код с регистра 5)

на четвертом выходе блока 8(сигнал Выдать код, поступающий- на вход, регистра З),

0

35

40

55

Таким образом, единица информаци поступившая от данного ВУ, записывается в первую свободную ячейку соответствующей информационной зоны блока 14.

После модификации маски возможна ситуация при которой единица появля ется в (К+1)-м разряде регистра 5, т.е. в предьщущем цикле работы данного ВУ с устройством информационная зона данного ВУ была заполнена, информация из нее была вьщана на выходной регистр 4, после чего зона была очищена. В этом случае на уста- новочньш вход регистра 5 подается управляющий сигнал с единичного выхода его (К+1)-го разряда и регистр 5 устанавливается в 0010...00. После этого если в командной части текущего информационного сообщения от ВУ не содержится кодовая комбинация КС, то осуществляются операции, обеспечивающие запись единицы информации от ВУ в первую свободную (в данном случае в третью) ячейку соответствующей информационной зоны блока 14.

Если запись очередной информации от ВУ не, приводит к полному заполнению соответствующей зоны, то устройство заканчивает цикл своей работы с данными ВУ. Сигнал с единичного первого выхода проходит по цепочке из элемента ИЛИ 42, элемента 47 задержки, элементов ИЛИ 43 и элемента И 30, и на выходе элемента ИЛИ 36 формируется единичный сигнал, устанавливающий сдвиговый регистр 56 в состояние 100..OOj а триггер 44 - в О. Таким образом, на вход элемента И 27 поступает единичный сигнал с триггера 44, а с второго входа элемента И 28 единичный сигнал снимается. На кольцевой сдвиговый регистр 16 блока 7 начинают поступать через элемент И 27 сдвигающие сигналы с генератора 26 блока 8, позволяющие выбрать следующее ВУ, готовое к реализации операции обмена в направлении I.

03069

структуры выдается на выходной

регистр 4. Это происходит следующим образом.

На шестой вход блока 8 поступает единичный сигнал с единичного выхода К-го разряда регистра 5.

Через элемент 2И-ИЛИ 55 и элемент 48, необходимый для задержки сигнала, инициирующего чтение из блока 14 и других сигналов на время, необходимое для записи в соответствующую ин- формапионную зону блока 14 последней единицы информации от ВУ (ею может 15 быть и код КС), на выходах блока 8 формируются следующие сигналы:

на семнадцатом выходе блока 8 сигнал Обращение к

на седьмом выходе блока 8 сигнал 2Q Чтение 2 (ЧТ2), устанавливающий триггер 13 в 1 через элемент ИЛИ 12} таким образом, на входе блока

14 формируется сигнал, определяющий операцию чтения из блока 14 с этого

25 же выхода блока 8 на вход регистра 4 подается управляющий сигнал разре- щения приема кoдaJ

на шестом выходе блока 8 сигнал .Вьщать код с регистра 1. 30 воздействием описанных управляющих сигналов происходит запись сформированного сообщения на регистр 4. С выходного регистра 4 это сообщение может быть в дальнейшем выдано на информационный выход 66 устройства и передано для обработки в ЭВМ.

Разряды выходной информационной щины блока 14,соответствующие разрядам маски, с информационными входами ре40 гистра 4 не коммутируются. Таким образом, на регистре 4 формируется сообщение описанной структуры.

С выхода элемента 48 единичный сигнал поступает на вход элемента

дс 50.задержки, необходимого для задержки сигналов, обеспечивающих обнуление соответствующей информационной зоны блока 14. Эти сигналы формируются на шестом и восемнадцатом выходах блока 8. С восемнадцатого выхода блока 8 на вход блока 14 подается сигнал обнуления информационной зоны блока 14, соответствующей признаку, который подается под воздействием управляющего сигнала с шестого выхода блока 8 с регистра 1 на адресные входы блока 14. Маска во второй ячейке информационной зоны устанавливается в 010...00.

35

50

55

рын является выходом 67 устройства, формируется сигнал Конец операции обмена с ВУ черея элемент ИЛИ 42, элемент 47 задержки, элемент ИЛИ 43, элемент И 30, элемент ИЛИ 36 и элемент И 31. Этот сигнал может быть использован для инициирования передачи сформированного на регистре 4 сообщения для дальнейшей обработки в ЭВМ. 9. Рассмотрим ситуацию, при которой в командной час ти текущего информационного сообщения от ВУ содержится вместо кода КЗ код КС, т.е. ВУ закон- 15 элемент ИЛИ 36 сигнал, устанавлива- чило вьщачу информации в направле- ющий сдвиговый регистр 56 в 100...00

10

полностью заполнена, устройством было сформировано информационное сообще- ние и вьдано на выходной регистр 4,

В этом случае запись кода КС в информационную зону блока 14, соот- ветствзтощую данному БУ, не производится, а сигналы КС и сигнал на третьем входе блока 8, свидетельствующий о том, что третий разряд ре- гистра 5 модифицированной маски единичный, формирует через элементы И 33 ,элемент ИЛИ 43,элемент И 30 и

НИИ I.

В этом случае устройство повторя последовательность операций, описанных в пп. 1-8, с тем отличием, что код КС записывается предварительно в регистр 3 и далее рассматривается как единица информации, поступившей от ВУ. Таким образом, вьтолняется следующая последовательность операций.

Аналогично описанному после выполнения операций по пп. 1-3 на пятом выходе блока 8 формируется сигнал, разрешающий дешифрацию и поступающий на управляющий вход дешифратора 11 .

В соответствии с содержимым регистра 2 на первом выходе дешифратора 11 появляется единичньш сигнал, поступающий на первый вход блока 8 и далее через элемент ИЛИ 57 н вход регистра 3. Одновременно на вход регистра 2 подается сигнал с первого выхода дешифратора 11. Таким образом в регистр 3 записьша- ется код КС.

Сигнал с первого входа блока 8 поступает также через элемент И 32 на единичный вход триггера 53, уста ливая его в l.

Далее осуществляются операции, описанные в пп. 3-8, с тем отличием, что роль сигнала на втором входе блока 8 выполняет единичный сигнал на выходе триггера 53.

Исключение составляет случай, когда в описьшаемой ситуации после модификации маски оказывается, что ее третий разряд установлен в 1. Это свидетельствует о том, что информационная зона, соответствующая данному ВУ, пуста, т.е. в предыдущем цикле работы устройства с данэлемент ИЛИ 36 сигнал, устанавлива- ющий сдвиговый регистр 56 в 100...00

полностью заполнена, устройством было сформировано информационное сообще- ние и вьдано на выходной регистр 4,

В этом случае запись кода КС в информационную зону блока 14, соот- ветствзтощую данному БУ, не производится, а сигналы КС и сигнал на третьем входе блока 8, свидетельствующий о том, что третий разряд ре- гистра 5 модифицированной маски единичный, формирует через элементы И 33 ,элемент ИЛИ 43,элемент И 30 и

0

0

5

и триггер 44 в О. Далее возможен процесс выборки следующего ВУ.

Рассмотрим процесс обмена в направлении II.

Обмен информацией в направлении II возможен между ЭВМ и ВУ, которое в момент поступления на вход 68 устройства запроса на обмен от ЭВМ в 5 направлении II не работает с устройством в направлении I. В последнем случае ЭВМ ожидает конца цикла работы устройства с ВУ, после чего начинает обмен в направлении II.

Обмен в направлении II осуществляется следующим образом.

На входы дешифратора 23 блока.7 по группе адресных входов 58 устройства поступает от ЭВМ адрес требуемого ВУ.

На входы передатчика 22 блока 7 по группе информационных входов 59 устройства поступает от ЭВМ информация для ВУ.

Сигнал запроса на обмен поступает от ЭВМ по входу 68 устройства на единичньш вход триггера 24 блока 7 и устанавливает его в 1. Эта единица поступает на управляющий вход узла 19 сравнения, разрешая проверку этим узлом кодовых комбинаций, поступающих с выходов группы элементов И 18 блока 7 и с выходов дешифратора 23, на идентичность.

Кодовая комбинация с вьгходов элементов И 18 определяет устройство, выбранное и осуществляющее обмен в направлении I. Кодовая комбинация с. выходов дешифратора 23 определяет ВУ, требуемое ЭВМ для обмена в на- правлении II. В случае их совпадения на выходе узла 19 сравнения формируется нулевой сигнал и обмен в направлении II блокируется, гакО

5

0

5

как отсутствует разрешающий прохождение информации через передатчик 22 на Соответствующее ВУ единичный сигнал на управляющем входе передатчика 22.

В случае несовпадения указанных кодовых комбинаций узел 19 сравнения формирует на своем выходе единичный сигнал. В результате разрешается прохождение информации от ЭВМ на ВУ через передатчик 22. Сигнал с выхода узла 19 сравнения поступает также на элемент 21 задержки, который через время, необходимое для окончания переходных процессов в передатчике 22, формирует на своем выходе сигнал, поступающий на все вторые входы ;группы элементов И 1 7,первые входы котрых соединены с выходами дешифратора 23. Таким образом, на выходе одного из элементов И 17 группы и, следовательно, на одном из выходов группы выходов 65 устройства формируется сигнал, инициирующий операцию обмена соответствующим ВУ.

С выходов передатчика 22, являющихся группой информационных ,выходов 64 устройства, на соответствующее ВУ поступает информация блоками.

Конец информационного сообщения от ЭВМ на ВУ определяется поступлением на входы распределителя кодовой комбинации Конец сообщения от ЭВМ. Эта кодовая комбинация проходит на выходы передатчика 22 блока 7 и направляется на соответствующее ВУ и одновременно на входы дешифратора 20, который в этом формирует на выходе единичный сигнал, устанавливая триггер 24 в О, и единичный сигнал с нулевого выхода этого триггера поступает на второй управляющий вход узла 19 сравнения, устанавливая О на его выходе и блокируя дальнейшее прохождение какой-либо информации через передатчик 22.

При поступлении очередного запроса от ЭВМ на обмен в направлении II описанные операции повторяются.

Формула изобретения

стороннего обмена данными между ЭВМ и внешними устройствами, в него введены блок обработки запросов, узел маскирования, дешифратор, четыре регистра, триггер, элемент ИЛИ, причем первая и вторая группы информационных входов блока обработки запросов образуют группы входов устройства для подключения соответственно к группам адресных и информа- ционных выходов ЭВМ, вход запуска блока обработки запросов является входом устройства для подключения

к выходу запроса на обмен ЭВМ, информационный выход первого регистра является выходом устройств для подключения к информационному входу ЭВМ, первый выход блока упрарления является выходом устройства для подключения к входу записи ЭВМ, третья группа инфомационных входов блока обработки запросов образует группу входов устройства для подключения к выходам готовности внешних устройств, первая и вторая группы информационных входов первого коммутатора образуют группы входов .устройства для подключения соответственно к адресным и информационным выходам внешних устройств, первая, вторая и третья группы информационных выходов блока обработки запросов образуют группы выходов устройства для подключения соответственно к адресным, информационным входам и входам запросавнешних устройств, при этом второй выход блока управления соединен с входом записи второго регистра, первый информационный вход которого соединен с первым выходом первого коммутатора, второй и третий выходы которого соединены с информационными входами третьего и четвертого регистров соответственно, входы записи которых соединены с установочным входом первого регистра и с третьим выходом блока управления, четвертый выход

которого соединен с входом чтения второго регистра, второй кнформацион- ньй вход которого соединен с информационным входом дешифратора и с выходом третьего регистра, вход чтения которого соединен с первым выходом дешифратора и с первым входом логического условия блока управления, пятый выход которого соединен со стробирующим входом дешифратора.

второй выход которого соединен с вторым входом логического условия блока управления, шестой выход которого соединен с входом чтения четвертого регистра, выход которого соединен с адресным входом блока.памяти, млад- Iшие и старшие разряды группы информационных выходов которого соединены соответственно с группами информационных входов первого и пятого регистров, вход записи первого регистра соединен с первым входом элемента I ИЛИ и с седьмым выходом блока управ- 1ления, восьмой выход которого соеди- Iнен с вторым входом элемента ИЛИ, I выход которого соединен с единичным входом триггера, единичный и нулевой выходы которого соединены соответственно с входами разрешения чтения и i записи блока памяти, информационный вход которого соединен с информационным выходом узла маскирования, перва группа информационных входов которо- I го соединена с группой выходов пято- |. го регистра, входы записи, сдвига, I чтения и синхронизации которого соеi динены соответственно с девятым, де- сятым, одиннадцатым и двенадцатым вы I ходами блока упр авления,- тринадцатый и четырнадцатый выходы которого i соединены соответственно с первым и вторым управляющими входами вто- рюго коммутатора, первая, вторая группы информационнных входов и группа выходов которого соединены соответственно с группами выходов второго, шестого регистров и с второй группой информационных входов узла маскирования, третий и К-й разряды группы выходов пятого регистра соединены соответственно с третьим и четвертым входами логического условия блока управления, пятый вход логического условия которого соединен с выходом запроса блока oбpaбoтки, запросов, тактовый вход которого соединен с пятнадцатьм выходом блока управления, шестнадцатый, семнадцатый и восемнадцатый выходы которого соединены соответственно с кулевыми входами триггера, с син- хровходом и установочным вхо - дом блока памяти, девятнадцатый и двадцатый вькоды блока управления соединены сйответственно с установочным входом и входом чтения шестого . регистра, (К+1)-й разряд группы выходов пятого регистра соединен

с установочным входом пятого регистра, группа выходов выборки блока обработки запросов соединена с группой управляющих входов первого ком- мутатора.

2, Устройство по п. 1, о т л и- чающееся тем, что блок управления содержит сдвиговый регистр,

четыре триггера, генератор импульсов, восемь элементов И, десять элементов ИЛИ, семь элементов задержки, элемент И-ИЛИ, причем первый вход первого элемента И соединен с первы5 ми входами второго, третьего элементов И и первого элемента ИЛИ и является первым входом логического условия блока, первый вход второго элемента ИЛИ соединен с первыми входами третьего и четвертого элементов ИЛИ и является вторым входом логического..условия блока, второй вход первого элемента И соединен с вторым входом второго элемента И и является

5 третьим входом логического условия блока, первый вход элемента И-ИЛИ является четвертым входом логического условия блока, единичной вход первого триггера соединен с входом

0 первого элемента задержки и является пятым входом логического условия блока, выходы четвертого элемента И и первого элемента ИЛИ являются соответственно первым и вторым выходами блока, выход первого триггера

0

5

0

соединен с единичным входом второго триггера, с вторым входом первого элемента ИЛИ и является третьим и девятнадцатым выходом блока, первый выход сдвигового регистра соединен

5

с первыми входами пятого, шестого, седьмого элементов ИЛИ, с вторым и третьим входами элемента И-ИЛИ, с вторым входом четвертого элемента ИЛИ, с единичным входом третьего триггера и является четвертым выходом блока, выходы пятого элемента И, четвертого элемента ИЛИ являются соответственно пятым и шестым выходами блока, выход второго элемента задержки соединен с входом третьего элемента задержки, с третьим входом четвертого элемента ИЛИ, С вторым входом пятого элемента ИЛИ и является седьмым выходом блока, выход третьего элемента ИЛИ соединен с третьим входом пятого элемента ИЛИ и является восьмым выходом блока, выход четвертого элемента задержки

0

15

является девятым выходом блока, второй выход сдвигового регистра соединен с п ервым входом восьмого элемента ИЛИ и является десятым и шестнадцатым выходами блока, выход седьмого элемента ИЛИ является одиннадцатым выходом блока, выход пятого элемента задержки соединен с первым входом девятого элемента ИЛИ, с вторым входом восьмого элемента ИЛИ и является двенадцатым выходом блока, единичный и нулевой выходы третьего триггера являются соответственно . тринадцатым и четырнадцатым выходами блока, выходы шестого элемента И пятого элемента ИЛИ, шестого элемента задержки являются соответственно пятнадцатым, семнадцатым и восемнадцатым выходами блока, третий выход сдвигового регистра соединен с четвертыми входами четвертого, пятого элементов ИЛИ, с вторым входом седьмого элемента ИЛИ и является двадцатым выходом блока, при этом в блоке управления выход генератора импульсов соединен с первым входом седьмого элемента И и с первым входом шестого элемента И, второй вход которого соединен с нулевым входом четвертого триггера и с нулевым выходом второго триггера, единичный выход которого соединен с вторым входом седьмого элемента И, выход которого.соединен с тактовым входом сдвигового регистра, четвертый выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с нулевым выходом четвертого триггера, единичный вход которого соединен с выходом второго элемента И, выход первого элемента задержки соединен с нулевым входом- первого триггера, установочный вход сдвигового регистра соединен с нулевым входом второго триггера, с первым входом четвертого элемента И и с выходом девятого элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента И, первый вход которого соединен с входами пятого элемента задержки и с выходом третьего элемента И, второй вход которого соединен с вторым входом восьмого элемента И и с выходом десятого элемента ИЛИ, первый вход которого соединен с третьим входом третьего элемента И и с вьжодом первого элемента И, второй втсод десято03069I 6

го элемента ИЛИ соединен с выходом седьмого элемента задержки, вход которого соединен с выходом шестого элемента ИЛИ, второй вход которого соединен с входом второго элемента задержки и с выходом элемента И-ИЛИ, четвертый вход которого соединен с единичным выходом четвертого триг1Q гера, с вторыми входами третьего и второго элементов ИЛИ, с пятым входом четвертого элемента ИЛИ, шестой вход которого соединен с выходом третьего элемента задержки, с вхо15 дом шестого элемента задержки, с вторым входом четвертого элемента И, выход второго элемента ИЛИ соединен с входом четвертого элемента задержки, выход восьмого элемента

2Q ИЛИ соединен с единичным входом третьего триггера.

30 тактовым входом блока, выход элемента ИЛИ является выходом запроса блока, единичньш вход триггера является входом запуска блока, группы информационных входов первого дешифратора, приемника, первые входы элементов И первой группы образуют соответственно первую, вторую и третью группы информационных входов блока, группа выходов первого дешиф Q ратора соединена с первыми входами элементов И второй группы, с первой группой входов узла сравнения и образует первую группу информационных выходов блока, группа информационных выходов передатчика соединена с группой информационных входов второго дешифратора и образует вторую группу информационных выходов блока, выходы элементов И второй группы образуют третью группу информационных выходов блока, выходы элементов И первой группы соединены с группой входов элемента ИЛИ, с второй группой входов узла сравнения и образуют группу выходов выборки блока, при этом в блоке обработки запросов группа выходов сдвигового регистра соединена с вторыми входами элементов И первой группы, вто35

50

55

17

1403069

рые входы элементов И второй группы соединены с выходом элемента задержки, вход которого соединен с управляющим входом передатчика и с выходом узла сравнения, первый и вто69

рой управляющие входы которого соединены соответственно с единичным и нулевым выходами триггера, нулевой вход которого соединен с выходом второго дешифратора.

фие.1

B0.i 6(2 Q/r

mi

6d 56

Kd

фав.г

CNtf.5

| Авторское свидетельство СССР 562811, кл, G 06 F 13/00, 1977 | |||

| Прибор для измерения малых перемещений | 1949 |

|

SU77999A2 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-15—Публикация

1986-08-04—Подача