Изобретение относится к вьмисли- тельной технике и может быть использовано в вычислительных системах, в которых используется конвейерная об- работка.

Цель изобретения - повьшение быстродействия вычислительного устройства.

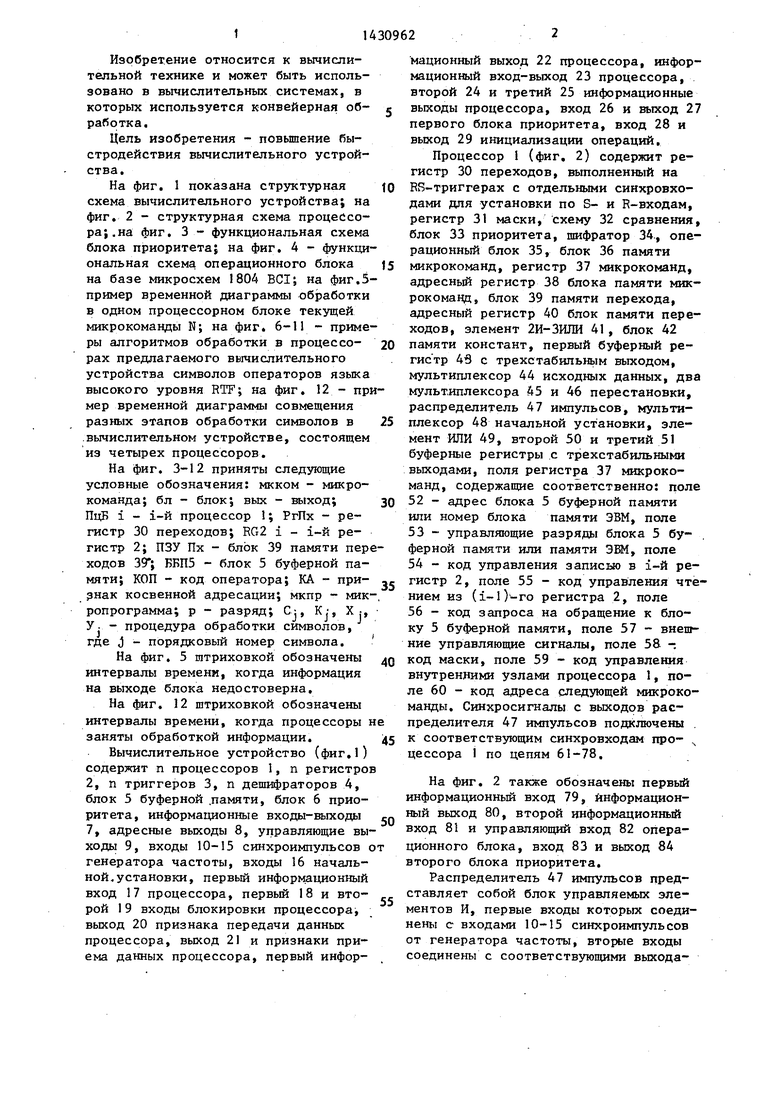

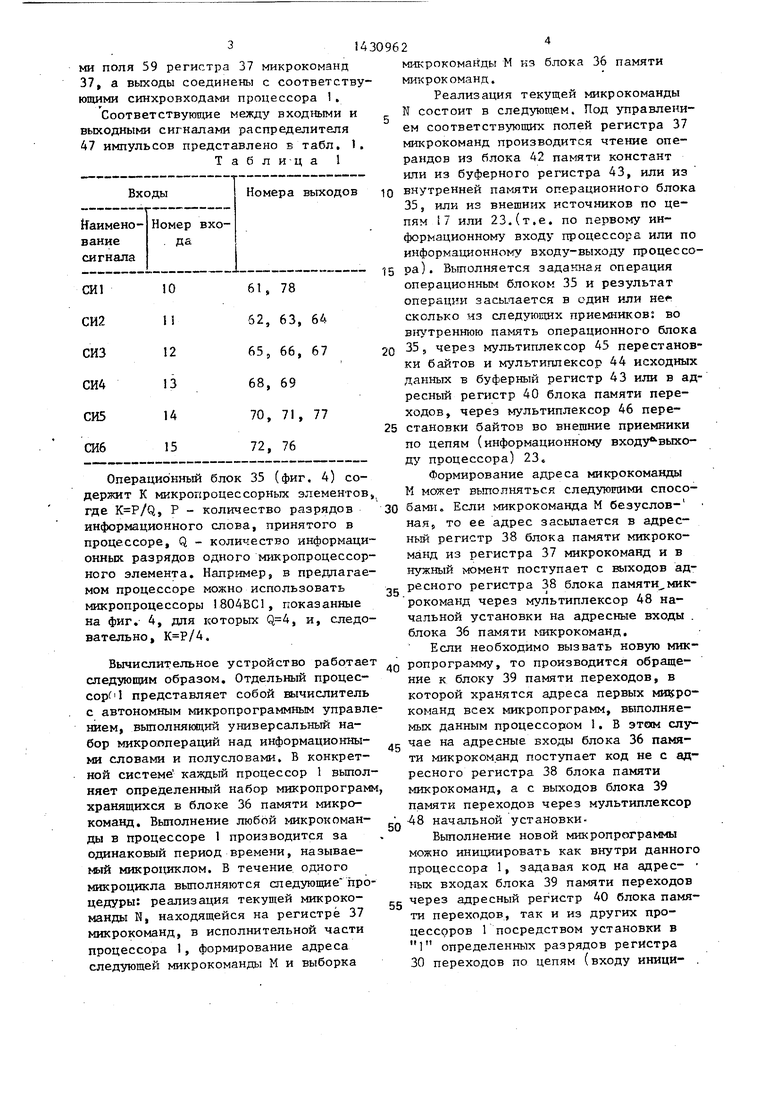

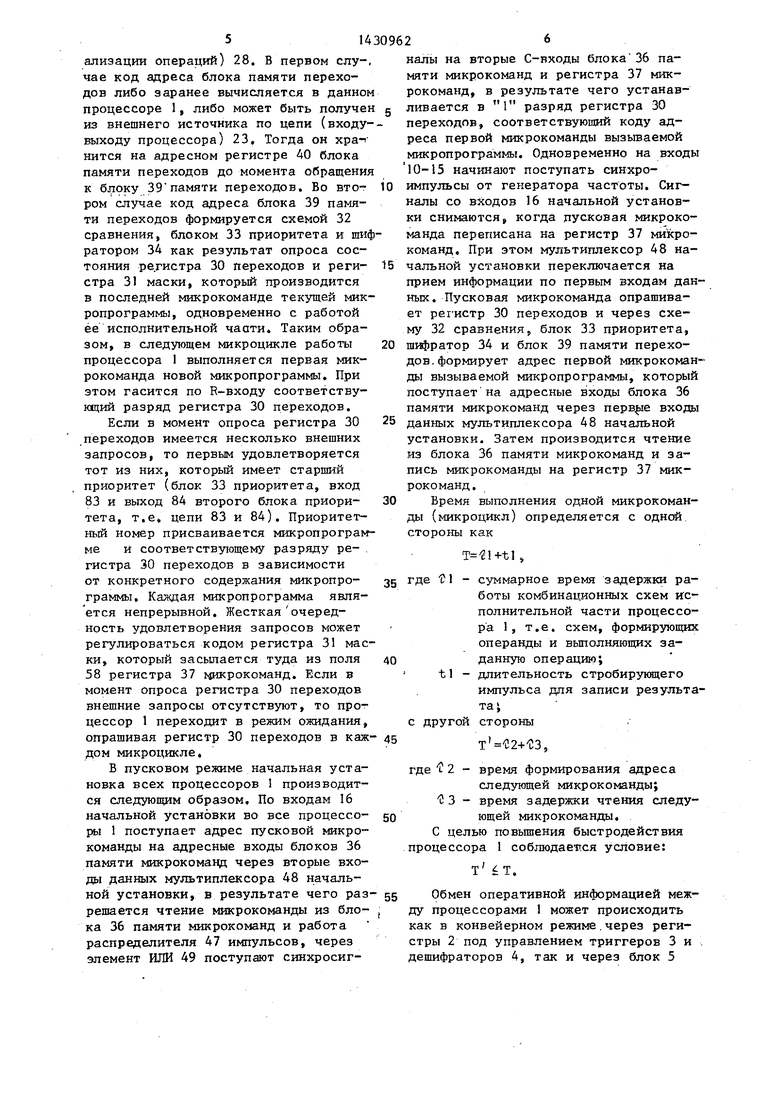

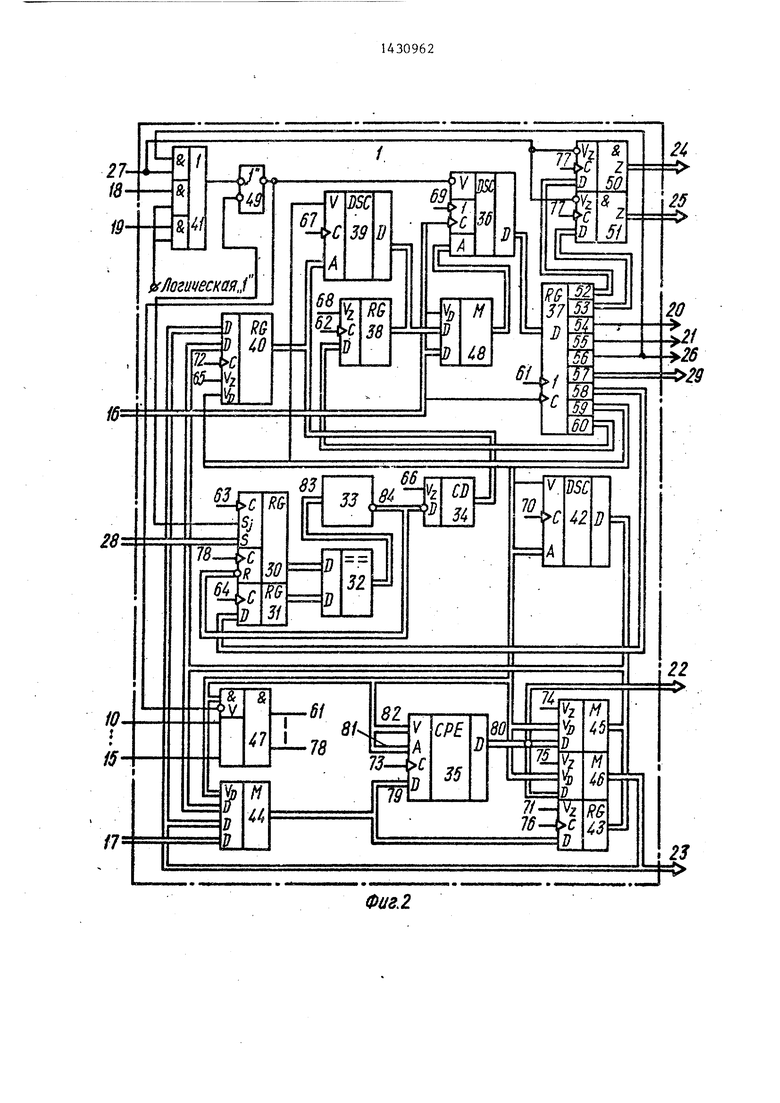

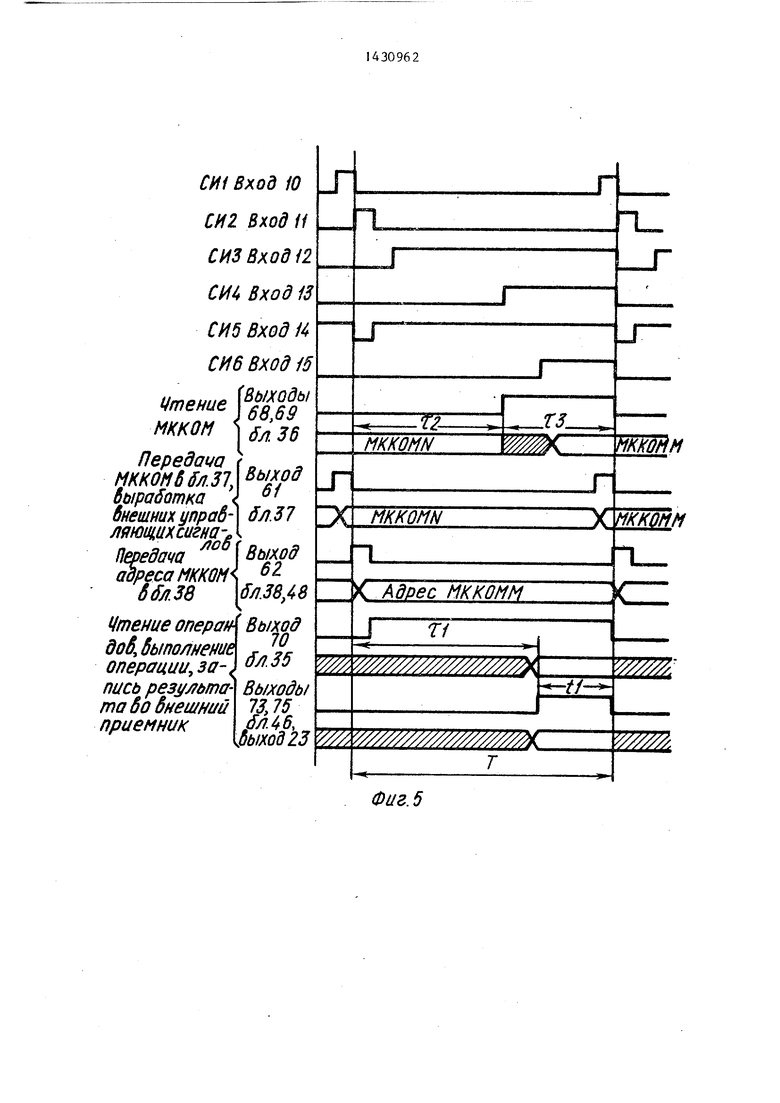

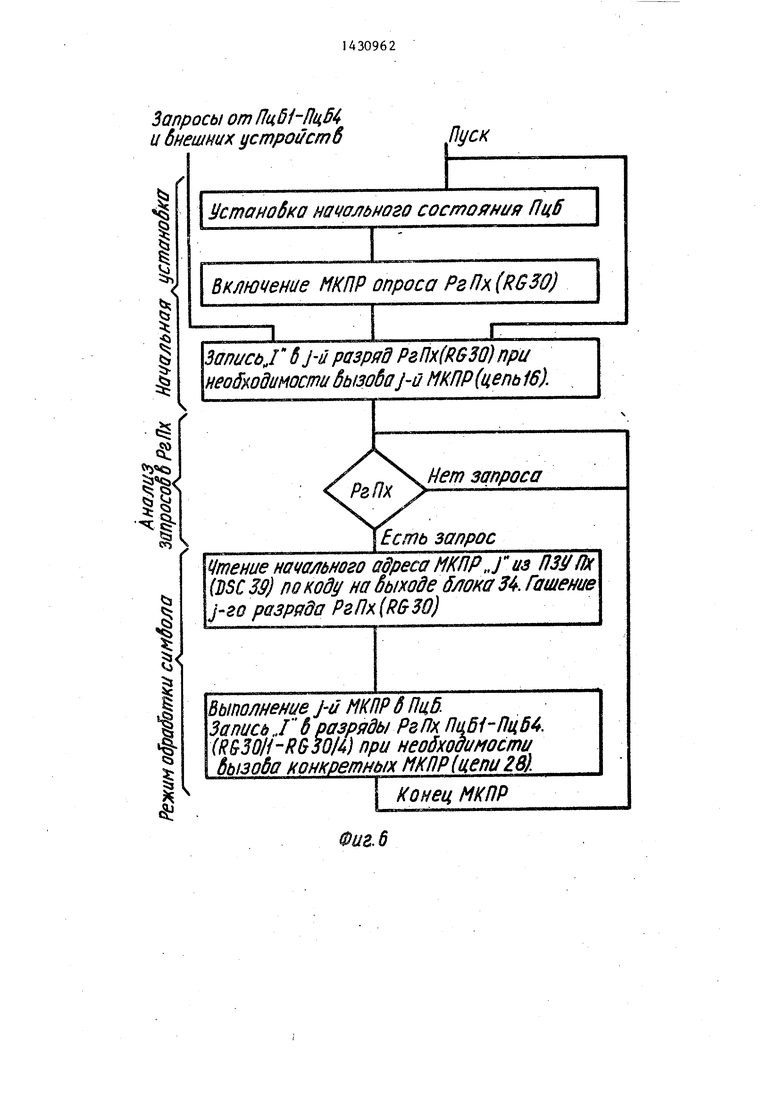

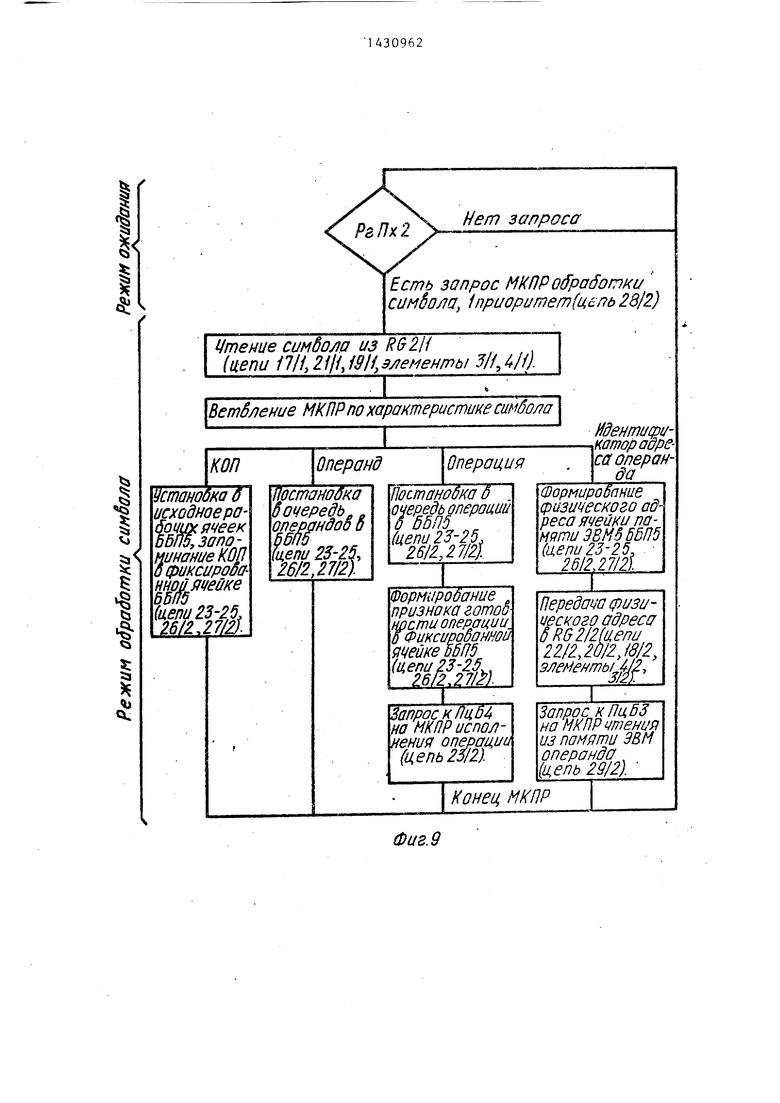

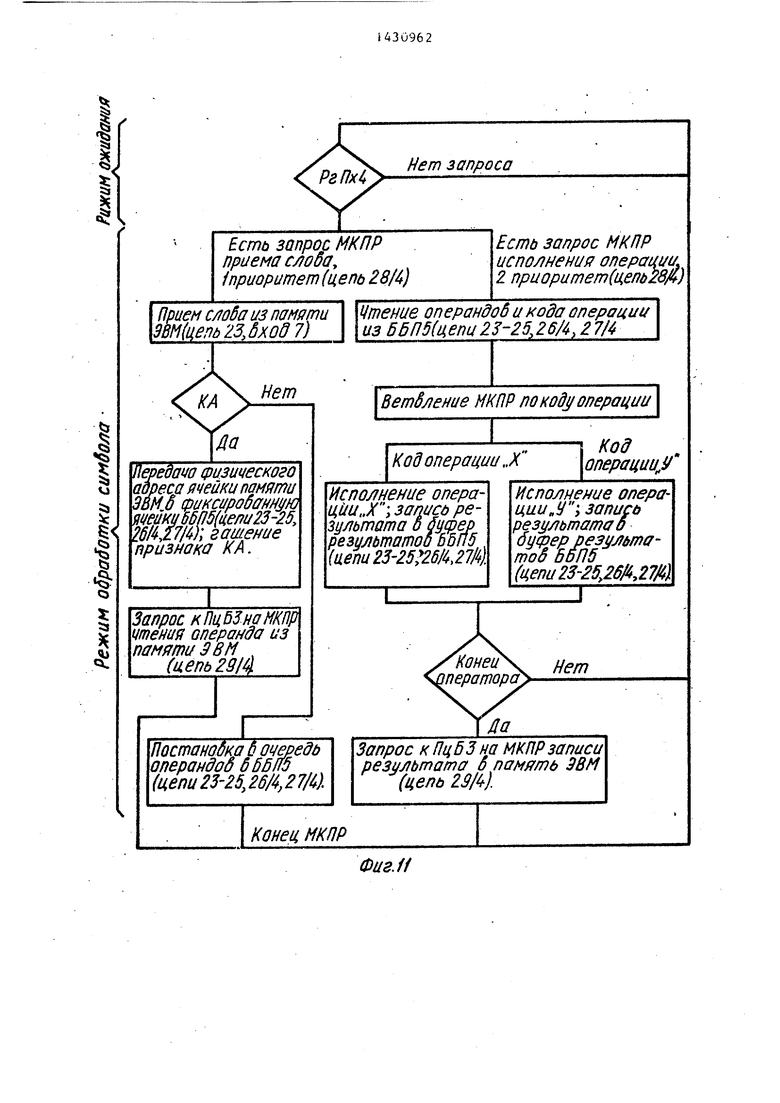

На фиг. 1 показана структурная схема вычислительного устройства; на фиг. 2 - структурная схема процессора;, на фиг. 3 - функциональная схема блока приоритета; на фиг. 4 - функциональная схема операционного блока на базе микросхем 1804 BCI; на фиг.5- пример временной диаграммы обработки в одном процессорном блоке текущей микрокоманды N; на фиг. 6-11 - примеры алгоритмов обработки в процессо- pax предлагаемого ввтислительного устройства символов операторов языка высокого уровня RTF; на фиг. 12 - пример временной диаграммы совмещения разных этапов обработки символов в вычислительном устройстве, состоящем из четырех процессоров.

На фиг. 3-12 приняты следующие условные обозначения: мкком - микрокоманда; бл - блок; вых - выход; ПцБ i - i-й процессор 1; РгПх - регистр 30 переходов; RG2 1 - i-й регистр 2; ПЗУ Пх - блок 39 памяти переходов ББП5 - блок 5 буферной памяти; КОП - код оператора; КА - при- знак косвенной адресации; мкпр - микропрограмма; р - разряд; С:, К;, X ;, у. - процедура обработки символов, где j - порядковый номер символа.

На фиг. 5 щтриховкой обозначены интервалы времени, когда информация на выходе блока недостоверна.

На фиг. 12 штриховкой обозначены интервалы времени, когда процессоры н заняты обработкой информации.

Вычислительное устройство (фиг.1) содержит п процессоров 1, п регистров 2, п триггеров 3, п дешифраторов 4, блок 5 буферной .памяти, блок 6 приоритета, информационные входы-выходы

7, адресные выходы 8, уцравляющие выходы 9, входы 10-15 синхроимпульсов о генератора частоты, входы 16 начальной, установки, первый информационный вход 17 процессора, первый 18 и второй 19 входы блокировки процессора, выход 20 признака передачи данных процессора, выход 21 и признаки приема данных процессора, первый инфор-

мационный выход 22 процессора, информационный вход-выход 23 процессора, второй 24 и третий 25 информационные выходы процессора, вход 26 и выход 27 первого блока приоритета, вход 28 и выход 29 инициализации операций.

Процессор 1 (фиг, 2) содержит регистр 30 переходов, вьшолненный на RS-триггерах с отдельными синхровхо- дами для установки по S- и R-входам, регистр 31 маски, схему 32 сравнения, блок 33 приоритета, шифратор 34., операционный блок 35, блок 36 памяти микрокоманд, регистр 37 микрокоманд, адресный регистр 38 блока памяти микрокоманд, блок 39 памяти перехода, адресный регистр 40 блок памяти переходов, злемент 2И-ЗИЛИ 41, блок 42 памяти констант, первый буферный ре- гис тр 43 с трехстабнпьньш выходом, мультиплексор 44 исходных данных, два мультиплексора 45 и 46 перестановки, распределитель 47 импульсов, мультиплексор 48 начальной установки, злемент ИЛИ 49, второй 50 и третий 51 буферные регистры с трехстабильными выходами, поля регистра 37 микрокоманд, содержащие соответственно: поле

52- адрес блока 5 буферной памяти или номер блока памяти ЭВМ, поле

53- управляющие разряды блока 5 буферной памяти или памяти ЭВМ, поле

54- код управления запись в i-й регистр 2, поле 55 - код управления чтением из (i-l)-ro регистра 2, поле

56 - код запроса на обращение к блоку 5 буферной памяти, поле 57 - внешние управляющие сигналы, поле 58 -. код маски, поле 59 - код управления внутренними узлами процессора 1, поле 60 - код адреса следующей микрокоманды. Синхросигналы с выходов распределителя 47 импульсов подключены . к соответствующим синхровходам про- цессора 1 по цепям 61-78.

На фиг. 2 также обозначены первый информационный вход 79, информационный выход 80, второй информационный вход 81 и управляющий вход 82 операционного блока, вход 83 и выход 84 второго блока приоритета.

Распределитель 47 импульсов представляет собой блок управляемых элементов И, первые входы которых соединены с входами 10-15 синхроимпульсов от генератора частоты, вторые входы соединены с соответствующими выходами поля 59 регистра 37 микрокоманд 37, а выходы соединены с соответствующими синхровходами процессора 1 .

Соответствующие между входными и выходными сигналами распределителя 47 импульсов представлено в табл. 1. Т а 6 л и-ц а 1

СИ1 СИ2 СИЗ СИ4 СИЗ СИ6

Операционный блок 35 (фиг. 4) содержит К микропроцессорных элементов где , Р - количество разрядов информационного слова, принятого в процессоре, Q - количество информационных разрядов одного микропроцессорного элемента. Например, в предлагаемом процессоре можно использовать микропроцессоры 1804БС1, показанные на фиг,- 4, для которых , и, следовательно, ,

Вычислительное устройство работает следующим образом. Отдельньш процес- copOl представляет собой вычислитель с автономным микропрограммным управлением, вьшолняющкй универсальный набор микроопераций над информационными словами и полусловами. Б конкретной системе каждый процессор 1 выполняет определенньш набор микропрограмм хранящихся в блоке 36 памяти микрокоманд. Выполнение любой микрокоманды в процессоре 1 производится за одинаковый период времени, называемый микроциклом. В течение одного микроцикла вьтолняются следующие процедуры: реализация текущей микрокоманды и, находящейся на регистре 37 микрокоманд, в исполнительной части процессора 1, формирование адреса следующей микрокоманды М и выборка

микрокоманды М кз блока 36 памяти микрокоманд.

Реализация текущей микрокоманды N состоит в следующем. Под управлением соответствующих полей регистра 37 микрокоманд производится чтение операндов из блока 42 памяти констант или из буферного регистра 43, или из

внутренней памяти операционного блока 35, или из внешних источников по цепям 17 или 23.(т.е. по первому информационному входу процессора или по информационному входу-выходу процессора). Выполняется заданная операция операционным блоком 35 и результат операции засьшается в один или Hef сколько из следующих приемников: во внутреннюю память операционного блока

355 через мультиплексор 45 перестановки байтов и мультиплексор 44 исходных данных в буферный регистр 43 или в адресный регистр 40 блока памяти переходов, через мультиплексор 46 перестановки байтов во внешние приемники по цепям (информационному входу выхо- ду процессора) 23.

Формирование адреса микрокоманды К может выполняться следующими способами. Если микрокоманда М безуслов- ная, то ее адрес засылается в адресный регистр 38 блока памяти микрокоманд из регистра 37 микрокоманд и в нужный момент поступает с выходов адресного регистра 38 блока памяти мик- рокоманд через мультиплексор 48 начальной установки на адресные входы блока 36 памяти микрокоманд.

Если необходимо вызвать новую микропрограмму, то производится обращение к блоку 39 памяти переходов, в которой хранятся адреса первых микрокоманд всех микропрограмм, выполняемых данным процессор(ом , В этом случае на адресные входы блока 36 памяти микрокоманд поступает код не с адресного регистра 38 блока памяти микрокоманд, а с выходов блока 39 памяти переходов через мультиплексор 48 начальной установкиВьтолнение новой микропрограммы можно инициировать как внутри данного процессора 1, задавая код на адрес- ных входах блока 39 памяти переходов

через адресный регистр 40 блока памяти переходов, так и из других про- цессрров 1 посредством установки в 1 определеннь1х разрядов регистра 30 переходов по цепям (входу иници- .

алиэации операций) 28. В первом слу-, чае код адреса блока памяти переходов либо заранее вычисляется в данном процессоре 1, либо может быть получен из внешнего источника по цепи (входувыходу процессора) 23, Тогда он нится на адресном регистре 40 блока памяти переходов до момента обращения к блоку 39 памяти переходов. Во вто-г ром случае код адреса блока 39 памяти переходов формируется схемой 32 сравнения, блоком 33 приоритета и шифратором 34 как результат опроса состояния ре.гистра 30 переходов и реги- стра 31 маски, который производится в последней микрокоманде текущей мкк- ропрограммы, одновременно с работой ее исполнительной части. Таким образом, в следующем микроцикле работы процессора 1 выполняется первая микрокоманда новой микропрограммы. При этом гасится по R-входу соответствующий разряд регистра 30 переходов.

Если в момент опроса регистра 30 переходов имеется несколько внешних запросов, то первым удовлетворяется тот из них, который имеет старший приоритет (блок 33 приоритета, вход 83 и вьгход 84 второго блока приори- тета, т.е. цепи 83 и 84). Приоритетный номер присваивается микропрограмме и соответствующему разряду ре- . гистра 30 переходов в зависимости от конкретного содержания микропро- граммы. Каждая микропрограмма является непрерывной. Жесткая очередность удовлетворения запросов может регулироваться кодом регистра 31 маски, который засылается туда из поля 58 регистра 37 4икpoкoмaнд. Если в момент опроса регистра 30 переходов внешние запросы отсутствуют, то процессор 1 переходит в режим ожидания, опрашивая регистр 30 переходов в каж- дом микроцикле,

В пусковом режиме начальная установка всех процессоров 1 производится следующим образом. По входам 16 начальной установки во все процессо- ры 1 поступает адрес пусковой микрокоманды на адресные входы блоков 36 памяти микрокоманд через вторые входы данных мультиплексора 48 начальной установки, в результате чего раз- решается чтение микрокоманды из бло- ка 36 памяти микрокоманд и работа распределителя 47 импульсов, через элемент ИЛИ 49 поступают синхросигналы на вторые С-входы блока 36 памяти микрокоманд и регистра 37 микрокоманд, в результате чего устанавливается в 1 разряд регистра 30 переходов, соответствующий коду адреса первой микрокоманды вызываемой микропрограммы. Одновременно на входы 10-15 начинают поступать синхроимпульсы от генератора частоты. Сигналы со входов 16 начальной установки снимаются, когда пусковая микрокоманда переписана на регистр 37 микрокоманд. При этом мультиплексор 48 начальной установки переключается на прием информации по первым входам дан ных. Пусковая микрокоманда опрашивает регистр 30 переходов и через схему 32 сравнения, блок 33 приоритета, шифратор 34 и блок 39 памяти переходов, формирует адрес первой микрокоманды вызываемой микропрограммы, который поступает на адресные входы блока 36 памяти микрокоманд через входы данных мультиплексора 48 начальной установки. Затем производится чтение из блока 36 памяти микрокоманд и запись микрокоманды на регистр 37 микрокоманд .

Время выполнения одной микрокоманды (микроцикл) определяется с одной стороны как

T IIl+tl,

где - суммарное время задержки работы комбинационных схем исполнительной части процессора 1, т.е. схем, формирующих операнды и вьшолнянпцих заданную операцию; tl - длительность стробирукщего

импульса для записи результата J

с другой стороны

Т С2+ СЗ,

где I) 2 - время формирования адреса

следующей микрокоманды; 1 3 - время задержки чтения следующей микрокоманды, С целью повышения быстродействия процессора 1 соблюдаеттся условие:

т т.

Обмен оперативной информацией между процессорами 1 может происходить как в конвейерном режиме,через регистры 2 под управлением триггеров 3 и дешифраторов 4, так и через блок 5

буферное памяти под управлением блока 6 приоритета. Конвейерная передача информации используется в наиболее срочных процедурах, когда нужно ис- ключить задержку, вносимую передачей через блок 5 буферной памяти. Информация, которую нужно передать из 1-го процессора 1 в {1+1)-й процессор , поступает с выходов i-ro процессора 1 по цепям 22 (т,е. по первому информационному выходу процессора) на ин- формационные входы i-ro регистра 2, а (х+О-й процессор 1 считывает ее с. выходов регистра 2 на свои информаци- онные входы по цепям (первому информационному входу процессора) 17, Управление конвейерной передачей информации из i-ro процессора I в (1+1)-й процессор 1 осуществляют i-й триггер

3 и i-й дешифратор А, На первый вход i-ro дешифратора 4 поступает сигнал записи информации в i-й регистр 2 из i-ro процессора I (цепь (выход) 20). На второй вход i-ro дешифратора 4 поступает из (i+l)-ro процессора 1 сигнал чтения информации, записанной в i-OM регистре 2 (цепь (выход) 21),На третий вход i-ro дешифратора 4 поступает сигнал с выхода триггера 3, Единичное состояние (1) i-«-ro триггера 3 cooTBeTCTByet наличию информации в i-oM регистре 2, нулевое состояние (О) - отсутствию информации .

Соответствие между входными кодами i-ro дешифратора 4 и функций его выходных сигналов приведено в табл,2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1986 |

|

SU1332328A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

Изобретение относится к вычис-. лительной технике и может быть использовано в вычислительных системах, в которых используется конвейерная обработка. Цель изобретения - повышение быстродействия вычислительного устройства. Вычислительное устройство содержит п процессоров 1, п регистров 2, п триггеров 3, п дешифраторов 4, блок 5 буферной памяти, блок 6 приоритета, информационный вход-выход 7, информационный выход 8, управляющий выход 9, синхровходы 10-15, вход 16 начальной установки. 3 табл. 12 ил. , 9SliO/S« l-il 4ib 00 О to фие, 1

в RG2, Установка RG2; I- в 1 триггер 3, вход

ТгЗ

О 1 1

4100

5 1,0 1 Останов i-ro процессора

О Установка в О триггера 3

1 Установка в О К-вход

триггера 3, Оста-ТгЗ,

нов i-ro процес-Цепь

сора(вход)19

запрос на запись RG2 свободен.

)

д

Комбинация невозможна .

Комбинация невозможна.

Нет запросов.

Запрос на записьт RG2 занят.

Удовлетворяется запрос на чтение RG2 занят.

Одновременные запросы на запись и чтение, RG2 занят. Удовлетворяется запрос на чтение.

На цыходах 2 и 3 сигналы не вырабатываются, поскольку невозможен запрос на чтение информации из (i-fl)-ro процессора 1, если перед этим не было записи информации в 1-й регистр 2 из 1-го процессорного блока 1, так как чтение реализуется микропрограммой (i+l)-ro процессорного блока 1, включение которой инициируется i-ом процессором 1 после, того, как произведена запись в регистр 2.

Сигналы останова текущей микропрограммы в i-OM процессоре 1 поступают по цепям (входам) 18 и 19 на входы элемента 41, с выхода которого они передаются через элемент ИЛИ 49 на управляющие входы блока 36 памяти микрокоманд и распределителя 47 импульсов как сигналы запрета чтения следующей микрокоманды.

Через блок 5 буферной памяти, к которому может/ обращаться любой процессор 1 (буферные регистры 50 и 51 и цепи 24-26), производится обмен -Оперативной информацией, не требующей срочной передачи, по цепям (информационному входу-выходу, процессора) 23, При этом очередность удовлетворения запросов устанавливается блоком 6 приоритета. Приоритетные номера при- сваива отся процессором 1 в зависимости от срочности выполняемых ими процедур в к:онкретной системе. Первый номер имеет старший приоритет.

Блок 6 приоритета передает по цепи (выходу) 27 на управляющий вход соответствующего процессора 1 сигнал разрешения удовлетворения запроса из числа поступивших в данный момент по це- пям (входу) 26 и имеющего старший приоритет, При этом в данном процессоре 1 разрешается продолжение выполнения текущей микропрограммы. Если запрос i-ro дроцессора 1 не удовлет- воряется, то по цеди (выходу) 27 ло- стулает на его вход сигнал останова текущей микропрограммы до тех пор, пока запрос не будет удовлетворен. Сигналы разрешения и останова микро- программы поступают по цепи (выходу) 27 через элементы 2И-ЗИЛИ 41 и ИЛИ 49 на управляюшие входы блока 36 памяти микрокоманд и распределителя 47

импульсов,

Если процессор с номером К записал в блок 5 буферной памяти информацию, которая должна быть обработана помощью определенной микропрограммы

в процессоре с номером М, то он вырабатывает сигнал на управляюшим выходе 29, который поступает по цепи (входу) 28 на конкретный вход регистра 30 переходов процессора (номер М) в качестве запроса на включение , соответствующей микропрограммы..

Работа и числительного устройства поясняется на примере обработки символов оператора языка высокого уров - ня RTF (фиг, 6-11), Под символом здесь и в дальнейшем понимается минимальная единица командной информации в языке RTF, Для обеспечения требуемого быстродействия вычислительного устройства принято ,

В табя, 3 приведена форма представления символов оператора языка RTF, поступающих в вычислительное устройство из памяти ЭВМ. Каждый символ имеет два поля; первое содержит характеристику символа, второе - код символа. Первым символом оператора всегда является код оператора. Далее .следует набор операндов и операций, представленных в польской записи. Операнд либо записан непосредственно в символе, либо хранится в ячейке памяти ЭВМ, В последнем случае символ содержит идентификатор адреса операнда, из которого формируется физический адрес ячейки памяти ЭВМ путем сложения с содержимым базового и индексного регистров, указанных в характеристике символа. Если в характеристике символа имеется признак косвенной адресации, то адресуемая ячейка памяти ЭВМ содержит в свою очередь адрес ячейки памяти ЭВМ, в которой находится операнд. В этом случае для получения операнда вьгаолняются два обращения к памяти ЭВМ,

Т а б л и -1 а 3

1Код оператора Код оператора

2Индентификатор Код идентифика- адреса операнда тора

3Операнд

4Операция

Код операнда Код операции

5 Идентификатор Код идентифика- адреса операнда тора

П1430962

Продолжение табл.3

3

Операция

Код операции

Признак конца оператора

На фиг. 6 показан алгоритм работы любого процессора в составе вычислительного устройства. Возможны следующие режимы его работы:

Пусковой режим, в котором производится начальная установка и включается опрос регистра 30 переходов. Если при пуске вьтислительного устройства требуется вызвать в данном процессоре определенную микропрограмму, то в этом режиме устанавливается в 1 соответствующий разряд регистра 30 переходов.

Режим анализа запросов в регистре. 30 переходов, который при отсутствии запросов является режимом ожидания, а при наличии запросов включает выполнекие микропрограммы, запрос имеет старший приоритетный номер;

Режим обработки символа, в котором вьтолняется вызванная микропрограмма обработки символа. В процессе ее выполнения могут инициироваться другие микропрограммы в любых процессорах. Это осуществляется с помощью вьщачи сигналов запросов по цепям (выход) 29, По окончании микропрограммы всегда включается режим анализа запросов в регистре 30 переходов.

Функции обработки символов оператора языка RTF распределены между процессорами следующим образом. Первый процессор осуществляет прием символов из памяти ЭВМ и их предварительный анализ с целью корректировки работы вычислительного устройства в конвейерном режиме в момент перехода от обработки последних символов предыдущего оператора к обработке первого символа следующего оператора. Второй процессор осуществляет анализ характеристик символа и подготовку его к исполнительной процедуре до момента обращения к памяти ЭВМ. Третий процесс реализует все запросы к памяти ЭВМ на чтение операндов и символов операторов и запись результатов в

2

0

5

0

5

0

5

0

5

0

5

режим ожидания слео

память ЭВМ.Четвертый процессор осуществляет прием и обработку операндов из памяти ЭВМ и адресов операндов при косвенной адресации, а также выполняет подготовленные операции.

На фиг. 7 показана блок-схема алгоритма взаимодействия процессоров в пусковом режиме. Третий процессор ини- 1ц ирует чтение из памяти ЭВМ первого символа оператора, а в дальнейшем инициирует чтение текущих символов. Остальные процессора ожидают прихода информатдии.

На фиг. 8-П показаны блок-схемы алгоритмов работы процессоров при обработке символов языка RTF. Если процессор выполняет несколько видов обработки символов, то для каждого вида обработки указан приоритетный номер.

Первый процессор включается в работу, когда первый символ оператора считан из памяти ЭВМ. Затем он иници-. ирует работу второго процессора, а сам переходит в дующего символа.

В свою очередь второй процессор после обработки очередного символа либо инициирует работу третьего процессора, если необходимо обратиться к памяти ЭВМ, либо работу четвертого процессора, если операция полностью подготовлена и может быть выполнена, либо не инициирует работу процессоров, если обработка символа полностью завершена микропрограммой второго процессора.

Третий процессор не инициирует работу других процессоров, так как обработка текущего символа, требующего обращения к памяти ЭВМ, прерывается на время чтения из памяти ЭВМ,

Четвертый процессор возобновляет обработку символа после прихода слова из памяти ЭВМ,либо выполняет заданную операцию, если для нее подготовлены все исходные данные.

Таким образом, при постоянном поступлении символов оператора из памяти ЭВМ процессоры осуществляют их обработку в конвейерном режиме, пользуясь для срочных передач информации регистрами 2 с соответствующими цепями управления, а для передач информации, требующих временной буферизации, используется блок 5 буферной памяти. Четвертый процессор всегда работает с информацией, требующей временной буферизации, поэтому он не

использует средств конвейерной передачи .

Через блок 5 буферной памяти выполняется также обмен информацией, направление передачи которой не совпадает с направлением конвейерной передачи, например, из четвертого про; цессора в третий (при обращении к па- , мяти ЭВМ) или из четвертого процессор ного блока в первый или второй процессор (при паред.яче условия ветвления вычислительного процесса).

Инициирование вьтолнения микропрограммы в процессорах при передаче информации как в конвейерном режиме, так и через блок 5 буферной памяти осуществляется с помощью внешних управляющих сигналов (цепи (выход) 29) и аппаратуры, реализующей микропро- грамю&ш переходы (йходы 28, регистры 30 и 31, схема 32 сравнения, блок 33 приоритета, шифратор 34 и блок 39 памяти переходов).

Вышеописанный пример обработки в -предлагаемом вычислительном устройстве символов операторов языка RTF показывает, что введение возможности- произвольного обмена информацией между процессора через блок 5 буфер- ной памяти и тем самым асинхронного взаимодействия между ними, позволяет увеличить быстродействие предпагаемо- го вычислительного устройства и свести к минимуму непроизводительную ра- боту отдельных процессоров за счет того, что в те временные интервалы, когда какие-либо процессоры не заняты срочной обработкой информации в конвейерном режиме, они вьшолняют менее срочные вычиелительные процедуры в соответствии с приоритетными номерами, присвоенными им при конкретном применении вычислительного устройства.

На фиг. 12 показан пример временной диаграммы вьтолнения ряда вычислительных процедур в вычислительном устройстве при . Здесь процедуры С1 и С4 требуют обработки информации во всех процессорах, С2 - в первом и втором процессорах, СЗ - в первом процессоре, XI - во втором и третьем процессорах, У1 - в третьем и четвертом процессорах. При жесткой конвейер ной обработке информации все процедуры должны были бы выполняться строго последовательно. При этом интервалы времени, в которые процессоры не

о

S 0

5 о . о 5

л

5

заняты обработкой информации, существенно возрастают.

Формула изобретения

Вычислительное устройство, содержащее п процессоров (п 1, где п - максимальное количество совмещенных операций), п регистров, п триггеров, п дешифраторов, причем информацион- ньй вход i-ro регистра (, п-1) соединен с первым информационным выходом 1-го процессора, а информацион- ньй выход i-ro регистра соединен с информационным входом (i+l)-ro процессора, первый выход i-ro дешифратора соединен с J-входом i-ro триггера и с входом управления записью i-ro регистра, выход i-ro дешифратора соединен с первым входом блокировки i-ro процессора, третий выход i-ro дешифратора соединен с первым К-вхо- дом i-ro триггера, четвертый выход i-ro дешифратора соединен с вторым К-входом i-ro триггера и с вторым входом блокировки процессора, первый вход i-ro дешифратора соединен с выходом признак а передачи данных i-ro процессора, второй вход i-ro дешифратора соединен с выходом признака приема данных (i+l)-ro процессора, третий вход i-ro дешифратора соединен с выходом i-ro триггера, информационный вход-выход, информационный и управляющий выходы вычислительного устройства соединены соответственно с информационными входами-выходами, с вторыми и третьими информационными выходами процессоров, входы синхронизации и входы начальной установки вычислительного устройства соединены соответственно с входами синхронизации и начальной установ ки процессоров, о т- личающееся тем,что, с целью повьшзения быстродействия, в него введены блок буферной памяти и блок приоритета, причем информационный вход-выход блока буферной памяти подключен к информационным входам-выходам процессоров и вычислительного устройства, адресные входы блока буферной памяти подключены к адресным к 1ходам процессоров, входы управления третьим состоянием, входы управления выборкой и вход управления записью блока буферной памяти соединены с оответст- вyющи и разрядами управляющего выхода вычислительного устройства, j-й (,

I 514

n) вход блока приоритета соединен с выходом запроса обращения к блоку буферной памяти J-ro процессора, J-й выход блока приоритета соединен с третьим входом блокировки j-ro процессора, выход инициализации операций i-ro процессора соединен с входом инициализации операций (i+l)-ro про

цессора, выход инициализации операций JQ цессора, третий вход элемента 21 1-ЗИЛИ

п-го процессора и выход п-го регистра соединены соответственно с вторым и , третьим информационными выходами вычислительного устройства, вход признаков и первый информационный вход |5 первого процессора соединены соответственно с первым и вторым информационными входами вычислительного устройства, причем i-й процессор содержит регистр переходов, регистр маски, 20 блок приоритета, схему сравнения, шифратор, операционный блок, блок памяти микрокоманд, регистр микрокоманд, адресный регистр блока памяти микро.команд, блок памяти переходов, адрес-25 ный регистр блока памяти перехрдов,

.элемент 2И-ЗИЛИ, блок памяти констант, мультиплексор исходных данных, первый и второй мультиплексоры перестановки байтов, распределитель импульсов, JQ мультиплексор начальной установки, элемент ИЛИ, с первого по третий буферные регистры с трехстабильньми выходами, причем первый информационный вход операционного блока соединен с информационным входом первого буферно- го регистра с трехстабильными выходами и с выходом мультиплексора исходных данных, информационный выход операционного блока соединен с первым .« информационным выходом i-ro процессора и с информационными входами первого и второго мультиплексоров перестановки байтов, адресные входы и входы

35

выборки блока памяти констант, второй- соединен с выходом поля адреса следуинформационный вход операционного блока, вход выборки блока памяти переходов, вход выборки блока памяти переходов, вход разрешения работы адресного регистра блока памяти переходов.

50

кртей микрокоманды регистра микрокоманд, выход адресного регистра блок памяти переходов соединен с выходом шифратора и с адресным входом блока памяти переходов, выход адресного регистра блока памяти микрокоманд соединен с выходом блока памяти переходов и с первым информационным входом мультиплексора начальной установки выход мультигшексора начальной установки соединен с адресным входом блока памяти микрокоманд, выход элемента ИЛИ соединен с управляющим входом выборки блока памяти ми1фокоманд и вхоуправляющие входы мультиплексора исходных данных и двух мультиплексоров перестановки байтов, вход кода операции операционного блока и распределителя импульсов объединены и соединены с выходом поля управления внутренними блоками i-ro процессора регистра микрокоманд, выходы схемы сравнения соединены с входами блока при ь

оритета 1-го процессора, выходы блока приоритета i-ro процессора соединены с информационными входами шифратора и с входами установки в О соответствующих разрядов регистра переходов, первый и второй входы элемента 2И- ЗИЛИ соединены соответственно с первым и вторым входами блокировки i-ro про50

5

Q «

5

соединен с входами управления третьим состоянием второго и третьего буферных регистров с трехстабильными выходами и с третьим входом блокировки i-ro процессора, четвертый вход элемента 2И-ЗИЛИ соединен с запросом на обращение к блоку буферной памяти i-ro процессора и с выходом поля запроса на обращение к блоку буферной памяти регистра микрокоманд, выход элемента соединен с перэым входом элемента ИЛИ, выход первого мультиплексора перестановки байтов соединен с выходом блока памяти констант, с выходом первого буферного регистра с трехстабильным выходном, с первым информационным входом мульти- ппексора исходных данных и с первым информационным входом адресного регистра блока дамяти переходов, выход второго мультиплексора перестановки байтов соединен с информационным входом-выходом i-ro процессорного блока, с вторым информационным входом мультиплексора исходных данных и вторым информационным входом адресного регистра блока памяти переходов, третий информационньй вход мультиплексора исходных данных соединен с информа- ционнь|н входом 1-го процессора, выход блока памяти микрокоманд соединен с информационным входом регистра микрокоманд, информационный вход адресного регистра блока-памяти ьмкрокоманд

0

5

кртей микрокоманды регистра микрокоманд, выход адресного регистра блок памяти переходов соединен с выходом шифратора и с адресным входом блока памяти переходов, выход адресного регистра блока памяти микрокоманд соединен с выходом блока памяти переходов и с первым информационным входом мультиплексора начальной установки выход мультигшексора начальной установки соединен с адресным входом блока памяти микрокоманд, выход элемента ИЛИ соединен с управляющим входом выборки блока памяти ми1фокоманд и входом блокировки распределителя импульсов, выход регистра переходов соединен с первым информационным входом схемы сравнения, выход регистра мае- ки соединен с вторым информационным входом схемы сравнения, информационный вход регистра маски соединен с выходом поля маски регистра микрокоманд, входы установки в 1 регистра переходов соединены с входами инициализации операции i-го процессора, выходы полей признака передачи и признака приема данных регистра микрокоманд соединены соответственно с одноименными выходами i-ro процессора, выходы поля адреса внешней памяти и поля управления внешней памяти регистра микрокоманд соединены соответственно с информационными входами вто- рого и третьего буферных регистров с трехстабильными выходами, выходы ко торых соединены соответственно с вторым и третьим информационными выходами 1-го процессора, выходы поля внет-них управляющих сигналов регистра микрокоманд соединены с выходами инициализации операций i-ro процессора, второй информационньй вход и управляющий вход мультиплексора начальной установки, второй вход элемента ИЛИ, лервые синхровхода блока памяти микрокоманд и регистра микрокоманд и второй информационньй вход регистра

переходов соединены с входами начальной установки i-ro процессора, синхро входы i-ro процессора соединены с синхровходами распределителя импульсов, с первого по восемнадцатый выходы которого соединены соответственно с вторым синхровходом регистра микрокоманд, синхровходом адресного регистра блока памяти микрокоманд, с первым синнровходом регистра переходов, с синхровходом регистра маски, с входами управления третьим состоянием адресного регистра блока памяти переходов и шифратора, с синхровходом блока памяти переходов, с входом управления третьим состоянием адресного регистра блока памяти микрокоманд, с вторым синхровходом бдока памяти микрокоманд, с синхровходом блока памяти констант, с входом управления третьим состоянием первого буферного регистра с трехстабильными выходами, с синхровходами адресного регистра блока памяти переходов и операционного блока, с входами управления третьим состоянием первого и второго мультиплексоров перестановки байтов, с синхровходом первого буферного регистра и синхровходами второго и третьего буферных регистров с трехстабильными выходами и с вторым синхровходом регистра переходовj

Фиг2

Фиг. 5

Запросы от Пц51- и.54 и днешиих дстроистб

I

Устаиодка на /альиого cocmoffHt/ff ПцВ

НКПР опроса PsHxiRGSO)

ЗаписьJ 6 j-u разрйд РвПк(К&30}при neoSwduHocm 5ызо6а -й МКПР(и.епь16).

5Чй j

ill

-I s

ч

х

Сз

I

I

I

Цтеиие наяа/ ьного адреса МКПР П31/Лх (DSC 39) по коду на дытде блока 34. Гашение j-BQ разряда РвП)({Р&30)

Выполнение J-u МКПР 6 Пц5. Запись „ГЬ разряды РзПх Пи61-Пцб4. (R&30H-R&30M при необходимости бызоба ноннретнш МКПР (menu 28),

Конец МКПР

Фив. 6

Луск

Нет запроса

Есть запрос

Конец МКПР

Нацальноя устанодка Пи,б1-Пц5Шепа 16/1-16/4).

г

Запись J 6 IP Рг Пк 3 (R&30I3. цепь 16/3).

Режим ожидания

и6раш.еиие к памяти ЭВМ за

cunSo/JOM программы .

- (чтение исходных данных, из

бВи5(цеш ,26j2.21l3) -формирование (pusin ecKoeo

адреса({екапамяти ЭВМ-, текуи4его

адрессс, -opzoHU3at4Uff запроса на

чтение из noMffmu 9ВМ

(цепи 23-25, быходы 7-9) Запись Гб 6р РгПкЗ.

Конец, МКПР

Фиг.7

Писн

«

Режим

Конец, МКПР

Прием си идола из памяти ЭВМ (и.епь 23. бход 7).

1

Да

Проберка нонао предыдущего оператора-, -чтение из б5П5признака конца оператора (u.enu23 25 26li, 27/1} . -проверка Hajfut/uff призиа(а конца

оператора

Нет

Есть

Передача симбола 6 R&211 {цепи 22Ц, 20/i, элементы 311,4Н1

I

Запрос к Пи Б 2 на МКПРофа откисимоо- /la: записьJ б1рРгПх2 (цепь 29/f).

Фиг.в

Hem запроса

Всть запрос МКПР

приема симболдиз naMffmtj ЗВтиепь 2e/fj

Нет

Да

Есть

Konei mnP

§

Чтение симдолр из R&2H (цепи НИ, 2111,19Н, в еменгт ы J/f, 4/f).

Ij-immгли1 ш H -гтг -jij i- ,i/ i -r- - JUMIL

шетбление МКПР no характеристике симбола

I

S

I

коп

ycmam6f a б исходноеро- оццу ячеек 5Пй, за поминание коп офиксирооаШ ячейке

(цепи 23-25. 2бШМ

Операнд

Постановка б очередь.. опердндооо

и,епи 23-25 26/2.27/2).

Hem запроса

Есть запрос МКПР обработки символа, 1приоритет(и,спь 28/2)

актеристике симбола

Операция

Постановка б очередь операций о 65iJ5 (цепи 23-2 5, 26/2,27/21

Идентити- каторадре са операнда

I

Формиробаиае фaзul ecкoгo адреса па- мятиЭВМ6ББП5 (цепи 23-25, 26/2,27/2.

Формирование

признака готоо ностиопераиии оФиксироооииои шке Ш5 -пи 23-25. 26/2.

Переда а физи- ijecKOBO адреса §RB2l2{u,enu 22fZ,2mj8l2, элеНенты,412.,

Запрос кПи,ВЗ на МКПР (Чтения из памяти ЭВМ операнда (цепь 29/2).

Коней, МКПР

Фиг.9

ФигМ

Есть запрос МКПР приема ело 6а, 1 приоритет (цепь 28/4)

прием с/1о5а из помрти д§М(иепд23,дхо97)

г.

:з

I

Передало фцзи веского адреса ffi/euKu памяти

да/7/4;; гашение признака .

L

Запрос кПцбЗнаМКПр чтения операнда из памйтиЗВМ . (иепь29/4

Код операци

Исполнение опера- u,Uu.., запись ре- зультвп га о дусрер резцмтатоо 55п5, Шепи 23-25,26/.27/4).

I

Коне inepam

I

Постаноока о ot epedd операндоо 666fi5 (цепи 23-25,26/4,27/1.).

Конец МКПР

Нет запроса

Есть запрос МКПР исполнение onepatwu. 2 прцоратет(цел1)28)

Чтение операндоб и кода операции из Б6П5(14епи ,26/4, Z 7/4

Ветдление МКПР по коду операции I

Код операции „Х

Код onepaauuj

Исполнение опера- и,и.и„У уЗапись рез1 льтап а о оу(рер pest/Mirtafl Г

moo 65/15

( 2S-25,26M7M

I

Коней X inepamopa

Да

Запрос нПцБЗна МКПР записи резильтата о naMffmb ЭВМ (цепьгзМ.

0U2.ff

nu6i

а

CZ

сз

Пцб2

ст

С2

XI

Коней oupaoofnKuCZ

С1

Пцб4

Г/

Фиг.12

С4

Ki

К2

Конец обра- ботки СЗ

и

7ГГ

К2

У1

XI

Ж

Ж

Коней oSpa mKuXI

У1

С4

Коней oSpgffojnKuCI

Конец

| Патент СШЛ № 4112489, кп | |||

| , опублик | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Патент США 4305124, кп | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1988-10-15—Публикация

1987-01-26—Подача