возможностей и повьшшние надежности - достигается путем регулирования уровней формируемых импульсов, блокировки выхода по внешнему сигналу и перевода выхода устройства в высокоим- педансное состояние при коротком замыкании выходной шины. Для этого в устро.йстБО дополнительно введены согласующий усилитель I, два дополнительных двухтактных усилителя 2 и 25, четыре инвертора 19, 20, 22 и 23 предварительный усилитель 24 низкого уровня, элемент 2 И-ИПИ-НЕ 21 , эле1

Изобретение относится к импульсной технике и может быть использовано в приборах измерительной и вычислительной техники в качестве за- датчика режимных воздействий,

; Цель изобретения - расширение функциональных возможностей и повышение надежности за счет обеспечения возможности регулирования уровней формируемых импульсов, блокировки выхода по внешнему сигналу и перевода выхода устройства в высокоимпе- дансное сосТбяние при коротком замыкании выходной шины. Цель достигается путем введения в устройство со- гласуюшего усилителя, двух дополнительных двухтактных усилителей, предварительного усилителя низкого уровняi четырех инверторов, элемента 2 И-ИЛИ /НЕ, элемента задержки, трех двухтранзисторных цепочек, коммутирующего и пяти блокирующих транзисторов.

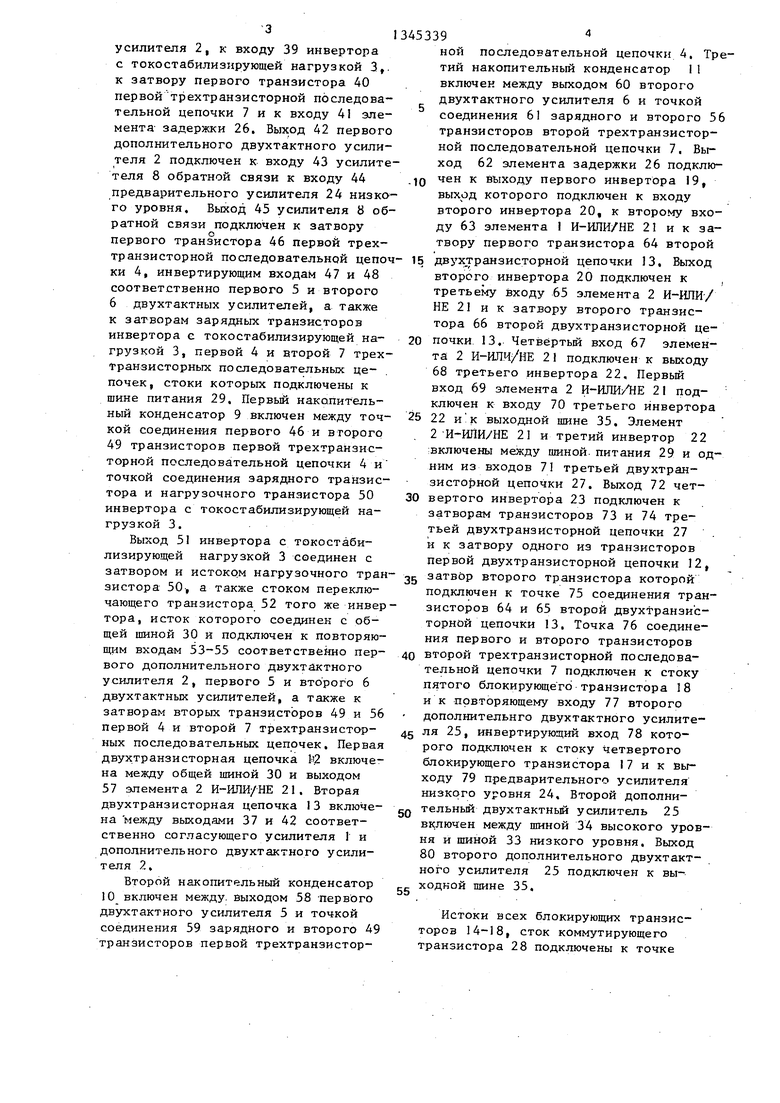

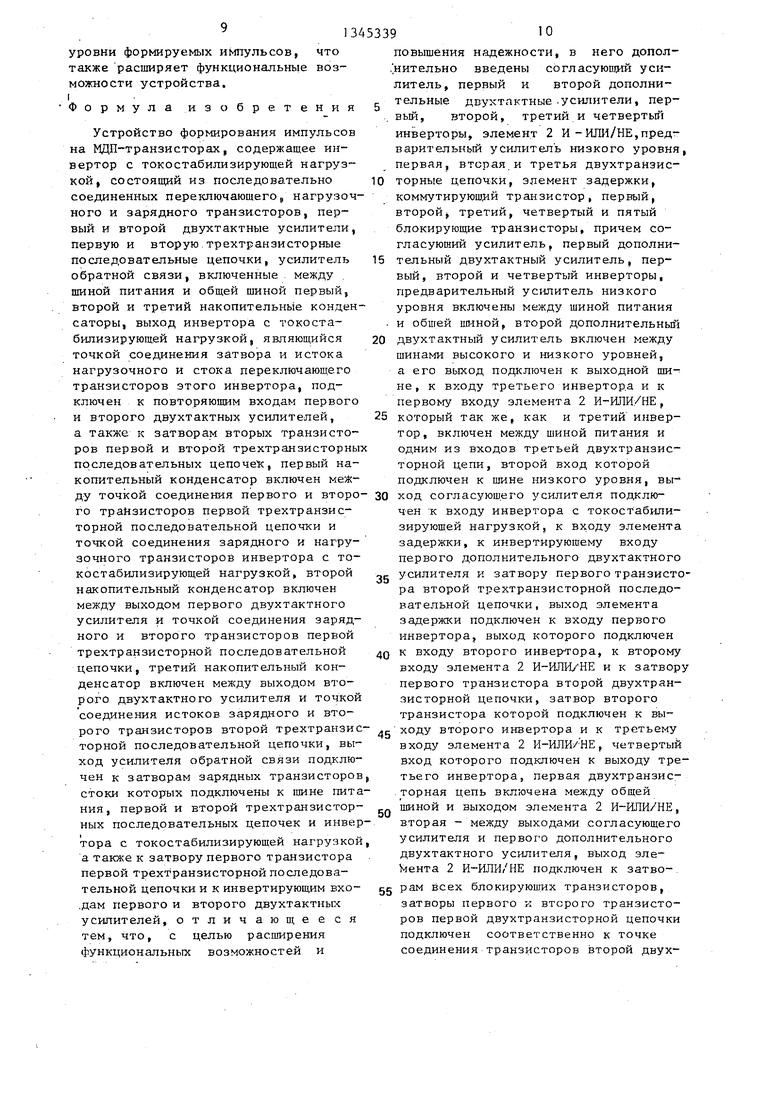

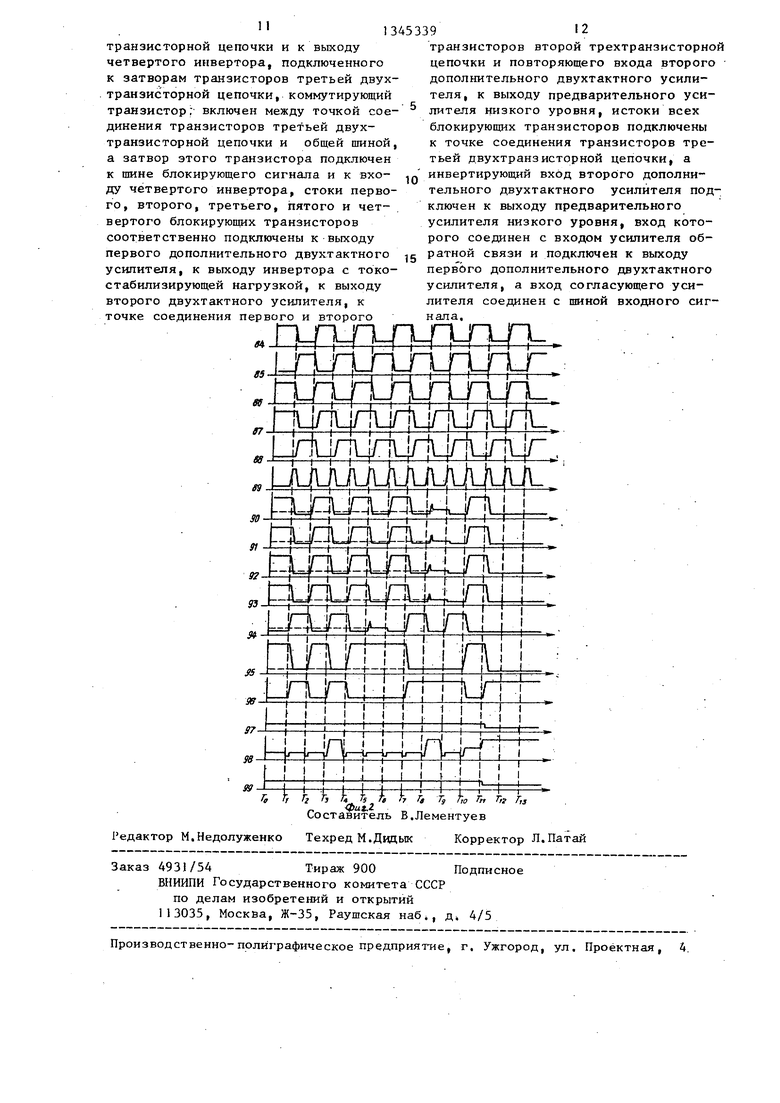

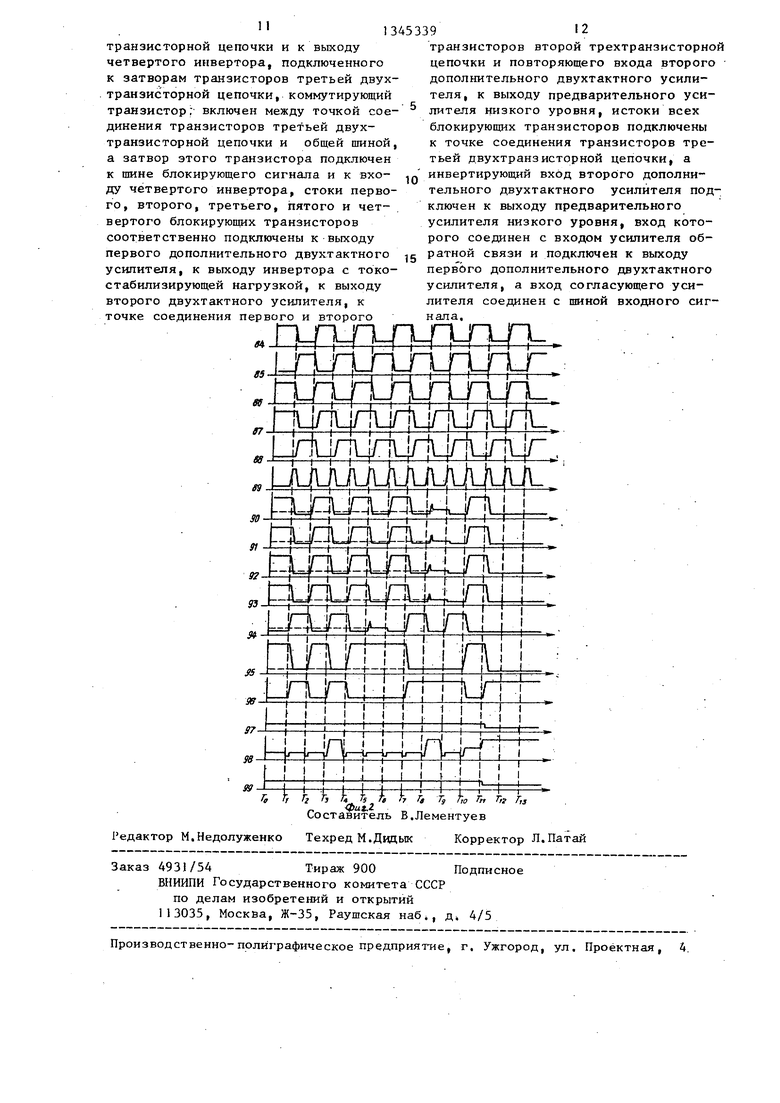

На фиг.1 приведена принципиальная схема устройства; на фиг.2 - временные диаграммы работы устройства в различных режимах, соответствующих различным моментам времени,

Устройство содержит согласующий усилитель 1, первый дополнительный двухтактный усилитель 2, инвертор с токостабилизирующей нагрузкой 3, первую трехтранзисторную последовательную цепочку 4, первьй 5 и второй 6 двухтактные усилители, вторую трехтранзисторную последовательную цепочмент 26 задержки, три грехуронневых транзисторных цепочки 4, 7 и 27, ком- мутируюагий транзистор 28 и пять блокирующих транзисторов 14, 15, 16, 17 и 18. В устройстве обеспечивается блокировка выходного сигнала при коротком замыкании выходной шины 35 на высокий или низкий уровень напряжения. Это позволяет использовать устройство в случаях, при которых возможны короткие замыкания выходной шины, что расширяет обл асть его применения. 2 ил.

ку 7, усилитель 8 обратной связи, первый 9, второй 10, третий 11 накопительные конденсаторы, первую 12 и вторую 13 двухтранзисторные цепочки, первый 14, второй 15, третий 16, четвертый 17,.пятьй 18 блокирующие транзисторы, первьй 19 и второй 20 инверторы, элемент 2 И-ИЛИ/НЕ 21,

третий 22 и четвертьй 23 инверторы, предварительньй усилитель 24 низкого уровня, второй дополнительный двухтактный, усилитель 25, элемент задержки 26, третью двухтранзисторную цепочку 27, коммутирующий транзистор 28, шину 29 питания, общую шину 30, шину 31 входного сигнала, шину 32 блокирующего сигнала, шину 33 низкого уровня, шину 34 высокого уровня, выходную тту 35.

Согласуюш,ий усилитель 1 , первьй дополнительньй двухтактный усилитель 2, инвертор с токостабилизируюшей нагрузкой 3, первая трехтранзисторная последовательная цепочка 4, первьй 5 и второй 6 двухтактные усилители, вторая трехтранзисторная последовательная цепочка 7, усилитель обратной связи 8, первьй инвертор 19,

второй, инвертор 20, третий инвертор 22 и предварительный усилитель низкого уровня 24 включены между шиной питания 29 и общей шиной 30. Вход 36 согласуюш.его - усилителя I подключен к шине 31 входного сигнала, а его выход 37 - к инвертирующему входу 38 дополнительного двухтактного

3

усилителя 2, к входу 39 инвертора

13А5339

ной

последовательной цепочки 4, Третий накопительный конденсатор I 1 включен между выходом 60 второго двухтактного усилителя 6 и точкой соединения 61 зарядного и второго 56 транзисторов второй трехтранзистор- ной последовательной цепочки 7. Выход 62 элемента задержки 26 подклю- .1Q чей к выходу первого инвертора 19, выход которого подключен к входу второго инвертора 20, к второму входу 63 элемента 1 И-ШТИ/НЕ 21 и к затвору первого транзистора 64 второй транзисторной последовательной цепоч- 15 двух -ранзисторной цепочки 13, Выход

с токостабилизирующей нагрузкой 3,. к затвору первого транзистора 40 пер вой тр ехтр анзисторной по следо ва- тельной цепочки 7 и к входу 41 элемента задержки 26. Выход 42 первого дополнительного двухтактного усилителя 2 подключен к входу 43 усилите- теля 8 обратной связи к входу 44 предварительного усилителя 24 низкого уровня. Выход 45 усилителя Б обратной связи подключен к затвору первого транзистора 46 первой трехки 4, инвертирующим входам 47 и 48 соответственно первого 5 и второго 6 двухтактных усилителей, а также к затворам зарядных транзисторов инвертора с токостабилизирующей нагрузкой 3, первой 4 и второй 7 трех транзисторных последовательных цепочек, стоки которых подключены к шине питания 29, Первый накопительный конденсатор 9 включен между точкой соединения первого 46 и второго 49 транзисторов первой трехтранзис- торной последовательной цепочки 4 и точкой соединения зарядного транзистора и нагрузочного транзистора 50 инвертора с токостабилизирующей нагрузкой 3.

Выход 51 инвертора с токостабилизирующей нагрузкой 3 соединен с затвором и истоком нагрузочного транзистора 50-, а также стоком переключающего транзистора 52 того же инвертора, исток которого соединен с общей шиной 30 и подключен к повторяющим входам 53-55 соответственно первого дополнительного двухтактного усилителя 2, первого 5 и второго 6 двухтактных усилителей, а также к затворам вторых транзисторов 49 и 56 первой 4 и второй 7 трехтранзистор- ных последовательных цепочек. Первая двухтранзисторная цепочка Ш включена между общей шиной 30 и выходом 57 элемента 2 И-ИЛИ/НЕ 21, Вторая двухтранзисторная цепочка 13 включена между выходами 37 и 42 соответственно согласующего усилителя 1 и дополнительного двухтактного усилителя 2,

Второй нак опит ель конденсатор 10 включен между, выходом 58 -первого двухтактного усилителя 5 и точкой соединения 59 зарядного и второго 49 транзисторов первой трехтранзистор3А5339

ной

тий вклю двух соед тран ной ход .1Q чей выхо втор ду 6 твор - 15 двух

второго инвертора 20 подключен к , третьему входу 63 элемента 2 И-ШТИ-/ НЕ 21 и к затвору второго транзистора 66 второй двухтранзисторной цепочки 13, Четвёртьй вход 67 элемента 2 И-ИЛЧ/НЕ 2I подключен к выходу 68 третьего инвертора 22, Первьй вход 69 элемента 2 И-ШШ/ИЕ 21 под- ключен к входу 70 третьего инвертора 22 и к выходной шине 35, Элемент 2 И-ИЛИ/НЕ 21 и третий инвертор 22 ;включены между шиной, питания 29 и одним из входов 71 третьей двухтран- зисторной цепочки 27, Выход 72 чет- вертого инвертора 23 подключен к затворам транзисторов 73 и 74 третьей двухтранзисторной цепочки 27 и к затвору одного из транзисторов первой двухтранзисторной цепочки 12, затвОр второго транзистора которой подключен к точке 75 соединения транзисторов 64 и 65 второй двухтранзисторной цепочки 13, Точка 76 соединения первого и второго транзисторов второй трехтранзисторной последовательной цепочки 7 подключен к стоку пятого блокирующего транзистора 18 и к повторяющему входу 77 второго дополнительнго двухтактного усилите- ля 25, инвертирующий вход 78 которого подключен к стоку четвертого блокирующего транзистора 17 и к выходу 79 п.редварительного усилителя низкого уровня 24, Второй дополни- тельньй двухтактньй усилитель 25 включен между шиной 34 высокого уровня и шиной 33 низкого уровня. Выход 80 второго дополнительного двухтактного усилителя 25 подключен к выходной шине 35,

Истоки всех блокирующих транзисторов 14-18, сток коммутирующего транзистора 28 подключены к точке

81 соединения транзисторов 73 и 74 третьей двухтранзисторной цепочки 27 Сток первого блокирующего транзистора 14 подключен к выходу 42 первого дополнительного двухтактного усилителя 2, Сток второго блокирующего транзистора 15 подключен к выходу 51 инвертора с токостабилизирующей нагрузкой 3. Сток третьего блокирующего транзистора 16 подключен к выходу 60 второго двухтактного усилителя 6. Исток коммутирующего транзистора 28 подключен к общей шине 30, Затворы всех блокирующих транзисторов 14-18 подключены к выходу 57 элемента 2-И-РШИ/НЕ 2 Г. Второй вход 82 третьей двухтранзисторной цепочки 27 подключен к шине 33 низкого уровня. Вход 83 четвертого инвертора 23 и затвор блокирующего

транзистора 28 подключены к щине блокирующего сигнала 32, .

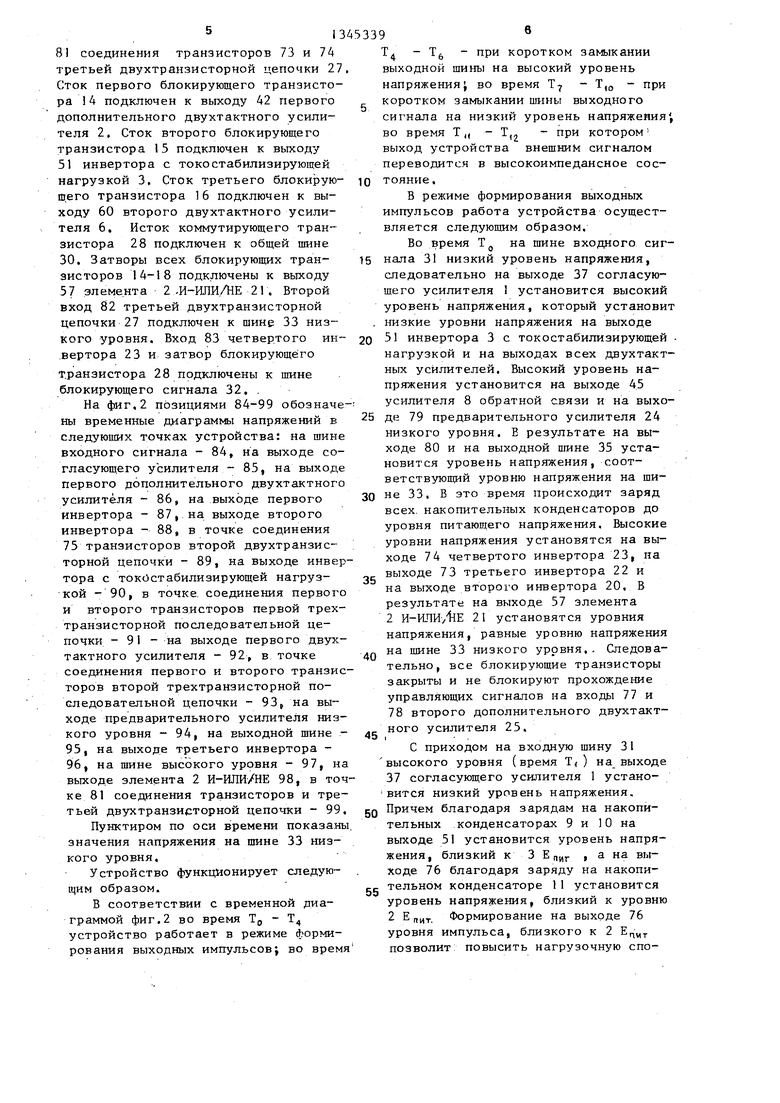

На фиг,2 позициями 84-99 обозначены временные диаграммы напряжений в следующих точках устройства: на шине входного сигнала - 84, на выходе согласующего усилителя - 85, на выходе первого дополнительного двухтактного усилителя - 86, на выходе первого инвертора - 87, на выходе второго инвертора - 88, в точке соединения 75 транзисторов второй двухтранзис- торной цепочки -89, на выходе инвертора с токОстабилизирующей нагрузкой - 90, в точке, соединения первого и второго транзисторов первой трех- транзисторной последовательной цепочки - 91 - на выходе первого двузс- тактного усилителя - 92, в точке соединения первого и второго транзисторов второй трехтранзисторной последовательной цепочки - 93, на выходе предварительного усилителя низкого уровня - 94, на выходной шине 95,на выходе третьего инвертора 96,на шине высокого уровня - 97, на выходе элемента 2 И-ИЛИ/НЕ 98, в точке 81 соединения транзисторов и третьей двухтранзисторной цепочки - 99,

Пунктиром по оси времени показа:ны значения напряжения на шине 33 низкого уровня.

Устройство функционирует следующим образом.

В соответствии с временной диаграммой фиг,2 во время TQ - Т устройство работает в режиме формирования выходных импульсов; во время

- Т,

при коротком замыкании

5

0

5

0

5

0

5

0

выходной щины на высокий уровень напряженияJ во время Т - T,o - при коротком замыкании шины выходного сигнала на низкий уровень напряжения , во время Т (, - Т,2 - при котором выход устройства внешним сигналом переводится в высокоимпедансное состояние,

В режиме формирования выходных импульсов работа устройства осуществляется следующим образом.

Во время Тд на шине входного сигнала 31 низкий уровень напряжения, следовательно на выходе 37 согласующего усилителя I установится высокий уровень напряжения, который установит низкие уровни напряжения на выходе 51 инвертора 3 с токостабилизирующей нагрузкой и на выходах всех двухтактных усилителей. Высокий уровень напряжения установится на выходе 45 усилителя 8 обратной связи и на выходе 79 предварительного усилителя 24 низкого уровня. Е результате на выходе 80 и на выходной шине 35 установится уровень напряжения, соответствующий уровню напряжения на шине 33, В это время происходит заряд всех, накопительных конденсаторов до уровня питающего напряжения. Высокие уровни напряжения установятся на выходе 74 четвертого инвертора 23, па выходе 73 третьего инвертора 22 и на выходе в торс I o инвертора 20, В результате на выходе 57 элемента 2 И-ИЛИ/llE 21 установятся уровния напряжения, равные уровню напряжения на щине 33 низкого уровня,. Следовательно, все блокирующие транзисторы закрыты и не блокируют прохождение управляющих сигналов на входь 77 и 78 второго дополнительного двухтактного усилителя 25, I С приходом на входную шину 31

высокого уровня (время Т() на выходе 37 согласующего усилителя 1 установится низкий уровень напряжения. Причем благодаря зарядам на накопительных конденсаторах 9 и 10 на выходе 51 установится уровень напря55

ПИГ

а на выжения, близкий к 3 Е ходе 76 благодаря заряду на накопительном конденсаторе 11 установится уровень напряжения, близкий к уровню

2 Е,

Формирование на выходе 76

уровня импульса, близкого к 2 Ещ, позволит: повысить нагрузочную способность устройства. Высокий уровень напряжения с выхода 42 передается на точку соединения транзисторов 75 второй двухтранзисторной цепочки 13. В первой двухтранзисторной цепочке 12 оба транзистора открыты, что исключает на выходе 57 элемента 2 И-Ш1И/НЕ 21 формирование высокого

уровня. Когда на выходе первого инверто-ю переключится в высокоимпедансное сос- ра 19 устанавливается высокий уровень напряжения, а на выходе второго инвертора 20 - низкий, в точке соединения транзисторов 75 второй двухтранзисторной цепочки 13 установится низкий уровень напряжения и блокировка выхода 57 на общую шину снимается.

15

тояние, исключив протекание тока короткого замыкания через повторяющий транзистор второго дополнительного двухтактного усилителя 25.

Во время Т„ - Т, на шину 32 поступает высокий уровень напряжения, На. выходе- 72 четвертого инвертора 23 установится низкий уровень напряжения, что исключит протекание тока через первую двухтранзисторную цепочку 12 и на выходе 57 установится высокий уровень напряжения, а истоки всех блокирующих транзисторов ,чёре.з . ключевой транзистор 28 подключатся 25 к общей шине. Высоким .уровнем напряжения на выходе 57 через блокирующие транзисторы выходы 42, 51, 60, 76 и 79 подключатся к общей шине 30. Выход 80 переключится в высокоимпедансное состояние. Переключение истоков блокирующих транзисторов в режиме высокоимпедансного состояния выхода устройства необходимо для-случая, когда уровень напряжения на выходной шине 35 более отрицательный, чем на шине 33 низкого уровня и разность напряжений превысит пороговое напря- . жение МДП-транзисторов второго дополнительного двухтактного усилителя 25, чтобы исключить протекание тока с щины 35 на шины высокого 34 и низкого 33 уровней.

Во время Tj - Т 5 на шину входного сигнала 31 поступает высокий уровень напряжения, и устройство устанавливается в исходное состояние. Во время переходного процесса в точке соединения транзисторов 75 второй . двухтранзисторной цепочки 13 формируется импульс, по длительности равный задержке на элементе задержки, который блокирует точку 57 на общую шину.

В дальнейшем работа устройства в этом режиме повторяется.

Во время

ТА Tg шина выходного

сигнала 35 закорочена на высокий уровень напряжения.

Во время Т происходит смена уровня входного сигнала с высокого на низкий. Во время смены в точке 75 сформируется импульс, которьм блокирует выход 57 элемента 2 И-ИЛИ/НЕ на обшую шину. После окончания им- пульса в точке 75 на выходе 5.7 эле- мелта 2 И-ИЛИ/НЕ сформируется высокий уровень напряжения, все блокирующие транзисторы откроются и на выходах 42, 51, 60, 76 и 79 установятся уровня напряжения, равные уровню напряжения на шине низкого уровня 33, Оба транзистора второго дополнительного двухтактного усилителя 25 закроются, т.е. выход устройства перейдет в высокоимпедансное состояние, что исключит прохождение тока короткого замыкания через ключевой транзистор второго дополнительного усилителя 25

Во время TT - TO шина вькодного сигнала закорочена на низкий уровень напряжения. Во время смены входного сигнала на шине входного сигнала 31 с низкого на высокий в точке 75 формируется короткий импульс, по длительности равный времени задержки элемента задержки 26, В этом время выход 57 элемента 2 И-ИЛИ/НЕ 2I закорочен на общую шину. После окончания импульса на этом выходе сформируется высокий уровень, благодаря чему за- блокируются выходы 42, 51, 60, 76 и 79 на шину 33 и выходная шина 35

ю переключится в высокоимпедансное сос-

15

тояние, исключив протекание тока короткого замыкания через повторяющий транзистор второго дополнительного двухтактного усилителя 25.

Во время Т„ - Т, на шину 32 по0

0

5

ступает высокий уровень напряжения, На. выходе- 72 четвертого инвертора 23 установится низкий уровень напряжения, что исключит протекание тока через первую двухтранзисторную цепочку 12 и на выходе 57 установится высокий уровень напряжения, а истоки всех блокирующих транзисторов ,чёре.з . ключевой транзистор 28 подключатся 5 к общей шине. Высоким .уровнем напряжения на выходе 57 через блокирующие транзисторы выходы 42, 51, 60, 76 и 79 подключатся к общей шине 30. Выход 80 переключится в высокоимпедансное состояние. Переключение истоков блокирующих транзисторов в режиме высокоимпедансного состояния выхода устройства необходимо для-случая, когда уровень напряжения на выходной шине 35 более отрицательный, чем на шине 33 низкого уровня и разность напряжений превысит пороговое напря- . жение МДП-транзисторов второго дополнительного двухтактного усилителя 25, чтобы исключить протекание тока с щины 35 на шины высокого 34 и низкого 33 уровней.

Таким образом, введение блокиров- .ки выхода устройства при подаче g внешнег-о управляющего сигнала позво- ,ляет в этом режиме на выходную шину 35 подавать сигналы с других устройств.

Наличие блокировки выходного . ,сигнала при коротком замыкании вы- Q ходной шины на высокий или низкий уровень напряжения позволяет использовать устройство в случаях, при которых возможны короткие замьжания выходной.шины, что значительно рас- g ширяет области применения устройства. Подключение двухтактного усилителя 25 к шинам высокого и низкого уровней позволяет с помощью регулировки этих уровней напряжений регулировать

0

уровни формируемых импульсов, что также расширяет функциональные возможности устройства, I Формула изобретения

Устройство формирования импульсов на МДП-транзисторах, содержащее инвертор с токостабилизирующей нагрузкой, состоящий из последовательно соединенных переключающегор нагрузочного и зарядного транзисторов, первый и второй двухтактные усилители, первую и вторую трехтранзисторные последовательные цепочки, усилитель обратной связи, включенные между шиной питания и общей шиной первый, второй и третий накопительные конденсаторы, выход инвертора с токостабилизирующей нагрузкой, являющийся точкой соединения затвора и истока нагрузочного и стока переключающего транзисторов этого инвертора, подключен к повторяющим входам первого и второго двухтактных усилителей, а также к затворам вторых транзисторов первой и второй трехтранэисторны последовательных цепоче с, первый накопительный конденсатор включен между точкой соединения первого и второго транзисторов первой трехтранзис- торной последовательной цепочки и точкой соединения зарядного и нагрузочного транзисторов инвертора с то- костабилизирующей нагрузкой, второй накопительный конденсатор включен между выходом первого двухтактного усилителя и точкой соединения зарядного и второго транзисторов первой трехтранзисторной последовательной цепочки, третий накопительный конденсатор включен между выходом второго двухтактного усилителя и точкой соединения истоков зарядного и второго транзисторов второй трехтранзис торной последовательной цепочки, выход усилителя обратной связи подключен к затворам зарядных транзисторов стоки которых подключены к шине питания, первой и второй трехтранзистор- ных последовательных цепочек и инвертора с токостабилизирующей нагрузкой а также к затвору первого транзистора первой трехтранзисторной последовательной цепочки и к инвертирующим вхо- .дам Первого и второго двухтактных усилителей, отличающееся тем, что, с целью расширения функциональных возможностей и

0

5

0

5

30

повышения надежности, в него допол- нительно введены согласуюпдай усилитель, первый и второй дополнительные двухтактные.усилители, первый, второй, третий и четвертый инверторы, элемент 2 И -ИЛИ/НЕ,предварительный усилитель низкого уровня, первая, вторая и третья двухтранзис- торные цепочки, злемент задержки, коммутирующей транзистор, первый, второйj третий, четвертый и пятый блокируюшр е транзисторь, причем со- гласуюший усилитель, первый дополнительный двухтактный усилитель, первый, второй и четвертый инверторы, предварительный ус1титель низкого уровня включены между шиной питания и обшей шиной, второй дополнительньй двухтактный усилитель включен между шинами высокого и низкого уровней, а его выход подключен к выходной шине, к входу третьего инвертора и к первому входу элемента 2 И-ИЛИ/НЕ, который так же, как и третий инвертор, включен между шиной питания и одним из входов третьей двухтранзис- торной цепи, второй вход которой подключен к шине низкого уровня, выход согласующего усилителя подключен К входу инвертора с токостабили- зируюшей нагрузкой, к входу элемента задержки, к инвертируюшему входу первого дополнительного двухтактного усилителя и затвору первого транзистора второй трехтранзисторной последовательной цепочки, выход элемента задержки подключен к входу первого инвертора, выход которого подключен к входу второго инвер-тора, к второму входу элемента 2 И-ИЛИ/НЕ и к затвору первого транзистора второй двухтран- зисторной цепочки, затвор второго транзистора которой подключен к выходу второго инвертора и к третьему входу элемента 2 И-ИЛИ/-НЕ, четвертый вход которого подключен к выходу третьего инвертора, первая двухтранзис- .торная цепь включена между общей шиной и выходом элемента 2 И-ИЛИ/НЕ, вторая - между выходами согласующего усилителя и первого дополнительного двухтактного усилителя, выход эле- чента 2 И-ИЛИ/НЕ подключен к затво-. 55 рам всех блокирующих транзисторов, затворы первого к второго транзисторов первой двухтранзисторной цепочки подключен соответственно к точке соединения транзисторов второй двух-

35

40

50

транзисторной цепочки и к выходу четвертого инвертора, подключенного к затворам транзисторов третьей двух транзисторной цепочки, коммутирующий транзистор; включен между точкой соединения транзисторов третьей двух- транзисторной цепочки и общей шиной а затвор этого транзистора подключен к шине блокирующего сигнала и к входу четвертого инвертора, стоки первого, второго, третьего, пятого и четвертого блокирующих транзисторов соответственно подключены к выходу первого дополнительного двухтактного усипителя, к выходу инвертора с токо стабилизирующей нагрузкой, к выходу второго двухтактного усилителя, к точке соединения первого и второго

„ ПП.П

0

транзисторов второй трехтранзисторной цепочки и повторяющего входа второго дополнительного двухтактного усилителя, к выходу предварительного усилителя низкого уровня, истоки всех блокирующих транзисторов подключены к точке соединения транзисторов третьей двухтранзисторной цепочки, а инвертируюпщй вход второго дополнительного двухтактного усилителя подключен к выходу предварительного усилителя низкого уровня, вход которого соединен с входом усилителя обратной связи и подключен к выходу первого дополнительного двухтактного усилителя, а вход согласующего усилителя соединен с шиной входного сигнала.

ви

т1ггм1-г№1

S9

иииуишшииииь

г, Гг г, i 4л h г т, k

- -, - 1,0 fn Т,г Г,1 J)ut.2 Составитель В.Лементуев

Редактор М.Недолуженко Техред М.ДвДык

Заказ 4931/54Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д, 4/5

Производственно-полиграфическое предприят-ие, г. Ужгород, ул. Проектная, 4.

Корректор Л.Патай

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный генератор (его варианты) | 1980 |

|

SU911693A1 |

| Квазистатическое счетное устройство на МДП-транзисторах | 1986 |

|

SU1319255A1 |

| Устройство формирования импульсных сигналов и уровней постоянного напряжения на МДП транзисторах | 1986 |

|

SU1370752A1 |

| Устройство формирования импульсов на МДП-транзисторах | 1985 |

|

SU1277380A1 |

| Усилитель-формирователь на металло= диэлектрических полупроводниковых транзисторах | 1974 |

|

SU531284A2 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| Усилитель-формирователь импульсов на мдп транзисторах | 1974 |

|

SU525247A1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| Формирователь импульсов на моп-транзисторах | 1978 |

|

SU790335A1 |

| Формирователь импульсов | 1984 |

|

SU1170599A1 |

Изобретение относится к импульсной технике и может быть использовано в приборах измерительной и вычислительной техники в качестве датчика режимных воздействий. Цель изобретения - расширение функциональных SZ (Л

| Авторское свидетельство СССР я | |||

| Формирователь импульсов | 1984 |

|

SU1170599A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-15—Публикация

1986-04-24—Подача