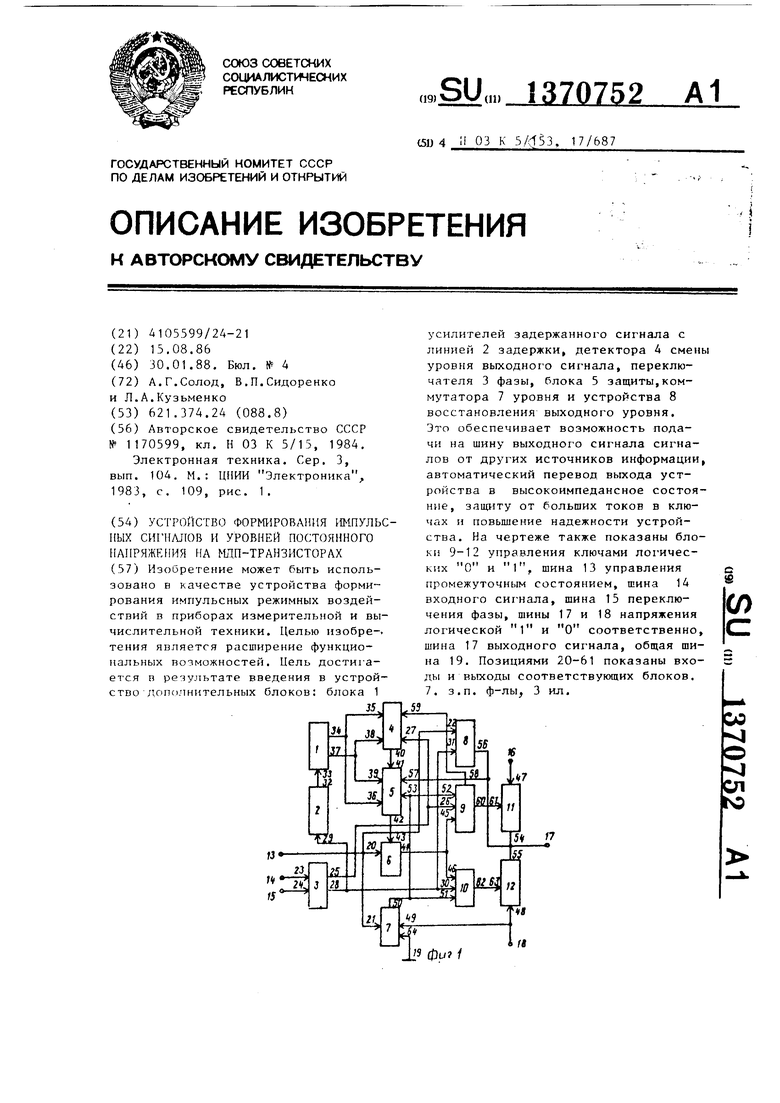

Изобпетекпс относится к импульсной технике и может быть испольэо- гано а качестве устройства формирования импульсных режимных воздействий в приборах измерительной и вычислительной техники.

Целью изобретения является расширение функциональных возможностей устройства за счет введения режима переключения фазы выходного сигнала и повьшение надежности устройства благодаря переводу выхода устройства в промежуточное высокоимпедансное состояние при коротком замыкании шины выходного сигнала на высокий или низкий уровень напряжения. Цель изобретения достигается путем введения в устройство дополнительных блоков - йлока усилителей задержанного сигнала с линией задержки, детектора смены уровня выходного сигнала, переключателя фазы, блока защиты, коммутатора уровня, устройства восстановления выходного уровня. Благодаря введенным блокам обеспечивается возможность подачи на шину выходног сигнала сигналов от других источников информации, уегулироиание уровней и переключение фазы выходных им пульсов, а гакя е обеспечивается автоматический перевод выхода устройства в высокоимпе;; iucHoe состояние при коротком заиыг- ании выходной шипы, т.е. заигнта от f jnbmnx токов в ключах li, следовательно, повышение надежности устройства.

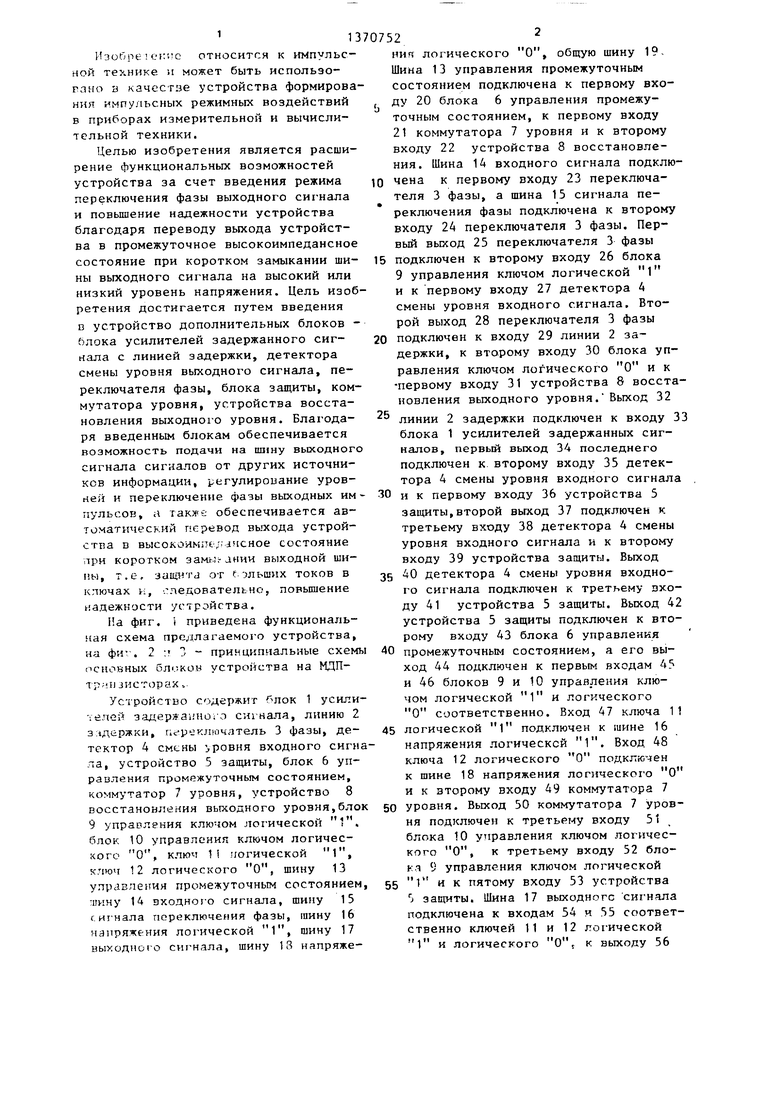

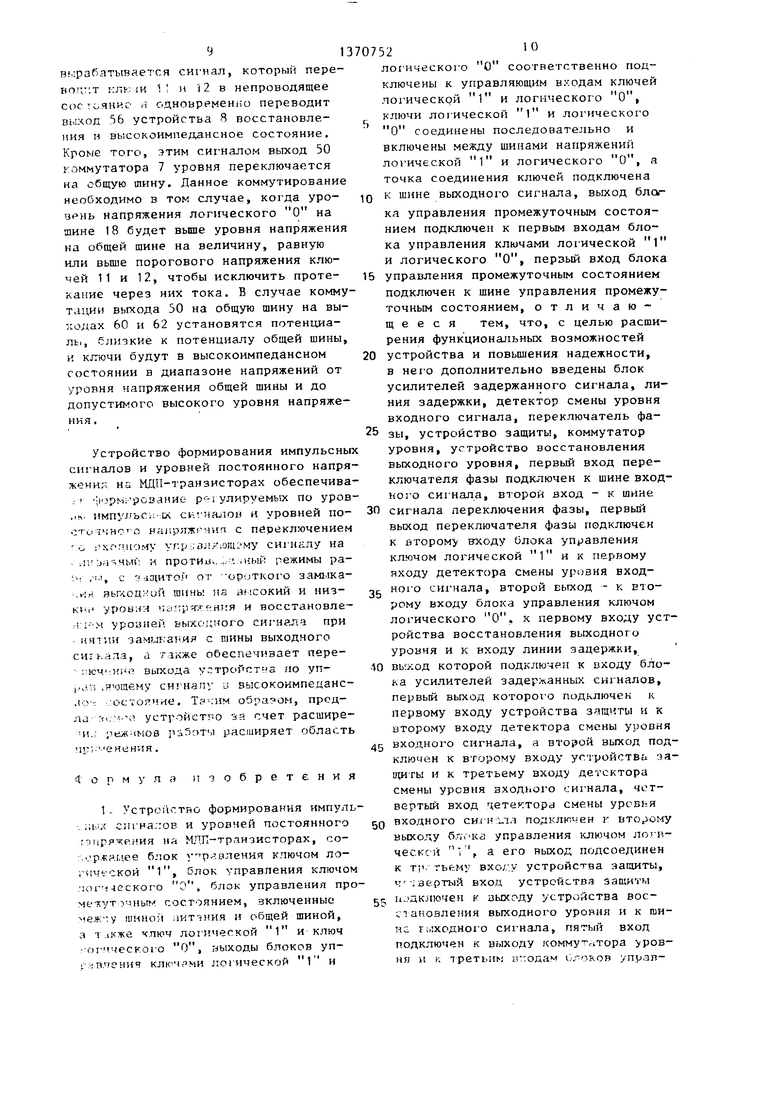

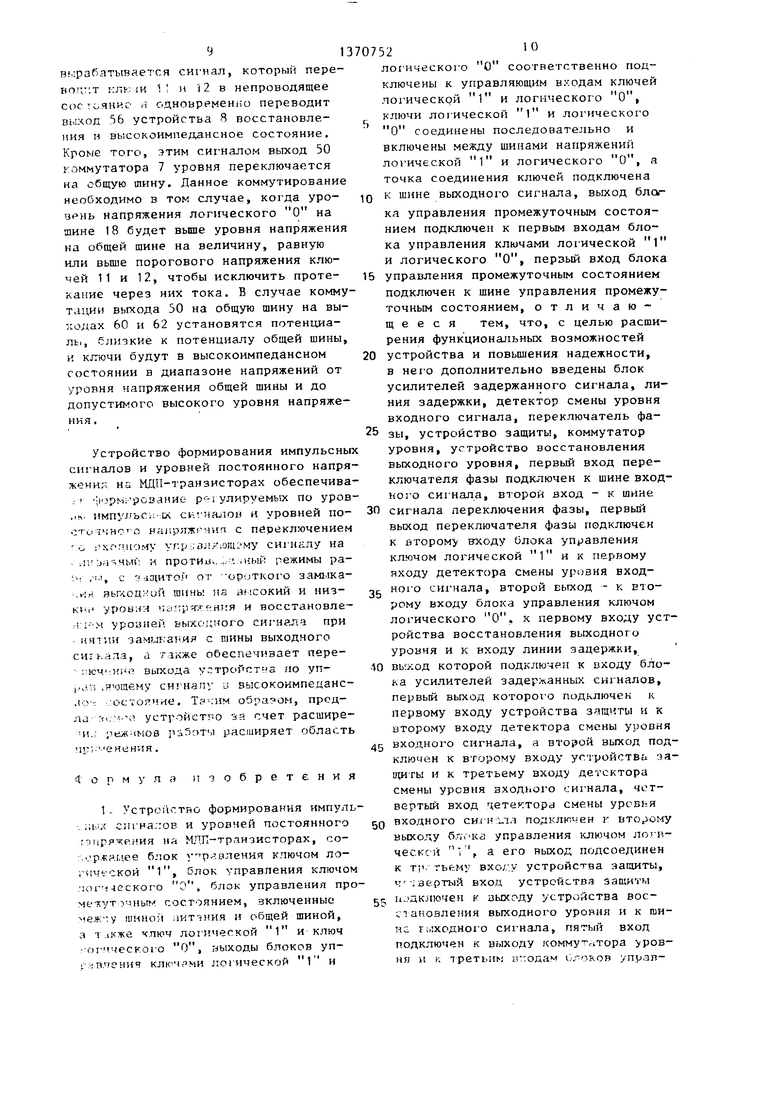

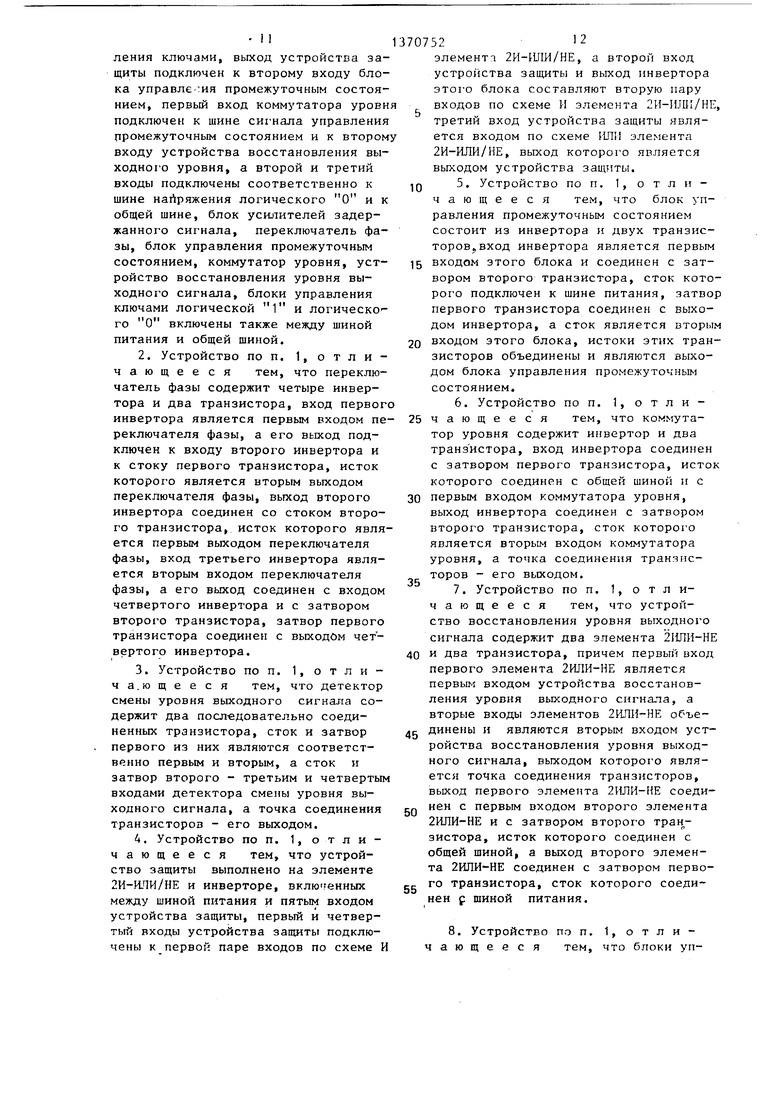

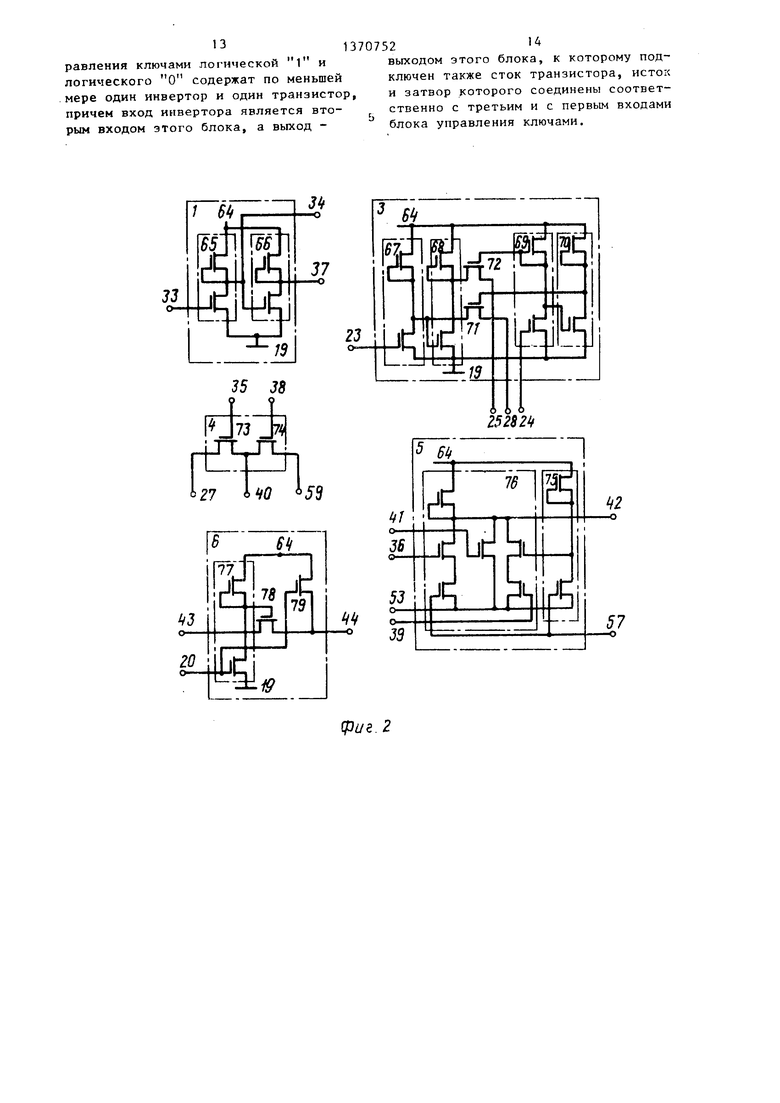

На фиг. ( приведена функциональная схема предлагаемого устройства, на фн . 2 : 3 - принципиальные схем основных бЛ1.;кон устройства на МДП- знсторах«

Устройство содержит блок 1 усилителей задержанного сигнала, линию 2 задержки, Пcp JKJ ючaтeль 3 фазы, детектор 4 смены уровня входного сигнла, устройство 5 защиты, блок 6 управления промежуточным состоянием, коммутатор 7 уровня, устройство 8 восстанонления вькодного уровня,бло 9 управления ключом логической 1, блок 10 управления ключом логического О, ключ 11 логической 1, к.пюч 12 логического О, шину 13 управления промежуточным состоянием лгину 14 входного сигнала, шину 15 гш нала переключения фазы, шину 16 напряжения логической 1, шину 17 выходиосо сигнала, шину 13 напряжения логического О, общую шину 19, Шина 13 управления промежуточньм состоянием подключена к первому вхоу 20 блока 6 управления промежуточным состоянием, к первому входу 21 коммутатора 7 уровня и к второму входу 22 устройства 8 восстановления. Шина 14 входного сигнала подключена к первому входу 23 переключателя 3 фазы, а шина 15 сигнала переключения фазы подключена к второму входу 24 переключателя 3 фазы. Первый выход 25 переключателя 3 фазы

подключен к второму входу 26 блока 9 управления ключом логической 1 и к первому входу 27 детектора 4 смены уровня входного сигнала. Второй выход 28 переключателя 3 фазы

подключен к входу 29 линии 2 задержки, к второму входу 30 блока управления ключом логического О и к первому входу 31 устройства 8 восстановления выходного уровня. Выход 32

линии 2 задержки подключен к входу 33 блока 1 усилителей задержанных сигналов, первый выход 34 последнего подключен к, второму входу 35 детектора 4 смены уровня входного сигнала

и к первому входу 36 устройства 5 защиты,второй выход 37 подключен к третьему входу 38 детектора 4 смены уровня входного сигнала и к второму входу 39 устройства защиты. Выход

40 детектора 4 смены уровня входного сигнала подключен к третьему входу 41 устройства 5 защиты. Выход 42 устройства 5 защиты подключен к второму входу 43 блока 6 управления

промежуточным состоянием, а его выход 44 подключен к первым входам 45 и 46 блоков 9 и 10 управления ключом логической 1 и логического О соответственно. Вход 47 ключа 11

логической 1 подключен к шине 16 напряжения логической 1. Вход 48 ключа 12 логического О подключен к шине 18 напряжения логического О и к второму входу 49 коммутатора 7

уровня. Выход 50 коммутатора 7 уровня подключен к третьему входу 51 блока 10 управления ключом логического О, к третьему входу 52 блока 9 управления ключом логической

1 и к пятому входу 53 устройства 5 защиты. Шина 17 выходного сигнала подключена к входам 54 и 55 соответственно ключей 11 и 12 логической 1 и логического О к выходу 56

31

устройства 8 восстановления и к четвертому входу 57 устройства 5 защиты, Второй выход 58 блока 9 управления ключом логической 1 подключен к четвертому входу 59 детектора А смены уровня входного си нала. Первый выход 60 блока управления ключом логической 1 подключен к управляющему входу 61 ключа 11 логической 1 Выход 62 блока 10 управления ключом логического О подключен к управлящему входу 63 ключа 12 логического О.

Блок 1 усилителей задержанного сигнала, переключатель 3 фазы, блок 6 управления промежуточным состоянием, коммутатор 7 уровня, устройство 8 восстановления выходного уровня, блок 9 управл ния ключом логического О и блок 10 управления ключом логической 1 выполнены на МДП-транзисторах и включены между шиной 64 питания и общей шиной 19

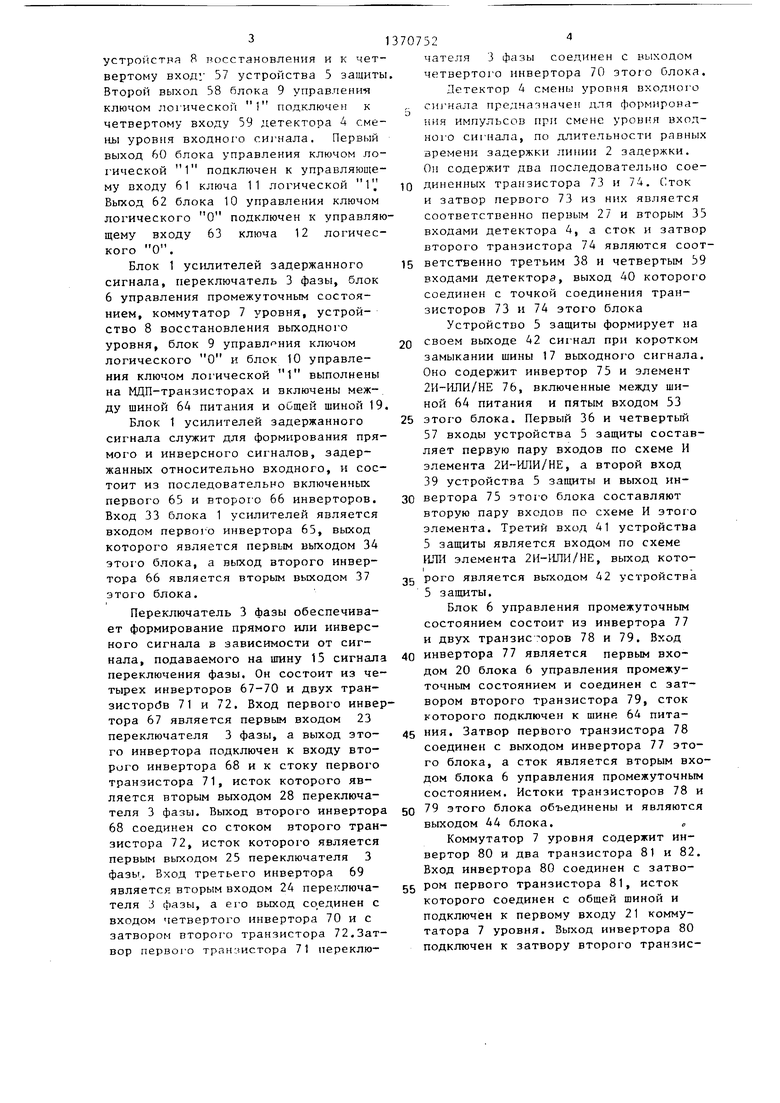

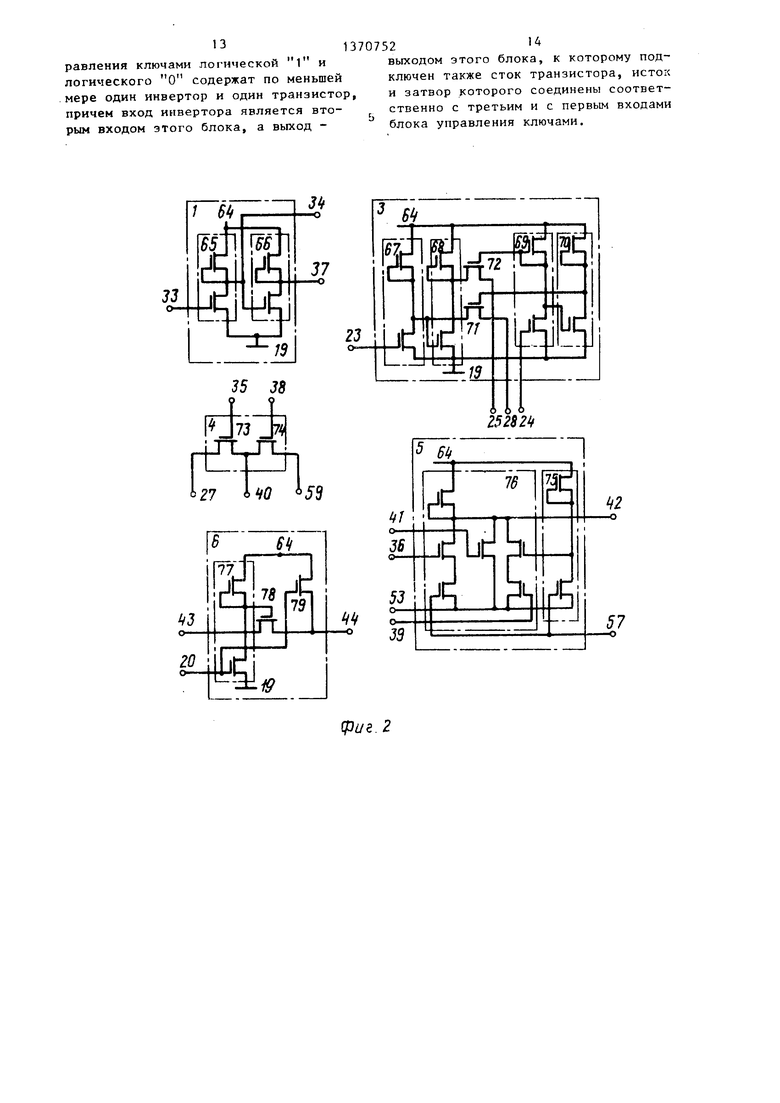

Блок 1 усилителей задержанного сигнала служит для формирования прямого и инверсного сигналов, задержанных относительно входного, и состоит из последовательно включенных первого 65 и BTOpoi o 66 инверторов. Вход 33 блока 1 усилителей является входом первого инвертора 65, выход которого является первым выходом 34 этог о блока, а выход второго инвертора 66 является вторым выходом 37 этого блока.

Переключатель 3 фазы обеспечивает формирование прямого или инверсного сигнала в зависимости от сигнала, подаваемого на шину 15 сигнала переключения фазы. Он состоит из четырех инверторов 67-70 и двух тран- зисторс5в 71 и 72, Вход первого инвертора 67 является первым входом 23 переключателя 3 фазы, а выход этого инвертора подключен к входу второго инвертора 68 и к стоку первого транзистора 71, исток которого является вторым выходом 28 переключателя 3 фазы. Выход второго инвертора 68 соединен со стоком второго транзистора 72, исток которого является первым выходом 25 переключателя 3 фазы. Вход третьего инвертора 69 является вторым входом 24 переключателя 3 фазы, а его вькод соединен с входом четвертого инвертора 70 и с затвором второг-о транзистора 72.Затвор первого транзистора 71 переклю70752

чателя 3 фазы соединен с выходом четвертого инвертора 70 этого блока.

Детектор 4 смены уровня входного CHj Hfu ia предназначен для формирования импульсов при смене уровня входного сигнала, по длительности равных времени задержки ;п1нии 2 задержки. Он содержит два последовательно сое10 диненных транзистора 73 и 74. Сток и затвор первого 73 из них является соответственно первым 27 и вторым 35 входами детектора 4, а сток и затвор второго транзистора 74 являются соот15 ветственно третьим 38 и четвертым 39 входами детектора, выход 40 которого соединен с точкой соединения транзисторов 73 и 74 этого блока

Устройство 5 защиты формирует на

0 своем выходе 42 сигнал при коротком замыкании шины 17 выходног о сигнала. Оно содержит инвертор 75 и элемент 2И-ИЛИ/НЕ 76, включенные между шиной 64 питания и пятым входом 53

5 этого блока. Первый 36 и четвертый 57 входы устройства 5 защиты составляет первую пару входов по схеме И элемента 2И-ИЛИ/НЕ, а второй вход 39 устройства 5 защиты и выход ин0 вертора 75 этого блока составляют вторую пару входов по схеме И этог-о элемента. Третий вход 41 устройства 5 защиты является входом по схеме

ИЛИ элемента 2И-ИЛИ/НЕ, выход кото- I 5 рого является выходом 42 устройства

5 защиты.

Блок 6 управления промежуточным состоянием состоит из инвертора 77 и двух транзисторов 78 и 79. Вход

0 инвертора 77 является первым входом 20 блока 6 управления промежуточным состоянием и соединен с затвором второго транзистора 79, сток которого подключен к шине 64 пита5 ния. Затвор nepjBoro транзистора 78 соединен с выходом инвертора 77 этого блока, а сток является вторым входом блока 6 управления промежуточным состоянием. Истоки транзисторов 78 и

0 79 этого блока объединены и являются выходом 44 блока.„

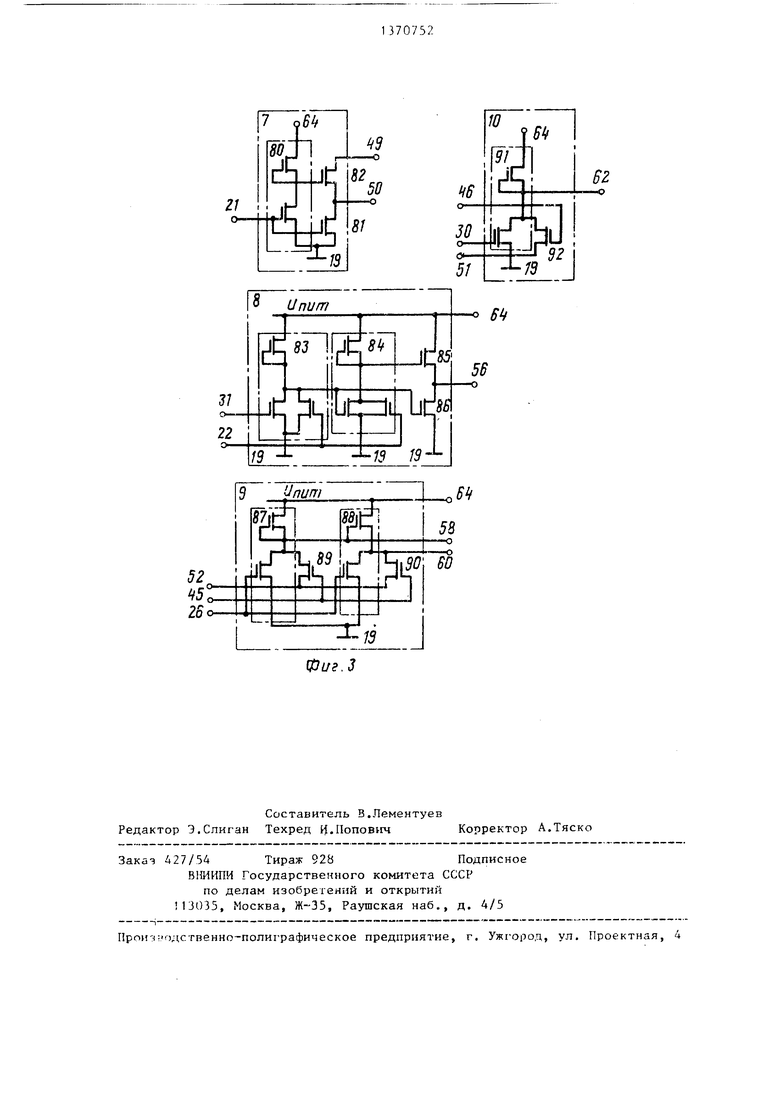

Коммутатор 7 уровня содержит инвертор 80 и два транзистора 81 и 82. Вход инвертора 80 соединен с затво5 ром первого транзистора 81, исток которого соединен с общей шиной и подключен к первому входу 21 коммутатора 7 уровня. Выход инвертора 80 подключен к затвору второго транзистора 82, сток которого является вторым входом 49 коммутатора 7 уровня, а точка соединения транзисторов 81 и 82 является выходом 50 этого блока

Блок 6 управления промежуточным состоянием формирует на своем выходе 44 блокирующий сигнал при поступлении на его входы 20 и 43 или сигнала управления промежуточным состоянием, или .сигнала с выхода 42 устройства 5 защиты.

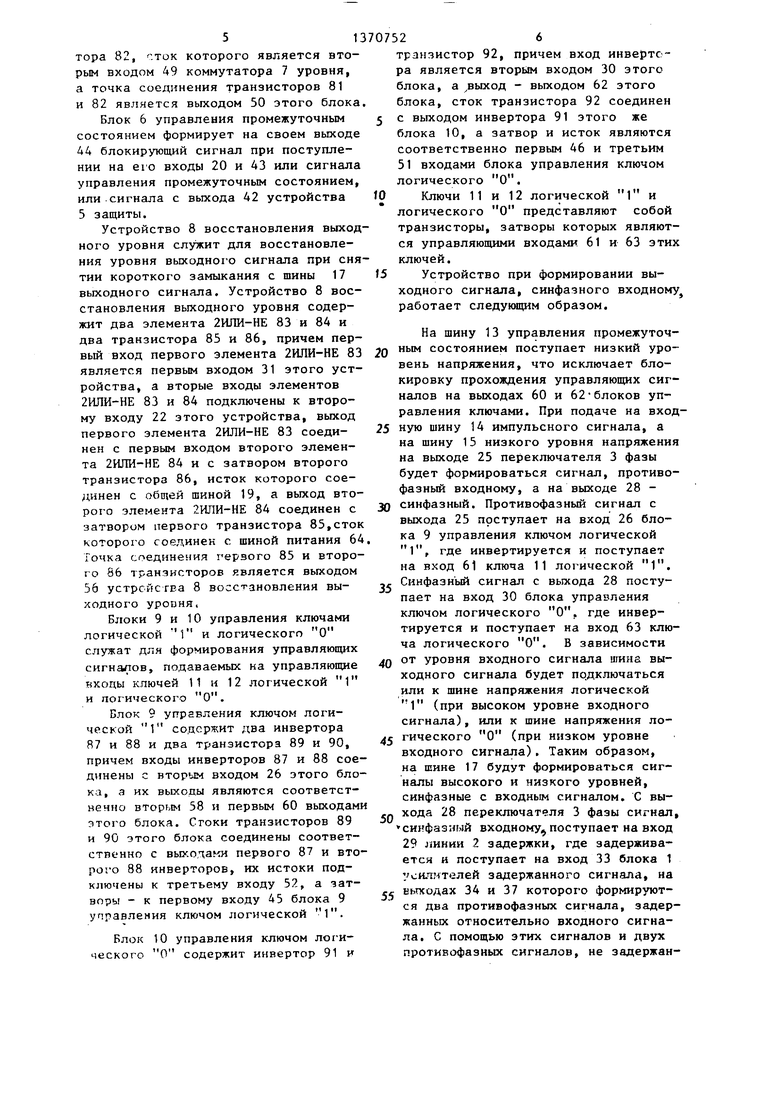

Устройство 8 восстановления выходного уровня служит для восстановления уровня выходного сигнала при снятии короткого замыкания с шины 17 выходного сигнала. Устройство 8 восстановления выходного уровня содержит два элемента 2ИЛИ-НЕ 83 и 84 и два транзистора 85 и 86, причем первый вход первого элемента 2ИЛИ-НЕ 83 является первым входом 31 этого устройства, а вторые входы элементов 2ИЛИ-НЕ 83 и 84 подключены к второму входу 22 этого устройства, выход первого элемента 2ИЛИ-НЕ 83 соединен с первым входом второго элемента 2ИЛИ-НЕ 84 и с затвором второго транзистора 86, исток которого соединен с общей шиной 19, а выход второго элемента 2ИЛИ-НЕ 84 соединен с затвором первого транзистора 85,сток которого соединен с. шиной питания 64 Точка соединения первого 85 и второго 86 транзисторов является выходом 56 устрсйсгва 8 восстановления выходного уровня.

Блоки 9 и 10 управления ключами логической и логического О служат для формирования управляющих сигналов, подаваемых на управляющие входы ключей 11 и 12 логической 1 и логического О.

Блок 9 управления ключом логической 1 содержит два инвертора 87 и 88 и два транзистора 89 и 90, причем входы инверторов 87 и 88 соединены с вторым входом 26 этого блока, а их выходы являются соответственно вторым 58 и первым 60 выходами этого блока. СРОКИ транзисторов 89 и 90 этого блока соединены соответственно с выходами первого 87 и второго 88 инверторов, их истоки подключены к третьему входу 52, а затворы - к первому входу 45 блока 9 управления ключом логической 1.

Блок 10 управления ключом логического О содержит инвертор 91 и

07526

транзистор 92, причем вход инвертора является BTopbiM входом 30 этого блока, а выход - выходом 62 этого блока, сток транзистора 92 соединен 5 с выходом инвертора 91 этого же блока 10, а затвор и исток являются соответственно первым 46 и третьим 51 входами блока управления ключом логического О.

to Ключи 11 и 12 логической 1 и логического О представляют собой транзисторы, затворы которых являются управляющими входами 61 и 63 этих ключей.

t5 Устройство при формировании выходного сигнала, синфазного входному работает следующим образом.

0

На шину 13 управления промежуточным состоянием поступает низкий уровень напряжения, что исключает блокировку прохождения управляющих сиг- нгшов на выходах 60 и 62блоков управления ключами. При подаче на вход5 ную шину 14 импульсного сигнала, а на шину 15 низкого уровня напряжения на выходе 25 переключателя 3 фазы будет формироваться сигнал, противофазный входному, а на выходе 28 0 синфазный. Противофазный сигнал с выхода 25 поступает на вход 26 блока 9 управления ключом логической 1, где инвертируется и поступает на вход 61 ключа 11 логической 1. Синфазный сигнал с выхода 28 поступает на вход 30 блока управления ключом логического О, где инвертируется и поступает на вход 63 ключа логического О. В зависимости от уровня входного сигнала шина выходного сигнала будет подключаться или к шине напряжения логической 1 (при высоком уровне входного сигнала), или к шине напряжения ло5 гического О (при низком уровне входного сигнала). Таким образом, на шине 17 будут формироваться сигналы высокого и низкого уровней, синфазные с входным сигналом, С выхода 28 переключателя 3 фазы сигнал, сиифазиый входному поступает на вход 29 линии 2 задержки, где задерживается и поступает на вход 33 блока 1 y ;ил тeлeй задержанного сигнала, на

г выходах 34 и 37 которого формируются два противофазных сигнала, задержанных относительно входного сигнала. С помощью этих сигналов и двух противофазных сигналов, не задержан5

0

0

7

ных относительно входного сигнала на выходе 40 детектора 4 во время переходного фоцесса, формируется импульс, по длительности равный длительности задержки. Этот импульс блокирует выход 42 устройства 5 защиты на общую шину, исключая формирование блокирующего сигнала на выходе 42, и обеспечивает устойчивую работу устройства в режимах формирования выходных сигналов. На выходе устройства 8 восстановления формируется сигнал, синфазный с выходным. Выходное сопротивление устройства восстановления намного больше выходного сопротивления открытых ключей 11 и 12 и в режимах формирования устройством выходных сигналов не оказывает влияния на формирование выходных импульсов.

Рассмотрим работу устройства при коротком замыкании шины 17 выходног сигнала на низкий уровень напряжения. I

На выходе 42 устройства 5 защиты вырабатывается блокирующий импульс, который передается через блок 6 управления промежуточным состоянием и блокирует входы 61 и 63 на шину напряжения логического О, вследствие чего ключи 11 и 12 закрываются и протекание тока через них исключается. В это время на выходе 56 устройства 8 восстановления должен формироваться высокий уровень, но выход 56 закорочен на низкий уровень напряжения, следовательно ток будет протекать с выхода 56.Но так как выходное напряжение устройства 8 восстановления большое, то ток этот будет незначительный. Формирование сигнала на выходе 42 устройства 5 защиты будет происходить, когда не будут совпадать фаза входного сигнала и фаза сигнала на выходной шине 17 при работе устройства в режиме формирования синфазных сигналов. Входной сигнал в это время имеет высокий уровень, а выходной сигнал - низкий, следовательно, на выходе 42 вьфабатывается сигнал за исключением времени, когда формируется сигнал на выходе 40 детектора 4 смены уровня входного сигнала. Следовательно, если ыходной сигнал начнет формироваться раньше, чем окончится импульс на выходе 40, то вотможно протекание тока во вре707528

мя переходного процесса черет ключ 11. Это произойдет в том случае, если время задержки сигнала на линии 2 задержки будет больше, чем время задержки формирования выходного сигнала относительно входного. Если эти времена будут равны, то ток через ключ 11 во время короткого замыкания

д протекать не будет. Так как уровень логического О выходного сигнала может отличаться от уровня логического О входного сигнала и сигналов, вырабатываемых узлами устройства,

15 то для обеспечения формирования сигнала защиты на выходе 42 необходимо подавать в режимах формирования выходных сигналов уровень напряжения логического О шины 18 на входы

20 51 - 53.

Устройство переключается по сиг на- лу на шине 15 на работу в режиме формирования сигналов на выходной шине, противофазных входным. По этому сиг25 налу фазы сигналов на выходах 25 и 28 изменяются на противофазные.Все остальные функциональные узлы устройства при работе устройства в режиме формирования выходного сигнала,

30 противофазного входному, работают так же, как в режиме формирования выходного сигнала, синфазного входному.

.jf Работа устройства при коротком замыкании выходной шины на высокий уровень напряжения аналогична работе при коротком замыкании на шину низкого уровня, за исключением того,

40 что, так как в это время формируются на выходе устройства сигналы, противофазные входному, блокирующий сигнал на выходе 42 формируется тогда, когда сигнал на выходной шине 17 син45 фазный входному. Таким образом, перевод ключей 11 и 12 в непроводящее состояние осуществляется при коротком замыкании выходной шины на высокий или низкий уровень напряжения в

50 случае работы устройства в режиме

формирования синфазных сигналов входным при несовпадении фаз входног о и выходного сигналов, а при работе в режиме формирования сигналов, проти5 вофазных входным - при совпадении фаз входного и выходног О сигналов. Когда на шину 13 поступает управляющий сигнал, на выходе 44 блока 6 управления промежуточным состоянием

вырабатывается сигнал, который пере- воцт;т ;лк; И 1 и 12 в непроводящее состояние- i одноиременио переводит выход эб устройства 8 восстановления и высоксимпедансное состояние. Кроме того, этим сигналом выход 50 коммутатора 7 уровня переключается на общую шину. Данное коммутирование необходимо в том случае, когда уровень напряжения логического О на шине 18 будет выше уровня напряжения на общей шине на величину, равную или выше порогового напряжения ключей 11 и 12, чтобы исключить протекание через них тока. В случае коммутации вьпсода 50 на общую шину на выходах 60 и 62 установятся потенциа- ЛЬ|, 6junKMe к потенциалу общей шины, и кхгючи будут в высокоимпедансном состоянии в диапазоне напряжений от уровня напряжения общей шины и до допустимого высокого уровня напряжения ,

Устройство формирования импульсны сигналов и уровней постоянного напряжения на МДП-транзисторах обеспечива;| нормирование улируемых по уров ..h. HMnyiJbcvi-к сигналов и уровней по- CTU74HCT-O налряжгчиг с переключением С iiKoruioM y упр:;)Лг ;ощ; му сигийлу на . .li jHSHbu : и проти....: .-. иый режимы ра- .- : . - , е г1п;итой o l ороткого замика- чик вьгх.одной шины на амсокий и низ- KVM уровни г.атгр -г.тйняя и иосстановле- /i:i- M уровней выходного сигнала при

нятпи замыкания с шины выходного сиг кала, а тдкже обеспечивает пере- ,;юч -1 1 0 выхода устройст а но уп- i-.av; .я оиему сит напу и высокоимпеданс- ло - .:ос7онние. Таким , прод- ла :i..-i устройсттю за счет расширеи.; ;1eж:t ioв расширяет область пр; ененяя.

Формула изобретения

1 „ Устрснг.тнс формирования импуль . ;ai; .::ов и уровней постоянного г пфржения на МЛП-транзисторах, со- :. - ржагдее блок уф оления ключом логической 1, блок управления ключом . ог -1еского О, блок управления про ме-куточнь состоянием, включенные- 1еж-ту шиноГ| ;1нт-5ния и общей шиной, а т .1кже члюч лог ической 1 и ключ -огмческого О, выходы блоков уп- 1.-;влгния ключами логической Г и

5

7075210

логического О соответственно подключены к управляющим входам ключей логическрй 1 и логического О, ключи логической 1 и логического О соединены последовательно и включены между шинами напряжений логической 1 и логического О, а точка соединения ключей подключена к шине выходного сигнала, выход бла- ка управления промежуточным состоянием подключен к первым входам бло10

ка управления ключами логической 1 и логического О, первый вход блока

управления промежуточным состоянием подключен к шине управления промежуточным состоянием, отличающееся тем, что, с целью расширения функциональных возможностей устройства и повьш1ения надежности, в него дополнительно введены блок усилителей задержанного сигнала, линия задержки, детектор смены уровня входного сигнала, переключатель фазы, устройство защиты, коммутатор уровня, устройство восстановления выходного уровня, первый вход переключателя фазы подключен к шине входного сигнала, второй вход - к шине сигнала переключения фазы, первьп выход переключателя фазы подключен к второму входу блока управления ключом логической 1 и к первому нходу детектора смены уровня входного сигнала, второй вьгеод - к второму входу блока управления ключом логического О, к первому входу устройства восстановления выходного уровня и к входу линии задержки, выход которой подключен к входу блока усилителей задержанных сигналов, первый выход которого подключен к первому входу устройства защиты и х второ.му входу детектора смены уровня

входного сигнала, а второй выход подключен к второму входу устройства защиты и к третьему входу детектора смены уровня входного сигнала, чет- вертьй вход чете стора смены уровня входного си:си.1.1Л подключен к второму выходу блч кг управления ключом логи- ческсй Г , а его выход подсоединен к Т1 тьему ВХО/.:У устройства защиты, ч ;вертъ Й вход устройства зашиты 11,. дключен к выходу устройства вос- таноалеиия выходного уроння и к тине Га ходно1 о сигнала, пятый вход подключен к выходу коммутатора уровня и к 7peтьи J выгодам G.: OROB упрап

II

ления ключами, выход устройства защиты подключен к второму входу блока управле- ия промежуточным состоянием, первый вход коммутатора уровн подключен к шине сигнала управления промежуточным состоянием и к втором входу устройства восстановления вы- ходног о уровня, а второй и третий входы подключены соответственно к шине напряжения логического О и к общей шине, блок усилителей задержанного сигнала, переключатель фазы, блок управления промежуточным состоянием, коммутатор уровня, устройство восстановления уровня выходного сигнала, блоки управления ключами логической 1 и логическо-- го О включены также между шиной питания и общей шиной.

2.Устройство по п. 1, отличающееся тем, что переключатель фазы содержит четыре инвертора и два транзистора, вход первог инвертора является первым входом переключателя фазы, а его выход подключен к входу второго инвертора и

к стоку первого транзистора, исток которого является вторым выходом переключателя фазы, выход второго инвертора соединен со стоком второго транзистора, исток которого является первым выходом переключателя фазы, вход третьего инвертора является вторым входом переключателя фазы, а его выход соединен с входом четвертого инвертора и с затвором второго транзистора, затвор первого транзистора соединен с выходом четвертого инвертора.

3.Устройство по п. 1, о т л и - ча.ющееся тем, что детектор смены уровня выходного сигнала содержит два последовательно соеди- ненньк транзистора, сток и затвор первого из них являются соответственно первым и вторым, а сток и затвор второго - третьим и четвертым входами детектора смены уровня выходного сигнала, а точка соединения транзисторов - его выходом.

4.Устройство по п. 1, отличающееся тем, что устройство защиты выполнено на элементе 2H-RnPl/HE и инверторе, вклю енных между шиной питания и пятым входом устройства защиты, первый и четвертый входы устройства защиты подключены к первой паре входов по схеме И

7075212

элемента 2И-Ш1И/НЕ, а второй вход устройства защиты и выход инвертора этого блока составляют вторую пару входов по схеме И элемента 2И-ИЛ1 /НЕ, третий вход устройства защиты является входом по схеме 11П11 элемента 2И-ИЛИ/НЕ, выход которого является выходом устройства защиты.

Q 5. Устройство по п. 1, о т л и - чающееся тем, что блок управления промежуточным состоянием состоит из инвертора я двух транзисторов, вход инвертора является первым

5 входам этого блока и соединен с затвором второго транзистора, сток которого подключен к шине питания, затвор первого транзистора соединен с выходом инвертора, а сток является вторым

2Q входом этого блока, истоки этих транзисторов объединены и являются выходом блока управления промежуточным состоянием.

6.Устройство по п. 1, о т л и - 25 чающееся тем, что коммутатор уровня содержит инвертор и два транзистора, вход инвертора соединен с затвором первого транзистора, исток которого соединен с общей шиной и с

30 первым входом коммутатора уровня, выход инвертора соединен с затвором второго транзистора, сток которого является вторым входом коммутатора уровня, а точка соединения транзисторов - его выходом.

7.Устройство по п. 1, отличающееся тем, что устройство восстановления уровня выходного сигнала содержит два элемента 2ИЛИ-НЕ

40 и два транзистора, причем первый вход первого элемента 2ИЛИ-НЕ является первым входом устройства восстановления уровня выходного сигнала, а вторые входы элементов 2ИЛИ-НЕ объедс динены и являются вторым входом устройства восстановления уровня выходного сигнала, выходом которого является точка соединения транзисторов, Бькод первого элемента 2ИЛИ-НЕ соеди

нен с первым входом второго элемента

2ИЛИ-НЕ и с затвором второго зистора, исток которого соединен с общей шиной, а выход второго элемента 2ИЛИ-НЕ соединен с затвором перво- го транзистора, сток которого соединен р шиной питания.

8. Устройство по п. 1, отличающееся тем, что блоки уп 31370752

равления ключами логической 1 и выходом этого блока, к которому под- логического О содержат по меньшей ключей также сток транзистора, исток .мере один инвертор и один транзистор, и затвор которого соединены соответ- причем вход инвертора является вто- ственно с третьим и с первым входами рым входом этого блока, а выход - блока управления ключами.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР ТЕСТОВЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2034399C1 |

| Логический элемент Исключающее ИЛИ | 1982 |

|

SU1072264A1 |

| Детектор фронта сигнала | 1987 |

|

SU1474834A1 |

| Многоканальный коммутатор | 1984 |

|

SU1220123A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832994C1 |

| Ячейка памяти | 1979 |

|

SU1022222A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653304C1 |

| Устройство обнаружения смены адресного сигнала в интегральном исполнении на МОП-транзисторах | 1984 |

|

SU1249695A1 |

| Стабилизатор постоянного напряжения | 1988 |

|

SU1557552A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

Изобретение может быть использовано в качестве устройства формирования импульсных режимных воздействий в приборах измерительной и вычислительной техники. Целью изобре-. тения является расширение функциональных возможностей. Цель достигается п результате введения в устройство ;;оп(итнительных блоков; блока 1 усилителей задержанного сигнала с линией 2 задержки, детектора 4 смены уровня выходного сигнала, переключателя 3 фазы, блока 5 защиты,коммутатора 7 уровня и устройства 8 восстановления выходного уровня. Это обеспечивает возможность подачи на шину выходного сигнала сигналов от других источников информации, автоматический перевод выхода устройства в высокоимпедансное состояние, защиту от больших токов в ключах и повышение надежности устройства. На чертеже также показаны блоки 9-12 управления ключами логичес 0 , шина 13 управления промежуточным состоянием, шина 14 входного сигнала, шина 15 переключения фазы, шины 17 и 18 напряжения логической 1 и О соответственно, шина 17 выходного сигнала, общая шина 19. Позициями 20-61 показаны входы и выходы соответствующих блоков. 7. з.п. ф-лы, 3 ил. /)

№i

Ь27 ЬЧО

дзиг.г

Фиг.З

5/

9Z I

J-;g I

о 54

| Формирователь импульсов | 1984 |

|

SU1170599A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Электронная техника | |||

| Сер | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Счетная таблица | 1919 |

|

SU104A1 |

| М.: ЦНИИ Электроника, 1983, с | |||

| Шкив для канатной передачи | 1920 |

|

SU109A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-01-30—Публикация

1986-08-15—Подача