Изобретение относится к радиотехнике и может быть применено в импульсной технике и автоматике.

Известен генератор, который йодержит статический триггер, времязадающие конденсаторы, времязадающие транзисторы и формирователь напряжения питания затворов времязадающих транзисторов 1.

Недостаток известного генератора состоит в том, что из-за отсутствия положительной обратной связи во время переключения имеют место большие длительности фронтов генерируемых импульсов, ограничен диапазон генерируемых частот и отсутствует автоматическая подстройка частоты.

Наиболее близким к предлагаемому являетсягенератор импульсов, содержащий статический триггер, два заторможенных мультивибратора, каждый из которых .содержит инвертор положительной обратной связи, времязадающий транзистор, времязадающий конденсатор и разрядный транзистор, причем каждый из входов триггера подключен к точкам соединения времязадающего и разрядного транзисторов и через времязадающий конденсатор к выходу инвертора обратной связи.

. вход последнего подключен к одному из выходов триггера 2.

Недостатком данного импульсного генератора является то, что для его работы требуется внешний источник стабильного напряжения, причем при отклонении параметров времязадающей цепи от номинсшьных значений измег няется частота генерирования устрой10ства.

Цель изобретения - расширение функциональных возможностей путем автоматической подстройки частоты генерирования импульсов к номиналь15ному значению при изменении питающего напряжения, температуры окружающей среды и параметров времязадающих цепей, получения линейной зависимости частоты гёнерирсэвания от прово20димости регулирующего резистора, а также путем обеспечения начала генерации импульсов при включении источника питания с определенной фазы.

Поставленная цель достигается

25 тем, что в импульсный генератор, содержащий статический триггер и два заторможенных мультивибратора, каждый из которых содержит инвертор обратной связи, времязадающий конден30сатор, времязадающий транзистор

и разрядный транзистор, выходом подключенных к соответствующим входам триггера, дополнительно введены устройство выделения последнего периода, делитель напряжения, дифференциальный усилитель, устройство запуска, устройство вьаделения сигналов рассогласования и параллельно соединенные разрядный резистор и накопительный конденсатор, причем устройство запуска содержит два блокирующих транзистора и две цепочки, состоящих из двухпоследовательно включенных транзисторов, а устройство вьщеления сигисшов рассогласования содержит два двухтактных усилителя, состоящих из повторяющего и инвертирующего транзисторов. Перв цепочку из четырех последовательно включенных транзисторов, элемент ИЛ на два входа с запоминающим конденсатором между затвором и истоком нагрузочного транзистора, один из входов элемента ИЛИ подключен к шин синхронизации и затворам нижних транзисторов первой цепочки устройства запуска и цепочки устройства выделения сигналов рассогласования, второй вход элемента ИЛИ подключен ко входу устройства выделения последнего периода,- к выходу правого плеча триггера и к затворам повторящего транзистора второго двухтактного усилителя и верхнего транзистора второй цепочки устройства запуска, второй вход устройства выделения последнего периода подключен к выходу левого плеча триггера и к затворам инвертирующих транзисторов двухтактных усилителей и нижнего транзистора второй цепочки устройст ва запуска, выход первой цепочки устройства запуска подключен-к затворам первого и второго блокирующих транзисторов, которые соответственно включены между входом левого пле ча триггера и общей шиной и между выходом левого плеча триггера и общей шиной, выход второй цепочки подключен к затворам верхнего транзистора первой цепочки и повторяющего транзистора первого двухтактного усилителя, выход первого двухтактного усилителя подключен к зат|ВОру среднего транзистора цепочки устройства выделения сигналов рассогласования, выход второго двухтйктного усилителя подключен к затвру нагрузочного транзистора элемента ИЛИ, выход элемента ИЛИ подключен к затвору верхнего транзистора цепочки устройства вьвделения сигналов рассогласования, а выход этой цепочки подключен к точке соединени разрядного резистора, накопительного конденсатора и к одному из входов дифференциальнбго усилителя, второй

вход дифференциальнохо усилителя подключен к делителю напряжения, а выход дифференциального усилителя подключен к затворам времязадающих транзисторов, выход устройства выделения последнего периода подключен к стокам повторяющего транзистора второго двухтактного усилителя и верхнего транзистора второй цепочки устройства запуска.

По второму варианту исполнения в устройство дополнительно введены элемент ИЛИ, запускающий конденсато включенный между выходом элемента И и шиной питания, два дополнительных блокирующих транзистора -и две цепочки формирования сигналов блокировки каждая из которых включена между одним из выходов.триггера и общей шиной, и состоящих из .последовательно включенных смещающего и обнуляющего транзисторов, соединенных с затворами.разрядных транзисторов заторможенных мультивибраторов и со входом элемента ИЛИ, причем затвор и сток смещающего транзистора цепочки формирования сигналов блокировки подключены к одному из выходов триггера, а затвор обнуляющего транзистора этой цепочки подключен к другому выходу триггера, выход элмента ИЛИ подключен к затворам дополнительных блркирукндих транзисторов, один иэ которых включен между одним из выходов триггера и общей шиной, а другой - между противоположным этому выходу входом триггера и общей шиной.

По третьему варианту исполнения в известное устройство дополнительно введена цепочка из четырех последовательно включенных транзисторов, преобразователь частоты-напряжения, содержащий истоковый повторитель, три проходнь1х транзистора, блокирующий транзистор, смещающий транзистор, дозирующий конденсатор, накопительный конденсатор и регулирующий резистор, причем сток и затвор смещающего транзистора подключены к истоку первого проходного транзистора, сток которого подключен к затвору повторяющего транзистора истокового повторителя и к истоку второго проходного транзистора, сто второго проходного транзистора через дозирующий конденсатор подключе к выходу истокового повторителя, а через третий.проходной транзистор к выходу, второй цепочки иэ четырех последовательно включенных транзисторов между выходом истокового повторителя и общей шиной подключены нагрузочный и блокирующий транзисторы, причем эатвор нагрузочного транзистора подключен к выходу цепочки из четырех последовательно

включенных транзисторо, затворы первого и второго проходных транзисторов подключены к одному из выходов триггера, а затворы третьего проходно-го и блокирующего транзисторов подключены ко второму выходу триггера.

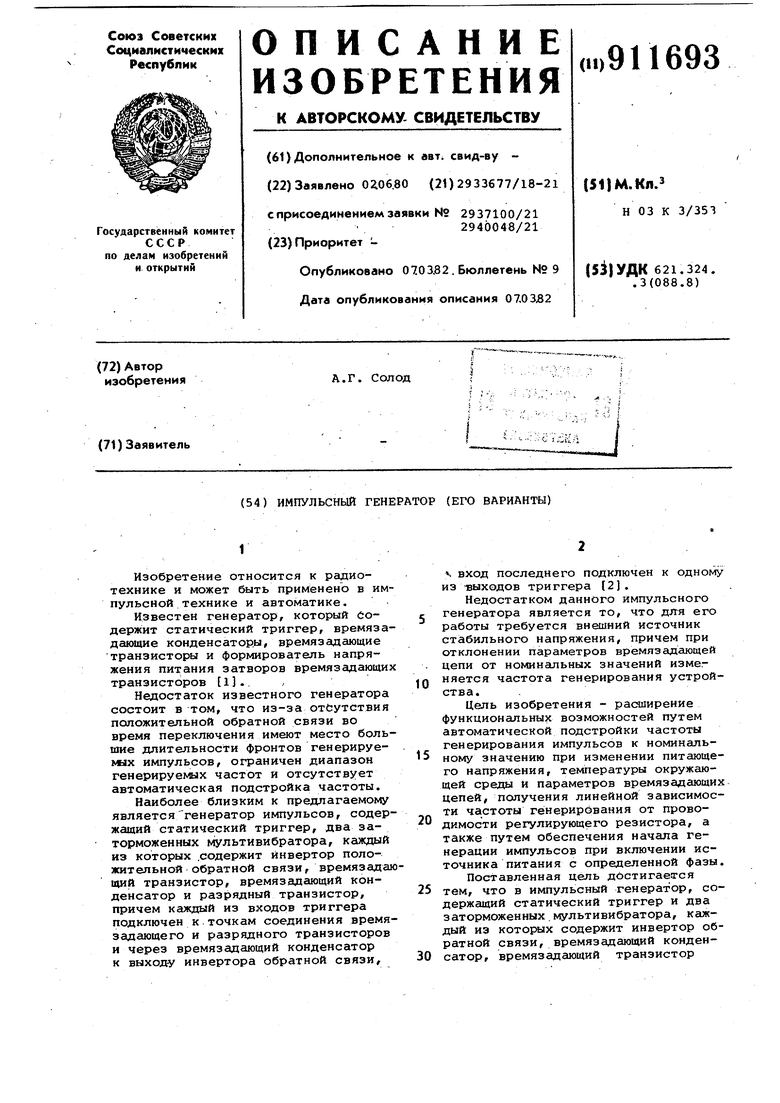

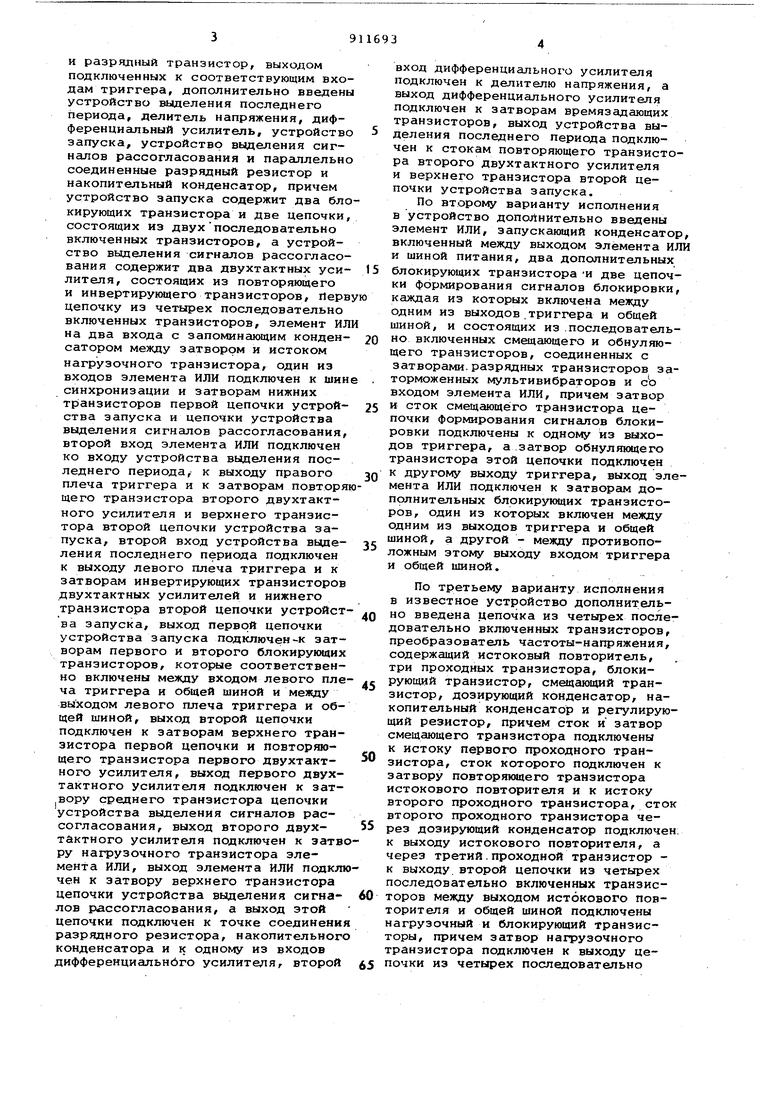

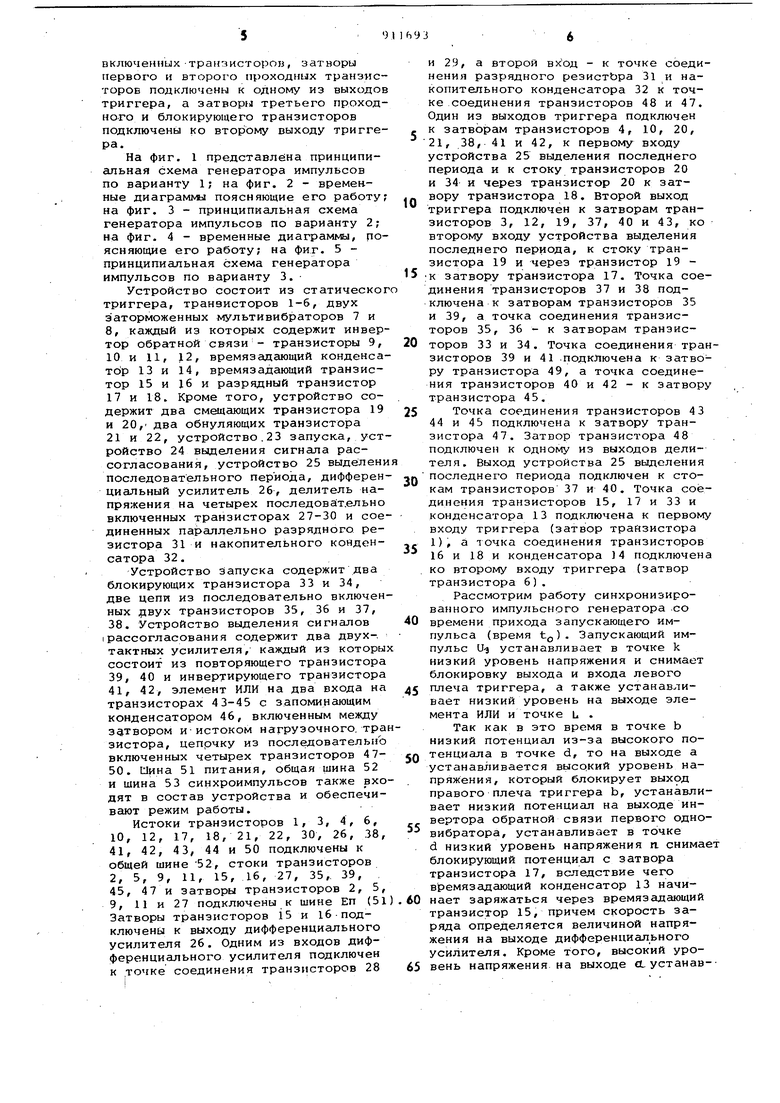

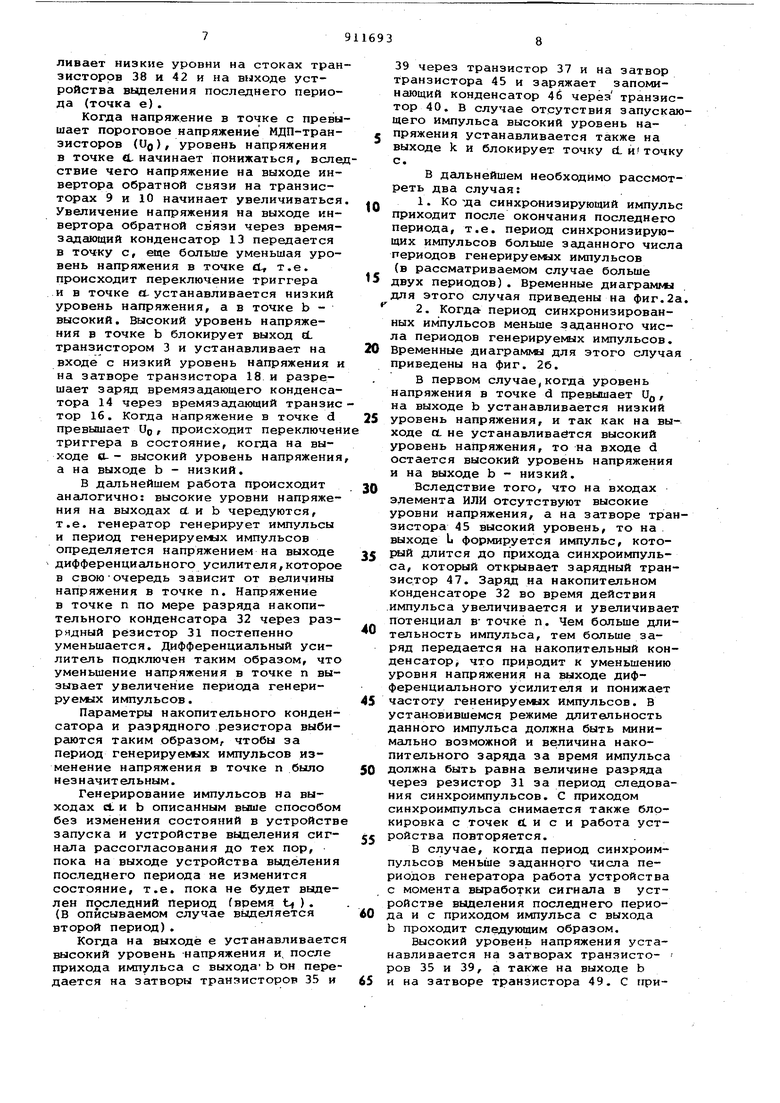

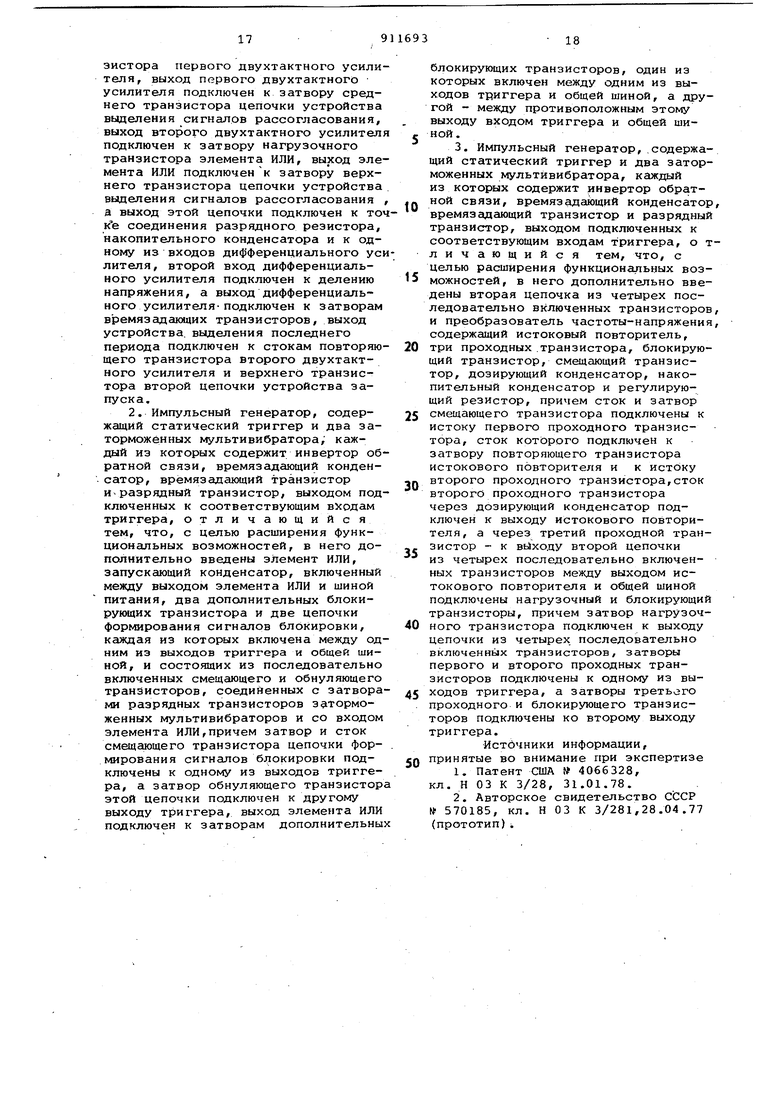

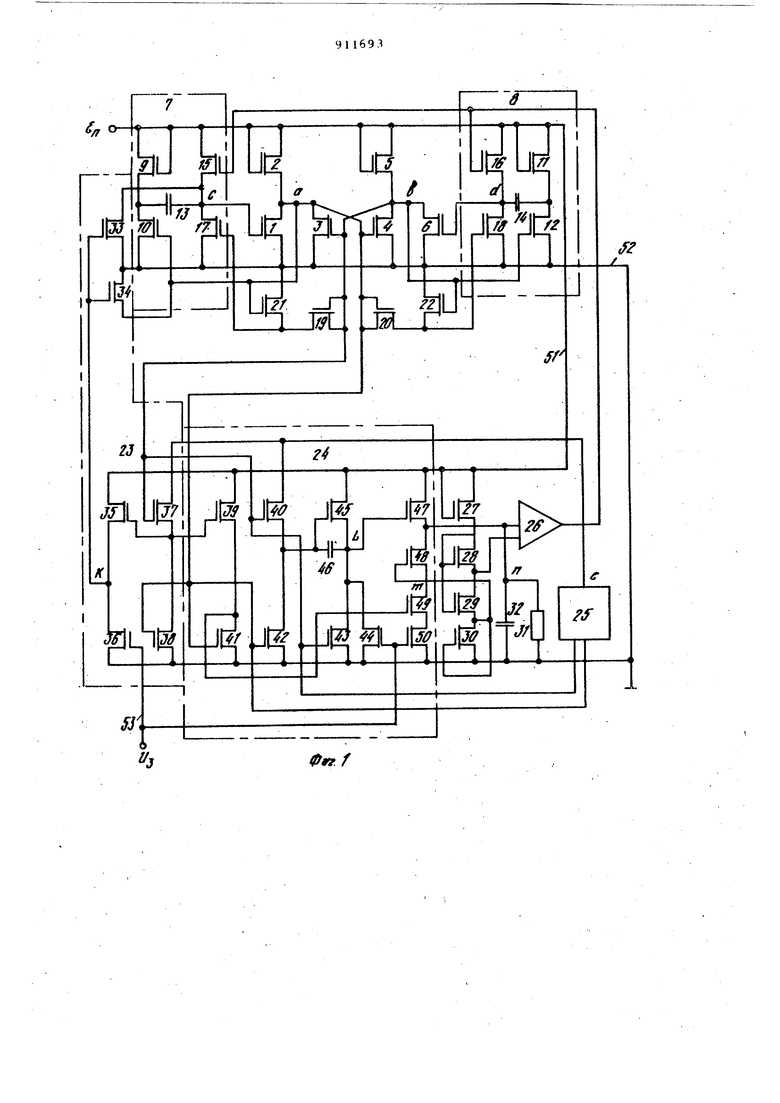

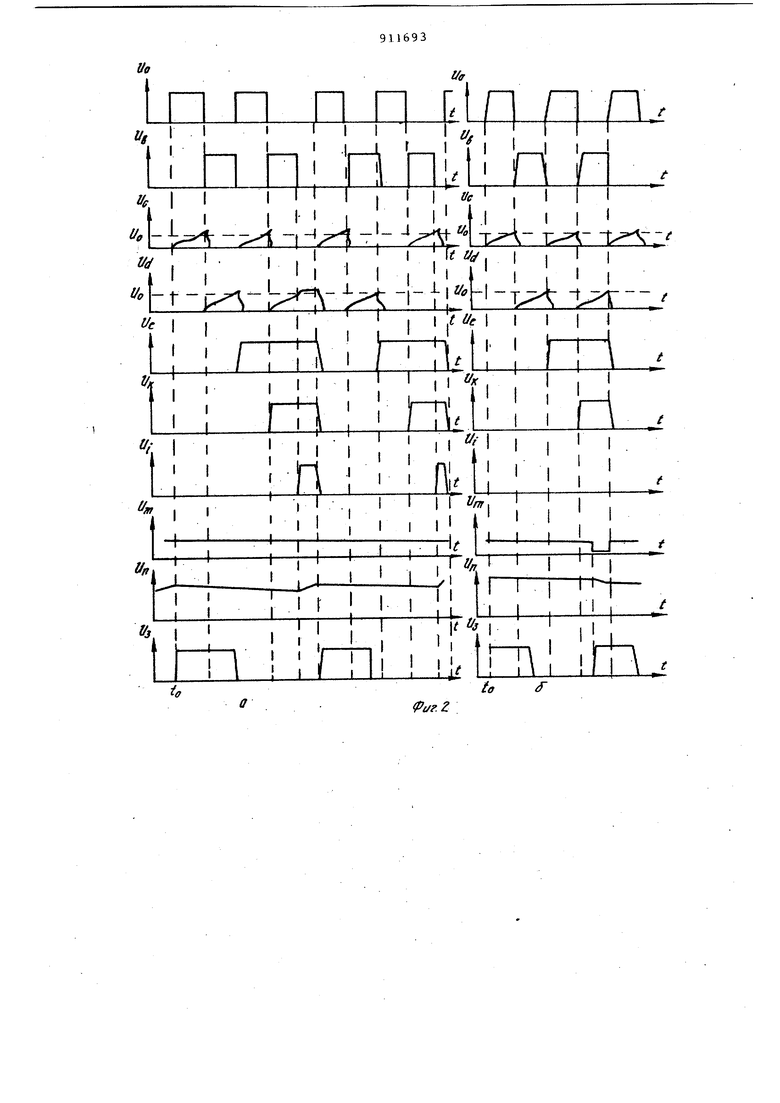

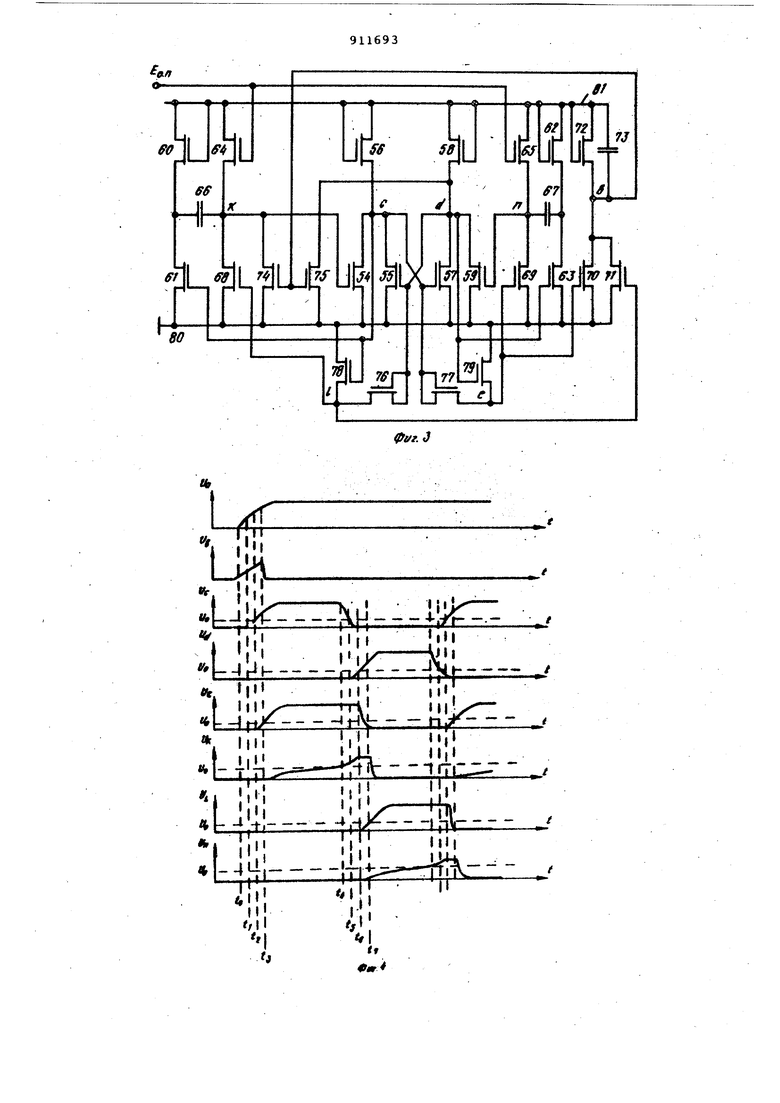

На фиг. 1 представлена принципиальная схема генератора импульсов по варианту 1; на фиг. 2 - временные диаграм1 ы поясняющие его работу; на фиг. 3 - принципиальная схема генератора импульсов по варианту 2; на фиг. 4 - временные диаграммы, поясняющие его работу; на фиг. 5 принципиальная схема генератора импульсов по варианту 3.

Устройство состоит из статическог триггера, транзисторов 1-6, двух заторможенных мультивибраторов 7 и

8,каждый из которых содержит инвертор обратной связи- транзисторы 9, 10 и 11, 12, времязадающий конденсатор 13 и 14, времязадающий транзистор 15 и 16 и разрядный транзистор 17 и 18. Кроме того, устройство содержит два смещающих транзистора 19 и 20, два обнуляющих транзистора

21 и 22, устройство.23 запуска, устройство 24 выделения сигнала рассогласования, устройство 25 выделени последовательного периода, дифференциальный усилитель 26, делитель напряжения на четырех последовйт.ельно включенных транзисторах 27-30 и соединенных параллельно разрядного резистора 31 и накопительного конденсатора 32.

Устройство запуска содержит два блокирующих транзистора 33 и 34, две цепи из последовательно включенных двух транзисторов 35, 36 и 37,

38.Устройство выделения сигналов (рассогласования содержит два двух-,

тактных усилителя, каждый из которых состоит из повторяющего транзистора

39,40 и инвертирующего транзистора 41, 42, элемент ИЛИ на два входа на транзисторах 43-45 с запоминающим конденсатором 46, включенным между затвором и-истоком нагрузочного, транзистора, цепрчку из последовательно включенных четырех транзисторов 4750. Иина 51 питания, общая шина 52

и шина 53 синхроимпульсов также входят в состав устройства и обеспечивают режим работы.

Истоки транзисторов 1, 3, 4, 6, 10, 12, 17, 18, 21, 22, 30, 26, 38, 41, 42, 43, 44 и 50 подключены к общей шине 52, стоки транзисторов 2, 5, 9, 11, 15, 16, 27, 35, 39, 45, 47 и затворы транзисторов 2, 5,

9,11 и 27 подключены к шине Еп (51 Затворы транзисторов 15 и 16-подключены к выходу дифференциального усилителя 26. Одним из входов дифференциального усилителя подключен

к точке соединения транзисторов 28

и 29, а второй вхЪд - к точке соединения разрядного резистЬра 31 и накопительного конденсатора 32 к точке соединения транзисторов 48 и 47. Один из выходов триггера подключен к затворам транзисторов 4, 10, 20, 21, 38,41 и 42, к первому входу устройства 25 выделения последнего периода и к стоку транзисторов 20 и 34 и через транзистор 20 к затвору транзистора 18. Второй выход

0 триггера подключен к затворам транзисторов 3, 12, 19, 37, 40 и 43, ко второму входу устройства выделения последнего периода, к стоку транзистора 19 и через транзистор 19 5:к затвору транзистора 17. Точка соединения транзисторов 37 и 38 подключена к затворам транзисторов 35 и 39, а точка соединения транзисторов 35, 36 - к затворам транзис0торов 33 и 34. Точка соединения транзисторов 39 и 41 .подключена к затвору транзистора 49, а точка соединения транзисторов 40 и 42 - к затвору транзистора 45.

5

Точка соединения транзисторов 43 44 и 45 подключена к затвору транзистора 47. Затвор транзистора 48 подключен к одному из выходов делителя. Выход устройства 25 выделения последнего периода подключен к сто0кам транзисторов 37 и 40. Точка соединения транзисторов 15, 17 и 33 и конденсатора 13 подключена к первому входу триггера (затвор транзистора 1), а 1очка соединения транзисторов

5 16 и 18 и конденсатора 14 подключена ко второму входу триггера (затвор транзистора 6).

Рассмотрим работу синхронизированного импульсного генератора со

0 времени прихода запускающего импульса (время to). Запускающий импульс U-3 устанавливает в точке k низкий уровень напряжения и снимает блокировку выхода и входа левого плеча триггера, а также устанавли5вает низкий уровень на выходе элемента ИЛИ и точке L .

Так как в это время в точке b низкий Потенциал из-за высокого потенциала в точке d, то на выходе а

0 устанавливается высокий уровень напряжения, который блокирует выход правого плеча триггера Ь, устанавливает низкий потенциал на выходе инвертора обратной связи первого одно5вибратора, устанавливает в точке d низкий уровень напряжения п. снимает блокирующий потенциал с затвора транзистора 17, вследствие чего времязадающий конденсатор 13 начи0нает заряжаться через времязадеиощий транзистор 15, причем скорость заряда определяется величиной напряжения на выходе дифференциального усилителя. Кроме того, высокий уровень напряжения на выходе Лустанав-5

ливает низкие уровни на стоках транзисторов 38 и 42 и на выходе устройства вьаделения последнего периода (точка е).

Когда напряжение в точке с превышает пороговое напряжение МДП-транзисторов (Ufl), уровень напряжения в точке «L начинает понижаться, вслествие чего напряжение на выходе инвертора обратной связи на транзисторах 9 и 10 начинает увеличиваться Увеличение напряжения на выходе инвертора обратной связи через времязадающий конденсатор 13 передается в точку с, еще больше уменьшая уровень напряжения в точке CL т.е. происходит переключение триггера и в точке О-устанавливается низкий уровень напряжения, а в точке b высокий. Высокий уровень напряжения в точке Ь блокирует выход йтранзистором 3 и устанавливает на входе с низкий уровень напряжения и на затворе транзистора 18. и разрешает заряд времязадающего конденсатора 14 через времязадающий транзистор 16. Когда напряжение в точке d превышает UQ, происходит переключен триггера в состояние, когда на выходе О- - высокий уровень напряжения а на выходе b - низкий.

В дальнейшем работа происходит аналогично: высокие уровни напряжения на выходах ct и b чередуются, т.е. генератор генерирует импульсы и период генерируемых импульсов определяется напряжением на выходе дифференциального усилителя,которое в своюОчередь зависит от величины напряжения в точке п. Напряжение в точке п по мере разряда накопительного конденсатора 32 через разрядный резистор 31 постепенно уменьшается. Дифференциальный усилитель подключен таким образом, что уменьшение напряжения в точке п вызывает увеличение периода генерируемых импульсов.

Параметры накопительного конденсатора и разрядного резистора выбираются таким образом, чтобы за период генерируемых импульсов изменение напряжения в точке п было незначительным.

Генерирование импульсов на выходах d и b описанным выше способом без изменения состояний в устройств запуска и устройстве вьщеления сигнала рассогласования до тех пор, пока на выходе устройства вьщеления последнего периода не изменится состояние, т.е. пока не будет выделен последний Период (время tf ). (В описываемом случае ввделяется

второй период).

Когда на выходе е устанавливаетс высокий уровень напряжения и, после прихода импульса с выхода- b он передается на затворы транзисторов 35 и

39 через транзистор 37 и на затвор транзистора 45 и заряжает запоминающий конденсатор 46 через транзистор 40, В случае отсутствия запускающего импульса высокий уровень напряжения устанавливается также на выходе k и блокирует точку d. и/ точку с.

В дальнейшем необходимо рассмотреть два случая:

Q 1. Ко ща синхронизирующий импульс приходит после окончания последнего периода, т.е. период синхронизирующих импульсов больше заданного числа периодов генерируемых импульсов (в рассматриваемом случае больше

5 двух периодов). Временные диаграмма

для этого случая приведены на фиг.2а. 2. Когда период синхронизированных импульсов меньше заданного числа периодов генерируе1«ых импульсов.

0 Временные диаграмма для этого случая приведены на фиг. 26.

В первом случае,когда уровень напряжения в точке d превышает Од, на выходе b устанавливается низкий

5 уровень напряжения, и так как на выходе О. не устанавливается высокий уровень напряжения, то на входе d остается высокий уровень напряжения и на выходе b - низкий.

0 Вследствие того, что на входах элемента ИЛИ отсутствуют высокие уровни напряжения, а на затворе транзистора 45 высокий уровень, то на выходе L формируется импульс, котоJ рый длится до прихода синхроимпульса, который открывает зарядный транзиртор 47. Заряд на накопительном конденсаторе 32 во время действия импульса увеличивается и увеличивает потенциал в- точке п. Чем больше длительность импульса, тем больше заряд передается на накопительный конденсатор j что приводит к уменьшению уровня напряжения на выходе дифференциального усилителя и понижает

5 частоту гененируемлх импульсов. В установившемся режиме длительность данного импульса должна быть минимально возможной и величина накопительного заряда за время импульса

0 должна быть равна величине разряда через резистор 31 за период следования синхроимпульсов. С приходом синхроимпульса снимается также блокировка с точек d и с и работа устг ройства повторяется.

В случае, когда период синхроимпульсов меньше заданного числа периодов генератора работа устройства с момента выработки сигнала в устройстве выделения последнего периода и с приходом импульса с выхода b проходит следующим образом.

Высокий уровень напряжения устанавливается на затворах транзисторов 35 и 39, а также на выходе b

5 и на затворе транзистора 49, С приходом импульса синхронизации в момент, когда не окончился импульс на выходе b открывается транзистор 50 и происходит разряд накопительного конденсатора через ограничивающий транзистор 48 и открытые транзисторы 49 и 50. Уровень напряжения в точке п понижается, что при водит к повышению потенциала на выходе дифференциального усилителя, а следовательно, к повышению частоты генерируемых импульсов. Одно.временно с приходом синхроимпульса снимается блокировка со входа с ивыхода cL и генерирование импульсов не прерывается, т.е. когда напряжение в точке d превысит U,,,, происходит переключение триггера и на выходе b устанавливается низкий напряжения, а на выходе tt - вы сокий. Вследствие этого, устанавливаются низкие уровни напряжения в точке е, на затворах транзисторов 35 и 36 и на затворе транзистора 49 Транзистор 49 закрывается, и разряд ный ток конденсатора 32 через цепочку последовательно соединенных транзисторов прекращается. Таким об разом, разрядный ток конденсатора 32 продолжается от прихода синхроимпульса до времени формирования им пульса на выходе Л. Таким образом, предлагаемой син ронизированный импульсный генерато обеспечивает синхронизацию внешним синхроимпульсами, причем частота синхроимпульсов кратна частоте генерируемых импульсов и равна f fr/n г где ff; - частота синхроимпульсов; f. - частота генератора; п -1,2,3.., В рассматриваемом случае п 2 Кроме того, в устройстве осуществляется автоматическая подстро ка частоты генерирования импульсов чтобы обеспечивать равенство fc как в случае, когда fc fj,/n, так и в случае, когда fj, t . Предлагаемый синхронизированный импульсный генератор может найти наиболее широкое применение в устройствах, в которых требуется внешн синхронизация импульсами, частота которых ниже частоты следования генерируемых импульсов. Наличие в генераторе, автоматической подстрой ки периода следования импульсов по воляет изменять частоту импульсов синхронизации в широких пределах, при этом частота генерирования импульсов генератора изменяется синх ронно с частотой синхроимпульсов. Возможность в генераторе изменя количество периодов в каждом перио следования синхроимпульсов значительно расширяет область применения синхронизированного импульсного генератора. По второму вар ианту исполнения (фиг. 3) импульсный генератор состоит из статического триггера на транзисторах 54-59, двух заторможенных мультивибраторов, содержащих инверторы обратной связи, транзисторы 60, 61 и 62, 63 времязадающие транзисторы 64 и 65, времязадающие конденсаторы 66 и 67 и разрядные транзисторы 68 и 69, элемент ИЛИ на дза входа из транзисторов 70-72, запускающего конденсатора 73,.блокирующих транзисторов 74 и 75, двух цепочек формирования сигналов блокировки, каждая из которых содержит последовательно включенные смещающий транзистор 76, 77 и обнуляющий транзистор 78, 79, общей шины 80 и шина 81 питания. Истоки транзисторов 54, 55, 57, 59, 61, 63, 68, 69, 70, 71, 74, 75, 78 и 79 подключены к общей шине 80. Стоки транзисторов 56, 58, 60, 62, 64, 65 и 72, затворы транзисторов 56, 58, 60, 62 и 72 подключены к шине 81 питания. Вход левого плеча триггера .подключен к первому ждущему мультивибратору в точке соединения транзисторов 64 и 68 и через времязадающий конденсатор 66 к выходу инвертора обратной связи на транзисторах 60 и 61, а вход правого плеча триггера аналогичным образом подключен ко второму ждущему мультивибратору. Выход левого плеча триггера подключен к затворам транзисторов 61, 77 и 78, к стоку транзистора 77 и через транзистор 77 - на затворы транзисторов 69 и. 70. Выход правого плеча триггера подключен к транзисторам 63, 76 и 79, к стокам транзисторов 75 и 76 и через транзистор 76 - к затворам транзисторов 68 и 61. Затворы транзисторов 64 и 65 подключены к шине опорного напряжения. Устройство работает следующим образом. При включении питания начинает возрастать напряжение питания (точка А.) . Возрастание напряжения через запускающий конденсатор 73 передается в точку Ь, и когда оно превышает пороговое напряжение МДП-транзйсторов (UQ) блокирующие транзисторы 74 и 75 открываются и блокируют возрастание напряжения на выходе правого плеча триггера (точка d) и на-входе левого плеча триггера (точка k) (время t ) . Когда напряжение источника питания превышает U, начинает возрастать напряжение на выходе левого плеча триггера (точка с) и когда оно превысит UQ, то блокирует

через транзистор 57 выход d (время t). Кроме того, транзистор 78 блок,ирует точку Ь и закрывает разрядный транзистор 68. В это же врем начинает возрастать найряжение в точке ей, когда оно превышает U, открывается транзистор 70 и снимает блокирующий сигнал в точке Ь, что в свою очередь закрывает блокирующие транзисторы 74 и 75 и разрешает заряд времязадающего конденсатора 6 через времязадающий транзистор 64

(время tj). Кроме трго, потенциалом в точке 6 через транзистор 69 блокируется вход правого плеча триггера

(точка п) .

Высокий потенциал на выходе с сохраняется до тех пор, пока напряжение в точке k не превышает U,, после чего напряжение в точке с начнает понижаться, что приводит к повышению напряжения на выходе инвертора обратной связи и через конденсатор 66 на входе k, что, в свою очередь, еще больше понижает напря,жение в точке с (время t ). Устройсво переключается в состояние, когда на выходе U устанавливается высокий уровень напряжения, а на выходе с низкий.

Рассмотрим переходной процесс. Когда уровень напряжения в точке с понижается до U (время tg-) , начинает возрастать напряжения в точке d, и когда оно превышает U (время tg), блокируется выход с транзистором 55. Через транзистор 7 в точке е устанавливается низкий потенциал, что разрешает заряд времязадающего конденсатора 67.

Когда напряжение на выходе d превьЕиает 2 UQ,a в точке L превышае UQ и через транзистор 68 устанавливает в точке k низкий уровень напряжения, через транзистор 70 поддерживается низкий уровень напряжения на выходе элемента ИЛИ (время t). В дальнейшем, когда напряжение в точке п npeBfimiaeT U, происходит переключение устройства в противоположное состояние, т.е. в точке d устанавливается низкий потенциал, а в точке с - высокий, и в симметричных точках устройства происходят процессы, аналогичные описанным выше.

Предлагаемый импульсный генерато на МДП-транзисторах, в отличие от известного, на выходе элемента ИЛИ при включении источника питания вырабатывает блокирующий импульс,, который обеспечивает начало генерации с.опредё.пенной фазы, т.е. при включении источника всегда сначала устанавливается высокий потенциал на выходе с. Кроме того, в предлагаемом генераторе -одновременно повышена устойчивость автоколебательного режима в широком диапазоне частот благодаря введению задержек между началом блокировки выходов с и d и снятия блокировок на входах k и п. Данный импульсный 5 генератор можно применить в качестве задающего генератора различного рода вычислительных и других устройствах, где необходима заданная фазировка задающего генератора, котоQ рая обеспечивает выполнение определенной функции, например обнуление всего устройства. Кроме того, его можно также применить в устройствах, в которых требуется в процессе работы регулировать частоту генерированных импульсов в широком диапазоне частот без изменения параметров.элементов генератора.

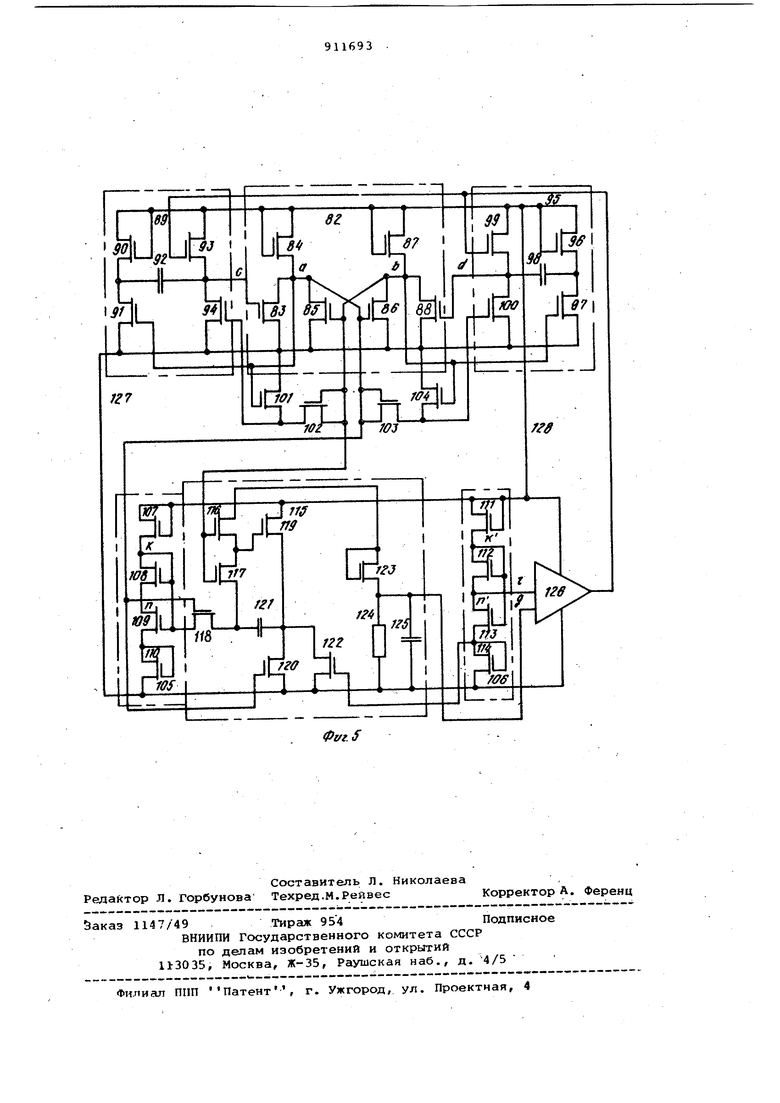

По третьему варианту исполнения (фиг. 5) импульсный генератор соQ .держит триггер 82 на tpaнзиcтopax 83-88, первый ждущий мультивибратор 89, содержащий инверто обратной связи, транзисторы 90 и 91, времязадающий конденсатор 92, времяэадающий

5 транзистор 93 и разрядный транзистор 94, второй ждущий мультивибратор .95, содержащий инвертор обратной связи на транзисторах 96 и 97, времяэадающий конденсатор 98, времяQ задающий транзистор 99 и разрядный транзистор 100. Цепочки формирования разрядных сигналов - на транзисторах 101, 102, 103 и 104. Делители напряжения 105, 106 - на транзисторах

5 107 - 110 и 111 - 114.

Преобразователь 115 частоты-напряжения содержит первый, второй и третий проходные транзисторы 116, 117 и 118, повторяющий транзистор

- 119 истокового повторителя, блокирующий транзистор 120, дозируюЩий конденсатор 121, нагрузочный транзистор 122, смещающий транзистор 123, регулирующий резистор 124, накопительный конденсатор 125 и дифференциальный усилитель 126, общую шину 127 и шину 128 питания.

Импульсный генератор работает след 1ующим образом.

л Рассмотрим работу с момента времени, когда на выходе ct устанавливается высокий потенциал, а на выходе b - низкий, на входе с - низкий и на входе d - высокий. Так как на выходе d. высокий потенциал, то через

транзистор 103 устанавливается высокий потенциал и на затворе разрядного транз 1стора 100, что, в свою очередь, устанавливает низкий уровень на входе d. На выходе b сохраняется

0 низкий потенциал благодаря перекрестным связям статического триггера.. Высоким потенциалом на выходе d. открываются транзисторы 101 и 91 и-устанавливаются низкие потендиеиты

5 на затворе разрядного транзистора 94 и на выходе инвертора положительной обратной связи. Через времязадающий транзистор 93 начинает заряжаться времязадающий конденсато 92 и повышается напряжение в точке с. Когда в точке с напряжение превышает пороговое, начинает понижать ся напряжение в точке cfr,вследствие чего повышается напряжение на выхо це инвертора положительной обратной |связи. Повышение последнего передается через времязадающий конденсато ,92 на ,вход с, в результате происходит лавинный процесс переключения и в точке сС устанавливается низкий уровень напряжения, а в точке b высокий. В дальнейшем через времязадающий транзистор 99 1ачинает заряжаться времязадающий конденсатор 98, повышается напряжение в точке d и, ког да последнее превышает пороговое напряжение транзисторов, происходит переключение генератора в друго состояние, В дгшьнейшем процессы повторяются. При этом длительность импульса йа выходе а определяется временем заряда времязгщающего конденсатора 92 через времязадающий транзистор 93 до напряи ения переклю чения, а длительность, импульса на выходе b определяется временем заря да до напряжения переключения врёмя задающего конденсатора 98 через вре мязадающий транзистор 99. Очевидно, что эти времена определяются напряж нием на затворах времязадающих тран зисторов, которое, в свою очередь, определяется разностью входных напряжений дифференциального усилител (входы с и д). Причем дифференциаль нйй усилитель подключен таким обрйзоМ, что увеличение напряжения на вход g при неизменном напряжении на входе е приводит к уменьшению напря жения на выходе дифференциального усилителя, а следовательно, к понижению частоты генерирования генератора. Напряжение на входе g вырабатывается преобразователем частотынапряжения. При приходе на затворы проходного транзистора 118 и ключевого транзистора 120, дозирующий конденсатор 121 заряжается до напря жения и , определяемого делителем напряжения, и величина заряда в установившемся режиме равна Q -Сс. , где Q. - величина заряда- конденсатора во время действия импульса на выходе а; и, - величина напряжения на делителе напряжения в точках k и k ; С - величина дозирующего кон денсатора. После окончания импульса на выхо де л. и установления высокого уровня на выходе b транзисторы 118 и 120 закрыбаются и открываются проходные транзисторы 11би 117 и часть заряда с дозирующего конденсатора передается на накопительный конденсатор через смещающий транзистор 123. Величина оставшегося заряда на дозирующем конденсаторе, равна QSL Uv Cg, где Q - величина оставшегося заряда На дозирующем конденсаторе в установившемся режиме при действии импульса на выхо, де b ; и - падение напряжения между затвором и истоком транзистора 119 в установившемся режиме. При идентичности размеров транзисторов 110, 114 и 122 токи, протекающие через делители напряжения и истоковый повторитель, равны, и, следовательно, при идентичности транзисторов 108, 112 и 119,напряжения между затворами и истоками этих транзисторов равны. Следовательно, величина заряда, который передается в накопительный конденсатор за один период составляет где Q- величина заряда, переданная в накопительный конденсатор за один период; величина напряжения на делителях в точках п и п . Напряжение на накопительном конденсаторе увеличивается за один период на величину АП Ui2--C9j-. ди де uU - увеличение напряжения на накопительном конденсаторе за один Период; Си величина емкости накопительного конденсатора. Таким образом, напряжение на наопительном конденсаторе возрастает ри каждой передаче заряда. Одновреенно часть заряда накопительного онденсатора стекает- через регулируюий резистор 124 и величина заряда, а который разряжается накопительный онденсатор за один период, составяетдо -Т, величина, на которую разряжается накопительный конденсатор;величина напряжения в точке g ; величина регулирующего резистора;период следования импульсов генератора. Как говорилось выше, повышение апряжения в точке g приводит к пониению частоты генерирования и к увеичению разряда накопительного конденсатора через регулирующий резистор. При большом коэффициенте усиления дифференциального усилител U(j. примерно равно Uj . В установивше ся режиме заряд, переданный из дозирующего конденсатора в накопитель ный за один период, полностью расходуется за счет разрядного тока.ч рез регулирующий резистор, т.е. вы полняется равенство .т, .(1) где Т - период генерирования импул сов/ .из которых следует: UZ-RH-C где f - частота генерирования импульсов. При равенстве UQ и U,, f -1- RhC Как видно из выражения (2), частот генератора определяется только вел чинами дозирующего конденсатора и величиной регулирующего резистора, причем зависимость частоты генерирования прямо пропорциональна пров димости регулирующего резистора и зависит от изменения, параметров времязадающих цепей генератора. При изменении питающего напряжения изменяется U, что приводит к изменению величины передаваемого р ряда в накопительный коиденсатор. Но в установившемся режиме всегда выполняются два условия: .1) и Uj, и-, ( 2) Л ifчто приводит к выражению (2), т.е. при большом коэффициенте усиления дифференцисШьного усилителя, при изменении питающего напряжения, частота в установившемся режиме практически не изменяется. Так как изменение температуры окружающей среды приводит к измене нию параметров времязадающих транзисторов и конденсаторов, то, исхо из выражения (2), частота генериро вания не изменяется при изменении температуры окружающей среды. Таким образом, предлагаемый генеЬатор имеет то преимущество, что его частота практически не зависит от изменения питающих напряжений, температуры окружающей среды и изменения параметров времязадающих элементов устройства, что позволяе применять данные генераторы в широ ком диапазоне изменяющихся напряже ний питания и температуры окружающей среды и при этом получать высо кую стабильность частоты. Кроме то го, при проектировании данног р генератора не нужно предъявлять высо ких требований к технологическому разбросу и стабильности параметров времязадающих элементов, что, в свою очередь, при использовании устройства в интегральных схемах, позволяет значительно повысить процент выхода годных микросхем. Формула изобретения 1. Импульсный генератор, содержащий статический триггер и два заторможенных мультивибратора, каждый из которых содержит инвертор обратной связи, времязадающий конденсатор, времязадающий транзистор и разрядный транзистору- выходом подключенных к соответствующим входам триггера, отличающийс-я тем, что, с целью расширения функциональных возможностей, в него дополнительно введены устройство выделения последнего периода, делитель напряжения, дифференциальный усили- / тель, устройство запуска, устройство вьшеления сигналов рассогласования и параллельно соединенные разрядный резистор и накопительный конденсатор, причем устройство запуска содержит два блокирующих транзистора и две цепочки, состоящих из двух последовательно включенных транзисторов, а устройство выделения сигналов рассогласования содержит два двухтактных усилителя, состоящих из повторяющего и инвертирующего транзисторов, первую цепочку,из , четырех последовательно включенных транзисторов, элемент ИЛИ на два входа с запомингиощим конденсатором между затвором и истоком нагрузочного транзистора, один из входов элемента ИЛИ подключен к шине синхронизации и затворам нижних транзисторов первой цепочки устройства запуска и цепочки устройства выделения сигналов рассогласования, второй вход элемента ИЛИ подключен ко входу устройства выделения последнего периода к выходу правого, плеча триггера и к затворам повторяющего транзистора второго двухтактного усилителя и верхнего транзистора второй цепочки устройства запуска, второй вход устройства выделения последнего периода подключен к выходу левого плеча триггера и к затворам инвертирующих транзисторов двухтактных усилителей и нижнего транзистора второй цепочки устройства запуска, выход первой цепочки устройства запуска подключен к затворам первого и второго блокирующих транзисторов, которые соответственно включены между входом левого пл,еча триггера и общей шиной и между выходом левого плеча триггера и общей шиной, выход второй цепочки подключен к затворам верхнего транзистора первой цепочки и повторяющего транэистора первого двухтактного усилителя, выход первого двухтактного усилителя подключен к затвору среднего транзистора цепочки устройства вьаделения сигналов рассогласования, выход второго двухтактного усилителя подключен к затвору нагрузочного транзистора элемента ИЛИ, выход элемента ИЛИ подключенк затвору верхнего транзистора цепочки устройства выделения сигналов рассогласования , а выход этой цепочки подключен к соединения разрядного резистора, накопительного конденсатора и к одному из входов дифференциального усилителя, второй вход дифференциального усилителя подключен к делению напряжения, а выход дифференциального усилителя- подключен к затворам времязадающих транзисторов, выход устройства, выделения последнего периода подключен к стокам повторяющего транзистора второго двухтактного усилителя и верхнего транзистора второй цепочки устройства запуска.

2. Импульсный генератор, содержащий статический триггер и два заторможенных мультивибратора; каждый из которых содержит инвертор обратной связи, времязадающий конденсатор, времязадающий транзистор и разрядный транзистор, выходом подключенных к соответствующим входам триггера, отличающийс я тем, что, с целью расширения функциональных возможностей, в него дополнительно введены элемент ИЛИ, запускающий конденсатор, включенный между выходом элемента ИЛИ и шиной питания, два дополнительных блокирующих транзистора и две цепочки формирования сигналов блокировки, каждая из которых включена между одним из выходов триггера и общей шиной, и состоящих из последовательно включенных смещающего и обнуляющего транзисторов, соедийенных с затворами разрядных транзисторов заторможенных мультивибраторов и со входом элемента ИЛИ,причем затвор и сток смещающего транзистора цепочки Формирования сигналов бJfIoкиpoвки подключены к одному из выходов триггера, а затвор обнуляющего транзистора этой цепочки подключен к другому выходу триггера, выход элемента ИЛИ подключен к затворам дополнительных

блокирующих транзисторов, один из которых включен между одним из выходов триггера и общей шиной, а другой - между противоположным этому выходу входом триггера и общей шие НОЙ.

3. импульсный генератор, .содержащий статический триггер и два заторможенных мультивибратора, каждый из которых содержит инвертор обратQ ной связи, времязадающий конденсатор, времязадающий транзистор и разрядный транзистор, выходом подключенных к соответствующим входам т риггера, о тличающийся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены вторая цепочка из четырех последовательно включенных транзисторов, и преобразователь частоты-напряжения, содержащий истоковый повторитель,

0 три проходных .транзистора, блокирующий транзистор, смещающий транзистор, дозирующий конденсатор, накопительный конденсатор и регулирующий резистор, причем сток и затвор

5 смещающего транзистора подключены к истоку первого проходного транзистора, сток которого подключен к затвору повторяющего транзистора истокового повторителя и к истоку

Q второго проходного транзистора,сток второго проходного транзистора через дозирующий конденсатор подключен к выходу истокового повторителя, а через третий проходной транзистор - к вьЛходу второй цепочки

5 из четырех последовательно включенных транзисторов между выходом истокового повторителя и общей шиной подключены нагрузочный и блокирующий транзисторы, причем затвор нагрузочного транзистора подключен к выходу цепочки из четырех последовательно включенных транзисторов/ затворы первого и второго проходных транзисторов подключены к одному из выходов триггера, а затворы третьего . проходного и блокирующего транзисторов подключены ко второму выходу триггера.

Источники информации,

п принятые во внимание при экспертизе

1.Патент США № 4066328, кл. Н 03 К 3/28, 31.01.78.

2.Авторское свидетельство СССР № 570185, кл. Н 03 К 3/281,28.04.77 (прототип)i

Vo ,., I- Л . I

l/ff I I I т / , niH П Г J --H.I|, ---,A - - - - I f -4 M г f r I I I I ЯП П П hi f I I I I,1iP,II

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования импульсов на МДП-транзисторах | 1986 |

|

SU1345339A1 |

| Квазистатическое счетное устройство на МДП-транзисторах | 1986 |

|

SU1319255A1 |

| Емкостное накопительное устройство | 1975 |

|

SU555540A1 |

| Генератор импульсов | 1975 |

|

SU570185A1 |

| Стабилизатор постоянного напряжения | 1975 |

|

SU547747A1 |

| Формирователь импульсов регенерации для запоминающих устройств на мдп-транзисторах | 1974 |

|

SU500581A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| СТАБИЛИЗИРОВАННЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 2011 |

|

RU2474948C1 |

| Синхронизированный генератор импульсов | 1980 |

|

SU894846A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

Авторы

Даты

1982-03-07—Публикация

1980-06-02—Подача