Изобретение относится к области радиотехники и может быть использовано в качестве малошумящего устройства усиления аналоговых сигналов, в структуре аналоговых интерфейсов различного функционального назначения, в т.ч. работающих в широком диапазоне температур и воздействия радиации.

Известны схемы классических операционных усилителей (ОУ), содержащие так называемый двухтактный «перегнутый» каскод, включающий два «перегнутых» каскода на полевых транзисторах с p и n каналами, нагруженные друг на друга и имеющих общий высокоимпедансный узел [1-11]. Это одна из наиболее популярных схем ОУ в аналоговой микроэлектронике. При этом входные каскады таких ОУ выполняются в рамках десятков различных схемотехнических решений [1-11].

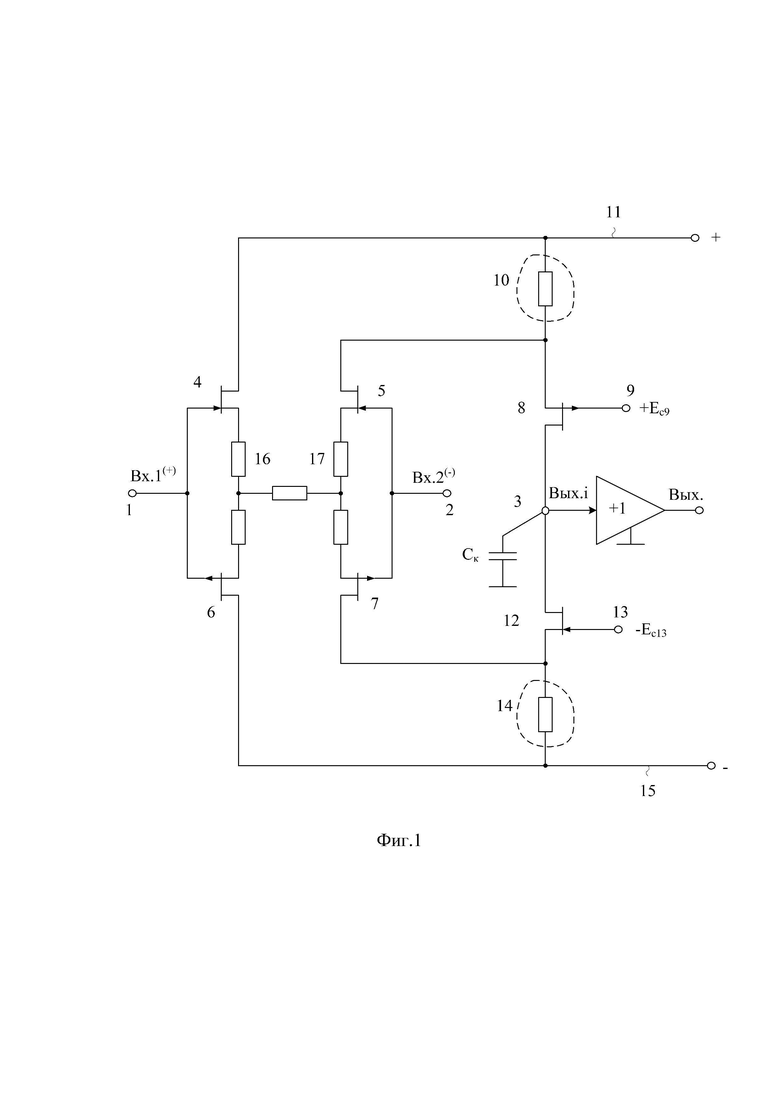

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель на основе двухтактного «перегнутого» каскода, представленный в статье Dimitri Danyuk "Linear Integrated Systems Headphone Amplifier Evaluation Board", Linear Integrated Systems, p. 1-17, URL: http://www.linearsystems.com/lsdata/others/ Headphone_Amplifier_Evaluation_Board.pdf. Он содержит первый 1 и второй 2 входы устройства, токовый выход 3 устройства, первый 4, второй 5, третий 6 и четвертый 7 входные полевые транзисторы, первый 8 выходной полевой транзистор, затвор которого связан с первым 9 источником напряжения смещения, сток подключен к токовому выходу 3 устройства, а исток соединен со стоком второго 5 входного полевого транзистора и через первый 10 токостабилизирующий двухполюсник соединен с первой 11 шиной источника питания, второй 12 выходной полевой транзистор, затвор которого связан со вторым 13 источником напряжения смещения, сток подключен к токовому выходу 3 устройства, а исток соединен со стоком четвертого 7 входного полевого транзистора и через второй 14 токостабилизирующий двухполюсник соединен со второй 15 шиной источника питания, затвор первого 4 входного полевого транзистора соединен с первым 1 входом устройства, а его сток согласован с первой 11 шиной источника питания, затвор второго 5 входного полевого транзистора связан со вторым 2 входом устройства, сток третьего 6 входного полевого транзистора согласован со второй 15 шиной источника питания, первый 16 и второй 17 вспомогательные резисторы.

Существенный недостаток известного ОУ фиг. 1 состоит в том, что он имеет повышенную входную емкость, что отрицательно сказывается на работе схемы в диапазоне высоких частот. Кроме этого в нем не обеспечиваются малые значения систематической составляющей напряжения смещения нуля (Uсм), что обусловлено недостатками его архитектуры.

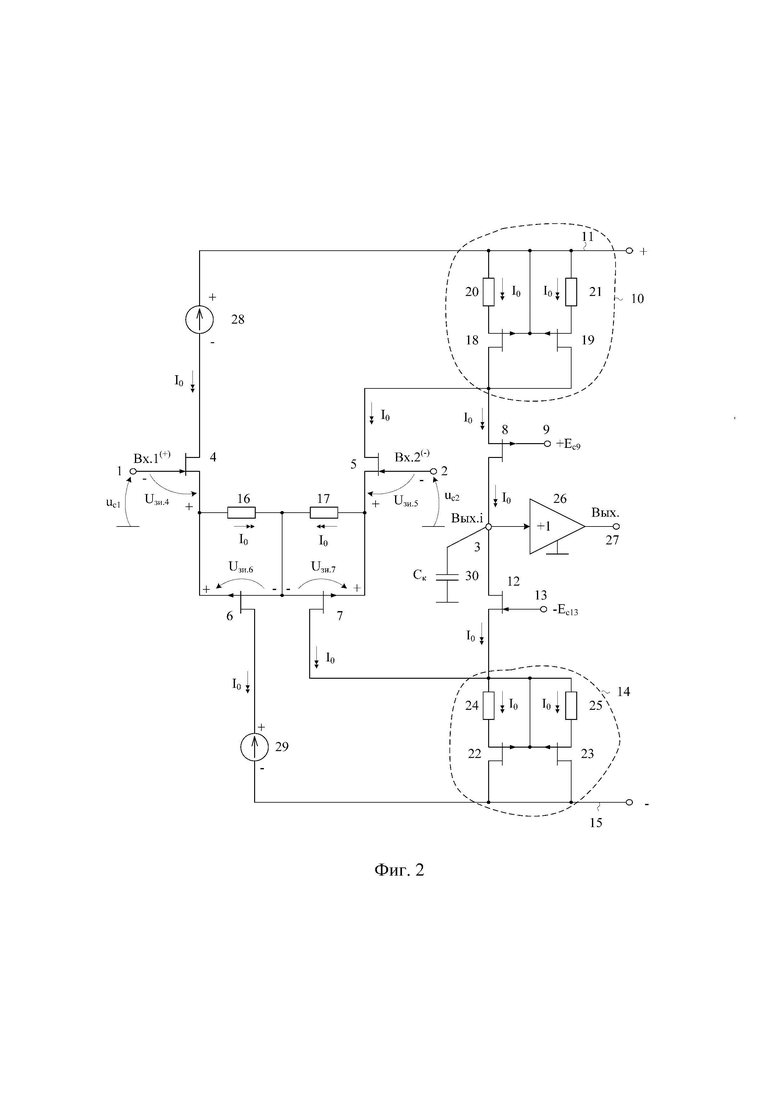

Основная задача предполагаемого изобретения состоит в создании условий, при которых в ОУ уменьшается в два раза входная емкость (за счет этого обеспечивается расширенный диапазон рабочих частот), а также реализуются малые значения систематической составляющей напряжения смещения нуля (Uсм), которая определяется симметрией и качеством схемотехнического решения ОУ при его «идеальном» построении, и в этом случае близка к нулю. При этом положительный эффект в схеме фиг. 2 обеспечивается за счет специального построения входного дифференциального каскада ОУ и двухтактного «перегнутого» каскода в соответствии с формулой изобретения.

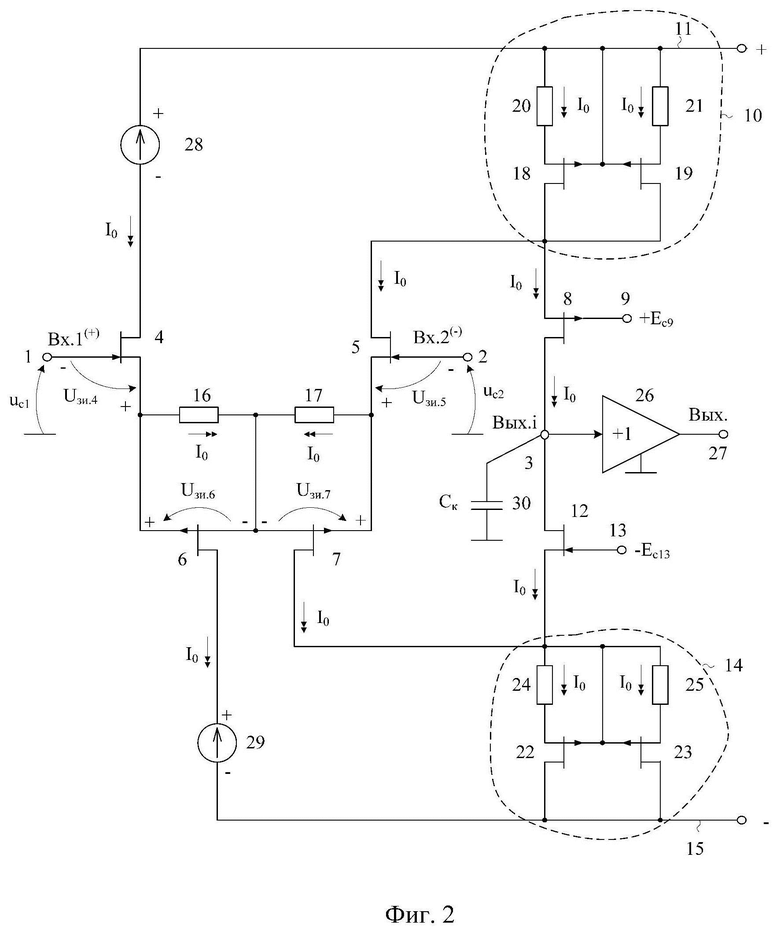

Поставленная задача решается тем, что в ОУ фиг. 1, содержащем первый 1 и второй 2 входы устройства, токовый выход 3 устройства, первый 4, второй 5, третий 6 и четвертый 7 входные полевые транзисторы, первый 8 выходной полевой транзистор, затвор которого связан с первым 9 источником напряжения смещения, сток подключен к токовому выходу 3 устройства, а исток соединен со стоком второго 5 входного полевого транзистора и через первый 10 токостабилизирующий двухполюсник соединен с первой 11 шиной источника питания, второй 12 выходной полевой транзистор, затвор которого связан со вторым 13 источником напряжения смещения, сток подключен к токовому выходу 3 устройства, а исток соединен со стоком четвертого 7 входного полевого транзистора и через второй 14 токостабилизирующий двухполюсник соединен со второй 15 шиной источника питания, затвор первого 4 входного полевого транзистора соединен с первым 1 входом устройства, а его сток согласован с первой 11 шиной источника питания, затвор второго 5 входного полевого транзистора связан со вторым 2 входом устройства, сток третьего 6 входного полевого транзистора согласован со второй 15 шиной источника питания, первый 16 и второй 17 вспомогательные резисторы, предусмотрены новые элементы и связи – исток первого 4 входного полевого транзистора связан с затвором третьего 6 входного полевого транзистора и через первый 16 вспомогательный резистор соединен с истоком третьего 6 входного полевого транзистора, исток второго 5 входного полевого транзистора соединен с затвором четвертого 7 входного полевого транзистора, и через второй 17 вспомогательный резистор соединен с объединенными истоками первого 6 и второго 7 входных полевых транзисторов, первый токостабилизирующий двухполюсник 10 содержит первый 18 и второй 19 дополнительные полевые транзисторы, затворы которых подключены к первой 11 шине источника питания, стоки объединены и соединены с истоком второго 8 выходного полевого транзистора, причем исток первого 18 дополнительного полевого транзистора соединен с первой 11 шиной источника питания через первый 20 дополнительный резистор, а исток второго 19 дополнительного полевого транзистора подключен к первой 11 шине источника питания через второй 21 дополнительный резистор, второй 14 токостабилизирующий двухполюсник содержит третий 22 и четвертый 23 дополнительные полевые транзисторы, затворы которых подключены к истоку второго 12 выходного полевого транзистора, стоки объединены и подключены ко второй 15 шине источника питания, причем исток третьего 22 дополнительного полевого транзистора соединен с истоком второго 12 выходного полевого транзистора через третий 24 дополнительный резистор, а исток четвертого 23 дополнительного полевого транзистора подключен к истоку второго 12 выходного полевого транзистора через четвертый 25 дополнительный резистор.

На чертеже фиг. 1 приведена схема ОУ-прототипа, а на чертеже фиг. 2 представлена схема заявляемого устройства в соответствии с п. 1, п. 2 и п. 3 формулы изобретения.

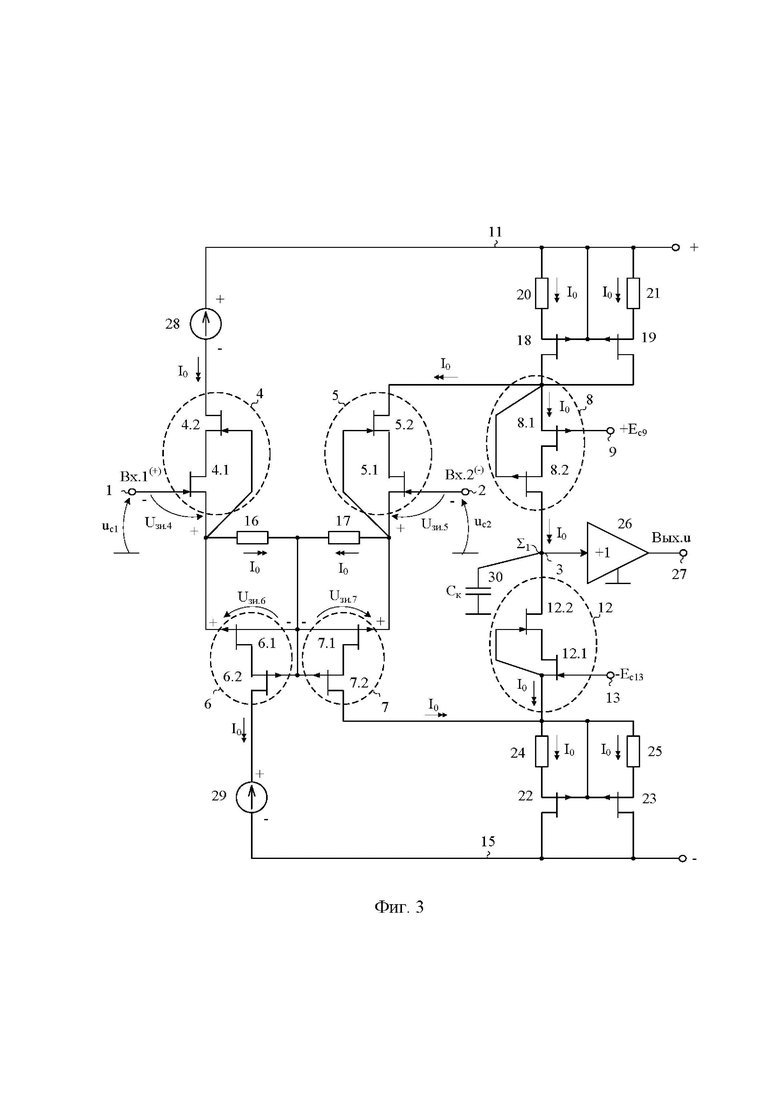

На чертеже фиг. 3 представлена схема заявляемого устройства в соответствии с п. 4 формулы изобретения.

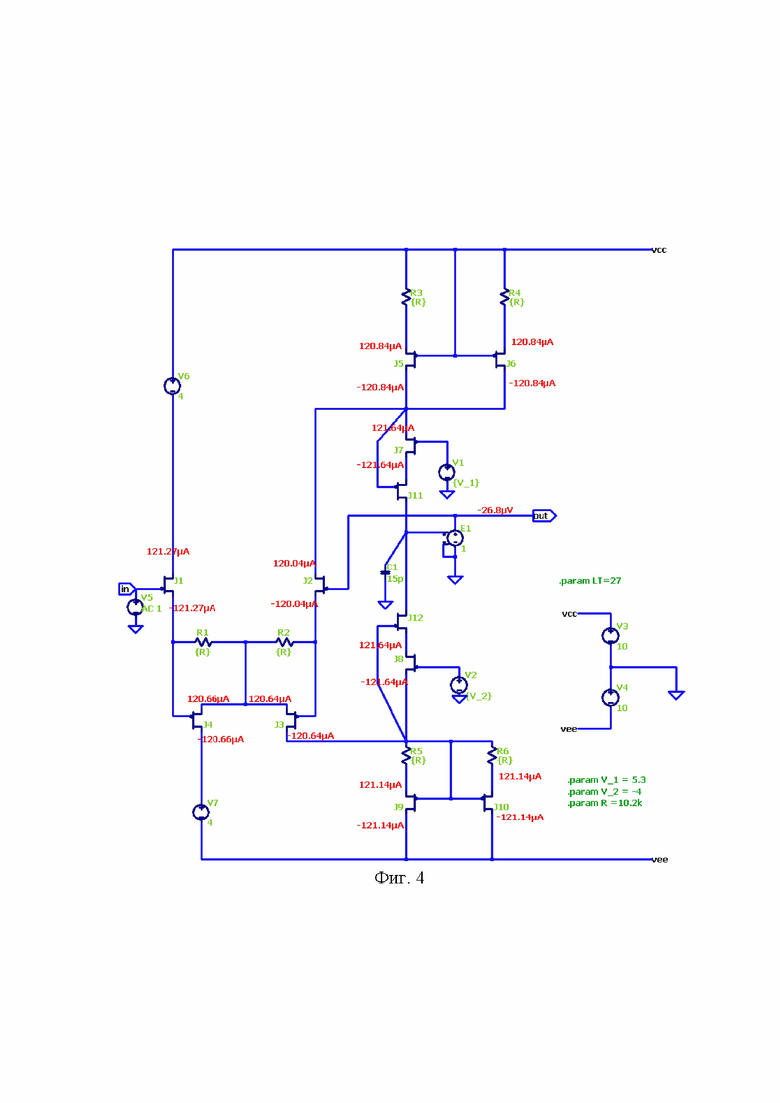

На чертеже фиг. 4 показана схема для моделирования операционного усилителя фиг. 2 в среде LTspice на моделях Si полевых транзисторах ОАО «Интеграл» (г. Минск) при комнатной температуре t=27°С, R1÷R6=10,2 кОм (R16=R17=R20=R21=R24=R25, см. фиг. 2), напряжениях на первом 28 и втором 29 вспомогательных двухполюсников 4 В, напряжении первого 9 источника напряжения смещения 5,3 В, напряжении второго (13) источника напряжения смещения -4 В, емкости корректирующего конденсатора (30) – 15 пФ, напряжениях на первой 11 и второй 15 шинах источников питания ±10 В.

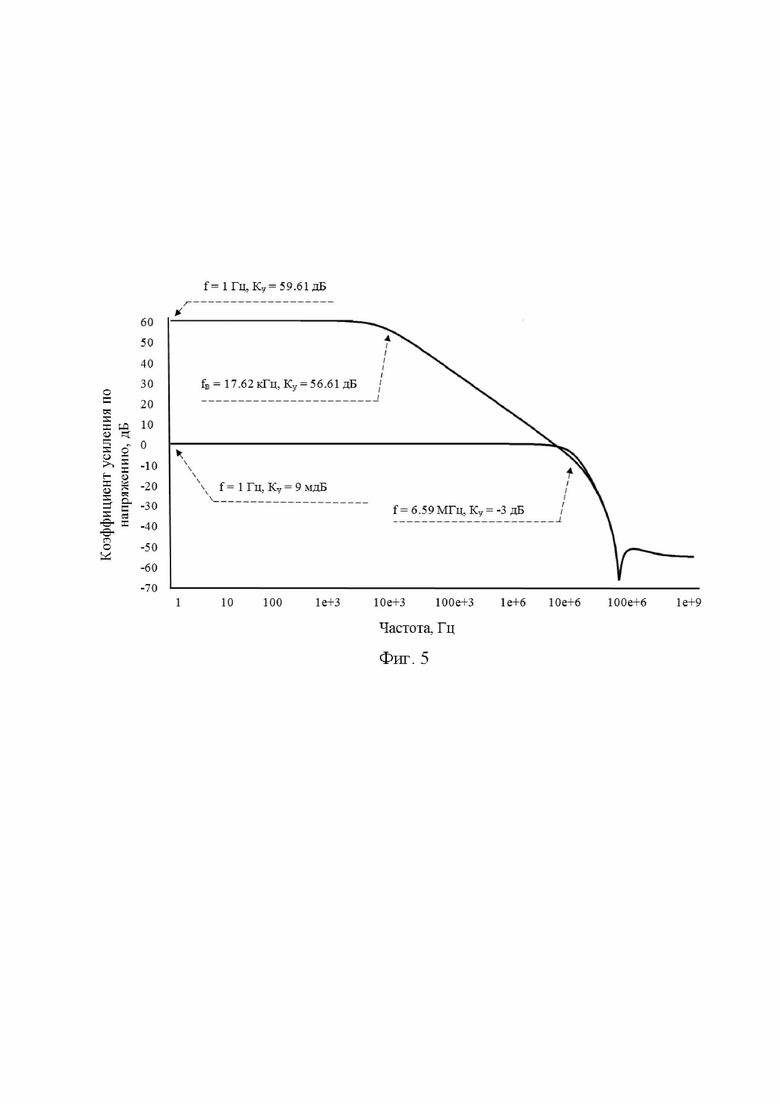

На чертеже фиг. 5 приведена логарифмическая амплитудно-частотная характеристика (ЛАЧХ) ОУ фиг. 4 при комнатной температуре t = 27°С.

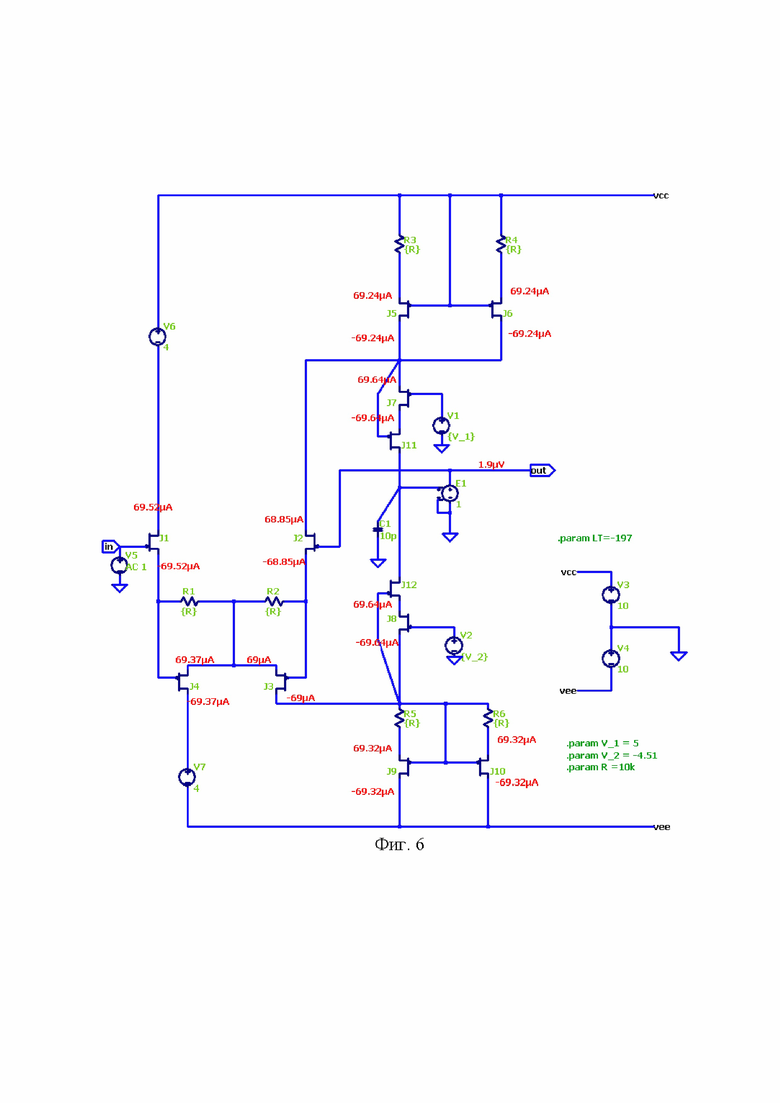

На чертеже фиг. 6 показана схема для моделирования операционного усилителя фиг.2 при криогенных температурах (t = -197°С), R1÷R6=10 кОм (R16=R17=R20=R21=R24=R25, см. фиг. 2), напряжении первого 9 источника напряжения смещения 5 В, напряжении второго 13 источника напряжения смещения -4.51 В, емкости корректирующего конденсатора (30) – 10 пФ на моделях Si полевых транзисторах ОАО «Интеграл» (г. Минск).

На чертеже фиг. 7 представлена ЛАЧХ ОУ фиг. 6 при криогенных температурах (t = -197°С).

Операционный усилитель на основе двухтактного «перегнутого» каскода и комплементарных полевых транзисторов с управляющим pn–переходом фиг. 2 содержит первый 1 и второй 2 входы устройства, токовый выход 3 устройства, первый 4, второй 5, третий 6 и четвертый 7 входные полевые транзисторы, первый 8 выходной полевой транзистор, затвор которого связан с первым 9 источником напряжения смещения, сток подключен к токовому выходу 3 устройства, а исток соединен со стоком второго 5 входного полевого транзистора и через первый 10 токостабилизирующий двухполюсник соединен с первой 11 шиной источника питания, второй 12 выходной полевой транзистор, затвор которого связан со вторым 13 источником напряжения смещения, сток подключен к токовому выходу 3 устройства, а исток соединен со стоком четвертого 7 входного полевого транзистора и через второй 14 токостабилизирующий двухполюсник соединен со второй 15 шиной источника питания, затвор первого 4 входного полевого транзистора соединен с первым 1 входом устройства, а его сток согласован с первой 11 шиной источника питания, затвор второго 5 входного полевого транзистора связан со вторым 2 входом устройства, сток третьего 6 входного полевого транзистора согласован со второй 15 шиной источника питания, первый 16 и второй 17 вспомогательные резисторы. Исток первого 4 входного полевого транзистора связан с затвором третьего 6 входного полевого транзистора и через первый 16 вспомогательный резистор соединен с истоком третьего 6 входного полевого транзистора, исток второго 5 входного полевого транзистора соединен с затвором четвертого 7 входного полевого транзистора, и через второй 17 вспомогательный резистор соединен с объединенными истоками первого 6 и второго 7 входных полевых транзисторов, первый токостабилизирующий двухполюсник 10 содержит первый 18 и второй 19 дополнительные полевые транзисторы, затворы которых подключены к первой 11 шине источника питания, стоки объединены и соединены с истоком второго 8 выходного полевого транзистора, причем исток первого 18 дополнительного полевого транзистора соединен с первой 11 шиной источника питания через первый 20 дополнительный резистор, а исток второго 19 дополнительного полевого транзистора подключен к первой 11 шине источника питания через второй 21 дополнительный резистор, второй 14 токостабилизирующий двухполюсник содержит третий 22 и четвертый 23 дополнительные полевые транзисторы, затворы которых подключены к истоку второго 12 выходного полевого транзистора, стоки объединены и подключены ко второй 15 шине источника питания, причем исток третьего 22 дополнительного полевого транзистора соединен с истоком второго 12 выходного полевого транзистора через третий 24 дополнительный резистор, а исток четвертого 23 дополнительного полевого транзистора подключен к истоку второго 12 выходного полевого транзистора через четвертый 25 дополнительный резистор.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, токовый выход 3 устройства соединен со входом буферного усилителя 26, выход которого 27 является потенциальным выходом устройства.

Кроме этого, на чертеже фиг. 2, в соответствии с п. 3 формулы изобретения, сток первого 4 входного полевого транзистора согласован с первой 11 шиной источника питания через первый 28 вспомогательный двухполюсник, а сток третьего 6 входного полевого транзистора согласован со второй 15 шиной источника питания через второй 29 вспомогательный двухполюсник.

На чертеже фиг. 3, в соответствии с п. 4 формулы изобретения, первый 4, второй 5, третий 6 и четвертый 7 входные полевые транзисторы, а также первый 8 и второй 12 выходные полевые транзисторы, выполнены как каскодные составные транзисторы по классическим схемам (4.1, 4.2), (5.1, 5.2), (6.1, 6.2), (7.1, 7.2), (8.1, 8.2) (12.1, 12.2).

Устойчивость ОУ фиг. 2 и фиг. 3 обеспечивается корректирующим конденсатором 30.

Рассмотрим работу ОУ фиг. 2.

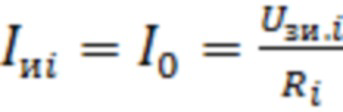

В статическом режиме, например, при подключении первого 1 и второго 2 входов ОУ фиг. 2 к общей шине источников питания, статические токи истоков первого 4, второго 5, третьего 6 и четвертого 7 входных полевых транзисторов, а также первого 18, второго 19 и третьего 22 дополнительных полевых транзисторов определяются численными значениями идентичных сопротивлений первого 16 и второго 17 вспомогательных резисторов, а также первого 20, второго 21, третьего 24 и четвертого 25 дополнительных резисторов:

, (1)

, (1)

где Iиi – ток истока i-го полевого транзистора;

Uзи.i – напряжение затвор-исток соответствующих полевых транзисторов в рабочей точке при токе истока, равном I0;

Ri – идентичные сопротивления соответствующих вспомогательных и дополнительных резисторов (18, 19, 22, 16, 17, 20, 21, 24, 25).

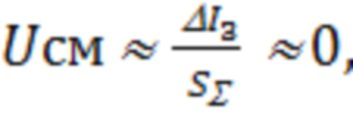

Таким образом, в схеме фиг. 2 за счет выбора одинаковыми сопротивлений первого 16 и второго 17 вспомогательных резисторов, первого 20, второго 21, третьего 24 и четвертого 25 дополнительных резисторов при идентичных стоко-затворных характеристиках третьего 6 и четвертого 7 входных полевых транзисторов, первого 18, второго 19 и третьего 22 и четвертого 23 дополнительных полевых транзисторов обеспечивается идентичный статический режим по току стока. Это является необходимым условием минимизации систематической составляющей напряжения смещения нуля Uсм операционного усилителя, так как в этом случае токовая ошибка в высокоимпедансном узле 3 (ΔI3) близка к нулю:

(2)

(2)

где SΣ - крутизна усиления ОУ со входов 1 и 2 устройства к токовому выходу 3.

Данный вывод подтверждается результатами компьютерного моделирования на чертежах фиг.4 и фиг.6, из которых следует, что систематическая составляющая напряжения смещения нуля (без учета разбросов параметров элементов) равна 26.8 мкВ (при t = 27 градусов), и 1.9 мкВ (при t = -197 градусов). Данный эффект обеспечивается за счет специального построения схемы предлагаемого ОУ.

Расширение частотного заявляемого ОУ обусловлено тем, что со входами 1 (2) устройства связан затвор только одного полевого транзистора 4 (5), т.е. эквивалентная входная емкость в заявляемой схеме ОУ в два раза меньше, чем в схеме ОУ прототипа фиг.1.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом, что позволяет рекомендовать его для практического использования в аналоговых интерфейсах, содержащих, например, полевые транзисторы с управляющим pn- переходом или КМОП транзисторы со встроенным каналом, которые имеют похожие вольт-амперные характеристики в сравнении с JFET.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 2005/0128000, fig.1, 2005 г.

2. Патент US 4.600.893, fig.3, 1986 г.

3. Патент US 4.284.959, fig.3, 1981 г.

4. Патент US 4783637, fig.2, 1988 г.

5. Патент US 5.729.177, fig.1, 1988 г.

6. Патент RU 2331966, fig.1, 2008 г.

7. Патент RU 2517699, fig.1, 2012 г.

8. Патент US 4.837.523, fig.4, 1989 г.

9. Патент RU 2193273, fig.1, 2002 г.

10. Патент US 3569848, fig.8, 1971 г.

11. Эннс В.И., Кобзев Ю.М. Проектирование аналоговых КМОП-микросхем. Краткий справочник разработчика / Под редакцией канд. техн. наук В. И. Эннса. – М.: Горячая линия–Телеком. – 2005. – С. 207, fig. 3.81.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

| НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ ТОКА КЛАССА "АВ" | 2022 |

|

RU2783042C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

Изобретение относится к области радиотехники. Технический результат: создание условий, при которых в ОУ уменьшается в два раза входная емкость, а также реализуются малые значения систематической составляющей напряжения смещения нуля. Для этого предложен операционный усилитель на основе двухтактного «перегнутого» каскода и комплементарных полевых транзисторов с управляющим pn–переходом, в котором исток первого (4) входного полевого транзистора связан с затвором третьего (6) входного полевого транзистора и через первый (16) вспомогательный резистор соединен с истоком третьего (6) входного полевого транзистора, исток второго (5) входного полевого транзистора соединен с затвором четвертого (7) входного полевого транзистора и через второй (17) вспомогательный резистор соединен с объединенными истоками первого (6) и второго (7) входных полевых транзисторов. 3 з.п. ф-лы, 7 ил.

1. Операционный усилитель на основе двухтактного «перегнутого» каскода и комплементарных полевых транзисторов с управляющим pn–переходом, содержащий первый (1) и второй (2) входы устройства, токовый выход (3) устройства, первый (4), второй (5), третий (6) и четвертый (7) входные полевые транзисторы, первый (8) выходной полевой транзистор, затвор которого связан с первым (9) источником напряжения смещения, сток подключен к токовому выходу (3) устройства, а исток соединен со стоком второго (5) входного полевого транзистора и через первый (10) токостабилизирующий двухполюсник соединен с первой (11) шиной источника питания, второй (12) выходной полевой транзистор, затвор которого связан со вторым (13) источником напряжения смещения, сток подключен к токовому выходу (3) устройства, а исток соединен со стоком четвертого (7) входного полевого транзистора и через второй (14) токостабилизирующий двухполюсник соединен со второй (15) шиной источника питания, затвор первого (4) входного полевого транзистора соединен с первым (1) входом устройства, а его сток связан с первой (11) шиной источника питания, затвор второго (5) входного полевого транзистора связан со вторым (2) входом устройства, сток третьего (6) входного полевого транзистора согласован со второй (15) шиной источника питания, первый (16) и второй (17) вспомогательные резисторы, отличающийся тем, что исток первого (4) входного полевого транзистора связан с затвором третьего (6) входного полевого транзистора и через первый (16) вспомогательный резистор соединен с истоком третьего (6) входного полевого транзистора, исток второго (5) входного полевого транзистора соединен с затвором четвертого (7) входного полевого транзистора и через второй (17) вспомогательный резистор соединен с объединенными истоками первого (6) и второго (7) входных полевых транзисторов, первый токостабилизирующий двухполюсник (10) содержит первый (18) и второй (19) дополнительные полевые транзисторы, затворы которых подключены к первой (11) шине источника питания, стоки объединены и соединены с истоком второго (8) выходного полевого транзистора, причем исток первого (18) дополнительного полевого транзистора соединен с первой (11) шиной источника питания через первый (20) дополнительный резистор, а исток второго (19) дополнительного полевого транзистора подключен к первой (11) шине источника питания через второй (21) дополнительный резистор, второй (14) токостабилизирующий двухполюсник содержит третий (22) и четвертый (23) дополнительные полевые транзисторы, затворы которых подключены к истоку второго (12) выходного полевого транзистора, стоки объединены и подключены ко второй (15) шине источника питания, причем исток третьего (22) дополнительного полевого транзистора соединен с истоком второго (12) выходного полевого транзистора через третий (24) дополнительный резистор, а исток четвертого (23) дополнительного полевого транзистора подключен к истоку второго (12) выходного полевого транзистора через четвертый (25) дополнительный резистор.

2. Операционный усилитель на основе двухтактного «перегнутого» каскода и комплементарных полевых транзисторов с управляющим pn–переходом по п.1, отличающийся тем что, токовый выход (3) устройства соединен с входом буферного усилителя (26), выход которого (27) является потенциальным выходом устройства.

3. Операционный усилитель на основе двухтактного «перегнутого» каскода и комплементарных полевых транзисторов с управляющим pn–переходом по п.1, отличающийся тем, что сток первого (4) входного полевого транзистора связан с первой (11) шиной источника питания через первый (28) вспомогательный двухполюсник, а сток третьего (6) входного полевого транзистора связан со второй (15) шиной источника питания через второй (29) вспомогательный двухполюсник.

4. Операционный усилитель на основе двухтактного «перегнутого» каскода и комплементарных полевых транзисторов с управляющим pn–переходом по п.1, отличающийся тем, что первый (4), второй (5), третий (6) и четвертый (7) входные полевые транзисторы, а также первый 8 и второй 12 выходные полевые транзисторы выполнены как каскодные составные транзисторы (4.1, 4.2), (5.1, 5.2), (6.1, 6.2), (7.1, 7.2), (8.1, 8.2) (12.1, 12.2).

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2592455C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2604684C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2592429C1 |

| US 4600893 A1, 15.07.1986. | |||

Авторы

Даты

2022-09-21—Публикация

2022-02-08—Подача