Изобретение относится к вычислительной технике и может быть использовано при построении сетей ЭВМ с синхронными каналами передачи данных Цель изобретения - уменьшение аппаратурных затрат.

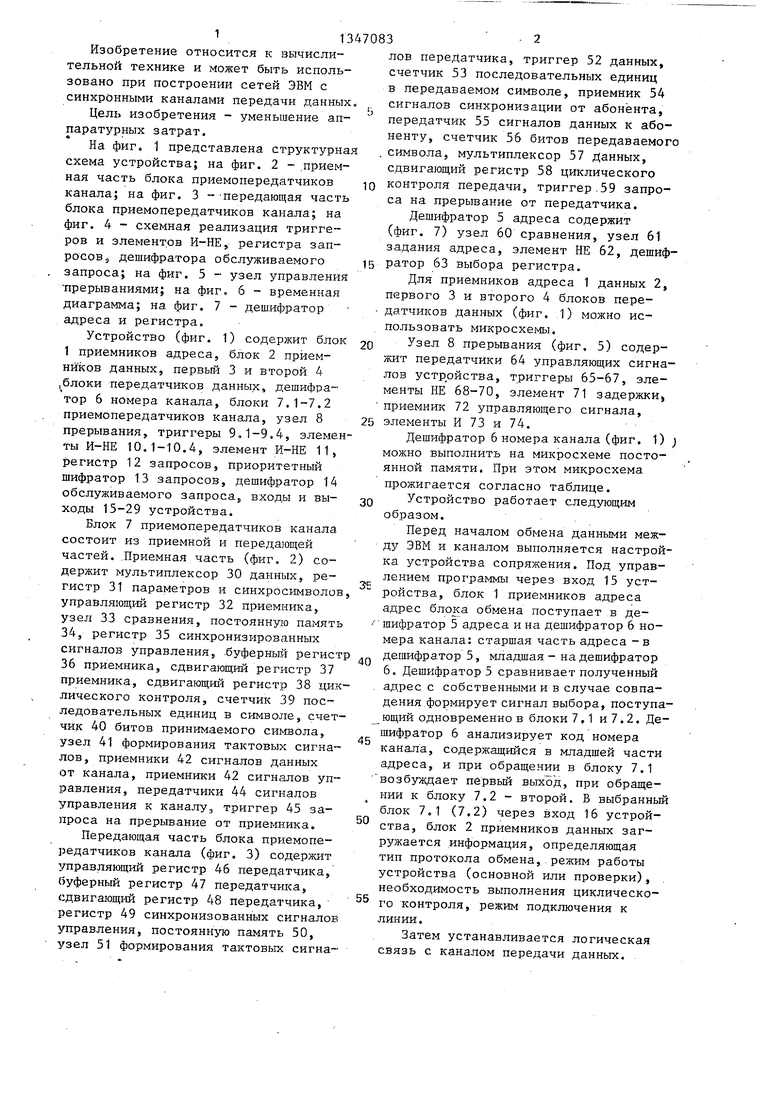

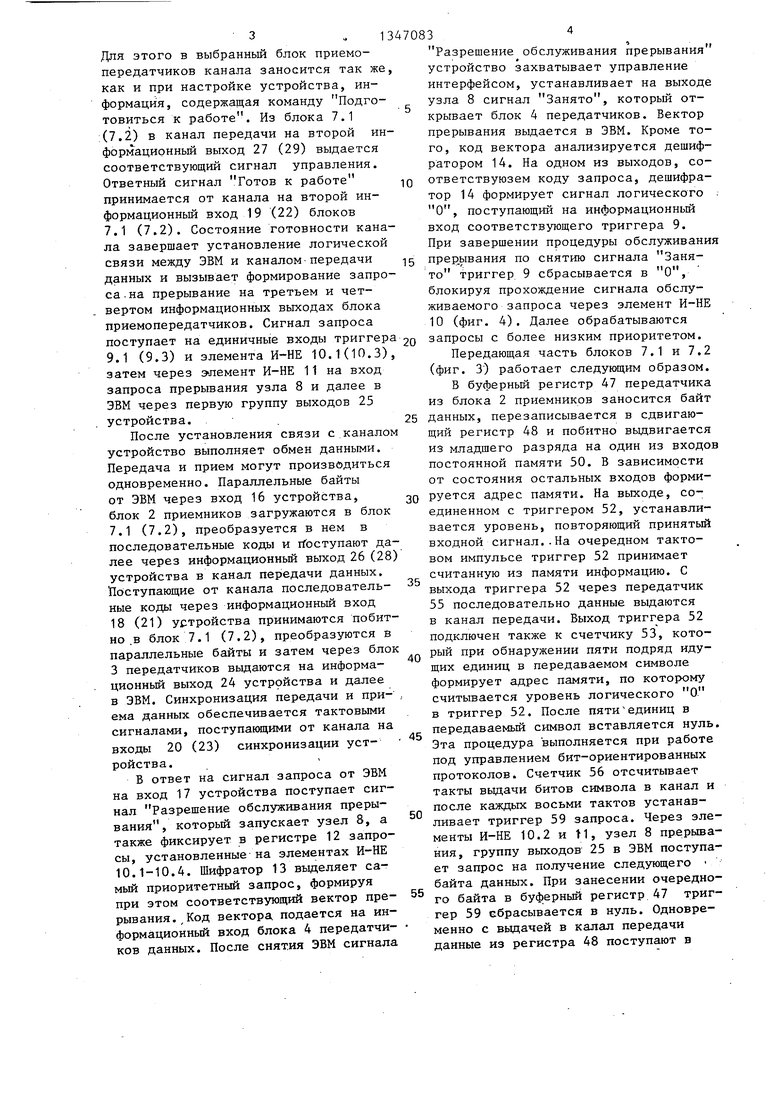

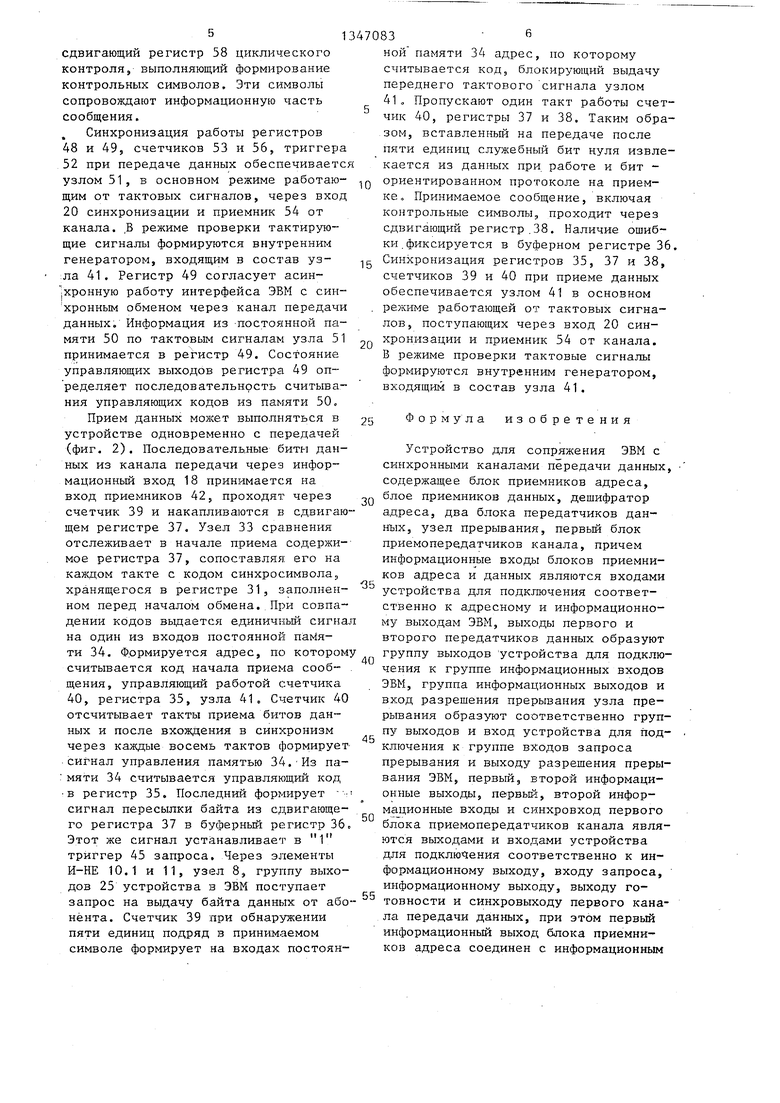

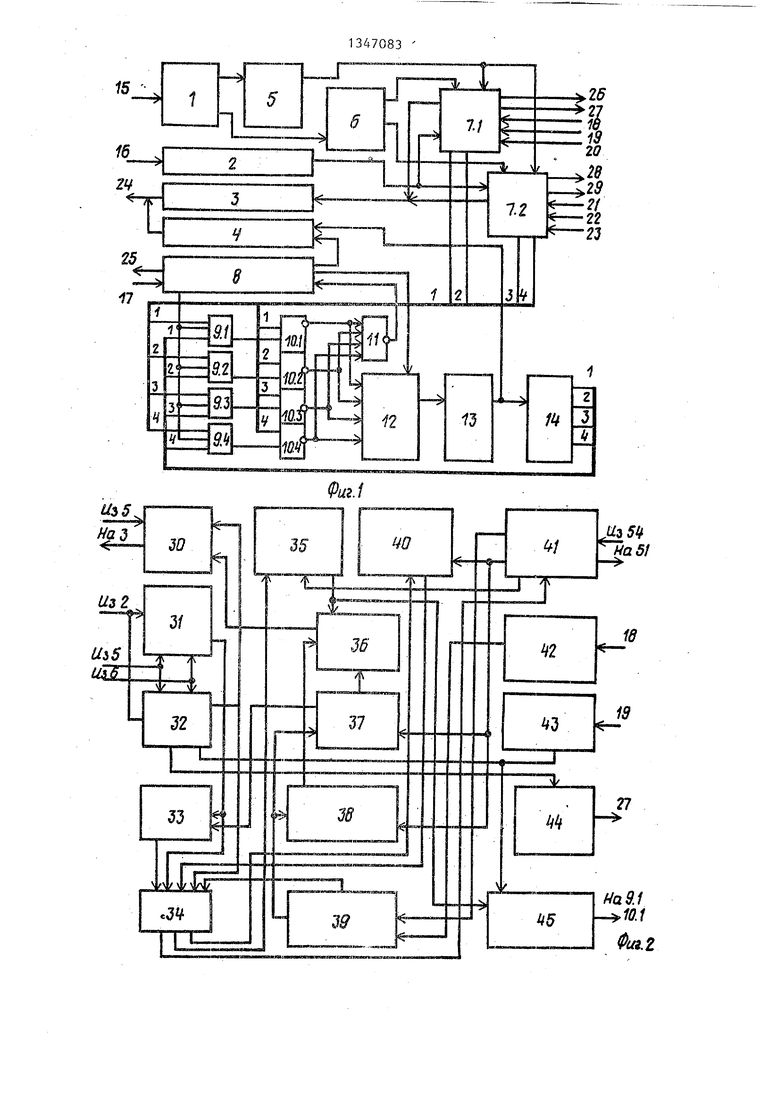

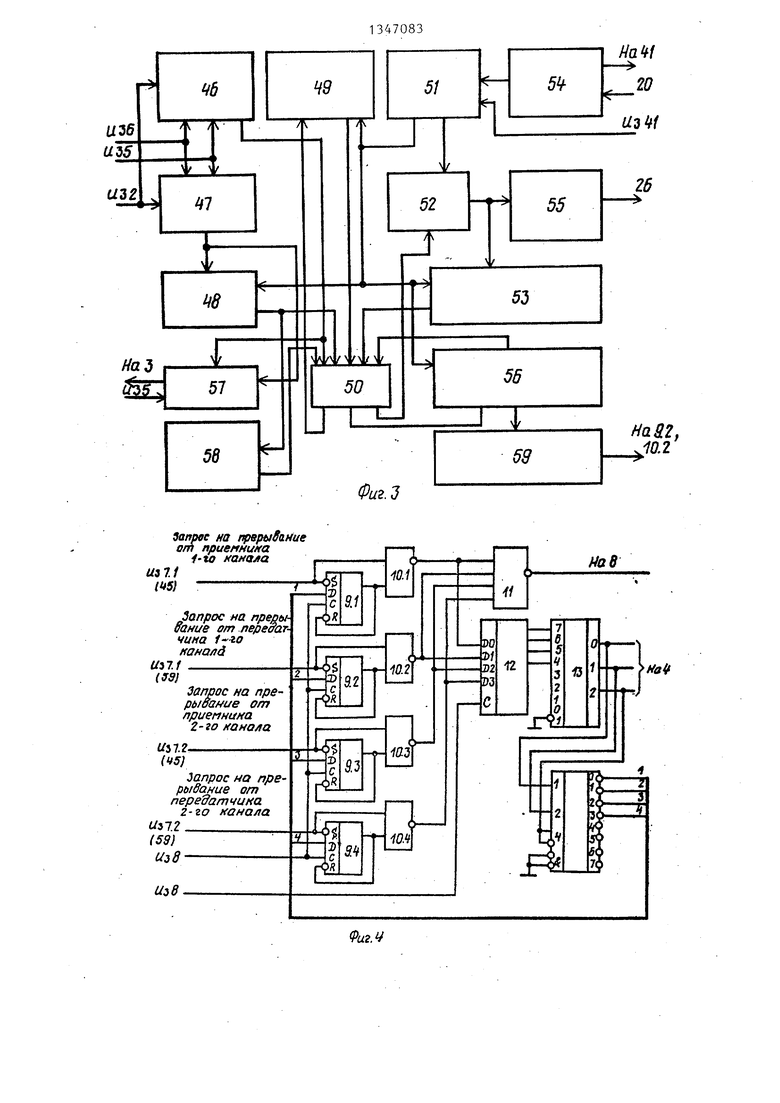

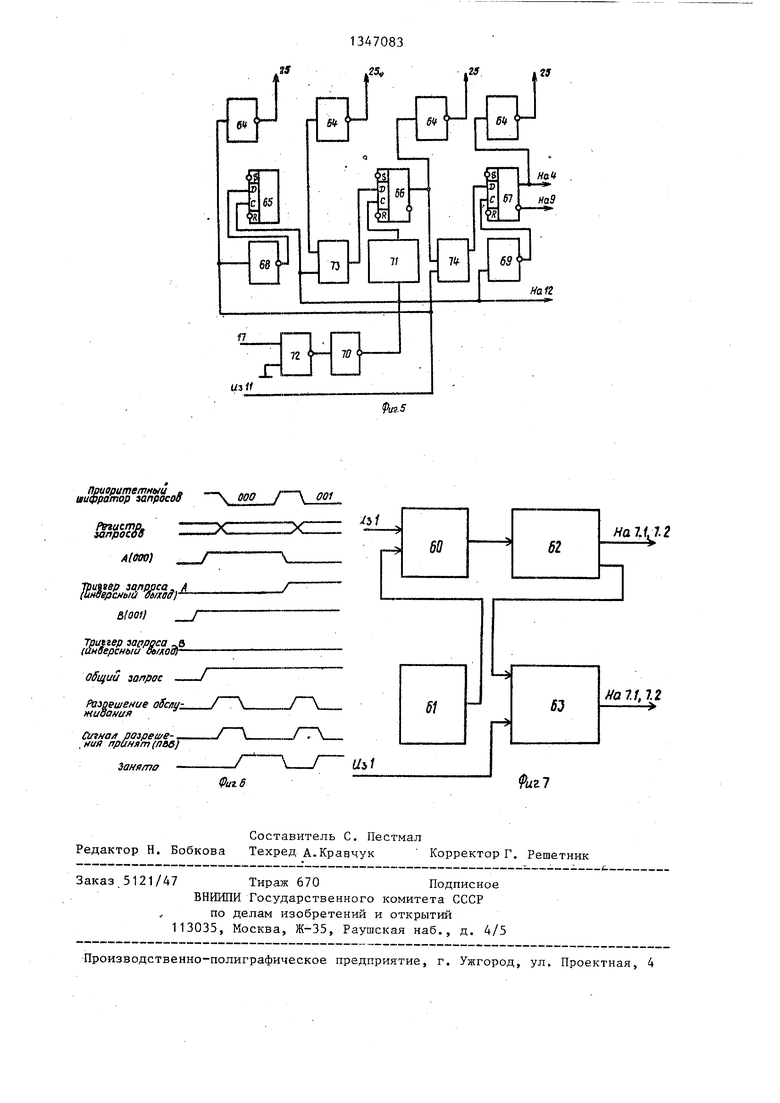

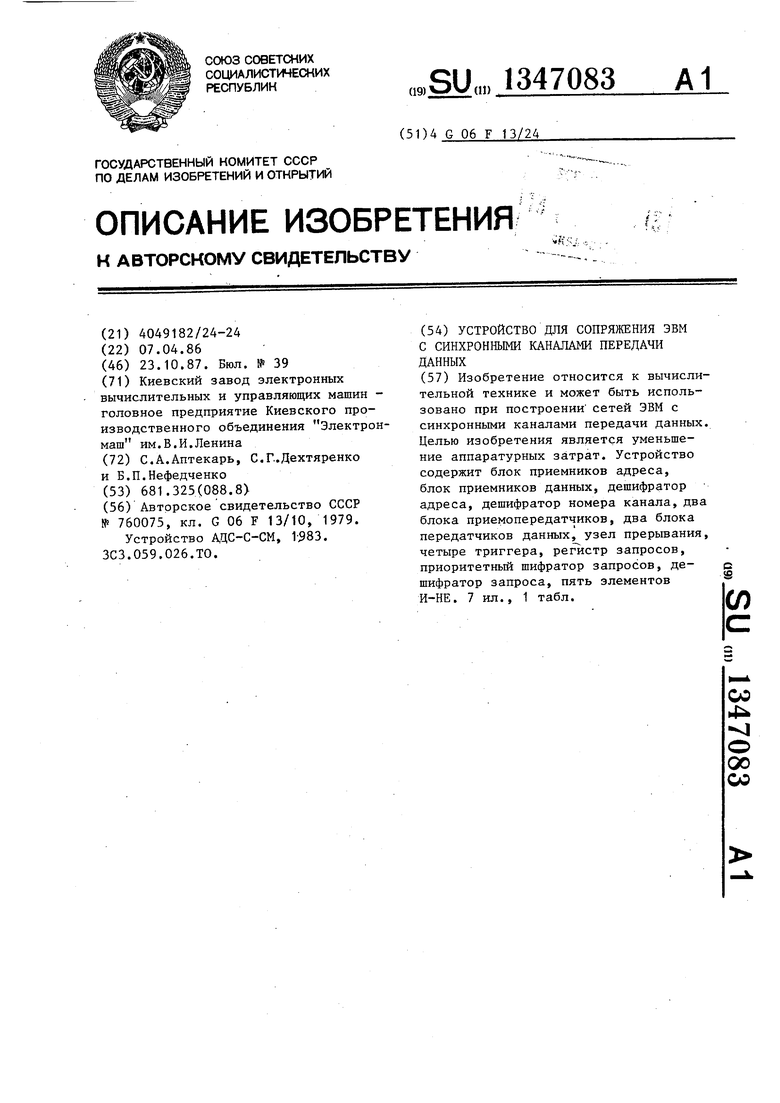

На фиг. 1 представлена структурна схема устройства; на фиг. 2 - .приемная часть блока приемопередатчиков канала; на фиг. 3 - -передающая часть блока приемопередатчиков канала; на фиг. 4 - схемная реализация триггеров и элементов И-НЕ, регистра запросов, дешифратора обслуживаемого запроса; на фиг. 5 - узел управления прерываниями; на фиг. 6 - временная диаграмма; на фиг. 7 - дешифратор адреса и регистра.

Устройство (фиг. 1) содержит блок 1 приемников адреса, блок 2 приемников данных, первьш 3 и второй 4 1 блоки передатчиков данных, дешифратор 6 номера канала, блоки 7.1-7.2 приемопередатчиков канала, узел 8 прерывания, триггеры 9,1-9,4, элементы И-НЕ 10.1-10.4, элемент И-НЕ 11, регистр 12 запросов, приоритетный шифратор 13 запросов, дешифратор 14 обслуживаемого запроса, входы и выходы 15-29 устройства.

Блок 7 приемопередатчиков канала состоит из приемной и передающей частей. .Приемная часть (фиг. 2) содержит мультиплексор 30 данных, регистр 31 параметров и синхросимволов управляющий регистр 32 приемника, узел 33 сравнения, постоянную память 34, регистр 35 синхронизированных сигналов управления, буферный регист 36 приемника, сдвигающий регистр 37 приемника, сдвигающий регистр 38 циклического контроля, счетчик 39 последовательных единиц в символе, счетчик 40 битов принимаемого символа, узел 41 формирования тактовых сигналов, приемники 42 сигналов данных от канала, приемники 42 сигналов управления, передатчики 44 сигналов управления к каналу, триггер 45 запроса на прерывание от приемника.

Передающая часть блока приемопередатчиков канала (фиг. 3) содержит управляющий регистр 46 передатчика, буферный регистр 47 передатчика, сдвигающий регистр 48 передатчика, регистр 49 синхронизованных сигналов управления, постоянн то память 50, узел 51 формирования тактовых сигна

0

5

лов передатчика, триггер 52 данных, счетчик 53 последовательных единиц в передаваемом символе, приемник 54 сигналов синхронизации от абонента, передатчик 55 сигналов данных к абоненту, счетчик 56 битов передаваемого символа, мультиплексор 57 данных, сдвигающий регистр 58 циклического контроля передачи, триггер.59 запроса на прерывание от передатчика. Дешифратор 5 адреса содержит (фиг. 7) узел 60 сравнения, узел 61 задания адреса, элемент НЕ 62, дешиф- 5 ратор 63 выбора регистра.

Для приемников адреса 1 данных 2, первого 3 и второго 4 блоков пере- датчиков данных (фиг. .1) можно использовать микросхе1Ф1.

Узел 8 прерывания (фиг. 5) содержит передатчики 64 управляющих сигналов устройства, триггеры 65-67, элементы НЕ 68-70, элемент 71 задержки приемник 72 управляющего сигнала, элементы И 73 и 74.

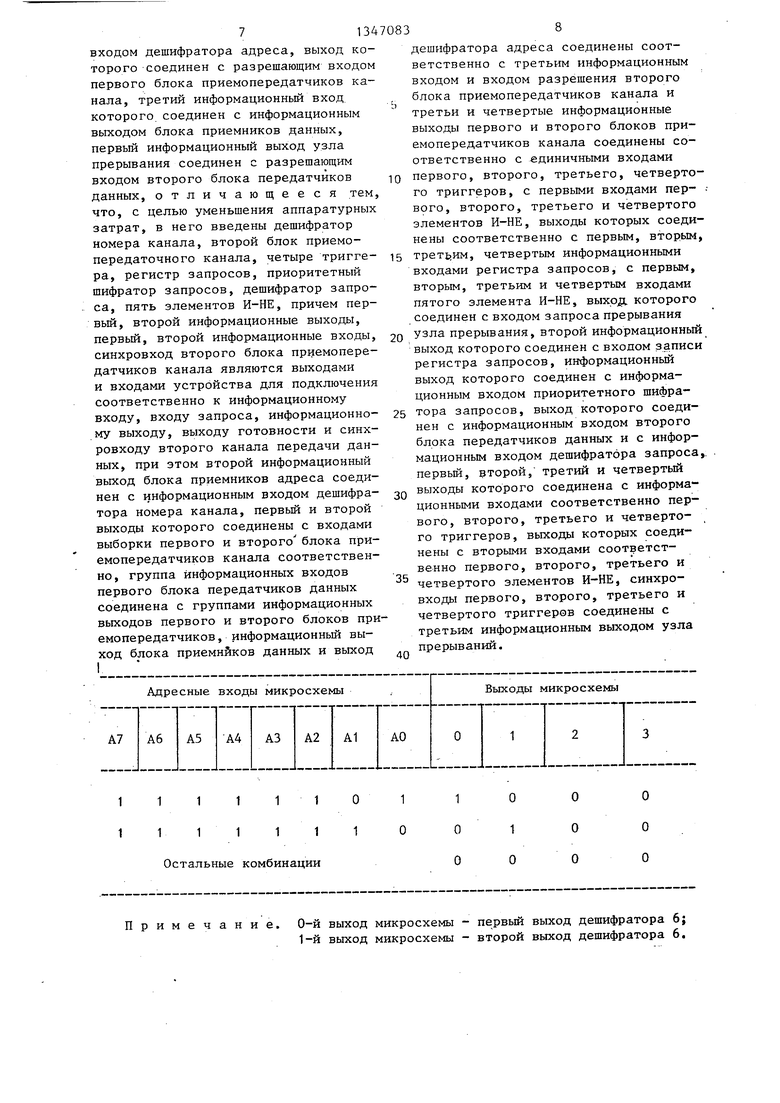

Дешифратор 6 номера канала (фиг. 1) ) можно выполнить на микросхеме постоянной памяти. При этом микросхема прожигается согласно таблице.

Устройство работает следующим образом.

Перед началом обмена данными между ЭВМ и каналом выполняется настройка устройства сопряжения. Под управлением программы через вход 15 устройства, блок 1 приемников адреса адрес блока обмена поступает в де- шифратор 5 адреса и на дешифратор 6 номера канала: старшая часть адреса -в дешифратор 5, младшая - на дешифратор 6, Дешифратор 5 сравнивает полученный адрес с собственными и в случае совпадения.формирует сигнал выбора, поступающий одновременно в блоки 7,1 и 7.2. Дешифратор 6 анализирует код номера канала, содержащийся в младшей части адреса, и при обращении в блоку 7.1 возбуждает первый выход, при обращении к блоку 7.2 - второй. В выбранный блок 7.1 (7.2) через вход 16 устройства, блок 2 приемников данных загружается .информация, определяющая тип протокола обмена, режим работы устройства (основной или проверки), необходимость выполнения циклического контроля, режим подключения к линии.

Затем устанавливается логическая связь с каналом передачи данных. .

0

S

0

5

0

55

Для этого в выбранный блок приемопередатчиков канапа заносится так же как и при настройке устройства, информация, содержащая команду Подготовиться к работе. Из блока 7.1 :(7.2) в канал передачи на второй информационный выход 27 (29) выдается соответствующий сигнал управления. Ответный сигнал Готов к работе принимается от канала на второй информационный вход 19 (22) блоков 7.1 (7.2). Состояние готовности канала завершает установление логической связи между ЭВМ и каналом-передачи данных и вызывает формирование запроса, на прерывание на третьем и четвертом информационных выходах блока приемопередатчиков. Сигнал запроса поступает на единичные входы триггера 9.1 (9.3) и элемента И-НЕ 10.1(10.3) затем через элемент И-НЕ 11 на вход запроса прерывания узла 8 и далее в ЭВМ через первую группу выходов 25 устройства.

После установления связи с каналом устройство выполняет обмен данными. Передача и прием могут производиться одновременно. Параллельные байты от ЭВМ через вход 16 устройства, блок 2 приемников загружаются в блок 7.1 (7.2), преобразуется в нем в последовательные коды и гГоступают далее через информационньй выход 26 (28) устройства в канал передачи данных. Поступающие от канала последователь- ные коды через информационный вход 18 (21) устройства принимаются побит- но .в блок 7.1 (7.2), преобразуются в параллельные байты и затем через блок 3 передатчиков вьщаются на информационный выход 24 устррйства и далее в ЭВМ. Синхронизация передачи и при- ема данных обеспечивается тактовыми сигналами, поступакяцими от канала на входы 20 (23) синхронизации устройства.

В ответ на сигнал запроса от ЭВМ на вход 17 устройства поступает сигнал Разрешение обслуживания прерывания, который запускает узел 8, а также фиксирует в регистре 12 запросы, установленные на элементах И-НЕ 10.1-10.4. Шифратор 13 вьщеляет самый приоритетный запрос, формируя при этом соответствующий вектор пре- рывания./Код вектора подается на информационный вход блока 4 передатчи- ков данных. После снятия ЭВМ сигнала

п-

, -jg а 2о , 25

м до ) 35 - к , 055

, 45

Разрешение обслуживания прерывания устройство захватывает управление интерфейсом, устанавливает на выходе узла 8 сигнал Занято, который открывает блок 4 передатчиков. Вектор прерывания выдается в ЭВМ. Кроме того, код вектора анализируется дешифратором 14. На одном из выходов, со- ответствуюзем коду запроса, дешифратор 14 формирует сигнал логического О, поступающий на информационный вход соответствующего триггера 9. При завершении процедуры обслуживания прер ьшания по снятию сигнала Занято триггер 9 сбрасывается в О, блокируя прохождение сигнала обслуживаемого запроса через элемент И-НЕ 10 (фиг. 4). Далее обрабатываются запросы с более низким приоритетом.

Передающая часть блоков 7.1 и 7.2 (фиг. 3) работает следующим образом. В буферный регистр 47 передатчика из блока 2 приемников заносится байт данных, перезаписывается в сдвигающий регистр 48 и побитно вьщвигается из младшего разряда на один из входов постоянной памяти 50. В зависимости от состояния остальных входов формируется адрес памяти. На выходе, соединенном с триггером 52, устанавливается уровень, повторяющий принятый входной сигнал..На очередном тактовом импульсе триггер 52 принимает считанную из памяти информацию. С выхода триггера 52 через передатчик 55 последовательно данные выдаются в канал передачи. Выход триггера 52 подключен также к счетчику 53, который при обнаружении пяти подряд идущих единиц в передаваемом символе формирует адрес памяти, по которому считывается уровень логического О в триггер 52. После пяти единиц в передаваемый символ вставляется нуль. Эта процедура выполняется при работе под управлением бит-ориентированных протоколов. Счетчик 56 отсчитывает такты вьщачи битов символа в канал и после каждых восьми тактов устанавливает триггер 59 запроса. Через элементы И-НЕ 10.2 и t1, узел 8 прерывания, группу выходов 25 в ЭВМ поступает запрос на получение следующего байта данных. При занесении очередного байта в буферный регистр 47 триггер 59 сбрасывается в нуль. Одновременно с вьщачей в калал передачи данные из регистра 48 поступают в

сдвигающий регистр 58 циклического контроля, выполняющий формирование контрольных символов. Эти символы сопровождают информационнуво часть сообщения.

Синхронизация работы регистров 48 и 49, счетчиков 53 и 56, триггера 52 при передаче данных обеспечивается узлом 51, в основном режиме работающим от тактовых сигналов, через вход 20 синхронизации и приемник 54 от канала. ,В режиме проверки тактирующие сигналы формируются внутренним генератором, входящим в состав уз- :ла 41. Регистр 49 согласует асин- |Хронную работу интерфейса ЭВМ с син- хронным обменом через канал передачи данных. Информация из Постоянной памяти 50 по тактовым сигналам узла 51 принимается в регистр 49. Состояние управляющих выходов регистра 49 оп- ределяет последовательность считывания управляющих кодов из памяти 50. Прием данных молсет выполняться в устройстве одновременно с передачей (фиг. 2). Последовательные биты данных из канала передачи через информационный вход 18 принимается на вход приемников 42, проходят через счетчик 39 и накапливаются в сдвигающем регистре 37. Узел 33 сравнения отслеживает в начале приема содержимое регистра 37, сопоставляя его на каждом такте с кодом синхросимвола, хранящегося в регистре 31, заполненном перед началом обмена..При совпадении кЬдов вьщается единичный сигнал на один из входов постоянной паМя- ти 34. Формируется адрес, по которому считывается код начала приема сообщения, управляющий работой счетчика 40, регистра 35, узла 41. Счетчик 40 отсчитывает такты приема битов данных и после вхождения в синхронизм через каждые восемь тактов формирует- сигнал управления памятью 34. Из па- мяти 34 считывается управляющий код в регистр 35. Последний формирует : сигнал пересылки байта из сдвигающего регистра 37 в буферный регистр 36. Этот же сигнал устанавливает в 1 триггер 45 запроса. Через элементы И-НЕ 10.1 и 11, узел 8, группу выходов 25 устройства в ЭВМ поступает запрос на выдачу байта данных от абонента. Счетчик 39 при обнаружении пяти единиц подряд в принимаемом символе формирует на входах постоян1347083 6

ной памяти 34 адрес, по которому считывается код, блокирующий выдачу переднего тактового сигнала узлом 41, Пропускают один такт работы счетчик 40, регистры 37 и 38. Таким образом, вставленный на передаче после пяти единиц служебный бит нуля извлекается из данных при работе и бит ориентированном протоколе на приемке. Принимаемое сообщение, включая контрольные символы, проходит через сдвигающий регистр.38. Наличие ошибки .фиксируется в буферном регистре 36.

g Синхронизация регистров 35, 37 и 38, счетчиков 39 и 40 при приеме данных обеспечивается узлом 41 в основном . режиме работающей от тактовых сигна20

25

30

35

40

45

50

55

лов, поступающих через вход 20 синхронизации и приемник 54 от канала. В режиме проверки тактовые сигналы формируются внутренним генератором, входящим в состав узла 41.

Формула изобретения

Устройство для сопряжения ЭВМ с синхронными каналами передачи данных, содержащее блок приемников адреса, блое приемников данных, дешифратор адреса, два блока передатчиков данных, узел прерывания, первый блок приемопередатчиков канала, причем информационные входы блоков приемников адреса и данных являются входами устройства для подключения соответственно к адресному и информационно- му выходам ЭВМ, выходы первого и второго передатчиков данных образуют группу выходов устройства для подключения к группе информационных входов ЭВМ, группа информационных выходов и вход разрешения прерывания узла прерывания образуют соответственно группу выходов и вход устройства для подключения к группе входов запроса прерывания и выходу разрешения прерывания ЭВМ, первый, второй информационные выходы, первьй, второй информационные входы и синхровход первого блока приемопередатчиков канала являются выходами и входами устройства для подключения соответственно к информационному выходу, входу запроса, информационному выходу, выходу готовности и синхровыходу первого канала передачи данных, при этом первый информационньй выход блока приемников адреса соединен с информационным

0

5

0

5

0

5

0

5

лов, поступающих через вход 20 синхронизации и приемник 54 от канала. В режиме проверки тактовые сигналы формируются внутренним генератором, входящим в состав узла 41.

Формула изобретения

Устройство для сопряжения ЭВМ с синхронными каналами передачи данных, содержащее блок приемников адреса, блое приемников данных, дешифратор адреса, два блока передатчиков данных, узел прерывания, первый блок приемопередатчиков канала, причем информационные входы блоков приемников адреса и данных являются входами устройства для подключения соответственно к адресному и информационно- му выходам ЭВМ, выходы первого и второго передатчиков данных образуют группу выходов устройства для подключения к группе информационных входов ЭВМ, группа информационных выходов и вход разрешения прерывания узла прерывания образуют соответственно группу выходов и вход устройства для подключения к группе входов запроса прерывания и выходу разрешения прерывания ЭВМ, первый, второй информационные выходы, первьй, второй информационные входы и синхровход первого блока приемопередатчиков канала являются выходами и входами устройства для подключения соответственно к информационному выходу, входу запроса, информационному выходу, выходу готовности и синхровыходу первого канала передачи данных, при этом первый информационньй выход блока приемников адреса соединен с информационным

входом дешифратора адреса, выход которого соединен с разрешающим входом первого блока приемопередатчиков канала, третий информационньш вход которого соединен с информационным выходом блока приемников данных, первый информационный выход узла прерывания соединен с разрешающим входом второго блока передатчиков данных, отличающееся тем что, с целью уменьшения аппаратурных затрат, в него введены дешифратор номера канала, второй блок приемо- передаточного канала, четыре триггера, регистр запросов, приоритетный шифратор запросов, дешифратор запроса, пять элементов И-НЕ, причем первый, второй информационные выходы, первый, второй информационные входы, синхровход второго блока npiieMonepe- датчиков канала являются выходами и входами устройства для подключения соответственно к информационному входу, входу запроса, информационному выходу, выходу готовности и синх- ровходу второго канала передачи данных, при этом второй информационный выход блока приемников адреса соединен с информационным входом дешифратора номера канала, первый и второй выходы которого соединены с входами выборки первого и второго блока приемопередатчиков канала соответственно, группа информационных входов первого блока передатчиков данных соединена с группами информационных выходов первого и второго блоков приемопередатчиков , информационный выход блока приемников данных и выход

1 1 1 11 111 1 1

Остальные комбинации

Примечание. 0-й выход микросхемы - первый выход дешифратора 6;

1-й выход микросхемы - второй выход дешифратора 6.

0

дешифратора адреса соединены соответственно с третьим информационным входом и входом разрешения второго блока приемопередатчиков канала и третьи и четвертые информационные выходы первого и второго блоков приемопередатчиков канала соединены соответственно с единичными входами первого, второго, третьего, четвертого триггеров, с первыми входами пер- вого, второго, третьего и четвертого элементов И-НЕ, выходы которых соединены соответственно с первым, вторьм,

5 третьим, четвертым информационными входами регистра запросов, с первым, вторым, третьим и четвертым входами пятого элемента И-НЕ, выход которого соединен с входом запроса прерывания

0 узла прерывания, второй информационный выход которого соединен с входом записи регистра запросов, информационный выход которого соединен с информационным входом приоритетного шифра5 тора запросов, выход которого соединен с информационным входом второго блока передатчиков данных и с информационным входом дешифратора запроса,. первьш, второй, третий и четвертый выходы которого соединена с информационными входами соответственно первого, второго, третьего и четвертого триггеров, выходы которых соединены с вторьши входами соот етст- венно первого, второго, третьего и четвертого элементов И-НЕ, синхро- входы первого, второго, третьего и четвертого триггеров соединены с третьим информационным выходом узла

прерываний.

0

О О О

о о о

w

9апрое на прврыбмие

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1566359A1 |

| Устройство для сопряжения ЭВМ с синхронным каналом передачи данных | 1986 |

|

SU1424023A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении сетей ЭВМ с синхронными каналами передачи данных. Целью изобретения является уменьшение аппаратурных затрат. Устройство содержит блок приемников адреса, блок приемников данных, дешифратор адреса, дешифратор номера канала, два блока приемопередатчиков, два блока передатчиков данных, узел прерывания, четыре триггера, регистр запросов, приоритетный шифратор запросов, дешифратор запроса, пять элементов И-НЕ. 7 ил., 1 табл. с S (Л со 4; -vi о 00 со

| Авторское свидетельство СССР № 760075, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство АЦС-С-СМ, 1-583 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-23—Публикация

1986-04-07—Подача