1

Изобретение относится к цифровой вычислительной технике и может быть использовано в распределенных вычислительных системах и сетях ЭВМ, особенно в локальных сетях для организации взаимодействия между компонентами сетей и систем.

Целью изобретения является повышение производительности станции, которая обеспечивает работу устройства с высокоскоростными каналами связи, например с моноканалом, п кото14

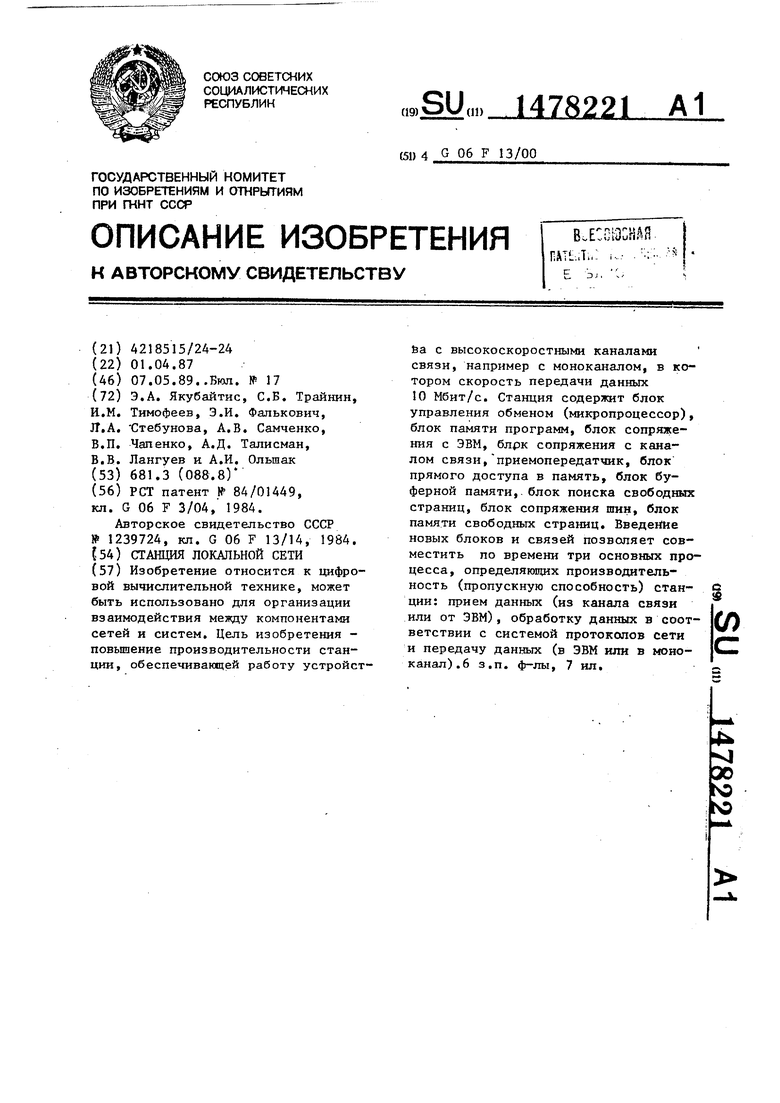

Блок 6 содержит узлы приема кадра 23 и выдачи кадра 24 и приемопере датчик 9.

Блок 7 прямого доступа в память связан с блоком 6 с помощью группы 25 шин, связанным с блоком 8 поиска

15

ром скорость передачи данных 10 Мбит/с.

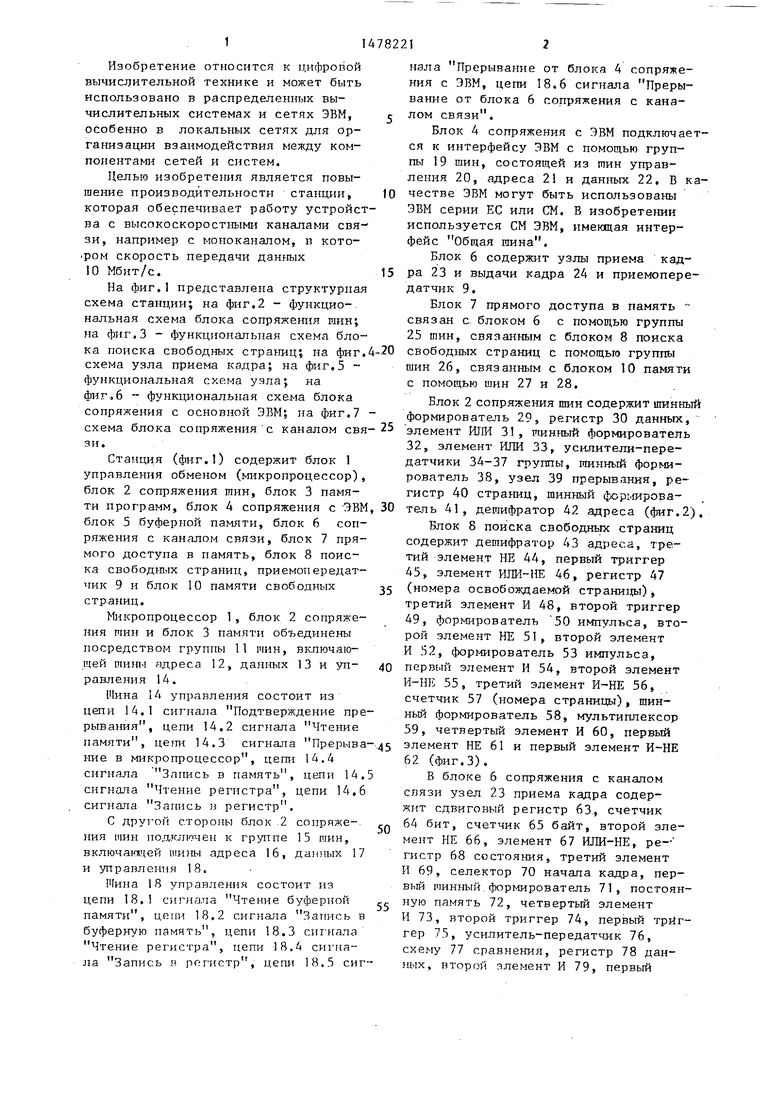

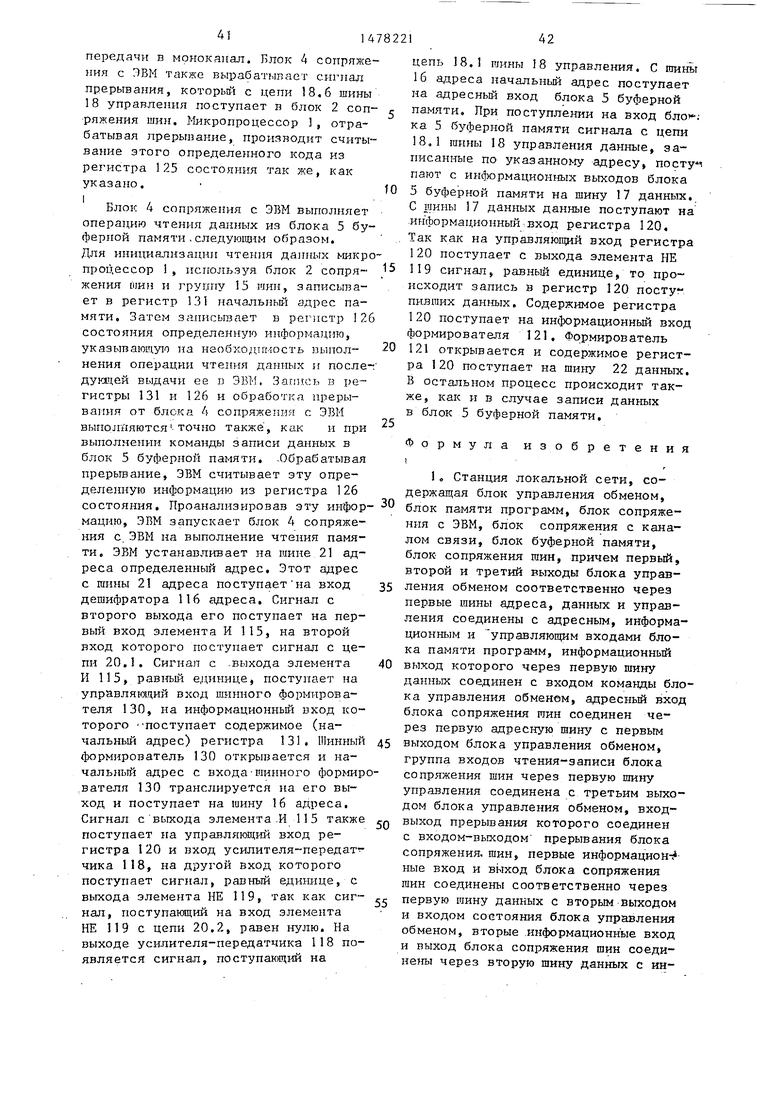

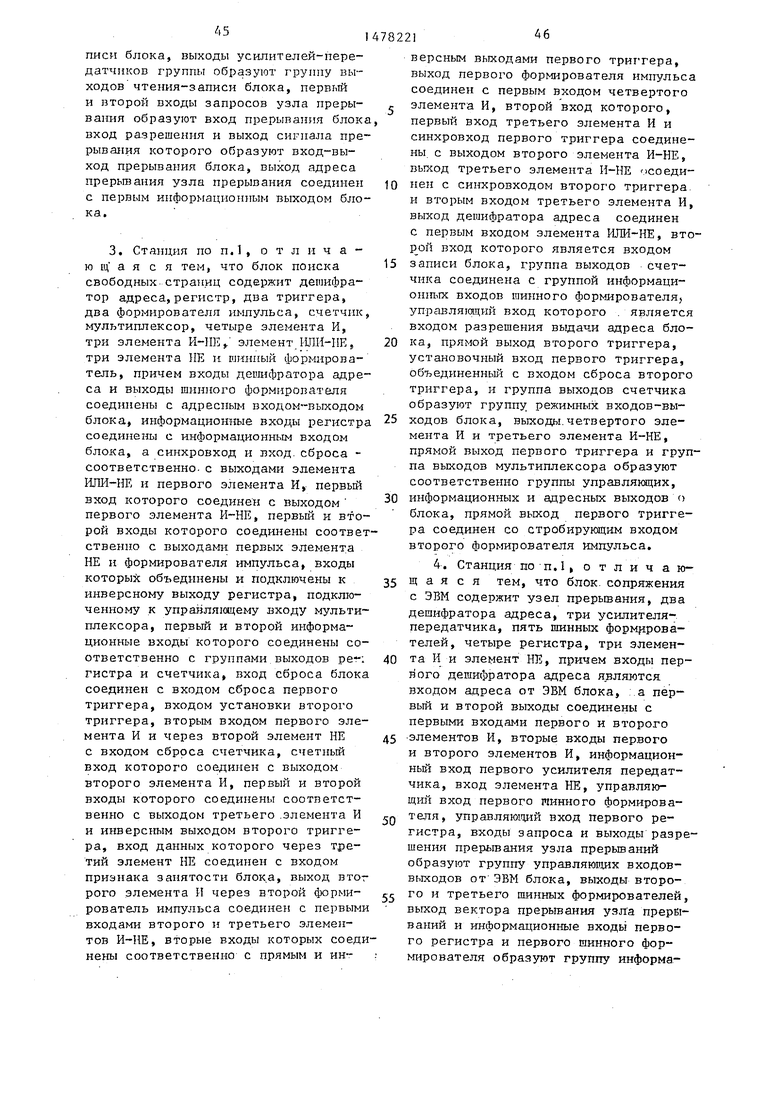

На фиг.1 представлена структурная схема станции; на фиг.2 - функциональная схема блока сопряжения шин; на фпг.З - функциональная схема блока поиска свободных страниц; на фиг.4-20 свободных страниц с помощью группы схема узла приема кадра; на фиг.5 шин 26, связанным с блоком 10 памяти функциональная схема уяла; на фиг,6 - функциональная схема блока сопряжения с основной ЭВМ; на фиг.7 - схема блока сопряжения с каналом свя- 25 зи.

с помощью шин 27 и 28.

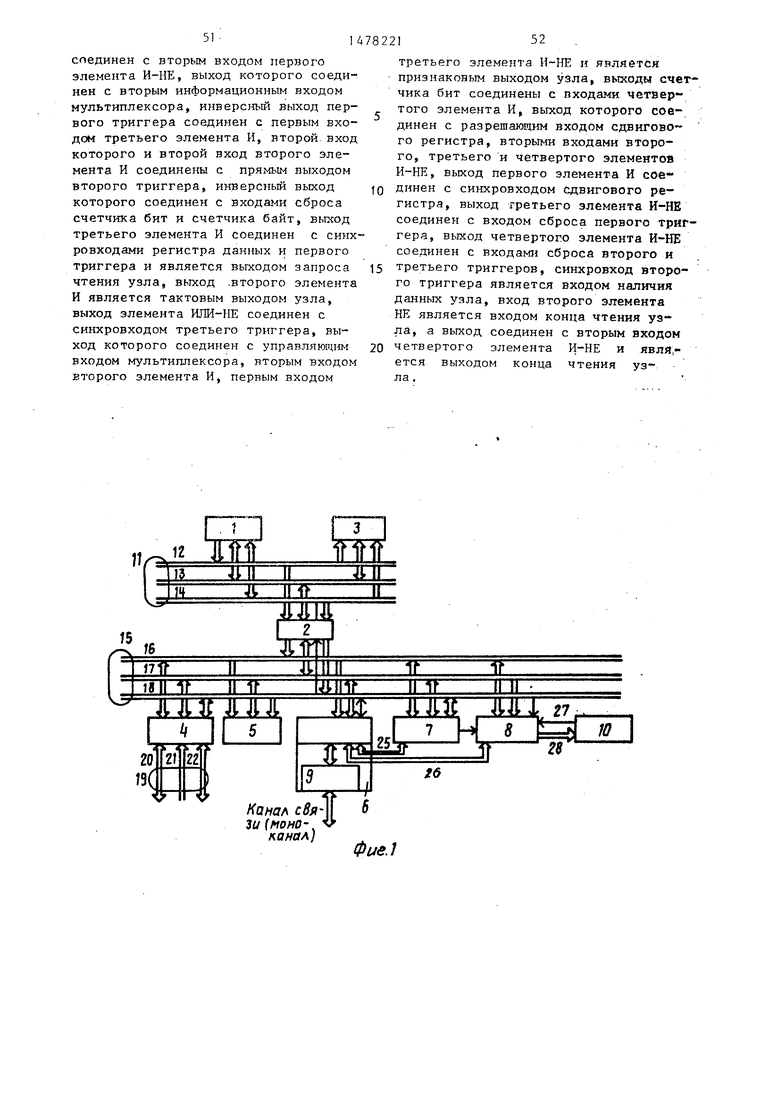

Блок 2 сопряжения шин содержит шинны формирователь 29, регистр 30 данных, элемент ИЛИ 31, тинный формирователь 32, элемент ИЛИ 33, усилители-передатчики 34-37 группы, шинный формирователь 38, узел 39 прерывания, регистр 40 страниц, тинный формироваСтанция (фиг.1) содержит блок 1 управления обменом (микропроцессор), блок 2 сопряжения тин, блок 3 памяти программ, блок 4 сопряжения с ЭВМ, 30 тель 41, дешифратор 42 адреса (фиг.2).

блок 5 буферной памяти, блок 6 сопряжения с каналом связи, блок 7 прямого доступа в память, блок 8 поиска свободных страниц, приемопередатчик 9 и блок 10 памяти свободных страниц.

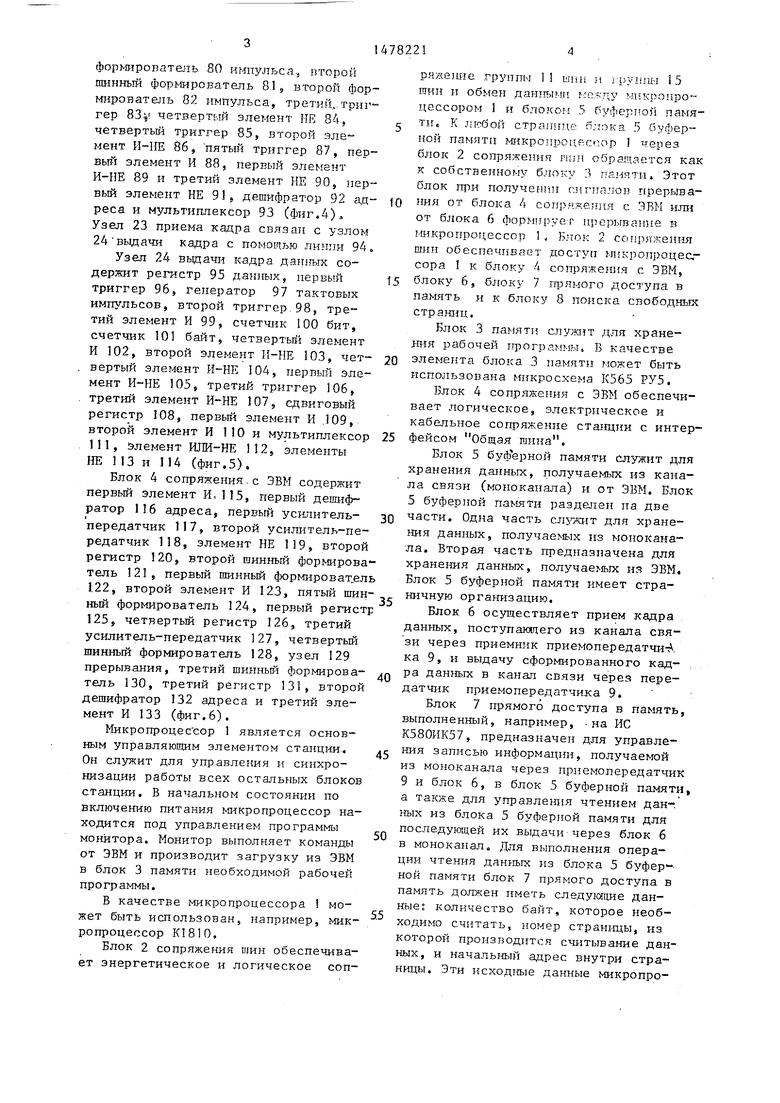

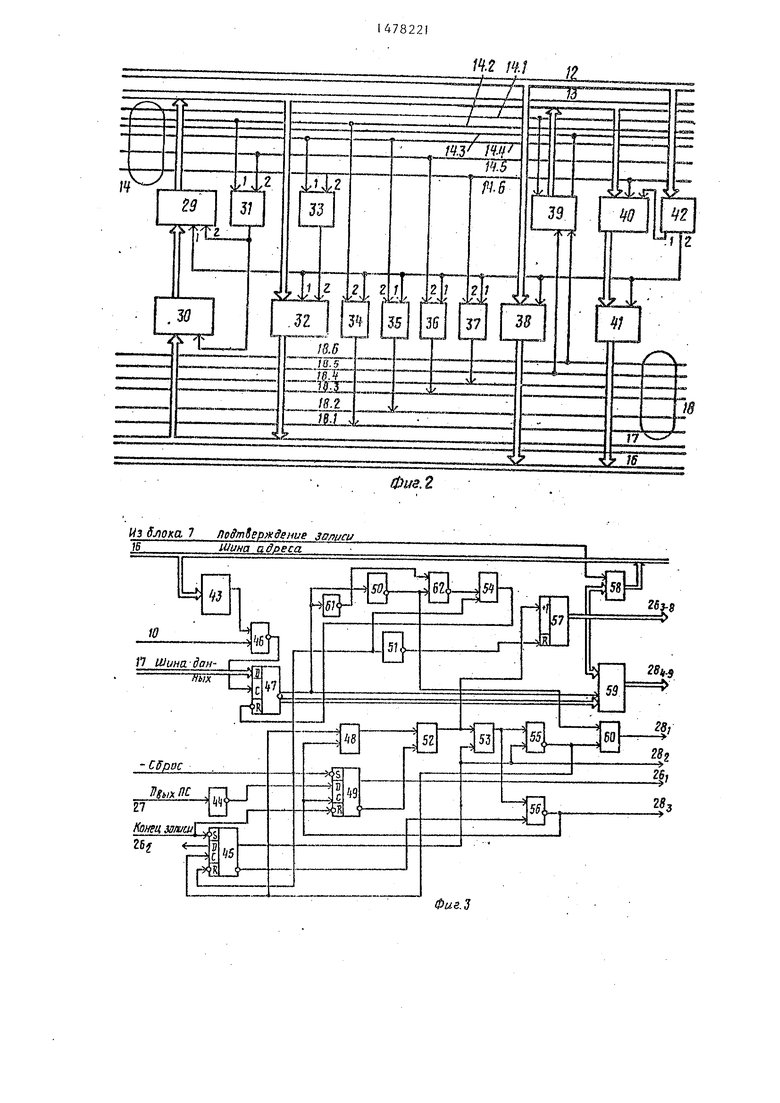

Микропроцессор 1, блок 2 сопряжения пин и блок 3 памяти объединены посредством группы 11 гаин, включаюБлок 8 поиска свободных страниц содержит дешифратор 43 адреса, третий элемент НЕ 44, первый триггер 45, элемент ИЛИ-НЕ 46, регистр 47 35 (номера освобождаемой страницы),

третий элемент И 48, второй триггер 49, формирователь 50 импульса, второй элемент НЕ 51, второй элемент И 52, формирователь 53 импульса, первЕий элемент И 54, второй элемент И-НЕ 55, третий элемент И-НЕ 56, счетчик 57 (номера страницы), шинный формирователь 58, мультиплексор 59, четвертый элемент И 60, первый

третий элемент И 48, второй триггер 49, формирователь 50 импульса, вто рой элемент НЕ 51, второй элемент И 52, формирователь 53 импульса, первЕий элемент И 54, второй элемент И-НЕ 55, третий элемент И-НЕ 56, счетчик 57 (номера страницы), шинный формирователь 58, мультиплексор 59, четвертый элемент И 60, первый

40

щей шины адреса 12, данных 13 и управления 14.

Чина 14 управления состоит из цепи 14.1 сигнала Подтверждение прерывания, цепи 14.2 сигнала Чтение памяти, цепи 14.3 сигнала Прерыва- з элемент НЕ 61 и первый элемент И-НЕ

ние в микропроцессор, цепи 14.4 сигнала Запись в память, цепи 14.5 сигнала Чтение регистра, цепи 14,6 сигнала Запись в регистр.

С другой стороны блок 2 сопряжения шин подключен к группе 15 шин, включающей шины адреса 16, данных 17 и управления 18,

Шина 18 управления состоит из цепи 18.1 сигнала Чтение буферной памяти, ЦЕПИ 18.2 сигнала Запись в буферную память, цепи 18.3 сигнала Чтение регистра, цепи 18.4 сигнала Запись Р регистр, цепи 18.5 сиг50

55

62 (фиг.З).

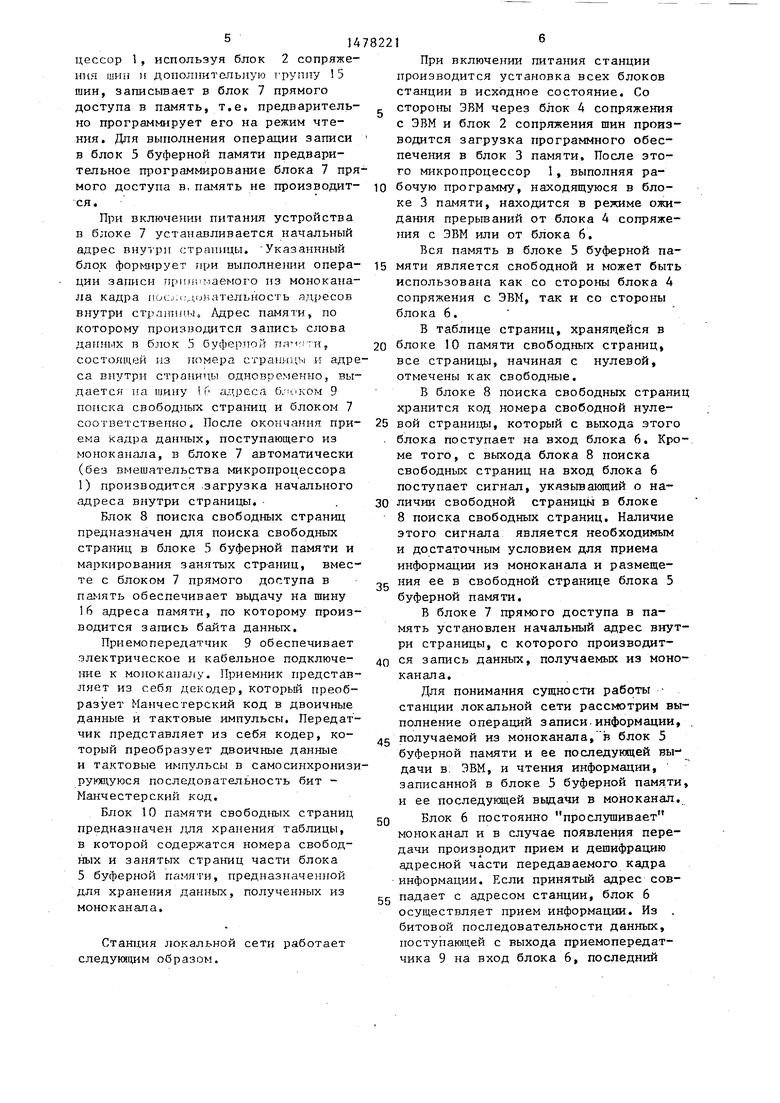

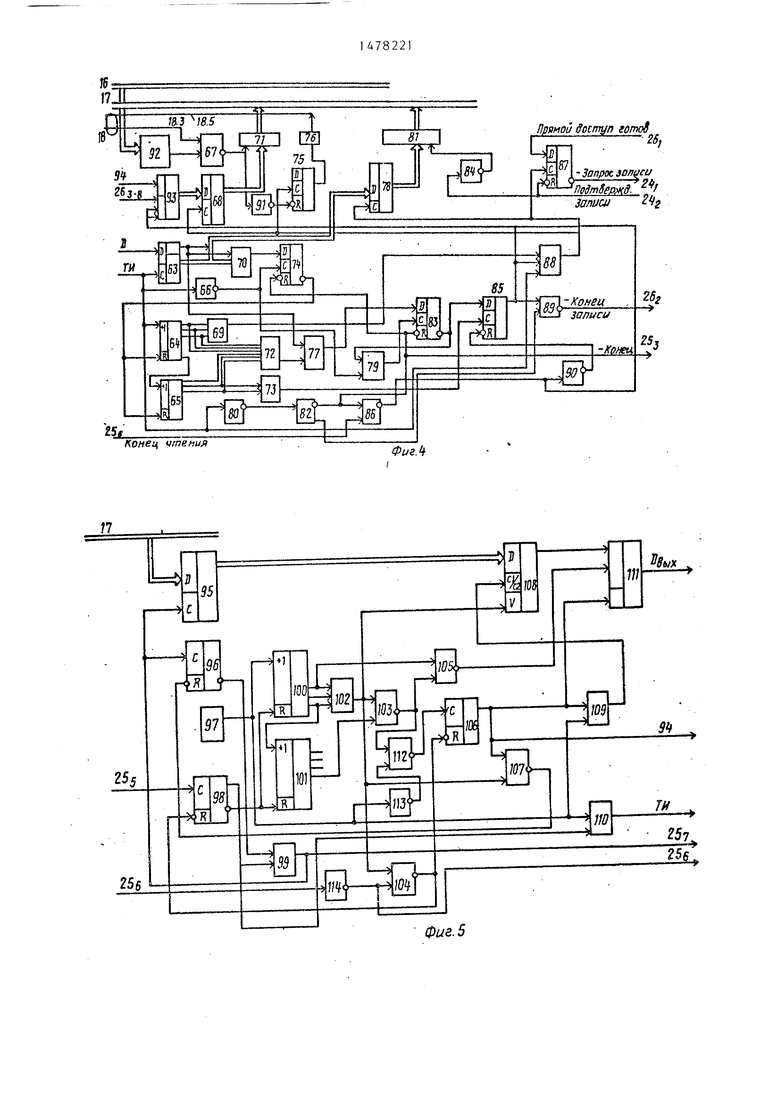

В блоке 6 сопряжения с каналом связи узел 23 приема кадра содержит сдвиговый регистр 63, счетчик 64 бит, счетчик 65 байт, второй элемент НЕ 66, элемент 67 ИЛИ-НЕ, ре- гистр 68 состояния, третий элемент И 69, селектор 70 начала кадра, первый шинный формирователь 71, постоян ную память 72, четвертый элемент И 73, второй триггер 74, первый триг гер 75, усилитель-передатчик 76, схему 77 сравнения, регистр 78 данных, второй элемент И 79, первый

82212

нала Прерывание от блока 4 сопряжения с ЭВМ, цепи 18.6 сигнала Прерывание от блока 6 сопряжения с кана- 5 лом связи.

Блок 4 сопряжения с ЭВМ подключается к интерфейсу ЭВМ с помощью группы 19 шин, состоящей из тин управления 20, адреса 21 и данных 22, В ка- JO честве ЭВМ могут быть использованы ЭВМ серии ЕС или СМ. В изобретении используется СМ ЭВМ, имеющая интерфейс Общая шина.

Блок 6 содержит узлы приема кадра 23 и выдачи кадра 24 и приемопередатчик 9.

Блок 7 прямого доступа в память связан с блоком 6 с помощью группы 25 шин, связанным с блоком 8 поиска

15

20 свободных страниц с помощью группы шин 26, связанным с блоком 10 памяти 25

свободных страниц с помощью группы шин 26, связанным с блоком 10 памяти

с помощью шин 27 и 28.

Блок 2 сопряжения шин содержит шинны формирователь 29, регистр 30 данных, элемент ИЛИ 31, тинный формирователь 32, элемент ИЛИ 33, усилители-передатчики 34-37 группы, шинный формирователь 38, узел 39 прерывания, регистр 40 страниц, тинный формироваБлок 8 поиска свободных страниц содержит дешифратор 43 адреса, третий элемент НЕ 44, первый триггер 45, элемент ИЛИ-НЕ 46, регистр 47 (номера освобождаемой страницы),

третий элемент И 48, второй триггер 49, формирователь 50 импульса, второй элемент НЕ 51, второй элемент И 52, формирователь 53 импульса, первЕий элемент И 54, второй элемент И-НЕ 55, третий элемент И-НЕ 56, счетчик 57 (номера страницы), шинный формирователь 58, мультиплексор 59, четвертый элемент И 60, первый

элемент НЕ 61 и первый элемент И-НЕ

0

5

62 (фиг.З).

В блоке 6 сопряжения с каналом связи узел 23 приема кадра содержит сдвиговый регистр 63, счетчик 64 бит, счетчик 65 байт, второй элемент НЕ 66, элемент 67 ИЛИ-НЕ, ре- гистр 68 состояния, третий элемент И 69, селектор 70 начала кадра, первый шинный формирователь 71, постоянную память 72, четвертый элемент И 73, второй триггер 74, первый триггер 75, усилитель-передатчик 76, схему 77 сравнения, регистр 78 данных, второй элемент И 79, первый

формирователь 80 импульсаs второй шинный формирователь второй формирователь 82 импульса, третий, триггер 83у четверти элемент НЕ 84 четвертый триггер 85, второй эле мент И-ПЕ 86, пятый триггер 87, первый элемент И 88, первый элемент И-НЕ 89 и третий элемент НЕ 90s первый элемент НЕ 9, дешифратор 92 адреса и мультиплексор 93 (фиг.4), Узел 23 приема кадра связан с узлом 24 выдачи кадра с помощью линии 94.

Узел 24 выдачи кадра данных содержит регистр 95 данных, первый триггер 96, генератор 97 тактовых импульсов, второй триггер 98, третий элемент И 99, счетчик 100 бит, счетчик 101 байт, четвертый элемент И 102, второй элемент П-НЕ 103, четвертый элемент И-НЕ 104, первый элемент И-НЕ 105, третий триггер 106, третий элемент И-НЕ 107, сдвиговый регистр 108, первый элемент И 109, второй элемент И 110 и мультиплексор 111, элемент ИЛИ-НЕ 112, элементы НЕ 113 и 114 (фиг.5).

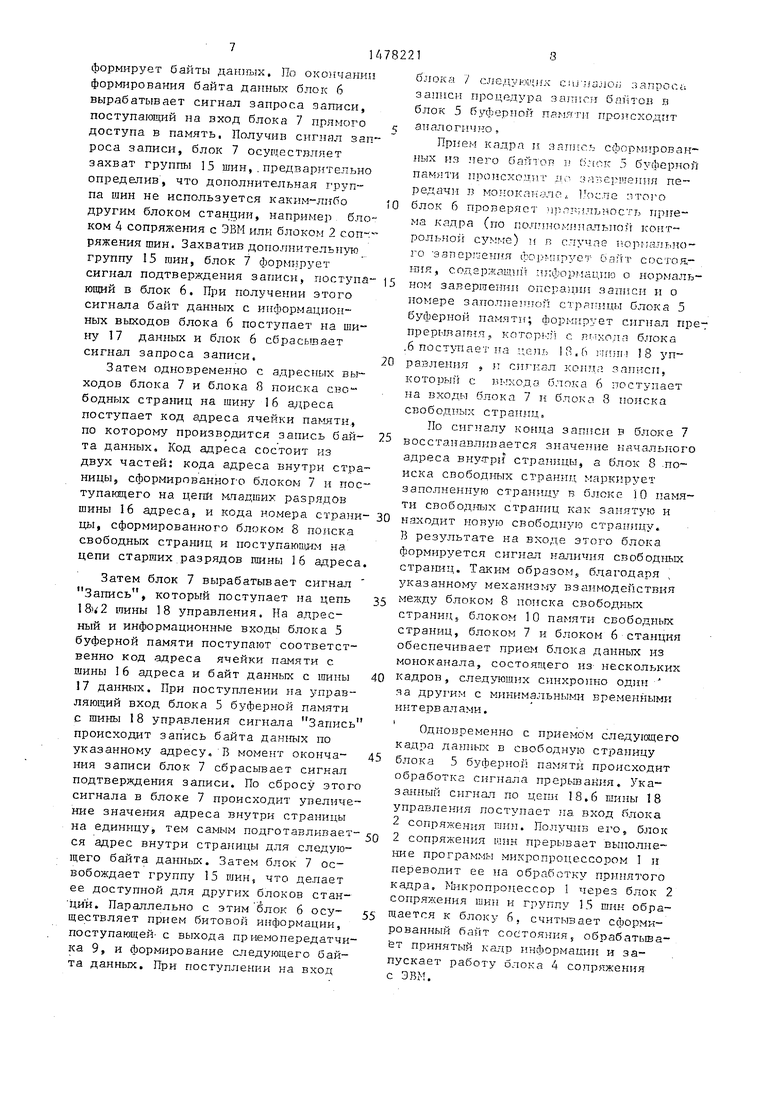

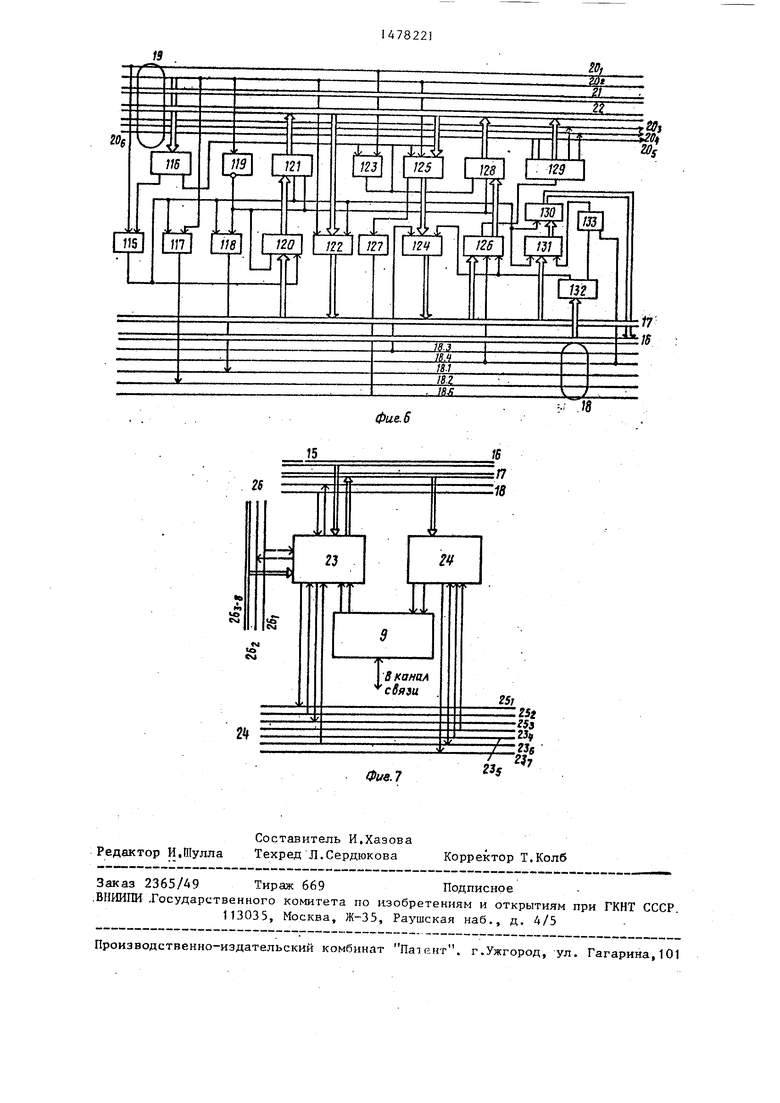

Блок 4 сопряжения с ЭВМ содержит первый элемент И,И5, первый дешифратор 116 адреса, первый усилитель- передатчик 117, второй усилитель-передатчик 118, элемент НЕ 119, второй регистр 120, второй шинный формирователь 121, первый шинный формировател 122, второй элемент И 123, пятый шинный формирователь 124, первый регист 125, четвертый регистр 126, третий усилитель-передатчик 127, четвертый шинный формирователь 128, узел 129 прерывания, третий шинный формирователь 130, третий регистр 131, второй дешифратор 132 адреса и третий элемент И 133 (фиг.6).

Микропроцес сор 1 является основным управляющим элементом станции. Он служит для управления и синхронизации работы всех остальных блоков станции. В начальном состоянии по включению питания микропроцессор находится под управлением программы монитора. Монитор выполняет команды от ЭВМ и производит загрузку из ЭВМ в блок 3 памяти необходимой рабочей программы.

В качестве микропроцессора 1 может быть использованs например, микропроцессор К1810.

Блок 2 сопряжения шин обеспечивает энергетическое и логическое соп

0

5

0

5

0

5

0

5

0

5

ряленне группы 1 ыиа и ivy-чиы 15 шин и обмен данными .у микропроцессором 1 и блоком 5 буферной памяти. PC лИэой странице- глока 5 буфер- нон памяти микропроцессор 1 срез блок 2 сопряжения г.ш обращается как к собственному блоку 3 ганяти, Этот блок при получении сигналов прерывания от блока 4 сопр сепис1 с ЭВМ или от блока 6 формирует прерывание я мнкропроцессоп 1, Блпк 2 сопряжения шин обеспечивает доступ микропроцессора 1 к блоку 4 сопряжения с ЭВМ, блоку 6, блоку 7 прямого доступа в память и к блоку 8 поиска свободных страниц.

Блок 3 памяти елулит для хранения рабочей тфограммч. В качестве элемента блока 3 памяти может быть использована микросхема К565 РУ5.

Блок 4 сопряжения с ЭВМ обеспечивает логическое, электрическое и кабельное сопряжение станции с интерфейсом Общая шина.

Блок 5 буф ерной памяти служит для хранения данных, получаемых из канала связи (моноканала) и от ЭВМ. Блок 5 буферной памяти разделен на две части. Одна часть служит для хранения данных, получаемых из моноканала. Вторая часть предназначена для хранения данных, получаемых из ЭВМ. Блок 5 буферной памяти имеет страничную организацию.

Блок 6 осуществляет прием кадра данных, поступающего из канала связи через приемник приемопередатчик ка 9, и выдачу сформированного кадра данных в канал связи через передатчик приемопередатчика 9.

Блок 7 прямого доступа в память, выполненный, например, на ИС К580ИК57, предназначен для управления записью информации, получаемой из моноканала через приемопередатчик 9 и блок 6, в блок 5 буферной памяти, а также для управления чтением данных из блока 5 буферной памяти для последующей их выдачи через блок 6 в моноканал. Для выполнения операции чтения данных из блока 5 буферной памяти блок 7 прямого доступа в память должен иметь следующие данные: количество байт, которое необходимо считать, номер страницы, из которой производится считывание данных, и начальный адрес внутри страницы. Эти исходные данные микропроb14

цессор 1, используя блок 2 сопряжения шин и дополнительную группу 15 шин, записывает в блок 7 прямого доступа в память, т.е. предваритель- но программирует его на режим чтения. Для выполнения операции записи в блок 5 буферной памяти предварительное программирование блока 7 прямого доступа в, память не производит- ся.

При включении питания устройства в блоке 7 устанавливается начальный адрес внутри страницы. Указаннный блок формирует при выполнении опера- ции записи npurii чаемого из моноканала кадра П л 1,оьач слыюс 1 ь адресов внутри стр.-шины. Адрес памяти, по которому производится запись слова данных в блок 5 буферной ты ч -ц. состоящей из померз странном и адреса внутри страницы одновременно, выдается на шину if1 адреса 6. мком 9 поиска свободных страниц и блоком 7 соответственно. После окончания при- ема кадра данных, поступающего из моноканала, в блоке 7 автоматически (без вмешательства микропроцессора 1) производится загрузка начального адреса внутри страницы. .

Блок 8 поиска свободных страниц предназначен для поиска свободных страниц в блоке 5 буферной памяти и маркирования занятых страниц, вместе с блоком 7 прямого доступа в память обеспечивает выдачу на шину 16 адреса памяти, по которому производится запись байта данных.

Приемопередатчик 9 обеспечивает электрическое и кабельное подключе- пие к моноканалу. Приемник представляет из себя декодер, который преобразует Манчестерский код в двоичные данные и тактовые импульсы. Передатчик представляет из себя кодер, который преобразует двоичные данные и тактовые импульсы в самосинхронизирующуюся последовательность бит - Манчестерский код.

Блок 10 памяти свободных страниц предназначен для хранения таблицы, в которой содержатся номера свободных и занятых страниц части блока 5 буферной памяти, предназначенной для хранения данных, полученных из моноканала.

Станция локальной сети работает следующим образом.

5 0 5 0

о

5

5

0

5

1е

При включении питания станции производится установка всех блоков станции в исходное состояние. Со стороны ЭВМ через блок 4 сопряжения с ЭВМ и блок 2 сопряжения шин производится загрузка программного обеспечения в блок 3 памяти. После этого микропроцессор 1, выполняя рабочую программу, находящуюся в блоке 3 памяти, находится в режиме ожидания прерываний от блока 4 сопряжения с ЭВМ или от блока 6.

Вся память в блоке 5 буферной памяти является свободной и может быть использована как со стороны блока 4 сопряжения с ЭВМ, так и со стороны блока 6.

В таблице страниц, хранящейся в блоке 10 памяти свободных страниц, все страницы, начиная с нулевой, отмечены как свободные.

В блоке 8 поиска свободных страниц хранится код номера свободной нулевой страницы, который с выхода этого блока поступает на вход блока 6. Кроме того, с выхода блока 8 поиска свободных страниц на вход блока 6 поступает сигнал, указывающий о наличии свободной страницы в блоке 8 поиска свободных страниц. Наличие этого сигнала является необходимым и достаточным условием для приема информации из моноканала и размещения ее в свободной странице блока 5 буферной памяти.

В блоке 7 прямого доступа в память установлен начальный адрес внутри страницы, с которого производится запись данных, получаемых из моноканала.

Для понимания сущности работы станции локальной сети рассмотрим выполнение операций записи информации, получаемой из моноканала,в блок 5 буферной памяти и ее последующей вы- дачи в ЭВМ, и чтения информации, записанной в блоке 5 буферной памяти, и ее последующей выдачи в моноканал.

Блок 6 постоянно прослушивает моноканал и в случае появления передачи производит прием и дешифрацию адресной части передаваемого кадра информации. Если принятый адрес совпадает с адресом станции, блок 6 осуществляет прием информации. Из битовой последовательности данных, поступающей с выхода приемопередатчика 9 на вход блока 6, последний

формирует байты данных. По окончании формирования байта данных блок 6 вырабатывает сигнал запроса -записи, поступающий на вход блока 7 прямого доступа в память. Получив сигнал запроса записи, блок 7 осуществляет захват группы 15 шин, предварительно определив, что дополнительная группа шин не используется каким-либо другим блоком станции, например блоком 4 сопряжения с ЭВМ или блоком 2 соп- ряжения шин. Захватив дополнительную группу 15 шин, блок 1 формирует сигнал подтверждения записи, поступающий в блок 6. При получении этого сигнала байт данных с информационных выходов блока б поступает на шину 17 данных и блок б сбрасывает сигнал запроса записи.

Затем одновременно с адресных выходов блока 7 и блока 8 поиска СРО- бодных страниц на шину 16 адреса поступает код адреса ячейки памяти, по которому производится запись байта данных. Код адреса состоит из двух частей: кода адреса внутри страницы,, сформированного блоком 7 и поступающего на цепи младших разрядов шины 16 адреса, и кода номера страницы, сформированного блоком 8 поиска свободных страниц и поступающим на цепи старших разрядов шины 16 адреса.

Затем блок 7 вырабатывает сигнал Запись, который поступает на цепь шины 18 управления. На адресный и информационные входы блока 5 буферной памяти поступают соответственно код адреса ячейки памяти с шины 16 адреса и байт данных с шины 17 данных. При поступлении на управляющий вход блока 5 буферной памяти с шины 18 управления сигнала Запись происходит запись байта данных по указанному адресу, В момент окончания записи блок 7 сбрасывает сигнал подтверждения записи. По сбросу этого сигнала в блоке 7 происходит увеличение значения адреса внутри страницы на единицу, тем самым подготавливается адрес внутри страницы для следующего байта данных. Затем блок 7 освобождает группу 15 шин, что делает ее доступной для других блоков станции. Параллельно с этим блок 6 осуществляет прием битовой информации, поступающей с выхода приемопередатчика 9, и формирование следующего байта данных. При поступлении на вход

блокл / следу Hi1; iix e u кзлОи .запрос., записи процедура -загисч бяъюв в блок 5 буферной ПРМТН происходит с; аналогично,

кадра и ля.чгоъ сформирован- ннх из него бачке1 5 буферной памяти прочсхр шг ;к 5, передачи л мопоклт ЛТ , Госте чтого

O блок 6 проверяет iiv:; -пь -юс ь приема (по ПОЛЧНОУШПЛЫЮЧ КОНТРОЛЬНОЙ сумме) ч п пучрэ РОГПЗПТ,ноге дпср -ечнл г-01 чруе | спсюч,- шя, гочсржгшпт чкС ормаг.пю о нормаль5 ном завершении операции яаппсн и о номере запоггпегто гтрргнцм блока 5 буферной памяти; cbopnunveT сигнал пре- прсрилэтпщ, котгр г РГ-ХО П блока .6 поступаем на ;гч 1 Р. d гпчп 18 уп0 равления , г. ситгал конча записи, который с ЯРХОПЗ блока 6 поступает на входы блока 7 и бпска 8 поиска свободных страшщ.

По сигналу конца записи в блоке 7

5 восстанавливается значение начального адреса внутри страницы, а блок 8 поиска свободных страниц маркирует заполненную страницу в блоке 10 памяти свободных страниц KJK занятую и

0 находит новую свободную страницу. В результате на входе этого блока формируется сигнал наличия свободных страниц. Таким образом, благодаря , указанному механизму взаимодействия

5 между блоком 8 поиска свободных

страниц, блоком 10 памяти свободных страниц, блоком 7 и блоком 6 станция обеспечивает прием блока данных из моноканала, состоящего из нескольких

0 кадров, следующих синхронно одни ча другим с минимальными временными интервалами.

Одновременно с приемом следующего кадра данных в свободную страницу

5 блока 5 буферной памяти происходит обработка сигнала прерывания. Указанный сигнал по цепи 18.6 шины 18 управления поступает ia вход блока 2 сопряжения пин. Почучпв его, блок

0 2 сопряжения мин прерывает выполнение программы микропроцессором I и переводит ее на обработку принятого кадра. Микропроцессор 1 через блок 2 сопряжения шин и группу 15 шик обра5 щается к блоку 6, считывает сформированный байт состояния, обрабатывает принятый кадр информации и запускает работу блока 4 сопряжения с ЭВМ.

9147822110

Для инициализации чтения данных . си этой информации указанный блок вы- нз нулевой страницы блока 5 буферной рабатывает сигнал прерывания, посту

| название | год | авторы | номер документа |

|---|---|---|---|

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Станция локальной сети | 1990 |

|

SU1824640A1 |

| Устройство для обработки видеоинформации | 1988 |

|

SU1640714A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1983 |

|

SU1141418A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1254498A2 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к цифровой вычислительной технике, может быть использовано для организации взаимодействия между компонентами сетей и систем. Цель изобретения - повышение производительности станции, обеспечивающей работу устройства с высокоскоростными каналами связи, например с моноканалом, в котором скорость передачи данных 10 Мбит/с. Станция содержит блок управления обменом (микропроцессор), блок памяти программ, блок сопряжения с ЭВМ, блок сопряжения с каналом связи, приемопередатчик, блок прямого доступа в память, блок буферной памяти, блок поиска свободных страниц, блок сопряжения шин, блок памяти свободных страниц. Введение новых блоков и связей позволяет совместить по времени три основных процесса, определяющих производительность /пропускную способность/ станции: прием данных /из канала связи или от ЭВМ/, обработку данных в соответствии с системой протоколов сети и передачу данных /в ЭВМ или в моноканал/. 6 з.п. ф-лы, 7 ил.

памяти в ЭВМ микропроцессор 1 , используя блок 2 сопряжения шин и группу 15 гаин, обращается к блоку 4 сопряжения с ЭВМ и записывает в него начальный адрес памяти, состоящий из кода нулевой страницы и кода адреса внутри страницы, и затем определенную информацию, указывающую на необходимость выполнения операции чтения данных и последующей выдачи в ЭВМ, Факт записи этой информации вызывает появление на выходе блока 4 сопря- 15 ряжения с ЭВМ. В этой информации

жения с ЭВМ сигнала прерывания, поступающего по цепи запроса прерывания интерфейса Общая гаина в СМ ЭВМ. Обрабатывая прерывание, СМ ЭВМ считывает с информационных выходов блока 4 сопряжения с ЭВМ указанную информацию, которая по шине 22 данных поступает в СМ ЭВМ, Проанализировав эту информацию, СМ ЭВМ запускает блок 4 сопряжения с ЭВМ на выполнение операции чтения памяти. Блок 4 сопряжения с основной ЭВМ захватывает группу 15 шин, код начального адреса памяти с адресного

35

выхода блока 4 сопряжения с ЭВМ выда- JQ мяти 10 свободных страниц маркируется как свободная.

Таким образом, возможно одновременное и независимое выполнение трех основных процедур в станции: прием очередного кадра из моноканала и размещение его в .свободной странице блока 5 буферной памяти; обработка микропроцессором 1 принятых кадров; передача блоком 4 сопряжения с ЭВМ об- 4Q работанных микропроцессором 1 кадров из блока 5 буферной памяти в ЭВМ.

Рассмотрена работа станции при поступлении одного кадра данных из моноканала и его передаче в ЭВМ.

45 В реальной работе поток данных, поступающий из моноканала, состоит из нескольких кадров. Указанный механизм взаимодействия между блоком 7 блоком 8 поиска свободных страниц, блоком 10 памяти свободных страниц и блоком 5 буферной памяти позволяет производить внепроцессорную запись поступающих кадров данных, обеспечивая получение всех кадров, преднаэjc наченных данной станции. Рабочая

программа, находящаяся в блоке 3 памяти, реализует определенную систему протоколов вычислительной сети. Окончание приема каждого кадра данных выется на шину 16 адреса и с шины 16 адреса поступает на адресный вход блока 5 буферной памяти. Затем блок 4 сопряжения с ЭВМ вырабатывает сигнал Чтение, поступающий на цепь 18,1 шины 18 управления. С этой цепи указанный сигнал поступает на управляющий вход блока 5 буферной памяти. Байт данных, записанный по указанному адресу, поступает с информационных выходов блока 5 буферной памяти на шину 17 данных. С шины 17 данных байт данных поступает на информационные входы блока 4 сопряжения с ЭВМ, записывается в указанном блоке и затем с информационных выходов по шине 22 данных поступает в СМ ЭВМ. В блоке 4 сопряжения с ЭВМ производится увеличение начального адреса памяти на единицу. Чтение следующих байтов данных из блока 5 буферной памяти происходит указанным образом.

О завершении операции чтения СМ ЭВМ указывает микропроцессору 1 следующим образом. СМ ЭВМ записывает в блок 4 сопряжения с ЭВМ определенную информацию, поступающую на информационные входы блока 4 сопряжения с ЭВМ с тины 22 данных. По факту запи50

пающий на цепь 18.5 шины 18 управления и затем с этой цепи поступающий на вход блока 2 сопряжения гаин. Получив сигнал прерывания, блок 2 сопряжения гаин прерывает выполнение программы микропроцессором 1 н переводит ее на обработку прерывания. Обрабатывая прерывание, микропроцессор 1, используя блок 2 сопряжения гаин и группу 15 шин, считывает указанную информацию из блока 4 сопуказано, что данные, поступившие из моноканала и хранившиеся в нулевой странице, переданы в ЭВМ. Проанализировав эту информацию, микропроцессор 1, используя блок 2 сопряжения шин и группу 15 гаин, приступает к освобождению нулевой страницы. Для этого микропроцессор 1 записыпа- ет в блок 8 поиска свободных страниц

код нулевой страницы. По факту записи кода в блоке 8 поиска свободных страниц запускается процесс освобождения страницы, в результате выполнения которого нулевая страница в па35

4Q

45

50

1 i

зывает прерывание от блока 6. Рабочая программа формирует очередь из полученных от блока б прерываний. Ряд кадров, получаемых из моноканала выполняет служебные функции и не требует передачи в ЭВМ. В промежутка между поступлением кадров из моноканала рабочая программа выбирает первое в порядке поступления прерывание из очереди полученных прерываний от блока б и производит обрзбот- ку-соответствующего ему кадра. Для этого микропроцессор 1, работающий под управлением рабочей программы, через блок 2 сопряжения шин и группу 15 шин получает доступ к странице, номер которой указан в этом пре рывании, и считывает определенную информацию. Получив эту информацию, рабочая программа определяет тип кадра (служебный или информационный) Если кадр информационный, то инициализируется работа блока 4 сопряжения с ЭВМ, и начинается выдача обработанного кадра данных из блока 5 буферной памяти. После выдачи кадра данных в ЭВМ производится освобождение страницы, в которой этот кадр размещен.

Рассмотрим режим выдачи информации из ЭВМ в моноканал.

ЭВМ, имея блок данных для передачи в моноканал, выдает информацию на шину 22 данных, которая поступает на вход блока 4 сопряжения с ЭВМ. Затем эта информация записывается в указанный блок. По факту записи этой информации блок 4 сопряжения с ЭВМ вырабатывает сигнал прерывания, поступающий на цепь 18.5 шины 18 управления. Данный сигнал с цепи 18.5 шины 18 управления поступает на вход блока 2 сопряжения шин. Получив этот сигнал, блок 2 сопряжения шин прерывает выполнение рабочей программы микропроцессором 1 и переводит ее на обработку полученного прерывания. Обрабатывая прерывание, микропроцессор 1, используя блок 2 сопряжения шин и группу 15 шин, произво- дит считывание этой инициативной информации из блока 4 сопряжения с ЭВМ. Микропроцессор 1, определив по считанной информации наличие в ЭВМ блока данных для выдачи в моноканал, производит следующие действия. Используя блок 2 сопряжения шин и группу 15 шин, записывает в блок 4 сопря822112

женин с ЭВМ члчттт, Л ггтрс г ЛРМЯТН, состоящий ит номера свободной стра- нчиы части блока 5 буферной памяти, ппслназначеннгй для приема данных из ЭВМ5 и адреса внутри страницы, и затем записывает определенную информацию По фпкту яапнси ттой информации блок 4 сотряс ешш с ЭВМ выра- 10 батьшает сигнал прорыв РЧШЯ. Сигнал прерывания с выхоца блока 4 сопряжения с ЭВМ поступает в шину 20 управления, а затем г, г.сс - з ЭВМ. Обрабатывая прерпп1кпг, ЗГ-М считывают эту информацию, которая с выхода блока 4 сопряжения с ЭВМ поступает на шину 22 даннь ь атсм с нее в ЭВМ. По полученной информации ЭВМ определяет, что станция готова к записи

0

5

0

5

0

5

0

5

данных в блок 5 буферной памяти. ЭВМ выдает на глшу 22 данных байт данных С шичы 22 бпнт данкуч поступает в блок 4 сопряжения с ЭВМ Затем блок 4 сопряжения с ЭВМ захватывает группу 15 шин, с адресных выходов этого блока на шину 16 адреса поступает начальный адрес памяти, а па пину 17 данных - байт данных, принятый из ЭВМ. Затем блок 4 сопряжения с ЭВМ формирует сигнал Запись, поступающий с выхода блока на цепь 18,2 шины 18 управления. На адресный и информационный входы блока 5 буферной памяти поступает адрес ячейки памяти и байт данных с шин адреса 16 и данных 17 соответственно. При поступлении сигнала Запись с цепи 18.2 шины 18 управления на вход блока 5 буферной памяти происходит запись байта данных в блок 5 буфер ной памяти. В момент окончания операции записи в блоке 4 сопряжения с ЭВМ происходит увеличение значения начального адреса памяти на единицу, тем самым подготавливается значение адреса памяти для записи следующего байта данных. Затем блок 4 сопряжения с ЭВМ освобождает группу 15 шин. Запись следующих байтов данных происходит указанным образом.

После окончания записи данных в указанную страницу блока 5 буферной памяти ЭВМ помещает на шине 22 данных информацию, указывающую на окончание записи в яту страницу. Эта информация с шины 22 данных поступает на вход блока 4 сопряжения с ЭВМ и затем записывается в нем. По факту записи этой информации блок 4 сопряжения с ЭВМ вырабатывает сигнал прерывания поступающий с выхода этого блока на цепь 18.5 шины 18 управлени Данный сигнал с цепи 18.5 шины 18 управления поступает на вход блока 2 сопряжения шин. Получив этот сигнал, блок 2 сопряжения шин прерывает выполнение рабочей программы микропроцессором 1 и переводит ее на обра- ботку полученного прерывания. Обрабатывая прерывание, микропроцессор 1, используя блок 2 сопряжения шин и группу 15 шин, производит считывание указанной информации из блока 4 соп- ряжения с ЭВМ. В этой информации содержится номер заполненной страницы блока 5 буферной памяти. Затем микропроцессор 1 обрабатывает принятый блок данных и подготавливает выдачу его в моноканал. Для этого микропроцессор 1 через блок 2 сопряжения шин и группу 15 шин записывает и блок 7 значение начального адреса памяти,

состоящего из номера страницы, содер- 25 да чтения. Указанный сигнал с выхожащей данные, полученные из ЭВМ, и значения длины блока данных Блок 7, получив эти данные, формирует сигнал наличия данных, предназначенных для выдачи в моноканал. С выхода блока 7 указанный сигнал поступает на вход блока 6. Если блок 6 готов к выдаче данных в моноканал, то он формирует сигнал запроса чтения. Указанный сигнал с выхода блока 6 поступает на вход блока 7.

Блок 7 захватывает группу 15 шин, формирует сигнал подтверждения чтения, который с выхода указанного блока поступает на вход блока 6. С адресных выходов блока 7 па шину 16 .адреса поступает первый (начальный) адрес формируемой последовательности адресов байтов данных. Затем блок 7 формирует сигнал Чтение, поступающий с выхода указанного блока на цепь 18.1 шины 18 управления. С шины 16 адреса начальный адрес поступает на адресный вход блока 5 буферной памяти. При поступлении на управляющий вход блока 5 буферной памяти с цепи 18.1 шины 18 управления сигнала чтения байт данных, записанный по начальному адресу, поступает с информационных выходов блока 5 буферной памяти на шину 17 данных. С шины 17 данных байт данных nocTvna- ет на информационный вход блока 6. Получив сигнал подтверждения чтения,

блок 6 сбрасывает сигнал запроса чтения. Блок 7 сбрасывает сигнал подтверждения чтения. По заднему фронту сигнала подтверждения чтения байт данных 1 записывается в блок 6. В блоке 7 происходит увеличение значения начального адреса на единицу и уменьшение на единицу значения длины блока. Блок 7 освобождает группу 15 шин. На этом заканчивается обслуживание запроса на чтение байта и блок 7 готов к приему следующего запроса.

Блок 6 начинает побитовую выдачу принятого байта через приемопередатчик 9 в моноканал и формирует новый сигнал запроса чтения, который вызывает следующий цикл в работе блока 7. Следующие циклы выполняются также, как указано. После выдачи всего блока данных блок 7 сбрасывает сигнал наличия данных для выдачи в моноканал и формирует сигнал кон0

5

0

5

0

5

да блока 7 поступает на вход блока 6. При поступлении этого сигнала блок 6 формирует байт состояния, содержащий информацию о нормальном завершении операции выдачи данных в моноканал и сигнал прерывания, который с выхода блока 6 поступает на цепь 18.6 шины 18 управления.

Сигнал прерывания с цепи 18.6 шины 18 управления поступает на вход блока 2 сопряжения шин. Получив его, блок 2 сопряжения шин прерывает выполнение программы микропроцессором 1 п переводит ее на обработку прерывания от блока 6, Микропроцессор 1 через блок 2 сопряжения шин и группу 15 шин обращается к блоку 6, считывает сформированный байт состояния. Затем рабочая программа помещает номер освобожденной страницы f блока 5 буферной памяти в таблицу свободных страниц, предназначенных для приема данных из ЭВМ. Данная

таблица размещается в блоке 3 памяти.

i

Блок 2 сопряжения шин обеспечивает энергетическое и логическое сопряжение группы 11 и 15 шин. Блок 2 сопряжения шин обеспечивает доступ микропроцессора 1 к любой странице блока 5 буферной памяти, а также к блоку 4 сопряжения с ЭВМ, блокам 6. и 7 и блоку 8 поиска свободных страниц. Для нормального функционирования станции необходимо взаимодействне между микропроцессором 1 с одной стороны и блоком 4 сопряжения с ЭВМ, блоком 6, блоком 8 поиска свободных страниц и блоком 7, с другой стороны. Это взаимодействие осуществляется посредством регистров, находящихся в указанных блоках. Эти регистры через блок 2 сопряжения шин доступны микропроцессору 1, т.е. микропроцессор 1 может записывать в них определенную информацию или считывать определенную информацию, необходимую для обеспечения передачи данных между ЭВМ и моноканалом. Для выполнения операций записи- чтения с любой страницей блока 5 буферной записи микропроцессор 1 прежде всего обращается к регистру 40

ваготся, и код номера страницы, поступающий с выхода регистра 40 страниц на информационный вход шинного формирователя 41, и код адреса ячейки внутри страницы, поступающий с гаи ны 12 адреса на информационный вход шинного формирователя 38, транслируются на шину 16 адреса группы 15 шин

При выполнении операции записи в блок 5 буферной памяти одновременно с адресных и информационных выходов микропроцессора 1 поступают код адреса ячейки внутри страницы и- 15 данные, которые нужно записать по данному адресу на шипы адреса 12 и данных 13,соответственно. С шины 13 данных данные поступают на информационный вход шинного формирователя

10

страниц и записывает в него код номе- 20 На пеРвьп 1 Управляющий вход шинного формирователя 32 в течение выра страницы с которой выполняется операция записи-чтения.

С адресных выхоцов микропроцессора 1 на шину 12 адреса поступает код адреса регистра 40 страниц. С шины

12адреса этот код поступает на вход дешифратора 42 адреса. На первом выходе дешифратора 42 адреса появляется сигнал разрешения занесения, поступающий на первый управляющий вход регистра 40 страниц К моменту появления сигнала разрешения занесения с информационных выходов микропроцессора 1 на шину 13 данных поступает код номера страницы, с которой выполняется операция записи-чтения. С шины

13данных код номера страницы поступает на третий информационный вход регистра 40 страниц. Затем микропроцессор 1 выдает сигнал Запись, поступающий на цепь 14.6 шины 14 управления. Сигнал Запись с цепи 14.6 шины 14 управления поступает на второй управляющий вход регистра

40 страниц. При появлении этого сигнала код номера страницы запоминается в регистре 40 страниц.- Затем с адресного выхода микропроцессора 1 на шину 12 адреса в течение цикла записи-чтения поступает код адреса ячейки внутри страницы. С шины 12 адреса этот код поступает на вход дешифратора 42 адреса и информационный вход шинного формирователя 38, На управляющие входы шинных формирователей 38 и 41 с второго выхода дешифратора 42 адреса поступает сигнал разрешения подключения к шине. Шинные формирователи 38 и 41 откры30

35

полпенни цикла записи, как и на упра ляющий вход усилителя-передатчика 35, поступает сигнал разрешения под- 25 ключения к шине. Затем микропроцессор 1 выдает сигнал Запись, поступающий на цепь 14.4 шины 14 управления. С цепи 14.4 сигнал поступает на первый вход элемента ИЛИ 33. Сигнал с выхода последнего поступает на второй управляющий вход шинного формирователя 32. Шинный формирователь 32 открывается и данные с выхода его поступают на шину 17 данных группы 15 шин. Сигнал Запись также поступает на второй вход усилителя-передатчика 35. Усилитель-передатчик 35 транслирует сигнал Запись с выхода на выход, так как на первый вход пос тупает сигнал разрешения подключения к шине. Сигнал с выхода усилителя- передатчика 35 поступает на цепь 18.2 шины 18 управления группы 15 шин„ На адресный и информационный входы блока 5 буферной памяти поступ ют соответственно код адреса ячейки памяти с шины 16 адреса и данные с шины 17 данных. При поступлении на управляющий вход блока 5 буферной памяти с цепи 18.2 шины 18 управления сигнала происходит запись данных по указанному адресу.

40

45

50

При выполнении операции чтения данных из блока 5 буферной памяти 55 выдача адреса, по которому производится считывание информации, на шину 16 адреса блоком 2 сопряжения шин происходит так же, как для операции записи. Затем микропроцессор 1 выдаваготся, и код номера страницы, поступающий с выхода регистра 40 страниц на информационный вход шинного формирователя 41, и код адреса ячейки внутри страницы, поступающий с гаи- ны 12 адреса на информационный вход шинного формирователя 38, транслируются на шину 16 адреса группы 15 шин.

При выполнении операции записи в блок 5 буферной памяти одновременно с адресных и информационных выходов микропроцессора 1 поступают код адреса ячейки внутри страницы и- данные, которые нужно записать по данному адресу на шипы адреса 12 и данных 13,соответственно. С шины 13 данных данные поступают на информационный вход шинного формирователя

0

5

полпенни цикла записи, как и на управляющий вход усилителя-передатчика 35, поступает сигнал разрешения под- 5 ключения к шине. Затем микропроцессор 1 выдает сигнал Запись, поступающий на цепь 14.4 шины 14 управления. С цепи 14.4 сигнал поступает на первый вход элемента ИЛИ 33. Сигнал с выхода последнего поступает на второй управляющий вход шинного формирователя 32. Шинный формирователь 32 открывается и данные с выхода его поступают на шину 17 данных группы 15 шин. Сигнал Запись также поступает на второй вход усилителя-передатчика 35. Усилитель-передатчик 35 транслирует сигнал Запись с выхода на выход, так как на первый вход поступает сигнал разрешения подключения к шине. Сигнал с выхода усилителя- передатчика 35 поступает на цепь 18.2 шины 18 управления группы 15 шин„ На адресный и информационный входы блока 5 буферной памяти поступают соответственно код адреса ячейки памяти с шины 16 адреса и данные с шины 17 данных. При поступлении на управляющий вход блока 5 буферной памяти с цепи 18.2 шины 18 управления сигнала происходит запись данных по указанному адресу.

0

5

0

При выполнении операции чтения данных из блока 5 буферной памяти выдача адреса, по которому производится считывание информации, на шину 16 адреса блоком 2 сопряжения шин происходит так же, как для операции записи. Затем микропроцессор 1 выда171478221

ет сигнал Чтение, поступающий на цепь 14.2 шины 14 управления. В указанной цепи сигнал поступает на второй вход усилителя-передатчика 34. Усилитель-передатчик 34 открывается и сигнал с его выхода поступает на цепь 18,1 шины 18 управления группы 15 шин. На адресный вход блока 5

буферной памяти поступает адрес с гаи- ю 32 открывается и данные с его выхода

ны 16 адреса. При поступлении на вход блока 5 буферной памяти сигнала с цепи 18.1 ганны 18 управления данные, записанные по указанному адресу, поступают с информационных выходов 15 блока 5 буферной памяти на шину 1 7 данных. С шипы 17 данных данные поступают на информационный вход регистра 30. Сигнал Чтение с цепи 14.2 шины 14 управления также посту- 20 пает на первый вход элемента ШШ 31. Сигнал с выхода элемента ШШ 31 поступает на управляющий вход регистра 30. По этому сигналу данные, поступающие на информационный вход регистра 25 30, запоминаются в нем. Сигналы с выхода регистра 30 поступают на информационный вход шинного формирователя 29, на первый и второй управляющие входы которого поступают сигнал 30 разрешения подключения к шине и сигнал с выхода элемента ИЛИ 31 соответственно. Шинный формирователь 29 открывается и данные поступают на шину 13 данных, а затем с нее - на информационный вход микропроцессора 1.

При выполнении операции записи данных в регистр, находящийся,например, в блоке 8 поиска свободных страниц, блок 2 сопряжения шин работает 40 следующим образом. Одновременно с адресного и информационного выходов микропроцессора 1 поступают код адреса регистра и данные, которые нужно записать в этот регистр, на шины д5 адреса 12 и данных 13 соответственно. С шины 12 адреса код адреса регистра поступает на вход дешифратора 42 адреса и информационный вход шинного формирователя 38, Сигнал разреше - вд ния подключения к шине с второго выхода дешифратора 42 адреса поступает на управляющий вход шинного формирователя 38, который открывается. Код адреса регистра с информационного „ входа шинного формирователя 38 транслируется на шину 16 адреса группы 15 шин. Затем микропроцессор Г выдает сигнал Запись, поступающий на цепь

35

поступают на шину 17 данных группы 15 шин. Сигнал с цепи 14,6 поступает на второй вход усилителя-передатчика 37, на первый вход которого поступает сигнал .разрешения подключения к шине. Усилитель-передатчик 37 открывается и на его выходе появляется сигнал, поступающий на цепь 18.1 шины 18 управления группы 15 шин. На адресный и информационный входы блока 8 поиска свободных страниц поступают соответственно код адреса регистра с шины 16 адреса и данные с шины 17 данных. При поступлении на вход блока 8 поиска свободных страниц сигнала с цепи

При выполнении операции чтения регистра, находящегося, например, в блоке 6, блок 2 сопряжения шин работает следующим образом. С адресного выхода микропроцессора 1 на шину 12 адреса поступает код адреса регистра, а с гаины 12 адреса код адреса - на вход дешифратора 42 и информационный вход шинного формирователя 38. Сигнал разрешения подключения к шине с второго выхода дешифратора 42 адреса поступает на управляющий вход шинного формирователя 38, который открывается. Код адреса регистра с информационного входа шинного формирователя 38 транслируется на шину 16 адреса группы 15 шин. Затем микропроцессор 1 выдает сиг- пал Чтение, поступающий на цепь

0 5 0

0 5

5

поступают на шину 17 данных группы 15 шин. Сигнал с цепи 14,6 поступает на второй вход усилителя-передатчика 37, на первый вход которого поступает сигнал .разрешения подключения к шине. Усилитель-передатчик 37 открывается и на его выходе появляется сигнал, поступающий на цепь 18.1 шины 18 управления группы 15 шин. На адресный и информационный входы блока 8 поиска свободных страниц поступают соответственно код адреса регистра с шины 16 адреса и данные с шины 17 данных. При поступлении на вход блока 8 поиска свободных страниц сигнала с цепи

При выполнении операции чтения регистра, находящегося, например, в блоке 6, блок 2 сопряжения шин работает следующим образом. С адресного выхода микропроцессора 1 на шину 12 адреса поступает код адреса регистра, а с гаины 12 адреса код адреса - на вход дешифратора 42 и информационный вход шинного формирователя 38. Сигнал разрешения подключения к шине с второго выхода дешифратора 42 адреса поступает на управляющий вход шинного формирователя 38, который открывается. Код адреса регистра с информационного входа шинного формирователя 38 транслируется на шину 16 адреса группы 15 шин. Затем микропроцессор 1 выдает сиг- пал Чтение, поступающий на цепь

ны 16 адреса. При поступлении на вход блока б сигнала с цепи 18.3 шины 18 управления содержимое -регистра с информационного выхода блока 6 поступает на шину 17 данных. С шины 17 данных данные поступают на информационный вход регистра 30. Сигнал Чтение с цепи 14.5 шкны 14 управления также поступает на второй вход элемента ИЛИ 31,, а затем на управляю- щий вход регистра 30. Поэтому сигнал данные, поступакшдие на информационный вход регистра 30, запоминаются в нем. Сигналы с выхода регистра 30 поступают на информационный вход шинного формирователя 29, на первый и второй управляющие входы которого потупают сигнал разрешения подключения к шине и сигнал с выхода элемента ИЛИ 31 соответственно. Шинный формирователь 29 открывается, данные поступают на тайну 13 данных и затем на информационный вход микропроцессора

Запросы прерывания от блока 4 соп ряжения с ЭВМ и от блока 6 поступают в узел 39 прерывания, который фиксирует наиболее приоритетный в настоящий момент запрос прерывания. Затем формирует сигнал, который с выхода узла 39 поступает на цепь 14.3 шины управления. Получив сигнал прерывания, микропроцессор 1 формирует сигнал подтверждения прерывания, поступающий на цепь 14.1 шины 14 управления. Сигнал с цепи 14.1 шины 14 управления поступает на вход узла 39. При получении сигнала с информационного выхода узла 39 на шину 13 данных поступает код, соответствующий номеру наиболее приоритетного прерывания. С шины 13 данных этот код затем поступает на информационный вход микропроцессора 1. В результате этого идентифицируется выдавший прерывание блок и управление передается соответствующей программе обслуживания прерывания. Обрабатывая прерывание, микропроцессор 1 производит чтение регистра идентифицируемого блока.

Таким образом, блок 2 сопряжения шин обеспечивает доступ микропроцессора 1 к любой странице блока 5 бу

ферной памяти и регистрам, находящим- 55 B единичное состояние триггер 49, ся в блоках станции, для получения Отрицательный импульс сброса также опр-еделенной информации, необходимой поступает на входы элементов НЕ 51 и для нормального выполнения рабочей программы, реализующей определенную

И 54. При этом на выходе элемента И 54 формируется отрицательный им10

15

20

.

25

7822120

систему протоколов пт,пшслительной сети. Блок 2 сопряжения пин занимает группу 15 шип только на время выполнения одной или нескольких one- раций записи-чтения, т.о. группа 15 шин практически используется только для передачи данных между моноканалом и основной ЭВМ, что позволяет существенно увеличить nponyciaryro способность станции. При выполнении рабочей программы, за исключением моментоя обращения микропроцессора 1 к страницам блока 5 буферной памя - ти и регистрам блоков 6 станции, обмен командами и данными между микропроцессором 1 и блоком 3 памяти происходит по группе 11 пни. Блок 8 поиска свободных страниц, используя блок 10 памяти свободных страниц, совместно с блоком 7 обеспечивает запись кадров данных, получаемых из моноканала, в блок 5 буферной памяти.

Блок 8 поиска свободных страниц совместно с блоком 7 прямого доступа в память формируют последовательность адресов блока 5 буферной памяти, в которых разместятся байты данных, f сформированные блоком б из кадра, получаемого из моноканала. Код адреса ячейки памяти состоит из двух частей: кода адреса внутри единицы, сформированного блоком 7 и поступающего на цепи младших разрядов шины 16 адреса, и кода номера страницы, сформированного блоком 8 поиска- . свободных страниц и поступающим на цепи старших разрядов шин 16 адреса.

Кадр данных, получаемый из моно30

35

40

канала, размещается в свободной странице части блока 5 буферной памяти, предназначенной для приема данных из моноканала. В блоке 10 памяти сво,: бодных страниц хранится информация о наличии свободных страниц.

Блок 8 поиска свободных страниц работает следующим образом. По отрицательному импульсу сброса при включении питания станции по входу сброса устанавливается в исходное (нулевое) состояние триггер 45, по установочному входу устанавливается

B единичное состояние триггер 49, Отрицательный импульс сброса также поступает на входы элементов НЕ 51

И 54. При этом на выходе элемента И 54 формируется отрицательный им211478221

пульс, поступающий на вход сброса ре- с

5 е

гистра 47 номера освобождаемой страницы и устанавливающий регистр 47 номера освобождаемой страницы в исходное состояние. На выходе элемента НЕ 51 формируется положительный импульс. Этот импульс поступает на вход сброса счетчика 57 и устанавливает его в исходное .(нулевое) состояние. По окончанию действия отрицательного импульса сброса с прямого выхода триггера 49 по цепи 26 на вход блока б поступает сигнал, равный единице и указывающий о наличии свободной страницы в блоке 5 буферной памяти.

Содержимое (код нулевой страницы) счетчика 57 номера страницы по цепям 26 j ,, поступает на вход блока 6. Наличие этих сигналов является необходимым и достаточным условием для записи в свободной (нулевой) странице блока 5 буферной памяти кадра данных, поступающего из канала.

Содержимое счетчика 57 номера страницы также поступает на информационные входы шинного формирователя 58, информационные выходы которого подсоединены к цепям старших разрядов шины 16 адреса. Содержимое счетчика 57 номера страницы транслируется на информационные выходы шинного формирователя 58, т.е. поступает на шину 16 адреса, только при появлении сигнала подтверждения записи, вырабатываемого блоком 7 при выполнении операции записи байта данных в блок 5 буферной памяти.

При получении от блока 6 по цепи 26j отрицательного импульса конца записи, сообщающего блоку 8 поиска свободных страниц о завершении записи в блок 5 буферной памяти, устанавливается в единичное состояние триггер 45. Одновременно этот импульс устанавливает в нулевое состояние триггер 49. Сигнал, равный единце, с прямого выхода триггера 45 поступает на второй вход элемента И-НЕ 55, а также на второй вход формирователя 53, запуская его. На выходе формирователя 53 формируется положительный импульс, который поступает на вход элемента И-НЕ 55. На выходе элемента И-НЕ 55 появляется отрицательный импульс, поступающий на вход элемента И 60, на другой вход которого поступает сигнал, равный единице,

22

с

инверсного выхода формирователя 50. На выходе элемента И 60 появляется отрицательный импульс записи в

блок 10 памяти свободных страниц,

который по цепи 28. поступает на вход записи блока 10 памяти свободных страниц. Сигнал с выхода регистра 47 поступает на первый управляющий вход мультиплексора 59 и управляет коммутацией сигналов, поступающих на информационные входы мультиплексора 59. Единичное значение сигнала на выходе регистра 47 (номера

освобождаемой страницы), являющееся следствием действия отрицательного импульса сброса, позволяет поступить содержимому (коду нулевой страницы) счетчика 57 номера страницы на выход мультиплексора 59. По цепям

код адреса нулевой страницы,

5

0

5

только что заполненной поступившим из моноканала кадром данных, поступает на адресный вход блока 10 памяти свободных страниц. По цепи 28,2 на вход блока 10 памяти свободных страниц поступает сигнал, равный единице, с прямого выхода триггера 45. По отрицательному импульсу на выходе элемента И 60 происходит запись единицы в ячейку памяти блока 10 памяти свободных страниц, кпд адреса которой (код нулевой страницы) установлен на адресном входе блока 10 памяти свободных страниц. Таким образом, нулевая страница в блоке 10 памяти свободных страниц помечается как занятая.

Выход элемента И-НЕ 55 соединен 0 с С-входом триггера 45 и входом элемента И 48. По заднему положительному фронту отрицательного импульса па выходе элемента И-НЕ 55 триггер 45 перебрасывается в нулевое состояние. 5 Кроме того, на выходе элемента И 48 устанавливается сигнал, равный единице, так как на второй вход его поступает сигнал, равный единице, с выхода элемента И-НЕ 56. В результате этого сигнал на выходе элемента И 52 изменяет сяое значение с нуля на единицу. Сигнал с выхода элемента И 52 поступает на счетный вход счетчика 57 номера страницы, а также на первый вход формирователя 53. Положительный (передний фронт) этого сигнала, изменяет содержимое счетчика 57 номера страницы на единицу,, т.е. в счетчике 57 номера страницы уже содер0

5

231

жится код (следующий) первой страницы, который по цепям 28 поступает на адресный вход блока 10 памяти свободных страниц. Одновременно положительный фронт этого сигнала запускает по первому входу формирователь 53. Выход формирователя 53 соединен с первым входом элемента И-НЕ 56, на второй вход которого поступает единичное значение сигнала с инверсного выхода триггера 45. На выходе элемента И-НЕ 56 формируется отрицательный импульс, который поступает на бинхровход триггера 49 и вход элемента И 48, а также по цепи 28.3 - на вход чтения блока 10 памяти свободных страниц. Код, следующий по порядку первой страницы, уже находится на адресном входе блока 10 памяти свободных страниц. При поступлении на вход чтения блока 10 памяти свобод

ных страниц отрицательного импульса с цепи 28.3 информация, записанная в ячейке памяти, код адреса (код номера страницы) которой уже находится на адресном входе, поступает на выход блока 10 памяти свободных страниц. Сигнал на выходе блока 10 памяти свободных страниц равен нулю, если страница, код номера которой установлен на адресном входе блока 10 памяти свободных страниц, свободна, и равен единице, если страница

заполнена данными из моноканала. Пер- 35 писанного, например, в нулевую

вая страница еще не заполнялась данными из моноканала, поэтому значение указанного сигнала равно нулю.,Сигнал с выхода блока 10 памяти свободных страниц по цепи 27 поступает на вход элемента НЕ 44. Выход элемента 44 соединен с входом триггера 49, т.е. на вход триггера 49 поступает сигнал, равный единице. По окончании отрицательного импульса на выходе элемента И-НЕ 56 по его заднему положительному фронту по синхровходу триггер 49 изменяет свое состояние, т.е. на его прямом выходе появляется сигнал, равный единице. Таким образом, с прямого выхода триггера 49 по цепи 26.1 на вход блока 6 поступает сигнал, равный единице и указывающий блоку 6 о наличии свободной (первой) страницы в блоке 5 буферной памяти. Содержимое (код первой страницы) счетчика 57 (номера страницы) по цепям 26 ve также поступает на вход блока 6. Наличие этих

24

0

сигналов указывает на готовность станции к записи следующего кадра данных, поступающего из моноканала, в свободную первую страницу блока 5 буферной памяти.

В том случае, если первая страница уже заполнена, то по окончании отрицательного импульса на выходе элемента И-НЕ 56 триггер 49 не изменяет своего состояния, так как на его вход с выхода элемента НЕ 44 поступает сигнал, равный нулю. В результ а- те этого сигнал на выходе элемента И 52 изменяет свое значение с нуля на единицу. Положительный (передний) фронт этого сигнала изменяет содержимое счетчика 57 на единицу, т.е. в счетчике 57 содержится код следую щей (второй) страницы. Одновременно положительный фронт этого сигнала запускает по первому входу формирователь 53, тем самым повторяя цикл чтения ячейки памяти блока 10 памяти

5 свободных страниц, код адреса (код номера второй страницы) которой новлен на адресном входе блока 10 памяти свободных страниц. Цикл чтения ячеек блока 10 памяти свободных

0 страниц может быть произведен несколько раз до тех пор, пока не найдется свободная страница.

После выдачи в ЭВМ кадра данных, полученного из моноканала и за-

0

страницу, микропроцессор 1 выполняет освобождение нулевой страницы. Микропроцессор 1, используя блок 2 сопряжения шин, выдает

на шину 16 адреса код адреса регистра 47 номера освобождаемой страниды. С шины 16 адреса код адреса поступает на адресный вход дешифратора 43 адреса, затем на первый вход элемента ИЛИ-НЕ 46, на второй вход которого поступает сигнал с цепи 18.4-шины 18 управления. К моменту поступления сигнала с цепи 12.4 на шине 17 данных уже установлен код номера

освобождаемой (нулевой) страницы,

поступающий с шины 17 данных на информационный вход регистра 47 номера освобождаемой страницы. При поступлении сигнала с цепи 18.4 шины 18

управления сигнал на выходе элемента ИЛИ-НЕ 46 меняет свое значение с нуля на единицу. Сигнал с выхода элемента ИЛИ-НЕ 46 поступает на синхро- вход регистра 47. По положитепьно251478221

му переднему фронту этого сигнала код освобождаемой (нулевой) страницы записывается в регистр 47. Факт записи вызывает изменение сигнала на первом выходе регистра 47. Сигнал на первом выходе регистра 47 становится равным нулю, в результате этого . содержимое регистра 47 номера освобождаемой страницы, поступающее на инфор-ю пями: по одной цепи от приемника посмационный вход мультиплексора 59, транслируется на его выход и затем по цепям 284-9 поступает на адресный вход блока 10 памяти свободных ниц. Изменение сигнала с единицы на нуль на первом выходе регистра 47 запускает формирователь 50. Отрицательный импульс с выхода формирователя 50 поступает на вход элемента

тупают двоичные данные, по второй цепи поступают тактовые сигналы, сопровождающие двоичные данные.

Каждый кадр данных, поступающий 15 из моноканала, содержит преамбулу, располагающуюся в начале кадра. Преамбула представляет собой код 10101010, повторяющийся восемь раз. За преамбулой следует специальное И 60. На выходе элемента И 60 появля- 20 поле, называемое ограничителем качается отрицательный импульс, который ла кадра (ОНК) и имеющее вид 101010М . по цепи 28.1 поступает на вход записи блока 10 памяти свободных страниц. На информационный вход блока 10 памяти свободных страниц поступает сигнал, равный нулю, так как триггер 45 установлен в исходное (нулевое состояние) . При поступлении отрицательного импульса на вход записи, блока 10 памяти свободных страниц в ячейку па- 30 Преамбула необходима для того, чтобы мяти, код которой (код нулевой осво-- приемник приемопередатчика 9 достиг бождаемой страницы) поступает на устойчивого рабочего состояния. В

результате приема кадра на последовательный вход сдвигового регистра 63 поступают биты данных, а на синх- ровход - тактовые импульсы. Занесение и сдвиг битов данных в сдвиговой регистр 63 происходит по переднему положительному фронту каждого тактового импульса. После приема восьми бит сдвиговый регистр 63 заполняется. С выхода этого регистра код, приняЗа ОНК следует адрес получателя (станции) . Адрес станции имеет длину 6 байт. За адресом станции далее идут 25 информационные биты.

Как только приемник приемопередатчика 9 обнаружит передачу в моноканале, то он начинает прием кадра. Приемник начинает принимать преамбулу.

адресный вход, записывается нуль, т.е занятая прежде нулевая страница маркируется как свободная.

После окончания отрицательного импульса, сформированного формирователем 50, на выходе элемента 62 появляется сигнал, равный нулю. Этот сигнал поступает на второй вход элемента И 54, на выходе которого -появляется сигнал, равный нулю и поступающий на вход сброса регистра 47 номера освобождаемой страницы. Регистр 47 номера освобождаемой страницы сбрасывается и на первом выходе его устанавливается сигнал, равный единице. Блок 8 поиска свободных страниц возвращается в исходное состояние.

Таким образом, блок 8 поиска свободных страниц совместно с блоком 10 памяти свободных страниц без вмешательства микропроцессора 1 обеспечивает в промежутках времени между поступлениями кадров данных из моноканала быстрый поиск свободной страницы для записи в нее следующего кадра данных.

35

40

45

50

55

тый из моноканала, поступает на информационный вход регистра 78 данных, а также на селектор 70 начала кадра. Селектор 70 является комбинационной схемой, построенной на элег ментах И и НЕ, предназначенной для определения кода 10101011, содержащегося в сдвиговом регистре 63 и указывающего на начало поступления информационных битов, после его приема. Как только указанная схема обнаружит, что содержимое сдвигового регистра 63 код 10101011, то на его выходе появляется сигнал, равный единице и поступающий на вход триггера 74 приема адреса. Тактовые импульсы поступают на вход элемента НЕ 66, с

1

26

Блок 6 сопряжения с каналом связи обеспечивает прием кадра, поступающего из моноканала через приемопередатчик 9, и выдачу кадра данных из блока 5 буферной памяти через приемопередатчик 9 в моноканал.

Узел приема кадра связан с приемником приемопередатчика 9 двумя цеКаждый кадр данных, поступающий из моноканала, содержит преамбулу, располагающуюся в начале кадра. Преамбула представляет собой код 10101010, повторяющийся восемь раз. За преамбулой следует специальное поле, называемое ограничителем качала кадра (ОНК) и имеющее вид 101010М . Преамбула необходима для того, чтобы приемник приемопередатчика 9 достиг устойчивого рабочего состояния. В

За ОНК следует адрес получателя (станции) . Адрес станции имеет длину 6 байт. За адресом станции далее идут информационные биты.

Как только приемник приемопередатчика 9 обнаружит передачу в моноканале, то он начинает прием кадра. Приемник начинает принимать преамбулу.

5

0

5

тый из моноканала, поступает на информационный вход регистра 78 данных, а также на селектор 70 начала кадра. Селектор 70 является комбинационной схемой, построенной на элег ментах И и НЕ, предназначенной для определения кода 10101011, содержащегося в сдвиговом регистре 63 и указывающего на начало поступления информационных битов, после его приема. Как только указанная схема обнаружит, что содержимое сдвигового регистра 63 код 10101011, то на его выходе появляется сигнал, равный единице и поступающий на вход триггера 74 приема адреса. Тактовые импульсы поступают на вход элемента НЕ 66, с

выхода которого инвертированные тактовые импульсы поступают на синхро- вход триггера 74 приема адреса. Как только на выходе селектора 70 появится сигнал, равный единице, то по положительному (заднему) фронту последнего инвертированного тактового импульса триггер 74 устанавливается в единичное состояние, а на его инверсном выходе появляется сигнал, равный нулю. Этот сигнал поступает на входы сброса счетччка 64 бит и счетчика 65 байт, и разрешает подсчет числа бит, поступающих после установки триггера 74. Счетчики бит

64и байт 65 осуществляют битовую и байтовую синхронизацию поступающих из моноканала данных. Адрес станции имеет длину 6 байт, т„е„ 48 бит. Счетчики бит 64 и байт 65 дол/ты произвести подсчет 48 тактовых импульсов для того, чтобы определить совпадает ли адрес получателя, содержащийся в принимаемом кадре, с собственным адресом станции. Собственный адрес станции содержится в памяти 72. По переднему положительному фронту каждого тактового импульса происходит модификация содержимого счетчиков бит 64 и байт 65

на единицу. Модифицированное значение счетчиков бит 64 и байт 65 сохраняется до прихода следующего тактвого импульса и является двоичным эквивалентом номера текущего бита. Содержимое счетчиков бит 64 и байт

65поступает на адресный вход памяти 72. На выходе памяти 72 появляется значение текущего бита присвоеннго номера станции. Сигнал с выхода памяти 72 поступает на первый вход схемы 77 сравнения, на второй вход которой поступает сигнал с первого выхода сдвигового регистра 63. Если значения текущих битов на входах схемы 77 сравнения совпадают, то на

выходе указанной схемы сигнал равен

i

нулю. Если значения текущих битов н

входах схемы 77 сравнения не совпадают, то на выходе указанной схемы появляется сигнал, равный единице. Сигнал с выхода схемы 77 сравнения поступает на вход триггера 83„ Если сигнал на входе триггера 83 равен единице, то по заднему положительному фронту последнего тактового импульса триггер 83 устанавливается в единичное состояние. На инверсном

выходе этого триггера устанавливается сигнал, ранный нулю. Этот сигнал поступает на вход триггера 85. По

достижении счетчиком 65 байт позиции 48 импульсов на выходе элемента И 73 сигнал становится равным единице, Он поступает на вход триггера 85 приема информации. Так как на

вход триггера 85 приема информации поступает сигнал, равный нулю, то при появлении сигнала па синхровходе тоянне триггера 85 приема информации не изменяется. Таким образом, при

несовпадении адреса, поступающего из моноканала, с собственным адресом станции (триггер 83 установлен в единичное состояние) происходит прием информации в сдвиговой регистр

63, но запись принимаемых данных в блок 5 буферной памяти не осуществляется. Триггер 74 приема адреса и триггер 83 совпадения адреса установлены в единичное состояние в течение приема кадра. Схема определения конца приема кадра, выполненная на формирователях 80 и 82, следит за наличием тактовых импульсов. При отсутствии тактовых импульсов на

запускающем входе формирователя 80 в течение длительности трех тактовых импульсов на выходе формирователя 80 формируется отрицательный импульс, запускающий формирователь 82. На выходе формирователя 82 формируется отрицательный импульс, поступающий на входы сброса триггера 83 и триг- гера 74 и устанавливающий их в исходное (нулевое состояние).

Если адрес станции, поступивший из моноканала, совпадает с собственным адресом станции, то состояние триггера 83 не изменится, т.е. на его инверсном выходе останется сигнал, равный единице. По достижению счетчиком 65 байт позиции 48 .импульсов на выходе элемента И 73 сиг- пал изменит свое значение с нуля на единицу. По положительному фронту

этого сигнала триггер 85 установится в единичное состояние, так как на его вход поступает сигнал, равный единице. После установки в единичное состояние триггера 85 начинается процесс записи информации в блок 5 буферной памяти. Запись информации осуществляется блоком приема кадра совместно с блоком 7 и блоком 8 поиска свободных страниц. Биты дан

ных, поступающие после адреса станции, заносятся в сдвиговой регистр 63 и сдвигаются там по каждому тактовому импульсу. Одновременно тактовые импульсы поступают на вход счетчика 64 бит. Как только содержимое счетчика 64 бит станет равным 7 (принято семь бит данных), на выходе элемент а И 69 сигнал изменит свое значение с нуля на единицу. Этот сигнал поступает на третий вход элемента И 88, на второй вход которого поступает сигнал, равный единице, с прямого выхода триггера 85. При поступлении на первый вход элемента И 88 следующего (восьмого) тактового импульса сигнал на выходе элемента И 88 изменит свое значение с нуля на единицу. Указанный сигнал поступает на синхровходы регистра

78 данных и триггера 87 запроса записи. По положительному фронту этого сигнала восьмибитовый код данных, находящийся в сдвиговом регистре 63 и поступающий на информационный вход регистра 78 данных, записывается в регистре 78 данных, а также устанавливается в единичное состояние триггер 87, так как на его вход и выхода блока 8 поиска свободных страниц по цепи 26.1 поступает сигнал, равный единице и указывающий на наличие свободной страницы в блоке 5 буферной памяти. Сигнал запроса записи с инверсного выхода триггера 87 по цепи 25.1 поступает на вход блока 7. Получив сигнал запроса записи, блок 7 осуществляет захват группы 15 шин и вырабатывает отрицательный сигнал подтверждения записи, который по цепи 25.2 поступает на вход элемента НЕ 84. Единичный сигнал с выхода элемента НЕ 84 открывает шинный формирователь 81, и содержимое регистра 78 данных, поступающее на информационный вход шинного формирователя 81, выдается на шину 17 данных. Блок 7 осуществляет запись этого байта в блок 5 буферной памяти. При поступле нии отрицательного сигнала запроса записи триггер 87 устанавливается в исходное состояние. По завершению записи байта данных в блок 5 буферной памяти в блоке 7 сигнал подтверж дения записи становится равным единице, в результате шинный формирователь 81 закрывается. Параллельно с этим происходит прием следующих бито

данных в сдвиговой регистр 63 и подсчет числа принятых битов в счетчике 64 бит. Как только содержимое счетчика 64 бит станет равным 7, указанный процесс записи следующего байта данных в блок 5 буферной памяти повторится. И так продолжается до тех пор, пока схема определения конца приема кадра не определит конец кадра. В результате этого на инверсном выходе формирователя 82 сформируется отрицательный импульс конца записи, который установит в исходное состояние триггеры 74 и 83. Указанный отрицательный импульс конца записи по цепи 25.3 поступает в блок 7. По этому сигналу в блоке 7 восстанавливается значение начального адреса внутри страницы. На прямом выходе формирователя 82 сформируется положительный импульс, который поступает на вход элемента И-НЕ 89, на второй вход которого поступает сигнал, равный единице, с прямого выхода гера 85. На выходе элемента И-НЕ 89 появляется сигнал конца записи, равный нулю. Этот сигнал с выхода элемента И-НЕ 89 по цепи 26.2 поступает в блок 8 поиска свободных страниц и запускает в нем механизм маркирования занятой принятым кадром страницы и поиска свободной страницы. Отрицательный импульс с инверсного выхода формирователя 82 поступает на первый вход элемента И-НЕ 86, на выходе которого появляется положительный импульс, поступающий на синхровход регистра 68 состояния. На управляющий вход мультиплексора 93 поступает сигнал, равный единице, с прямого выхода триггера 85, В результате этого код номера страницы, поступающий по цепи 26,3.g с выхода блока 8 поиска свободных страниц на первый информационный вход мультиплексора 93, и сигнал, равный единице, с прямого выхода триггера 85 транслируется на выход мультиплексора 93. Полученный таким образом, код поступает на информационный вход регистра 68 состояния. При поступлении на синхровход регистра 68 состояния положительного импульса с выхода И-НЕ 86 этот код записывается в регистр 68 состояния. Одновременно положительный импульс с, выхода элемента И-НЕ 86 устанавливав ет в единичное состояние триггер 75. Сигнал, равный единице, с прямого

31

выхода триггера 75 поступает на вход усилителя-передатчика 76, на выходе которого формируется сигнап прерывания по концу записи кадра, который по цепи 18.5 шины 18 управле ния поступает в блок 2 сопряжения тин. Положительный импульс с выхода элемента И-НЕ 86 также поступает на вход элемента НЕ 90. На выходе элемента НЕ 90 появляется отрицательный импульс, который поступает на вход сброса триггера 85 и сбрасывает триггер 85 в исходное (нулевое) состояние.

Получив сигнал,прерывания, блок 2 сопряжения шин прерывает выполнение программы микропроцессором 1 и переводит ее на обработку принятого прерывания. Обрабатывая принятое прерывание, микропроцессор 1, используя блок 2 сопряжения шин, выполняет следующие действия. С адресных выходов блока 2 сопряжения шин на шину 16 адреса выдается код адреса регистра 68 состояния. С шины 16 адреса код адреса поступает на адресный вход дешифратора 92 адреса. Сигнал с выхода дешифратора 92 адреса поступает на второй вход элемента ИЛИ-НЕ 67, на первый вход которого затем поступает сигнал с цепи 18.3 шины 18 управления. При поступлении сигнала с цепи 18.3 шины 18 управления сигнал на выходе элемента И-НЕ 67 меняет свое значение с нуля на единицу. Сигнал с выхода элемента ИЛИ-НЕ 67 поступает на управляющий вход шинного формирователя 71. Содержимое регистра 68 состояния, поступающее на информационный вход шинного формирователя 71, транслируется на его выход. С, его выхода сформированный байт состояния поступает на шину 17 данных, затем в блок 2 сопряжения шин. Сформированный байт состояния содержит информацию о нормальном завершении операции запипи кадра и номере заполненной страницы блока 5 буферной памяти.

Сигнал с выхода элемента ИЛИ-НЕ 67 также поступает на вход элемента НЕ 91. Отрицательный сигнал с выхода элемента НЕ 91 , поступающий на вход сброса триггера 75 прерывания устанавливает его в исходное (нулевое) состояние.

- 15

20

7822132

Кадр данных, выдаваемый через передатчик приемопередатчика 9 в моноканал, должен содержать-преамбулу, ограничитель начала кадра, за которы-1 ми следуют биты данных, первые 48 из которых представляют собой адрес получателя.

Блок выдачи кадра формирует кадр

Ю из блока данных, предназначенных для выдачи в моноканал, т.е. формирует преамбулу, ограничитель начала кадра, за которым затем следуют данные, получаемые из блока 5 буферной памяти.

При наличии в блоке 5 буферной памяти данных, полученных от основной ЭВМ и предназначенных для выдачи в моноканал, микропроцессор 1 через блок 2 сопряжения шин и группу 15 шин записывает в блок 7 значение начального адреса памяти и значение длины блока. Блок 7, получив эти данные, формирует сигнал наличия дан25 ных. Этот сигнал по цепи,25.5 поступает на синхровход триггера 98. По положительному фронту сигнала наличия данных триггер 98 устанавливается в единичное состояние, После установки в единичное состояние триггера 98 на оба входа элемента И 99 поступают сигналы, равные единице. Сигнал с выхода элемента И 99 является сигналом запроса чтения. Сигнал запроса чтения по цепи 25,7 поступает на вход блока 7. Блок 7 захватывает группу 15 шин, выполняет операцию чтения памяти и формирует сигнал подтверждения чтения, кото4д рый с выхода указанного блока по цепи 25.4 поступает на синхровходы регистра 95 данных и триггера 96. Считанный из блока 5 буферной памяти байт данных с пины 17 данных пос45 тупает на информационный вход регистра 95 данных. При поступлении по цепи 25.4 сигнала подтверждения чтения байт данных заносится в регистр 95 данных и одновременно устанавливается в единичное состояние триггер 96. Сигнал, равный нулю,.с инверсного выхода этого триггера поступает на первый вход элемента И 99. Сигнал на выходе элемента И 99 становится равным нулю. Байт данных хранится в регистре 95 данных до момента окончания выдачи преамбулы и ограничителя начала кадра в передатчик приемопередатчика 9.

30

35

50

55

Одновременно с этим начинается выдача преамбулы кадра. На инверсном выходе триггера 98 появляется сигнал равный нулю. Этот сигнал поступает на входы сброса счетчика 100 бит и счетчика 101. Содержимое счетчика 100 бит и счетчика 101 равно нулю, так как до поступления сигнала наличия данных на их входы сброса посту- пал сигнал, равный единице с инверсного выхода триггера 98в Сигнал, равный нулю, с первого выхода счетчика 100 бит поступает на первый вход элемента И-НЕ 105, на второй вход которого поступает сигнал, равный единице, с выхода элемента И-НЕ 103. На выходе элемента И-ПЕ 105 сигнал равен единице и поступает на первый информационный вход мультиплексора 111. Так как триггер 106 еще не установлен, то сигнал, ранный пулю, с прямого выхода этого триггера поступает на управляющий вход мультиплексора 111 и разрешает прохожде- ние единичного сигнала с первого информационного входа на выход мультиплексора 111. Сигнал с выхода мультиплексора поступает в передатчик приемопередатчика 9. Как только триг гер 98 установится в единичное состояние, то на второй вход элемента И 110 поступит сигнал, разрешающий прохождение тактовых импульсов, поступающих на второй вход этого эле- мента, на выход элемента И 110. Сигнал на выходе мультиплексора 111 представляет собой первый бит преамбулы и при появлении первого же тактового импульса на выходе элемента И 110 этот бит в сопровождении тактового импульса поступит в передатчик приемопередатчика 9. Тактовые импульсы с выхода элемента И 110 поступают в передатчик приемопередатчика 9. Одновременно первый тактовый импульс после установки в единичное состояние триггера 98, поступающий на последовательный вход счетчика 100 бит, производит модификацию со- держимого счетчика 100 бит, на первом выходе которого после первого тактового импульса появится сигнал, равный единице. Этот сигнал поступает на первый вход элемента И-НЕ 105, на выходе которого появляется сигнал равный нулю, так как сигнал на выхо- де элемента И-НЕ 103 не изменил своего значения. Сигнал, равный нулю, с

выхода элемента И-НЕ 105 поступает на первый информационный вход мультиплексора 111. Нулевой сигнал с первого информационного входа транслируется на выход мультиплексора 111. При поступлении второго тактового импульса после установки триггера 98 подготовленный второй бит преамбулы, равный нулю, в сопровождении второго тактового импульса поступит в передатчик приемопередатчика 9. При поступлении третьего тактового импульса после установки в единичное состояние триггера 98 с выхода мультиплексора 1 1 1 ел едущий бит преамбулы равный единице, в сопрово адении так тового импульса поступает в передатчик приемопередатчика 9. Таким образом, при поступлении восьми тактовых импульсов на последовательный вход счетчика 100 бит с выхода мультиплексора 111 в передатчик приемопередатчка 9 поступит код 10103010, Каждый бит этого кода сопровождается тактовым импульсом, поступающим в передатчик приемопередатчика 9. Как только в счетчике 100 бит содержится число 7, то при поступлении следующего восьмого импульса на последовательный вход счетчика 100 бит по заднему отрицательному фронту сигнала на третьем выходе счетчика 100 бит, поступающему на последовательный вход счетчика 101, на первом выходе счетчика 101 установится сигнал, равный единице. Таким образом, счетчик 101 осуществляет подсчет числа октетов (кода 10101010) преамбулы, выданных в передатчик приемопередатчика 9. После выдачи восьми октетов кода 10101010 преамбулы на четвертом выходе счетчика 101 устанавливается сигнал, равный единице. После выдачи последнего бита преамбулы начинается выдача ограничителя начала кадра - кода 10101011. Формирование первых битов ограничителя начала кадра происходит также, как указано. После поступления семи тактовых импульсов ограничителя начала кадра содержимое счетчика 100 бит становится равным 7, поэтому на выходе элемента И 102,появляется сигнал, равный единице. Единичный сигнал с выхода элемента И 02 поступает на вход элемента И-НЕ 103, на другой вход которого поступает единичный сигнал с четвертого выхода счетчика 101 На

выходе элемента И-НЕ 103 появляется сигнал, равный нулю. Этот сигнал поступает на вход элемента И-НЕ 105. На выходе элемента И-НЕ 105 устанавливается сигнал, равный единице. При поступлении следующего тактового импульса последний бит ограничителя начала кадра, равный единице, поступит в передатчик приемопередатчика 9

Тактовые импульсы с выхода генератора 97 тактовых импульсов также поступают на вход элемента НЕ 113. При выдаче последнего бита ограничителя начала кадра на первый вход элемента ИЛИ-НЕ 112 поступает сигнал, равный нулю, с выхода элемента И-НЕ 103, При поступлении на второй вход элемента ИЛИ-НЕ 112 инвертированного тактового импульса сигнал на выходе этого элемента изменяет свое значение с нуля на единицу. По переднему положительному фронту этого сигнала, поступающего на вход триггера 106, данный триггер устанавливается в единичное состояние. Содержимое регистра 95 данных поступает на информационный вход сдвигового регистра 108 На управляющий вход сдвигового регистра 108 поступает сигнал, равный единице, с выхода элемента И 102. При наличии сигнала, равного единице на управляющем входе этого регистра при появлении положительного импульса, сформированного элементом И 109, на один вход которого поступает единичное значение сигнала с прямого выхода триггера 106 выдачи данных, а на другой вход поступает текущий тактовый импульс, происходит занесение содержимого регистра 95 данных в сдвиговой регистр 108. Одновременно на выходе элемента И-НЕ 107 формируется сигнал, равный нулю. Этот сигнал поступает на вход сброса триггера 96 данных и устанавливает его в нулевое состояние. На выходе элемента И 99 формируется новый сигнал запроса чтения, который вызовет новый цикл чтения памяти блоком 7 „ В результате этого следующий байт данного записывается в регистр 95 данных. По следующему тактовому импульсу происходит выдача с выхода сдвигового регистра 108 первого информационного бита, поступающего с второго информационного входа мультиплексора 111 на его выход, в передатчик приемопередатчика 9. Так как сигнал на выходе элемента И 102 становится равен нулю (изменяется г содержимое счетчика 98 бит), то

по следующему положительному импульсу, сформированному элементом И 109, происходит сдвиг на единицу содержимого сдвигового регистра 108. Со