11347175 2

Изобретение относится к импульснойходной 14 шинам селектора импульсов,

технике, в частности к селекторамВторой выход дешифратора подключен

импульсов, и может быть использованок входу счетчика 9 адреса, выходы

в радио- и оптоэлектронных системахкоторого подключены к соответствугавыделения периодических последователь-щим адресным входам оперативной станостей сигналов на фоне случайныхтической памяти 7, помех.Селектор импульсов работает слеЦель изобретения - расширение функ-дующим образом.

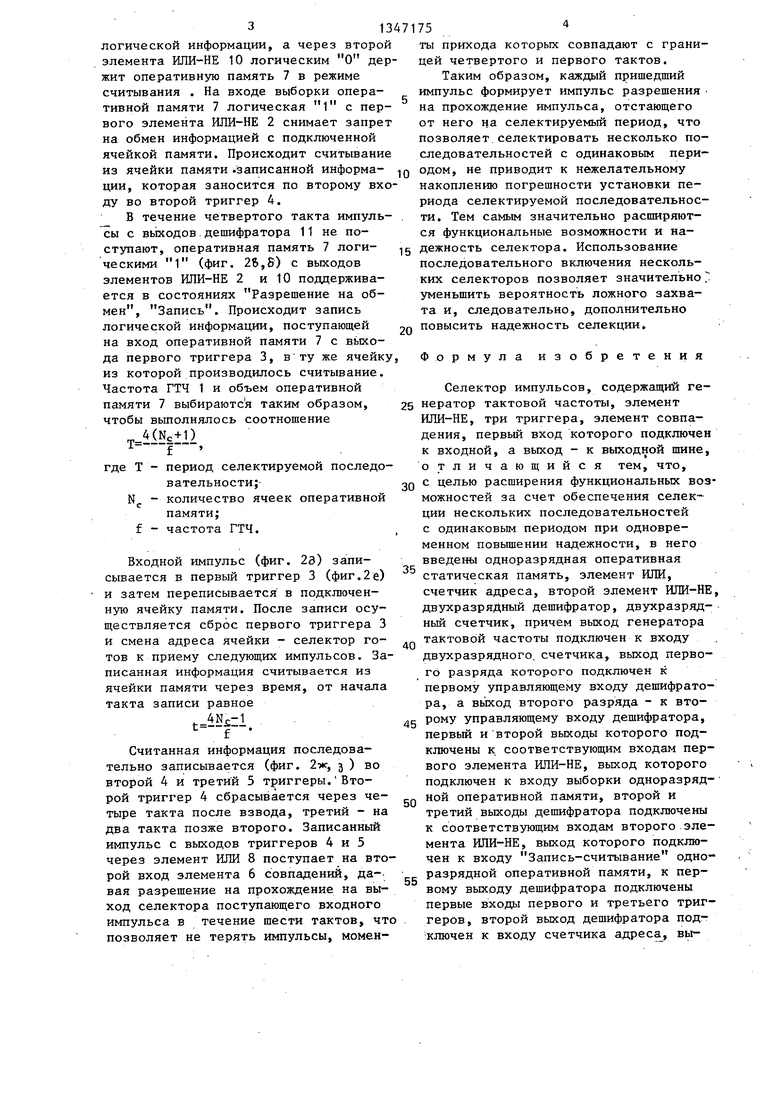

циональных возможностей селектора за ю исходном состоянии все триггеры счет обеспечения селекции нескольких3-5 находятся в- бостоянии логичес- последовательностей с одинаковым пе-кого О, информационный вход и вы- риодом при одновременном повьшенииход одноразрядной оперативной стати- надежности,ческой памяти 7 подключается последоНа фиг. 1 представлена функциональ-15вательно к каждой ячейке памяти, из

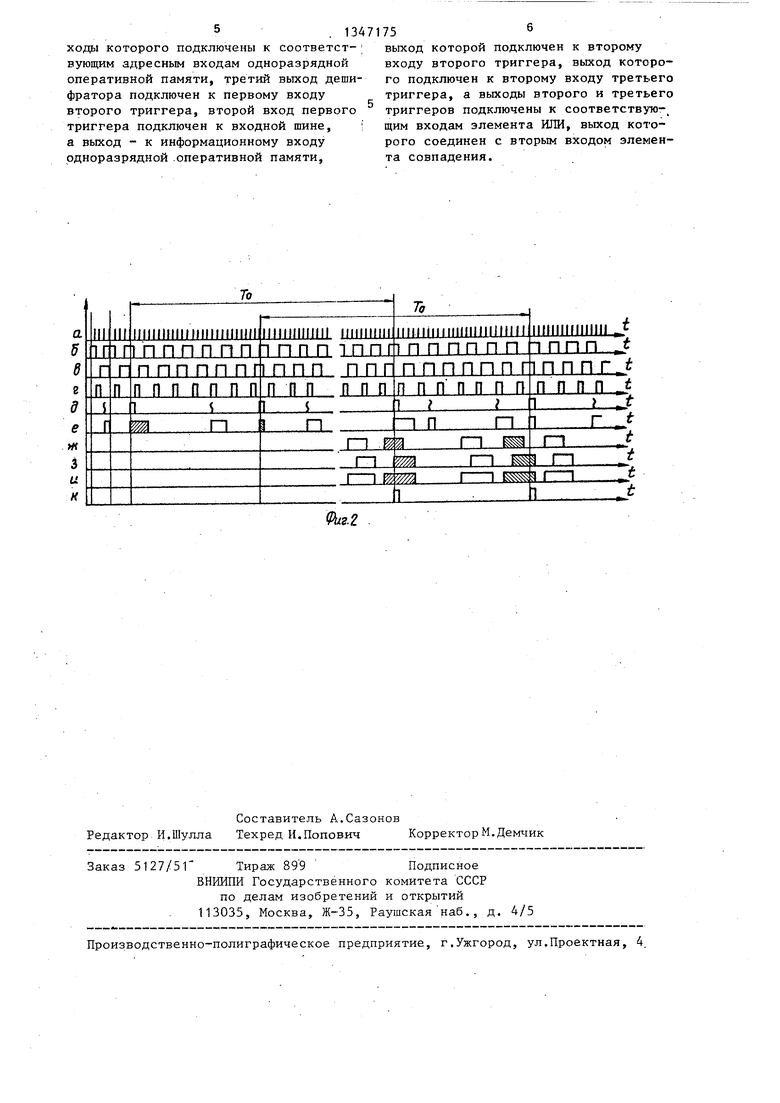

ная структурная схема селектора им-которых считывается в триггер 4 и

пульсов; на фиг. 2 - временные диа-вновь записывается из триггера 3 лограммы его работы.гической О.

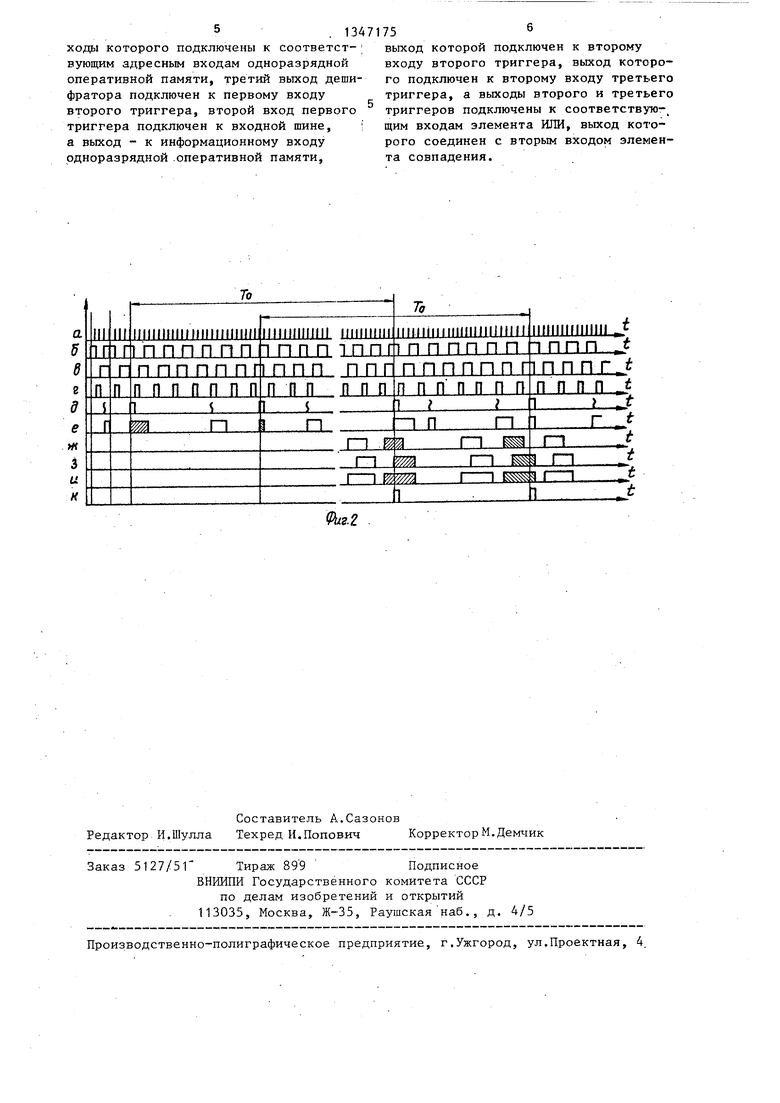

Селектор импульсов содержит гене- ГТЧ 1 вырабатывает импульсы, опре- ратор 1 тактовой частоты (ГТЧ), пер- JQделяюпще циклический режим работы вый элемент ИЛИ-НЕ 2, первый 3, вто-оперативной памяти 7 и триггеров 3 - 5. рой 4 и третий 5 триггеры, элемент 6Импульсы ГТЧ (фиг. 2о), пройдя двух- совпадения,.одноразрядную оперативнуюразрядный счетчик 12 поочередно с вы- статическую память 7, элемент ИЛИ 8,ходов первого и второго разрядов счетчик 9 адреса, второй элемент ИЛИ- 25счетчика 12, поступают на управляюпрте НЕ 10, двухразрядный дешифратор 11,входы двухразрядного дешифратора II. двухразрядный счетчик 12, Выход гене-На выходах дешифратора 11 циклически ратора 1 тактовой частоты подключен появляются импульсы, соответствуюгцие к входу двухразрядного счетчика 12,первому, второму, третьему, четверто- выход первого разряда которого под- о импульсам ГТЧ. Последовательность ключен к первому управляюш;ему входуэтих четырех импульсов, управляющих дешифратора 11, а выход второго раз-работой оперативной памяти 7, состав- ряда - к второму управляющему входуляет цикл.

дешифратора 11. Первый и второй вьпсо- Первый импульс цикла - импульс с ды дешифратора 11 подключены к вхо- .первого выхода дешифратора 11, постудам первого элемента ИЛИ-НЕ 2, а вто-пая на первые входы первого 3 и тре- рой и третий выходы дешифратора 11 -тьего 5 триггеров, осуществляет их к входам второго элемента ИЛИ-НЁ 10.сброс и, воздействуя через первый Выходы первого 2 и второго 10 элемен-элемент ИЛИ-НЕ 2 на вход выборки опе- тов ИЛИ-НЕ подключены соответственноративной памяти 7, логическим О к входу выборки и входу Запись -(фиг. 2 ) обеспечивает запрет обмена считывание оперативной памяти 7. Пер-информацией с ячейками памяти. Уст- вые входы первого 3 и третьего 5 триг-ройство подготавливается таким обра- геров подключены к первому вьпсоду, азом к дальнейшей работе.

первьш вход второго триггера 4 - к Второй импульс цикла - импульс с

4

третьему выходу дешифратора 11. Втогвторого выхода дешифратора 11 через

рой вход первого триггера 3 подклю- первый 2 и второй 10 элементы ИЛИ-НЕ

чен к входу селектора импульсов, асоответственно логическим О (фиг.

выход - к информационному входу одно-25,й) обеспечивает запрет обмена инразрядной оперативной памяти. Вторые -формацией и режим считывания. Этот

входы которого 4 и третьего 5 тригге-импульс (фиг. 2 ) действует на вход

ров подключены соответственно к выхо-счетчика 9 адреса, который осуществдам одноразрядной оперативной памяти 7ляет изменение адреса ячейки операи второго триггера 4, Выходы второго 4тивной памяти 7.

и третьего 5 триггеров подключены к .. Третий импульс цикла - импульс с

входам элемента ИЛИ 8, выход которого второго выхода дешифратора 11, поступодключен к второму входу элемента 6 пая на первый вход второго триггесовпадения, первый вход которого под-ра 4, передним фронтом обнуляет триг-

ключен к входной 13, а выход - к вы-гер, подготавливая к приему новой

313

логической информации, а через второй элемента ИЛИ-НЕ 10 логическим О держит оперативную память 7 в режиме считывания . На входе выборки оперативной памяти 7 логическая 1 с первого элемента ИЛИ-НЕ 2 снимает запрет на обмен информацией с подключенной ячейкой памяти. Происходит считывание из ячейки памяти .записанной информа- ции, которая заносится по второму входу во второй триггер 4.

В течение четвертого такта импульсы с вьЬюдов . дешифратора 11 не поступают, оперативная память 7 логи- ческими 1 (фиг. 2S,S) с выходов элементов ИЛИ-НЕ 2 и 10 поддерживается в состояниях Разрешение на обмен, Запись. Происходит запись логической информации, поступающей на вход оперативной памяти 7 с вько- да первого триггера 3, в ту же ячейку из которой производилось считывание. Частота ГТЧ 1 и объем оперативной памяти 7 выбираются таким образом, чтобы вьтолнялось соотношение

T,(NC+I) J ,

где Т - период селектируемой последовательности;N - количество ячеек оперативной

памяти; f - частота ГТЧ.

Входной импульс (фиг. 23) записывается в первый триггер 3 (фиг.2е) и затем переписывается в подключенную ячейку памяти. После записи осуществляется сброс первого триггера 3 и смена адреса ячейки - селектор го- тов к приему следующих импульсов. Записанная информация считывается из ячейки памяти через время, от начала такта записи равное

f

Считанная информация последовательно записывается (фиг. 2ж, j ) во второй 4 и третий 5 триггеры. Второй триггер 4 сбрасывается через четыре такта после взвода, третий - на два такта позже второго. Записанный импульс с выходов триггеров 4 и 5 через элемент ИЛИ 8 поступает на второй вход элемента 6 совпадений, да-- вая разрешение на прохождение на выход селектора поступающего входного импульса в течение шести тактов, чт позволяет не терять импульсы, момен

Q

о 5

Q

.„

5

0

5

75 ..

ты прихода которых совпадают с границей четвертого и первого тактов.

Таким образом, каждый пришедший импульс формирует импульс разрешения на прохождение импульса, отстающего от него на селектируемый период, что позволяет.селектировать несколько последовательностей с одинаковым периодом, не приводит к нежелательному накоплению погрешности установки периода селектируемой последовательности. Тем самым значительно расширяются функциональные возможности и надежность селектора. Использование последовательного включения нескольких селекторов позволяет значительно j уменьшить вероятность ложного захвата и, следовательно, дополнительно повысить надежность селекции.

Формула изобретения

Селектор импульсов, содержащий генератор тактовой частоты, элемент ИЛИ-НЕ, три триггера, элемент совпадения, первый вход которого подключен к входной, а выход - к выходной шине, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения селек ции нескольких последовательностей с одинаковым периодом при одновременном повьшении надежности, в него введены одноразрядная оперативная статическая память, элемент ИЛИ, счетчик адреса, второй элемент ИЛИ-НЕ, двухразрядный дешифратор, двухразрядный счетчик, причем выход генератора тактовой частоты подключен к входу двухразрядного, счетчика, выход первого разряда которого подключен к первому управляющему входу дешифратора, а вьЬсод второго разряда - к второму управляющему входу дешифратора, первый и второй выходы которого подключены к соответствующим входам первого элемента ИЛИ-НЕ, выход которого подключен к входу выборки одноразряд- ной оперативной памяти, второй и третий выходы дешифратора подключены к соответствующим входам второго.элемента ИЛИ-НЕ, выход которого подключен к входу Запись-считывание одноразрядной оперативной памяти, к первому выходу дешифратора подключены первые входы первого и третьего триггеров, второй выход дешифратора под- ключен к входу счетчика адреса, . 1347

ходы которого подключены к соответст- вующим адресным входам одноразрядной оперативной памяти, третий выход дешифратора подключен к первому входу второго триггера, второй вход первого триггера подключен к входной шине, ; а выход - к информационному входу одноразрядной .оперативной памяти,

Составитель А.Сазонов Редактор И.Шулла Техред И,Попович КорректорМ.Демчик

7 -- -- -------------- -------- ------------ ------.---.- ------..--.- --i-.- - -..«....«

Заказ 5127/5 Г Тираж 899 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и откр1ытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

1756

выход которой подключен к второму входу второго триггера, выход которого подключен к второму входу третьего триггера, а выходы второго и третьего триггеров подключены к соответствую- щим входам элемента ИЛИ, выход которого соединен с вторым входом элемента совпадения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное устройство для обучения языкам | 1987 |

|

SU1441445A1 |

| Устройство для отладки программ | 1983 |

|

SU1198525A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Формирователь кодов радиально-круговой развертки для индикатора кругового обзора | 1986 |

|

SU1401422A2 |

| Устройство для записи информации в оперативную память | 1982 |

|

SU1049966A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Многоканальное измерительно-регистрирующее устройство (его варианты) | 1982 |

|

SU1038807A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели переменного тока | 1989 |

|

SU1793458A1 |

| Устройство для построения программируемых логических автоматов | 2023 |

|

RU2814507C1 |

Изобретение может быть использовано в радио- и оптоэлектронных системах вьщеления периодической последовательности импульсных сигналов на фоне случайных помех. Цель изобретения - расширение функциональных возможностей за счет обеспечения селекции нескольких последовательностей с одинаковым периодом при одновременном повьппении надежности. Для этого в селектор импульсов, содержащий гет нератор 1 тактовой частоты, первый . элемент ИЛИ-НЕ 2, триггеры 3-5, элемент 6 совпадения, дополнительно введены одноразрядная статическая память 7, элемент ИЛИ 8, счетчик адреса 9, второй элемент ИЛИ-НЕ 10, двухразрядный дешифратор 11 и двухразряд- ньш счетчик 12. Изобретение позволяет селекти ровать несколько последовательностей с одинаковым периодом при исключении накопления погрешности установки периода селектируемой последовательности, что повышает надежность селектора в работе. 2 ил. 7 Ш (Л С СА:) 4 vl cm Фиг.1

| Селектор импульсов | 1982 |

|

SU1034166A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Селектор импульсов | 1977 |

|

SU746899A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-23—Публикация

1985-12-09—Подача