lioro дешифратора соединен с тактовым входом первого регистра, информационный выход которого соединен с вторым входом шестого элемента И, третий выход первого дешифратора соединен с третьим входом второго элемента И, с третьим управляющим входом второго дешифратора, с инверсным входом четвертого элемента И, выход которого соединен со счетным входом счетчика, выход блока сравнения соединен с вторым входом

98525

третьего элемента И, выход которого соединен с входом установки в 1 D-триггера, входы команды и начальной установки устройства соединены соответственно с третьим входом пятого элемента И и с нулевым входом D-триггера, информационный вход которого соединен с шиной нулевого потенциала устройства, выход блока постоянной памяти соединен с третьим информационным входом блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1989 |

|

SU1683019A2 |

| Устройство для отладки программ | 1988 |

|

SU1552190A2 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

| Устройство для вычисления параметров диаграмм разрежения индикаторов при исследовании сердечно-сосудистой системы | 1982 |

|

SU1157547A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1293730A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ, содержащее элемент ИЛИ, первый и второй элементы И, блок постоянной памяти, блок оперативной памяти, блок сравнения, причем адресный вход устройства соединен с адресными входами блоков постоянной и оперативной памяти и спервым информационным входом блока сравнения, вход обращения устройства соединен с тактовым входом блока сравнения и с входами обращения блоков постоянной и оперативнрй памяти, информационный вход устройства соединен с вторым информационным входом блока сравнения и с информационным входом блока оперативной памяти, вход установки режима устройства соединен с входом записи блока оперативной памяти, выходы блоков постоянной и оперативной памяти соединены с первыми входами соответственно первого и второго элементов И, выходы которых соединены со.ответственно с первым и вторым входами элемента ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения оперативной подмены зон информа ии. расположенных в блоке постоянной памяти, информацией, расположенной в блоке оперативной памяти, в него введеиы пять элементов И, двухраз-. рядный двоичньй счетчик, D-триггер первый и второй дешифраторы, первый и второй регистры, причем инверсный выход D-триггера соединен с вторым входом первого элемента И, первым входом третьего элемента И и входом установки в О двухразрядного счетчика, информационные выходы которого соединены с входами первого дешифратора, тактовый вход устройства соединен с первыми входами четвертого и пятого элементов И,, с первым упi равляющим входом второго дешифрато(Л ра, с третьим входом первого элемента И и с входом второго элемента И, адресный вход устройства соединен с инфррмахщонными входами второго дешифратора, первого и второго регистров, вход обращения устройства соединен с вторьм управляющим входом рторого дешифратора,персо вый, второй и третий выходы которого Об соединены соответственно с тактовым сд to ел входом Р-триггера, с первым входом шестого элемента И и первым входом седьмого элемента И, выходы пятого, шестого и седьмого элементов И соединены соответственно с третьим, четвертым и пятым входами элемента ИЛИ, выход которого является выходом команды устройства, первый выход первого дешифратора соединен с вторым входом пятого элемента И и с тактовым входом второго регистра, информационный выход которого соединен с вторым входом седьмого элемента И, второй выход пер

Изобретение-относится к цифровой вычислительной технике и может быть использовано при отладк.е программ Специализированных ЦВМ, содержащях в своем составе штатные блоки постоянной памяти (ВШ) с рабочими программами.

Цель изобретения - расширение функциональных возможностей за счет обеспечения оперативной подмены зон информации, расположенных в блоке постоянной памяти, информацией, расположенной в блоке оперативной памяти.

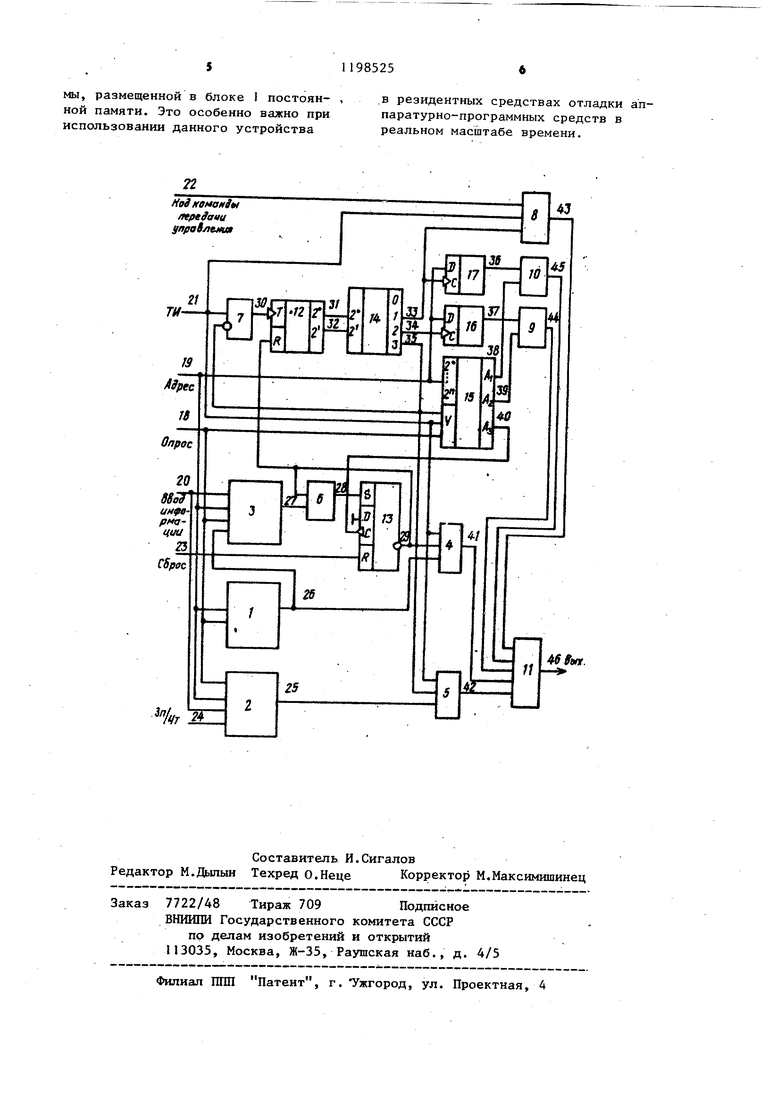

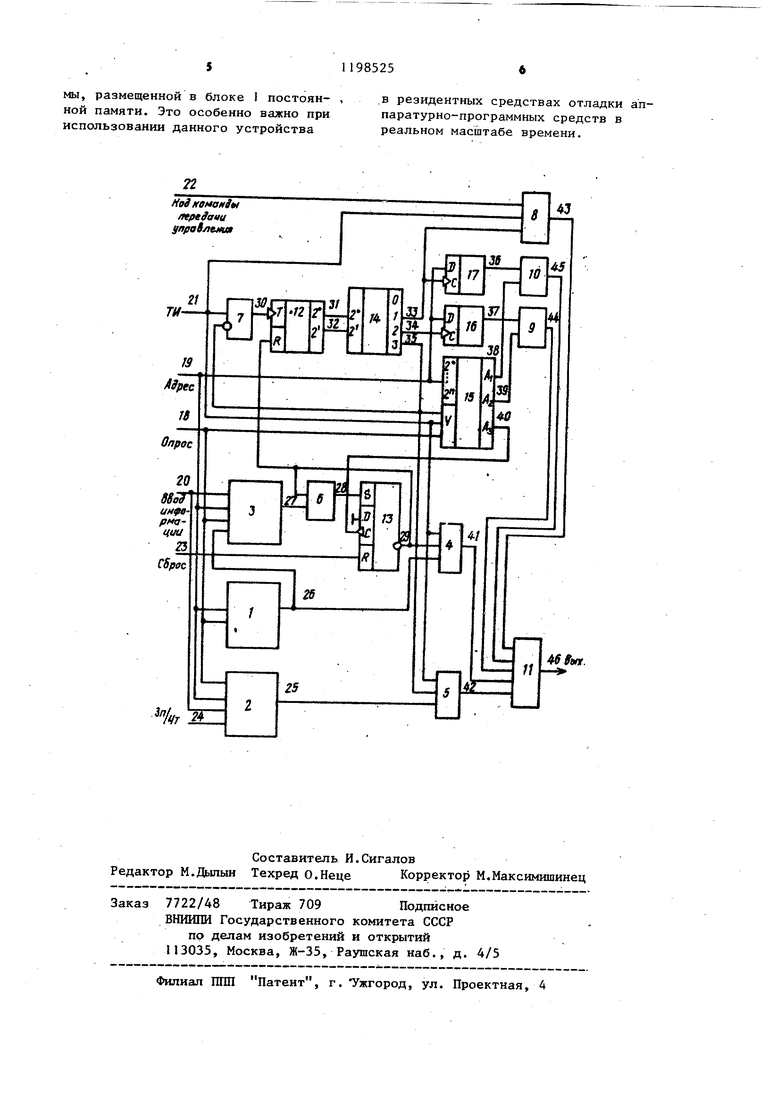

На чертеже представлена функциональная схема устройства.

.Устройство содержит блок I постоянной памяти, блок 2 оперативной памяти, блок 3 сравнения, первыйседьмой элементы И 4-10, элемент ИЛИ }1, двухразрядный двоичный счетчик 12, D-триггер 13, первый 14 и второй 15 дешифраторы, первый 16 и второй 17 регистры, причем к входу 18 обращения устройства подключены тактовый вход блока 3 сравнения, входы обращения блоков постоянной памяти I и оперативной памят 2 и второй управляющий вход второго дешифратора 15.-К адресному входу 18 устройства подключены первый информационный вход блока 3 сравнения, адресные входы блоков постоянно 1 и оперативной 2 памяти, информационные входы второго дешифратора 15, первого и второго регистров 16 и 17, к информационному входу 20 устройства подключены второй- информационный вход блока 3 сравнения, информационный вход блока 2 оперативной памяти, к тактовому входу 21 устройства .подключены первые входы четвертого и пятого элементов И 7 и 8 соответственно,- первый управляющи вход дешифратора 15, третий вход первого элемента И 4 и второй вход второго элемента И 5 к входу 22 команды устройства подключен третий вход пятого элемента И 8, к .входу 23 начальной установки устройства подключен вход установки в О D-триггера 13, к входу 24 установки режима подключен вход записи блока 2 оперативной памяти. К выходу 25 блока оперативной памяти подключен первый вход второго элемента И 5, к выходу 26 блока постоянной памяти подключены первый вход пер-вого элемента И 4 и третий информационный вход блока 3 сравнения, к выходу 27 блока 3 сравнения подключен второй вход третьего элемента И 6, к выходу 28 третьего элемента И 6 подключен вход установки в D-триггера 13, к инверсному выходу 29 D-триггера 13 подключены первый вход третьего элемента И 6 вход установки в О двухраэрядного двоичного счетчика 12 и второй вход первого элемента И 4, к выходу 30 четвертого элемента И 7 подключен счетный вход двухразрядного двоичного счетчика 12, к информационным выходам 31 и 32 двухразрядного двоичного счетчика подключены входы первого дешифратора 14, к выходам первого дешифратора 14 подключены: к первому 33 - тактовый вход второ3

го регистра 17 и второй вход пятого элемента И 8, к второму 34 - тактовый вход первого регистра 16, к третьему 35 - второй инвертирующий вход четвертого элемента И 7, третий управляющий вход второго дешифратора 5 и третий вход второго элемента И 5, к выходу 36 второго регистра 17 подключен второй вход седьмого элемента И 10, к выходу 37 первого регистра 16 подключен второй вход шестого элемента И 9, к выходам второго дешифратора 15 подключены: к первому 38 - первый тактовый вход D-тригг.ера 13, к второму 39 - первый вход шестого элемента И 9, к третьему 40 - первый вход седьмого элемента И 10, к выходам 41-45 первого, второго, пятого, шестого и седьмого элементов И 4,5,8,9и 10 подключены первый, второй, третий, четвертый и пятый входы элемента ИЛИ 11 соответственно, выход элемента i. ИЛИ 11 является выходом 46 команды устройства.

Устройство работает следую цим образом.

В исходном Состоянии, в которое устройство устанавливается при подаче на вход Сброс 23 сигнала начальной .установки, разрешается считьгоакие информации только с блока 1 постоянной памяти через первьй элемент И 4 в момент появления тактовых импульсов, поступающих на вход 21 тактовых импульсов. Поэтому на вход 46 устройства выдается информация, размещенная в блоке 1 постоянной памяти. Блок 3 сравнения по заданному критерию определяет место -в программе, размещенной в. блоке 1 постоянной памяти, где необходимо выполнить ее корректировку или вьтолнить сервисную программу. Назовем это место в программе.точкой замещения. Когда точка замещения обнаруживается, блок 3 сравнени на выходе-27 формирует сигнал, который через третий элемент И 6 устанавливает в I триггер 13. Поэтому запрещается считывание информации с блока 1 постоянной памяти, прохождение сигнала с выхода .27 блока 3 сравнения через третий элемент И 6 и разрешается работа счетчика 12. При поступлении на вход 21 тактовьк импульсов первого после обнаружения точки замещения такто98525Л

вого импульса разрешается прохождение кода команды передачи управления через пятый элемент ИЗ с входа 22 на выход 46 устройства и за, поминается состояние входа I9 адреса во втором регистре 17. Следовательно, вместо очередной команды программы, размещенной в блоке 1 постоянной памяти, на выход 46

Q устройства выдается команда передачи управления, например команда перезапуска, и во втором регистре 17 запоминается адрес точки замещения. По команде передачи управления в следующем такте содержимое счетчи15ка команд загружается в стек. В этом такте, втором после обнаружения точки замещения, запрещается прохождение кода передачи управления через пятый элемент И 8 на выход 46 уст20ройства и запоминается состояние входа 19 адреса в первом регистре 16, т.е. значение указателя стека программы, размещенной в блоке 1

р, постоянной памяти. В третьем, после обнаружения точки замещения такте управление передается по адресу, однозначно определяемому кодом команды передачи управления, запрещается прохождение тактовых

30 импульсов на счетный вход счетчика 12 через четвертый элемент И 7, разрешается работа второго дешифратора 15 и считывание информации с блока 2 оперативной памяти на

35 выход 46 устройства через второй

элемент И 5. I

Таким образом, в предложенном уст-.

ройстве для управления обращением к памяти при отладке программ

40 упропдена аппаратурная реализация. Поскольку объем блока 2 оперативной памяти может быть выбран произвольным независимо от объема отлаживаемой программы, размещенной

45 в блоке 1 постоянной памяти, значительно расширены функциональные возможности вследствие замещения массива информации, размещенного в блоке постоянной памяти, массивом информации произвольной размерности, размещенным в блоке 2 оперативной памяти, введения дополнительного фрагмента программы, подпрограммы в программу, размещенную в блоке

55 1 постоянной памяти, исключения фрагмента программы, подпрограммы, размещенных в блоке 1 постоянной памяти, зацикливания участков программы, размещенной в блоке 1 постоянной памяти. Это особенно важно при использовании данного устройства

.в резидентных средствах отладки аппаратурно-программных средств в реальном масштабе времени.

- .. 4Sfwe.

| Устройство для управления обращением к памяти при отладке программ | 1981 |

|

SU1001099A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления памятью | 1979 |

|

SU943726A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-15—Публикация

1983-10-12—Подача