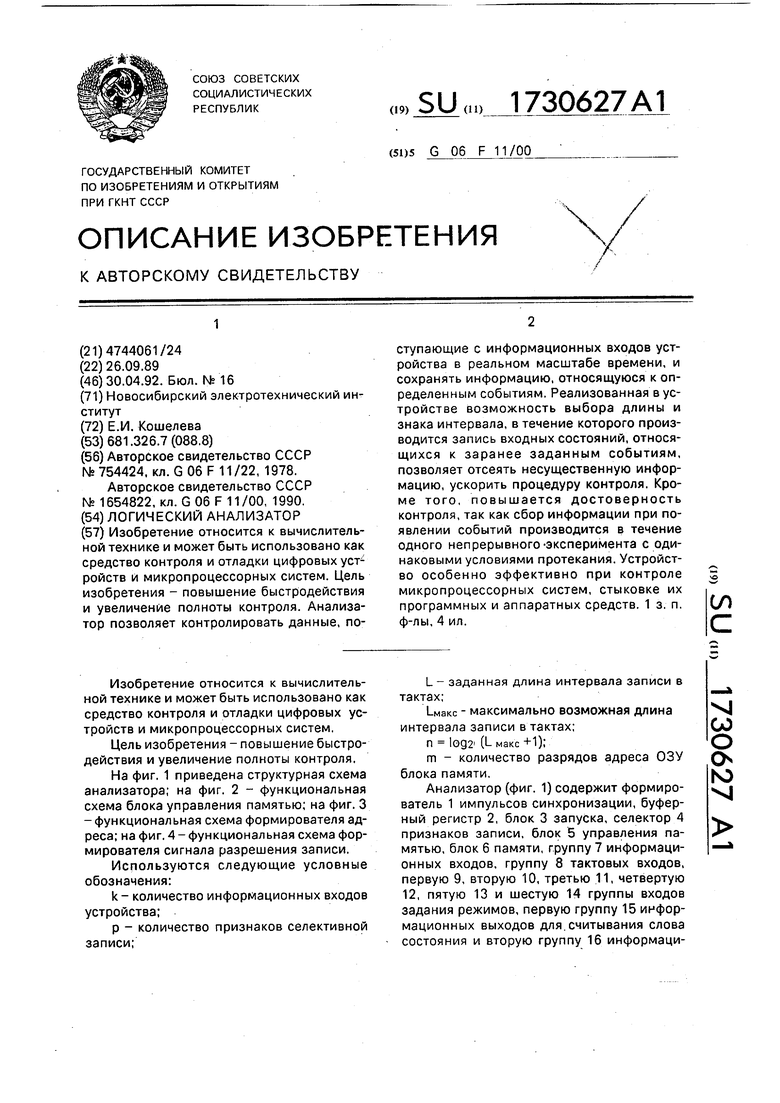

Изобретение относится к вычислительной технике и может быть использовано как средство контроля и отладки цифровых устройств и микропроцессорных систем,

Цель изобретения - повышение быстродействия и увеличение полноты контроля.

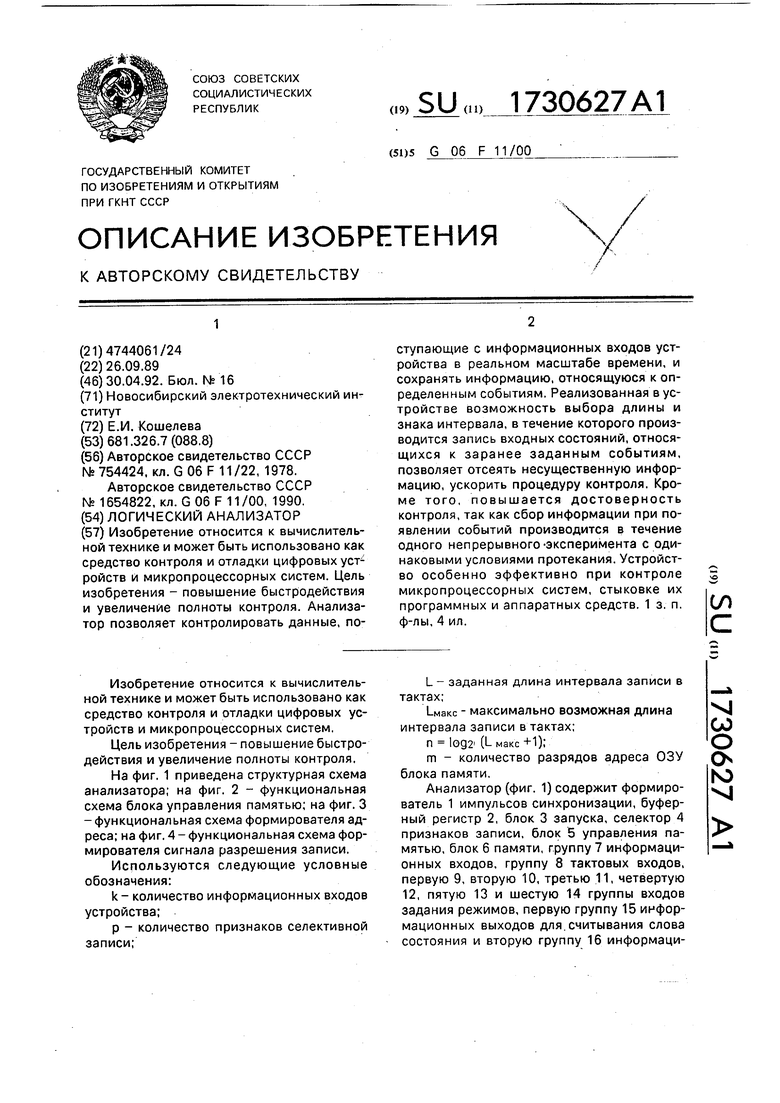

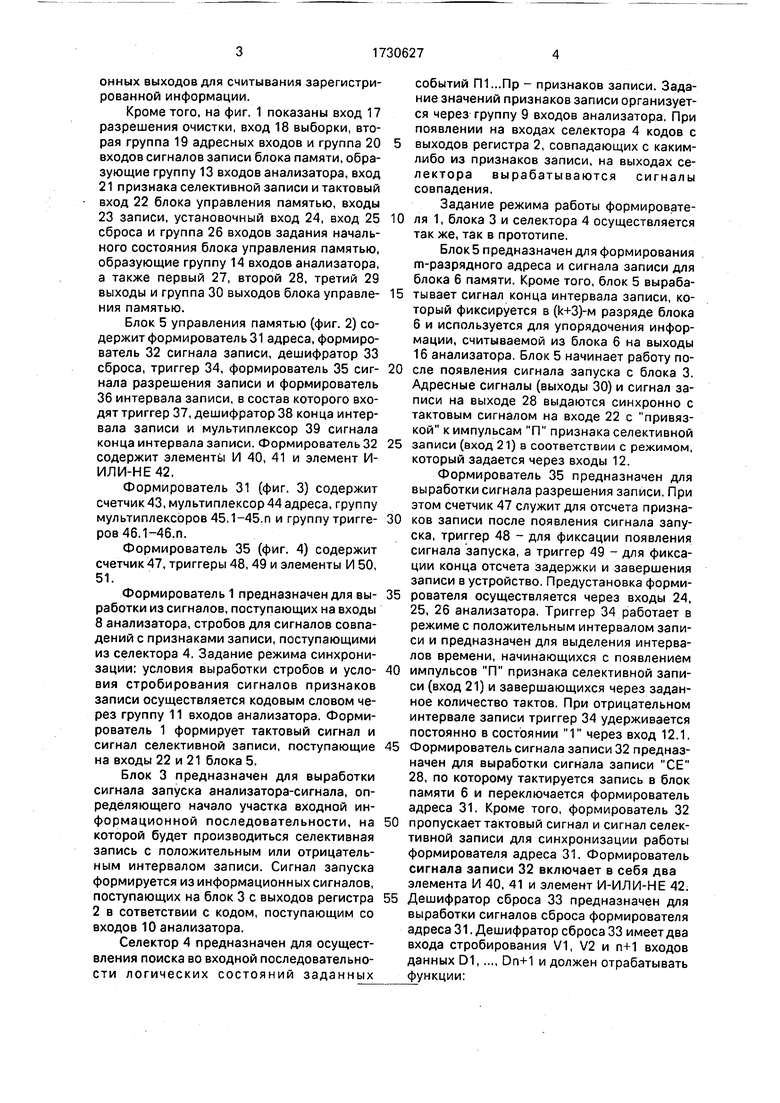

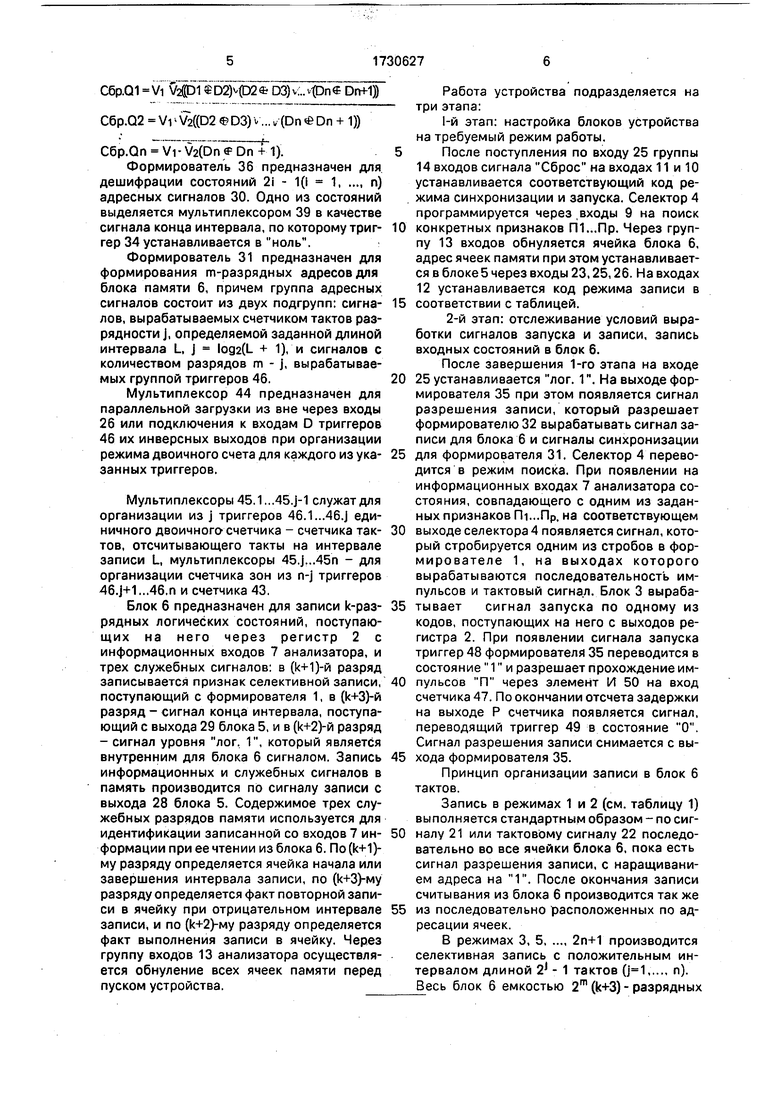

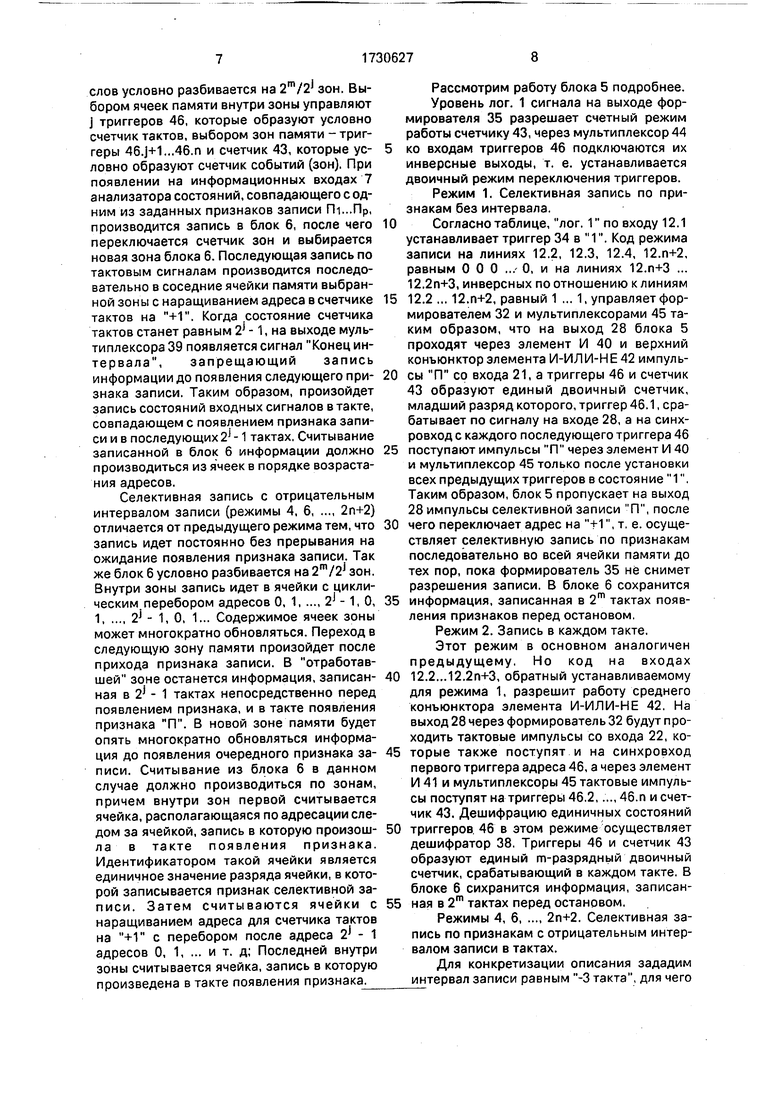

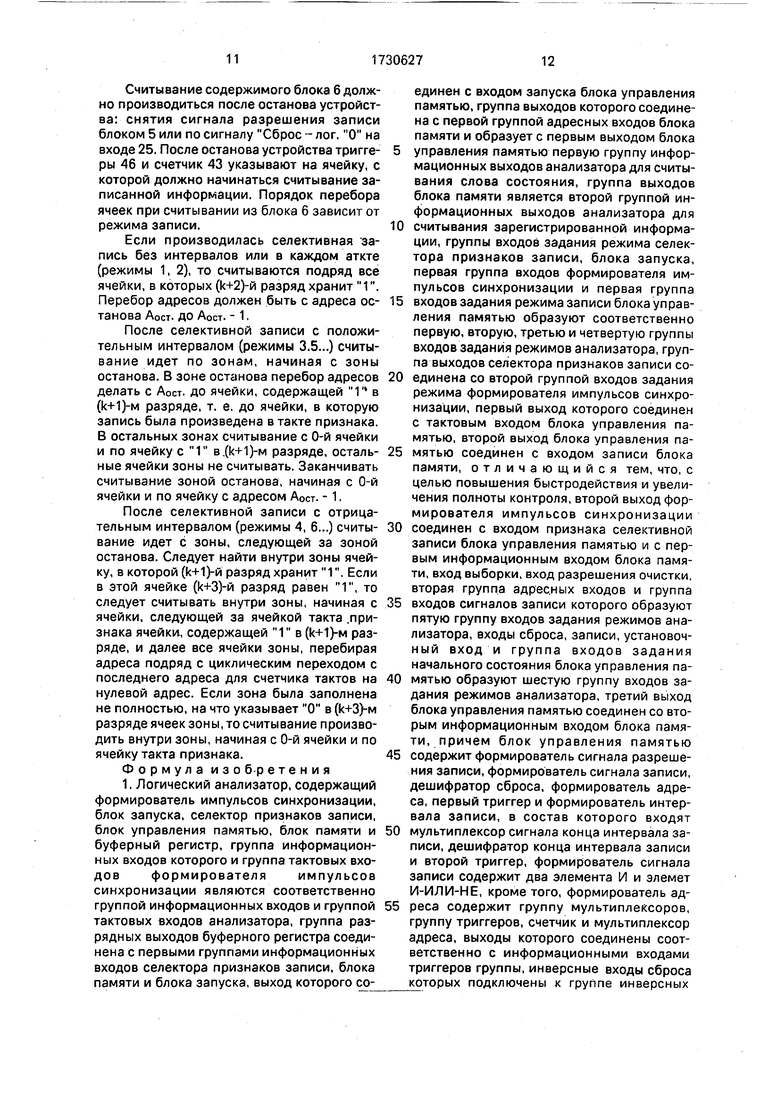

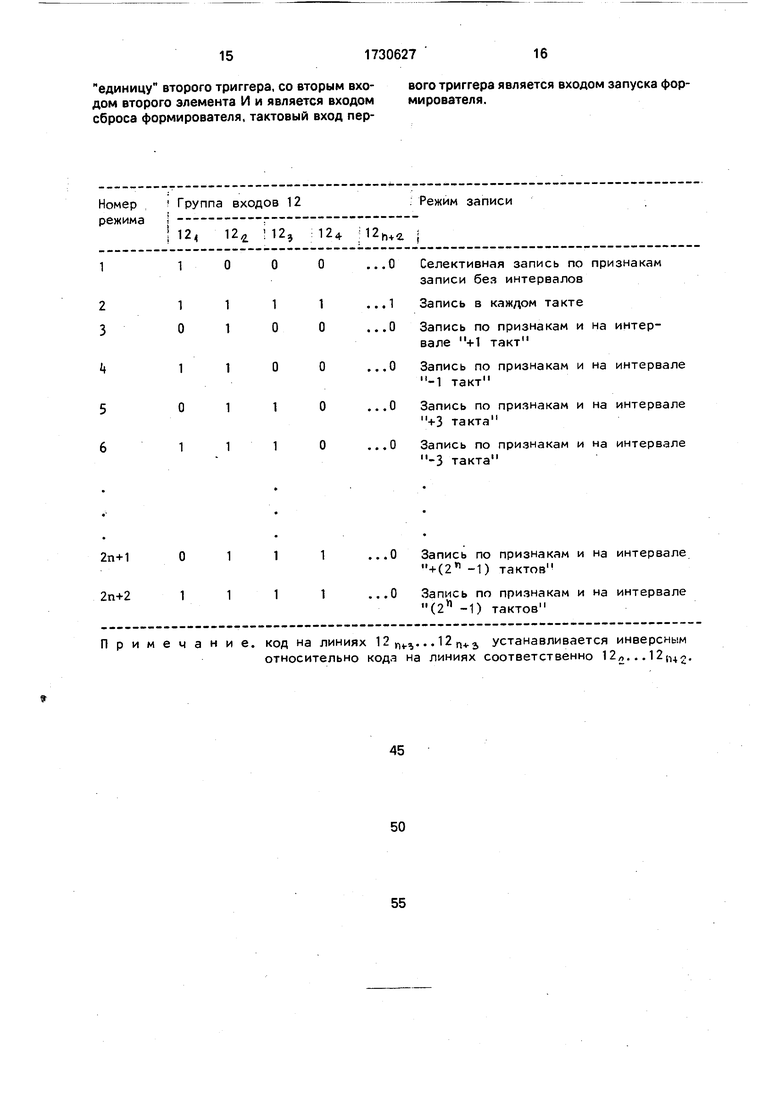

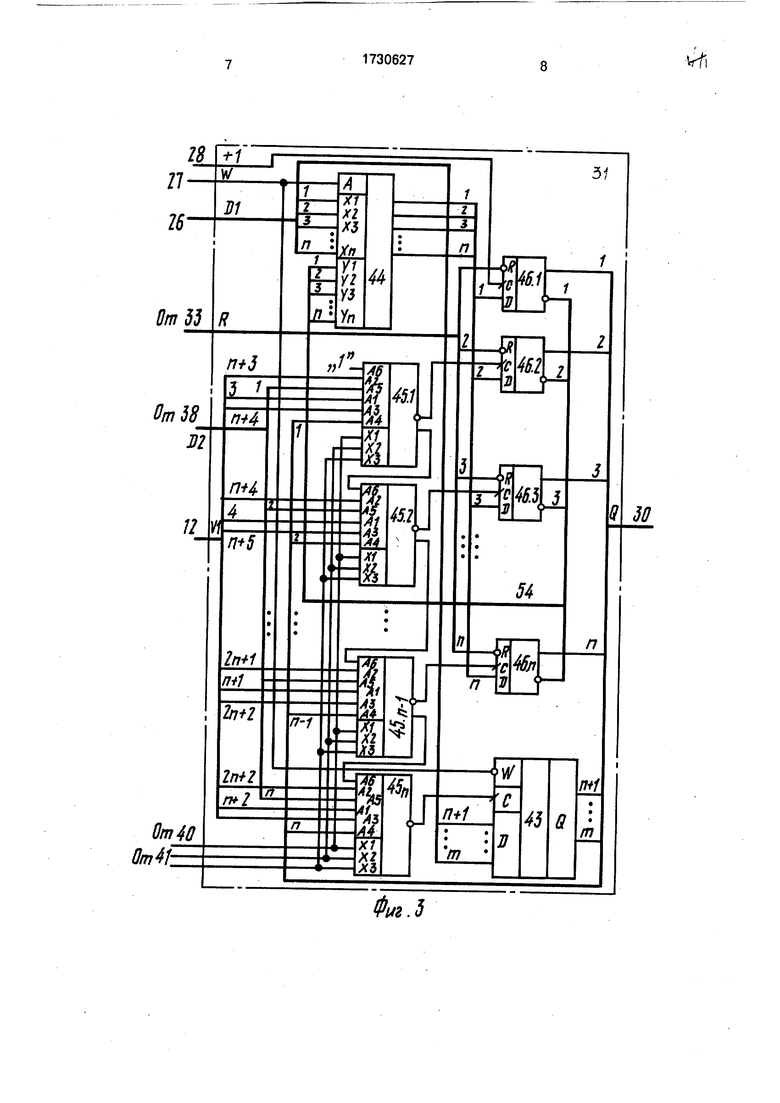

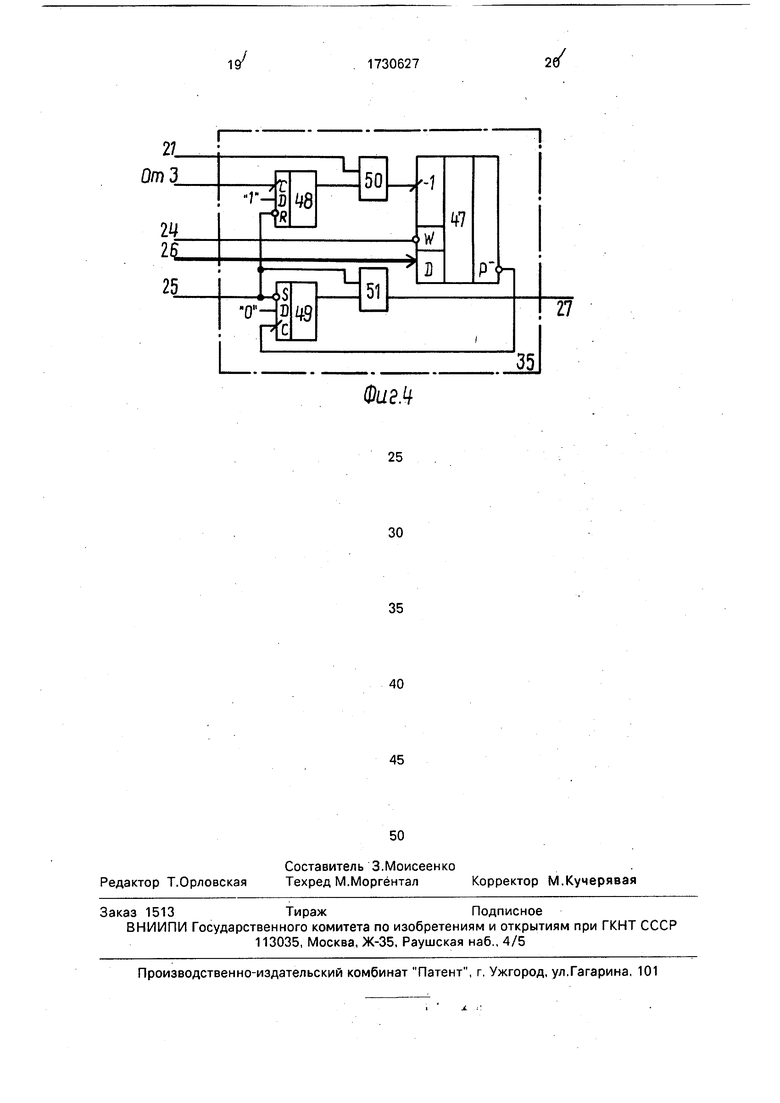

На фиг. 1 приведена структурная схема анализатора; на фиг. 2 - функциональная схема блока управления памятью; на фиг. 3 - функциональная схема формирователя адреса; на фиг. 4 - функциональная схема формирователя сигнала разрешения записи,

Используются следующие условные обозначения:

к- количество информационных входов устройства;

р - количество признаков селективной записи;

L- заданная длина интервала записи в тактах;

L-макс - максимально возможная длина интервала записи в тактах;

П 10Q2 (L макс +1);

m - количество разрядов адреса ОЗУ блока памяти.

Анализатор (фиг. 1) содержит формирователь 1 импульсов синхронизации, буферный регистр 2, блок 3 запуска, селектор 4 признаков записи, блок 5 управления памятью, блок 6 памяти, группу 7 информационных входов, группу 8 тактовых входов, первую 9, вторую 10, третью 11, четвертую 12, пятую 13 и шестую 14 группы входов задания режимов, первую группу 15 информационных выходов для считывания слова состояния и вторую группу 16 информациXI

СО

о о ю XI

онных выходов для считывания зарегистрированной информации.

Кроме того, на фиг. 1 показаны вход 17 разрешения очистки, вход 18 выборки, вторая группа 19 адресных входов и группа 20 входов сигналов записи блока памяти, образующие группу 13 входов анализатора, вход 21 признака селективной записи и тактовый вход 22 блока управления памятью, входы 23 записи, установочный вход 24, вход 25 сброса и группа 26 входов задания начального состояния блока управления памятью, образующие группу 14 входов анализатора, а также первый 27, второй 28, третий 29 выходы и группа 30 выходов блока управления памятью.

Блок 5 управления памятью (фиг. 2) содержит формирователь 31 адреса, формирователь 32 сигнала записи, дешифратор 33 сброса, триггер 34, формирователь 35 сигнала разрешения записи и формирователь 36 интервала записи, в состав которого входят триггер 37, дешифратор 38 конца интервала записи и мультиплексор 39 сигнала конца интервала записи. Формирователь 32 содержит элементе, И 40, 41 и элемент И- ИЛИ-НЕ42.

Формирователь 31 (фиг. 3) содержит счетчик43, мультиплексор44 адреса, группу мультиплексоров 45.1-45.П и группу триггеров 46.1-46.п.

Формирователь 35 (фиг. 4) содержит счетчик 47, триггеры 48,49 и элементы И 50, 51.

Формирователь 1 предназначен для выработки из сигналов, поступающих на входы 8 анализатора, стробов для сигналов совпадений с признаками записи, поступающими из селектора 4. Задание режима синхронизации: условия выработки стробов и условия стробирования сигналов признаков записи осуществляется кодовым словом через группу 11 входов анализатора. Формирователь 1 формирует тактовый сигнал и сигнал селективной записи, поступающие на входы 22 и 21 блока 5.

Блок 3 предназначен для выработки сигнала запуска анализатора-сигнала, определяющего начало участка входной информационной последовательности, на которой будет производиться селективная запись с положительным или отрицательным интервалом записи. Сигнал запуска формируется из информационных сигналов, поступающих на блок 3 с выходов регистра 2 в сответствии с кодом, поступающим со входов 10 анализатора.

Селектор 4 предназначен для осуществления поиска во входной последовательности логических состояний заданных

событий П1...Пр - признаков записи. Задание значений признаков записи организуется через группу 9 входов анализатора. При появлении на входах селектора 4 кодов с

выходов регистра 2, совпадающих с каким- либо из признаков записи, на выходах селектора вырабатываются сигналы совпадения.

Задание режима работы формировате0 ля 1, блока 3 и селектора 4 осуществляется так же, так в прототипе.

Блок 5 предназначен для формирования m-разрядного адреса и сигнала записи для блока 6 памяти. Кроме того, блок 5 выраба5 тывает сигнал конца интервала записи, который фиксируется в (k+3)-M разряде блока 6 и используется для упорядочения информации, считываемой из блока 6 на выходы 16 анализатора. Блок 5 начинает работу по0 еле появления сигнала запуска с блока 3. Адресные сигналы (выходы 30) и сигнал записи на выходе 28 выдаются синхронно с тактовым сигналом на входе 22 с привязкой к импульсам П признака селективной

5 записи (вход 21) в соответствии с режимом, который задается через входы 12.

Формирователь 35 предназначен для выработки сигнала разрешения записи. При этом счетчик 47 служит для отсчета призна0 ков записи после появления сигнала запуска, триггер 48 - для фиксации появления сигнала запуска, а триггер 49 - для фиксации конца отсчета задержки и завершения записи в устройство. Предустановка форми5 рователя осуществляется через входы 24, 25, 26 анализатора. Триггер 34 работает в режиме с положительным интервалом записи и предназначен для выделения интервалов времени, начинающихся с появлением

0 импульсов П признака селективной записи (вход 21) и завершающихся через заданное количество тактов. При отрицательном интервале записи триггер 34 удерживается постоянно в состоянии 1 через вход 12.1.

5 Формирователь сигнала записи 32 предназначен для выработки сигнала записи СЕ 28, по которому тактируется запись в блок памяти 6 и переключается формирователь адреса 31. Кроме того, формирователь 32

0 пропускает тактовый сигнал и сигнал селективной записи для синхронизации работы формирователя адреса 31. Формирователь сигнала записи 32 включает в себя два элемента И 40, 41 и элемент И-ИЛИ-НЕ 42.

5 Дешифратор сброса 33 предназначен для выработки сигналов сброса формирователя адреса 31. Дешифратор сброса 33 имеет два входа стробирования V1, V2 и п+1 входов данных D1,..., Dn+1 и должен отрабатывать функции:

C6p.Q1 Vi V2(p1 «D2HD2 D3)v...v{Dn« Dn+1))

C6p.Q2 Vi - V2((D2 Ф D3) v... „ (Dn Ф Dn + 1))

C6p.Qn Vi- V2(Dn flPDnTl).

Формирователь 36 предназначен для

дешифрации состояний 2i - 1(1 1 п)

адресных сигналов 30. Одно из состояний выделяется мультиплексором 39 в качестве сигнала конца интервала, по которому триггер 34 устанавливается .

Формирователь 31 предназначен для формирования m-разрядных адресов для блока памяти 6, причем группа адресных сигналов состоит из двух подгрупп: сигналов, вырабатываемых счетчиком тактов разрядности J, определяемой заданной длиной интервала L, j log2(L + 1), и сигналов с количеством разрядов m - j, вырабатываемых группой триггеров 46.

Мультиплексор 44 предназначен для параллельной загрузки из вне через входы 26 или подключения к входам О триггеров 46 их инверсных выходов при организации режима двоичного счета для каждого из указанных триггеров.

Мультиплексоры 45.1...45.J-1 служат для организации из j триггеров 46.1...46.J единичного двоичнога счетчика - счетчика тактов, отсчитывающего такты на интервале записи L, мультиплексоры 45.j...45n - для организации счетчика зон из n-j триггеров 46.j+1...46.n и счетчика 43.

Блок 6 предназначен для записи k-раз- рядных логических состояний, поступающих на него через регистр 2 с информационных входов 7 анализатора, и трех служебных сигналов: в (к-Н)-й разряд записывается признак селективной записи, поступающий с формирователя 1, в (к+3)-й разряд- сигнал конца интервала, поступающий с выхода 29 блока 5, и в (к+2)-й разряд - сигнал уровня лог. 1, который является внутренним для блока 6 сигналом. Запись информационных и служебных сигналов в память производится по сигналу записи с выхода 28 блока 5. Содержимое трех служебных разрядов памяти используется для идентификации записанной со входов информации при ее чтении из блока 6. По (k+1)- му разряду определяется ячейка начала или завершения интервала записи, по (к+3)-му разряду определяется факт повторной записи в ячейку при отрицательном интервале записи, и по (к+2)-му разряду определяется факт выполнения записи в ячейку. Через группу входов 13 анализатора осуществляется обнуление всех ячеек памяти перед пуском устройства.

Работа устройства подразделяется на три этапа:

1-й этап: настройка блоков устройства на требуемый режим работы. После поступления по входу 25 группы

14 входов сигнала Сброс на входах 11 и 10 устанавливается соответствующий код режима синхронизации и запуска. Селектор 4 программируется через .входы 9 на поиск 0 конкретных признаков П1...Пр. Через группу 13 входов обнуляется ячейка блока 6, адрес ячеек памяти при этом устанавливается в блоке 5 через входы 23,25,26. На входах 12 устанавливается код режима записи в 5 соответствии с таблицей.

2-й этап: отслеживание условий выработки сигналов запуска и записи, запись входных состояний в блок 6.

После завершения 1-го этапа на входе 0 25 устанавливается лог. 1. На выходе формирователя 35 при этом появляется сигнал разрешения записи, который разрешает формирователю 32 вырабатывать сигнал записи для блока 6 и сигналы синхронизации 5 для формирователя 31. Селектор 4 переводится в режим поиска. При появлении на информационных входах 7 анализатора состояния, совпадающего с одним из заданных признаков П1...ПР, на соответствующем выходе селектора 4 появляется сигнал, который стробируется одним из стробов в фор- мирователе 1, на выходах которого вырабатываются последовательность импульсов и тактовый сигнал. Блок 3 вырабатывает сигнал запуска по одному из кодов, поступающих на него с выходов регистра 2. При появлении сигнала запуска триггер 48 формирователя 35 переводится в состояние 1 и разрешает прохождение импульсов П через элемент И 50 на вход счетчика 47. По окончании отсчета задержки на выходе Р счетчика появляется сигнал, переводящий триггер 49 в состояние О. Сигнал разрешения записи снимается с выхода формирователя 35.

Принцип организации записи в блок 6 тактов.

Запись в режимах 1 и 2 (см. таблицу 1) выполняется стандартным образом - по сигналу 21 или тактовому сигналу 22 последовательно во все ячейки блока 6, пока есть сигнал разрешения записи, с наращиванием адреса на 1. После окончания записи считывания из блока 6 производится так же из последовательно расположенных по адресации ячеек.

В режимах 3, 52п+1 производится

селективная запись с положительным интервалом длиной 2J - 1 тактов ().

Весь блок 6 емкостью 2т (k+З)- разрядных

0

5

0

5

0

5

слов условно разбивается на 2т/2 зон. Выбором ячеек памяти внутри зоны управляют j триггеров 46, которые образуют условно счетчик тактов, выбором зон памяти - триггеры 46.j+1...46.n и счетчик 43, которые ус- ловно образуют счетчик событий (зон). При появлении на информационных входах 7 анализатора состояний, совпадающего с одним из заданных признаков записи П1...ПР, производится запись в блок 6, после чего переключается счетчик зон и выбирается новая зона блока 6. Последующая запись по тактовым сигналам производится последовательно в соседние ячейки памяти выбранной зоны с наращиванием адреса в счетчике тактов на +1. Когда состояние счетчика тактов станет равным 2 -1, на выходе мультиплексора 39 появляется сигнал Конец ин- тервала, запрещающий запись информации до появления следующего при- знака записи. Таким образом, произойдет запись состояний входных сигналов в такте, совпадающем с появлением признака записи и в последующих 2 -1 тактах. Считывание записанной в блок 6 информации должно производиться из ячеек в порядке возрастания адресов.

Селективная запись с отрицательным интервалом записи (режимы 4, 6, ..., 2п+2) отличается от предыдущего режима тем, что запись идет постоянно без прерывания на ожидание появления признака записи. Так же блок 6 условно разбивается на 2m/2j зон. Внутри зоны запись идет в ячейки с циклическим перебором адресов 0, 12 - 1, О,

12 - 1,0, 1... Содержимое ячеек зоны

может многократно обновляться. Переход в следующую зону памяти произойдет после прихода признака записи. В отработавшей зоне останется информация, записан- ная в 2 - 1 тактах непосредственно перед появлением признака, и в такте появления признака П. В новой зоне памяти будет опять многократно обновляться информация до появления очередного признака за- писи. Считывание из блока 6 в данном случае должно производиться по зонам, причем внутри зон первой считывается ячейка, располагающаяся по адресации следом за ячейкой, запись в которую произош- ла в такте появления признака. Идентификатором такой ячейки является единичное значение разряда ячейки, в которой записывается признак селективной записи. Затем считываются ячейки с наращиванием адреса для счетчика тактов на +1 с перебором после адреса 2j - 1 адресов 0, 1, ... и т. д; Последней внутри зоны считывается ячейка, запись в которую произведена в такте появления признака:

Рассмотрим работу блока 5 подробнее.

Уровень лог. 1 сигнала на выходе формирователя 35 разрешает счетный режим работы счетчику 43, через мультиплексор 44 ко входам триггеров 46 подключаются их инверсные выходы, т. е. устанавливается двоичный режим переключения триггеров.

Режим 1. Селективная запись по признакам без интервала.

Согласно таблице, лог. 1 по входу 12.1 устанавливает триггер 34 в 1. Код режима записи на линиях 12.2, 12.3, 12.4, 12.П+2, равным 000 ../ О, и на линиях 12.П+3 ... 12.2п+3, инверсных по отношению к линиям 12.2 ... 12.П+2, равный 1 ... 1, управляет формирователем 32 и мультиплексорами 45 таким образом, что на выход 28 блока 5 проходят через элемент И 40 и верхний конъюнктор элемента И-ИЛИ-НЕ 42 импульсы П со входа 21, а триггеры 46 и счетчик 43 образуют единый двоичный счетчик, младший разряд которого, триггер 46.1, срабатывает по сигналу на входе 28, а на синх- ровход с каждого последующего триггера 46 поступают импульсы П через элемент И 40 и мультиплексор 45 только после установки всех предыдущих триггеров в состояние 1. Таким образом, блок 5 пропускает на выход 28 импульсы селективной записи П, после чего переключает адрес на +1, т. е. осуществляет селективную запись по признакам последовательно во всей ячейки памяти до тех пор, пока формирователь 35 не снимет разрешения записи. В блоке 6 сохранится информация, записанная в 2т тактах появления признаков перед остановом.

Режим 2. Запись в каждом такте,

Этот режим в основном аналогичен предыдущему. Но код на входах 12.2...12.2п+3, обратный устанавливаемому для режима 1, разрешит работу среднего конъюнктора элемента И-ИЛИ-НЕ 42. На выход 28 через формирователь 32 будут проходить тактовые импульсы со входа 22, которые также поступят и на синхровход первого триггера адреса 46, а через элемент И 41 и мультиплексоры 45 тактовые импульсы поступят на триггеры 46.246.п и счетчик 43. Дешифрацию единичных состояний триггеров 46 в этом режиме осуществляет дешифратор 38. Триггеры 46 и счетчик 43 образуют единый m-разрядный двоичный счетчик, срабатывающий в каждом такте, В блоке 6 сихранится информация, записанная в 2Ш тактах перед остановом.

Режимы 4, 62п+2. Селективная запись по признакам с отрицательным интервалом записи в тактах.

Для конкретизации описания зададим интервал записи равным -3 такта, для чего

по входам 12 должен поступать код, соответствующий режиму б (см. таблицу). По- прежнему удерживается триггер разрешения записи 34 в 1. Через элементы И 40 и 41 импульсы П проходят со входа 21 и тактовые импульсы со входа 22. Кодом режима элемента И-ИЛИ-НЕ 42 открыт средний конъюнктор, на выход 28 и на син- хровходы триггеров 46.1, 46.2 будут проходить тактовые итмпульсы, причем из триггеров 46.1 и 46.2 образуются двоичный счетчик тактов, который будет формировать два младших разряда в полном адресе.

Дешифрацию единичного состояния предшествующего триггера 46.1 выполняет дешифратор 38 по выходу 21-1. Код 001 на линиях 12.4, 12.П+4, 12.П+5 разрешает прохождение импульсов П на синхровход С триггера 46.3 без учета состояния предшествующих триггеров 46.1, 46.2. Таким образом, триггер 46.3 срабатывает по каждому импульсу П и является младшим разрядом счетчика зон. Связь триггеров 46.3

46.п и счетчика 43 в единичный двоичный счетчик осуществляется с помощью мультиплексоров 45.3, ..., 45.п. Отличие в том, что О со входа 12.П+4 и, следовательно, дешифрация единичного состояния триггеров 46 будет выполняться без учета состояний триггеров 46.1, 46.2, образующих счетчик тактов. Двоичный счетчик зон формирует разряды адреса ЗОзЗОп30т.

Каждая зона памяти может оказаться недозаполненной, заполненной однократно или многократно обновленной в ожидании признака П. Кроме того, при величине задержки, заданной для формирователя 35, превышающей емкость счетчика зон, может многократно обновляться вся память, в то же время в отдельных зонах ОЗУ может произойти неполное обновление ячеек зоны. Например, на первом цикле работы счетчика зон зона памяти заполнилась полностью, а при записи в ту же зону на следующем цикле работы счетчика зон обновилась только часть ячеек зоны. Это происходит, когда признаки П появляются чаще, чем заданный интервал записи в тактах. Записанная в такой ситуации информация будет принадлежать разным участкам последовательности состояний на входах 7. Считываться должны только те ячейки зоны памяти, которые были обновлены на последнем цикле работы счетчика зон. Для идентификации этих ячеек и служит сигнал на выходе 29 блока 5, который записывается в (к+3)-й разряд ячейки блока 6. Если этот разряд в ячейке, в которую производилась запись в такте признака, хранит 1, то содержимое всех ячеек зоны отражает один непрерывный

участок входной последовательности. Ячейка, соответствующая такту признака, определяется по 1 в (к+1)-м разряде, в который записывается признак селективной записи

(вход 21 блока 5). Ячейки, в которые запись не производилась, определяются по(к+2)-му разряду: перед пуском все разряды ячеек обнуляются, а при выполнении записи в блок 6 в (к+2)-й разряд записывается 1,

формируемая внутри блока 6.

Режимы 3, 52п+1. Селективная запись по признакам с положительным интервалом записи в тактах.

Для конкретизации описания зададим

интервал записи, равный +3 такта. По входам 12 должен поступать код, соответствующий режиму 5 (см. таблицу), отличающийся от кода режима для отрицательного интервала записи -3 такта только

значением бита по входу 12.1. Положительный интервал записи задается сигналом лог. О, который перестает удерживать триггер 34 в 1, и триггер 34 при наличии высокого уровня сигнала на выходе формирователя 35 переходит в состояние 1 при появлении импульса П на входе 21 и в состояние О - при появлении на выходе сигнала конца интервала на выходе мультиплексора 39. Таким образом, импульсы со

входов 21 и 22 проходят через элементы И 40 и 41 на интервале времени, начиная с такта признака и далее в течение интервала записи (трех тактов). Счетчик тактов (триггеры 46i и 462) по завершении интервала записи останется в состоянии 11, заполнятся все ячейки памяти, кроме последней, имеющей адрес по двум младшим разрядам 11. Работа формирователя 32 и мультиплексоров 45 не отличается от работы в паредыдущем режиме. Работа триггера 37 для данного режима несущественна. Как и в режиме записи с отрицательным интервалом, происходит частичное или полное заполнение зон ОЗУ. Если формирователь 35

не снимет сигнал разрешения до конца работы счетчика зон, то начнется повторное заполнение зон памяти. Повторная запись может обновить только часть ячеек зоны, если импульсы П будут идти чаще, чем

заданная длина интервала. Внутри зоны последняя запись делается всегда в такте появления импульса П. Ячейка, в которой по (к+1)-му разряду хранится 1, содержит информацию, принадлежащую такту признака, и все последующие ячейки внутри зоны (если остались таковые) не должны считываться в контроллер.

3-й этап: считывание зарегистрированной информации в контроллер.

Считывание содержимого блока б должно производиться после останова устройства: снятия сигнала разрешения записи блоком 5 или по сигналу Сброс - лог. О на входе 25. После останова устройства тригге- ры 46 и счетчик 43 указывают на ячейку, с которой должно начинаться считывание записанной информации. Порядок перебора ячеек при считывании из блока 6 зависит от режима записи.

Если производилась селективная запись без интервалов или в каждом аткте (режимы 1, 2), то считываются подряд все ячейки, в которых (к+2)-й разряд хранит 1. Перебор адресов должен быть с адреса ос- танова Аост. до А0ст. - 1.

После селективной записи с положительным интервалом (режимы 3.5...) считывание идет по зонам, начиная с зоны останова. В зоне останова перебор адресов делать с Аост. до ячейки, содержащей Т в (к+1)-м разряде, т. е. до ячейки, в которую запись была произведена в такте признака. В остальных зонах считывание с 0-й ячейки и по ячейку с 1 в.(к+1)-м разряде, осталь- ные ячейки зоны не считывать. Заканчивать считывание зоной останова, начиная с 0-й ячейки и по ячейку с адресом А0ст. -1.

После селективной записи с отрицательным интервалом (режимы 4, 6...) считы- вание идет с зоны, следующей за зоной останова. Следует найти внутри зоны ячейку, в которой (к+1)-й разряд хранит 1, Если в этой ячейке (к+3)-й разряд равен 1, то следует считывать внутри зоны, начиная с ячейки, следующей за ячейкой такта .признака ячейки, содержащей 1 в (к+1)-м разряде, и далее все ячейки зоны, перебирая адреса подряд с циклическим переходом с последнего адреса для счетчика тактов на нулевой адрес. Если зона была заполнена не полностью, на что указывает О в (к+3}-м разряде ячеек зоны, то считывание производить внутри зоны, начиная с 0-й ячейки и по ячейку такта признака.

Формула изобретения

1. Логический анализатор, содержащий формирователь импульсов синхронизации, блок запуска, селектор признаков записи, блок управления памятью, блок памяти и буферный регистр, группа информационных входов которого и группа тактовых входов формирователя импульсов синхронизации являются соответственно группой информационных входов и группой тактовых входов анализатора, группа разрядных выходов буферного регистра соединена с первыми группами информационных входов селектора признаков записи, блока памяти и блока запуска, выход которого соединен с входом запуска блока управления памятью, группа выходов которого соединена с первой группой адресных входов блока памяти и образует с первым выходом блока управления памятью первую группу информационных выходов анализатора для считывания слова состояния, группа выходов блока памяти является второй группой информационных выходов анализатора для считывания зарегистрированной информации, группы входов задания режима селектора признаков записи, блока запуска, первая группа входов формирователя импульсов синхронизации и первая группа входов задания режима записи блока управления памятью образуют соответственно первую, вторую, третью и четвертую группы входов задания режимов анализатора, группа выходов селектора признаков записи соединена со второй группой входов задания режима формирователя импульсов синхронизации, первый выход которого соединен с тактовым входом блока управления памятью, второй выход блока управления памятью соединен с входом записи блока памяти, отличающийся тем, что, с целью повышения быстродействия и увеличения полноты контроля, второй выход формирователя импульсов синхронизации соединен с входом признака селективной записи блока управления памятью и с первым информационным входом блока памяти, вход выборки, вход разрешения очистки, вторая группа адресных входов и группа входов сигналов записи которого образуют пятую группу входов задания режимов анализатора, входы сброса, записи, установоч- ный вход и группа входов задания начального состояния блока управления памятью образуют шестую группу входов задания режимов анализатора, третий выход блока управления памятью соединен со вторым информационным входом блока памяти, причем блок управления памятью содержит формирователь сигнала разрешения записи, формирователь сигнала записи, дешифратор сброса, формирователь адреса, первый триггер и формирователь интервала записи, в состав которого входят мультиплексор сигнала конца интервала записи, дешифратор конца интервала записи и второй триггер, формирователь сигнала записи содержит два элемента И и элемет И-ИЛИ-НЕ, кроме того, формирователь адреса содержит группу мультиплексоров, группу триггеров, счетчик и мультиплексор адреса, выходы которого соединены соответственно с информационными входами триггеров группы, инверсные входы сброса которых подключены к группе инверсных

выходов дешифратора сброса, тактовый вход первого триггера группы соединен с инверсным входом разрешения дешифратора сброса и подключен к выходу элемента И-ИЛИ-НЕ, тактовый вход каждого 1-го триггера группы подключен к инверсному выхо- jgy(i - 1)-го мультиплексора группы, где i 2,n, n 1од2(1макс + 1), L-макс - максимально возможная длина (в тактах) интервала записи, инверсный выход n-го мультиплексора группы соединен со счетным входом счетчика, инверсный вход записи которого соединен с адресным входом мультиплексора и подключен к выходу формирователя сигнала разрешения записи, прямой вход разрешения дешифратора сброса соединен с первым входом установки в единицу первого триггера, с первым входом первого элемента И и с тактовым входом формирователя сигнала разрешения записи и является входом признака селективной записи блока управления памятью, выход формирователя сигнала разрешения записи соединен с инверсным входом сброса первого триггера со вторым входом первого элемента И, с первым входом второго элемента И и является первым выходом блока управления памятью, информационный вход первого триггера подключен к шине нулевого потенциала, выход первого триггера соединен с третьим входом первого элемента И и со вторым входом второго элемента И, третий вход которого является тактовым входом блока управления памятью, выход первого элемента И соединен с первым входом элемента И-ИЛИ-НЕ и с первыми информационными входами мультиплексоров группы,вторые информационные входы которых и второй вход элемента И-ИЛИ-НЕ подключены к выходу второго элемента И, третьи информационные входы мультиплексоров группы, третий и четвертый входы элемента И-ИЛИ-НЕ образуют вход записи блока управления памятью, выход элемента И-ИЛИ-НЕ является вторым выходом блока управления памятью, первые, вторые и третьи адресные входы мультиплексоров группы, информационные входы дешифратора сброса, второй вход установки в единицу первого триггера и пятый и шестой входы элемента И-ИЛИ-НЕ образуют группу входов задания режима записи блока управления памятью, четвертые адресные входы мультиплексоров группы подключены к прямым выходам триггеров группы, инверсные выходы которых соединены с первой группой информационных входов мульттиплексора адреса, вторая группа информационных входов которого, группа информационных входов счетчика и

группа входов задания начального состояния формирователя сигнала разрешения записи образуют группу входов задания начального состояния блока управления памятью, пятые адресные входы мультиплексоров группы подключены к группе выходов дешифратора конца интервала записи, шестой адресный вход первого мультиплексора группы подключен к шине

0 единичного потенциала, шестой адресный вход каждого i-ro мультиплексора группы подключен к прямому выходу (i - 1}-го мультиплексора группы, прямые выходы триггеров группы соединены со входами

5 дешифратора конца интервала записи, группа выходов которого соединена с группой информационных входов мультипилек- сора сигнала конца интервала записи, адресные входы которого попарно объеди0 нены с информационными входами дешифратора сброса, начиная со второго , выход мультиплексора сигнала конца интервала записи соединен с тактовыми входами первого и второго триггеров, информационный

5 вход второго триггера подключен к шине единичного потенциала, выход второго триггера является третьим выходом блока управления памятью, первый инверсный выход группы инверсных выходов дешифра0 тора сброса соединен с инверсным входом сброса второго триггера, входы запуска, сброса и установочный вход формирователя сигнала разрешения записи являются одноименными входами блока управления па5 мятью, прямые выходы триггеров группы и разрядные выходы снетчика образуют группу выходов блока управления памятью.

2. Анализатор по п. 1, отличающий- с я тем, что формирователь сигнала разреше0 ния записи содержит счетчик, два триггера и два элемента И, первый вход первого из которых является входом признака селективнойзаписиформирователя, информационные входы первого и второго

5 триггеров подключены к шинам единичного и нулевого потенциалов соответственно, выход первого триггера соединен со вторым входом первого элемента И, выход которого соединен с вычитающим входом счетчика,

0 инверсный вход записи которого является установочным входом формирователя, группа информационных входов счетчика является группой входов задания начального состояния входов формирователя, выход за5 ема счетчика соединен с тактовым входом второго триггера, выход которого соединен с первым входом второго элемента И, выход которого является выходом формирователя, инверсный вход сброса первого триггера соединен с инверсным входом установки в

15173062716

единицу второго триггера, со вторым вхо- вого триггера является входом запуска фордом второго элемента И и является входом мирователя. сброса формирователя, тактовый вход пер

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Устройство для кусочно-линейной аппроксимации | 1990 |

|

SU1837272A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Сигнатурный анализатор | 1988 |

|

SU1580366A1 |

Изобретение относится к вычислительной технике и может быть использовано как средство контроля и отладки цифровых устройств и микропроцессорных систем. Цель изобретения - повышение быстродействия и увеличение полноты контроля. Анализатор позволяет контролировать данные, поступающие с информационных входов устройства в реальном масштабе времени, и сохранять информацию, относящуюся к определенным событиям. Реализованная в устройстве возможность выбора длины и знака интервала, в течение которого производится запись входных состояний, относящихся к заранее заданным событиям, позволяет отсеять несущественную информацию, ускорить процедуру контроля. Кроме того, повышается достоверность контроля, так как сбор информации при появлении событий производится в течение одного непрерывного-эксперимента с одинаковыми условиями протекания. Устройство особенно эффективно при контроле микропроцессорных систем, стыковке их программных и аппаратных средств. 1 з. п. ф-лы, 4 ил. (Л С

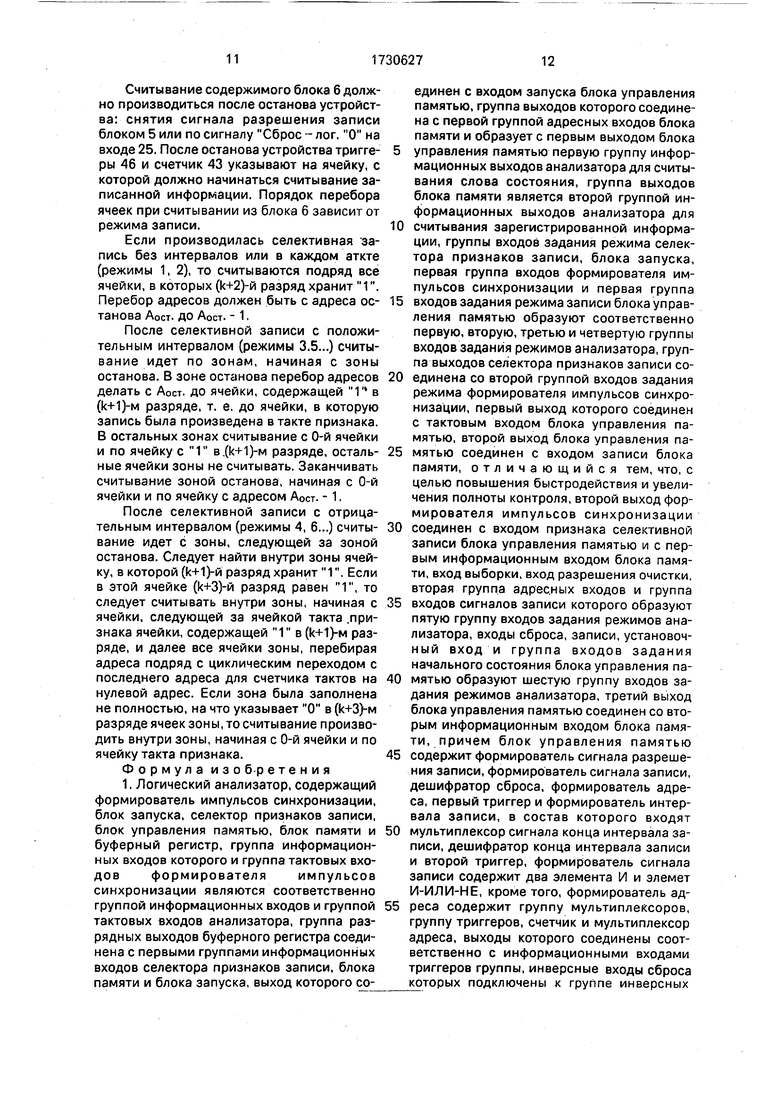

Примечание. код на линиях 12 nt.v .. 12 n4.j устанавливается инверсным

относительно кода на линиях соответственно 12/,... 12(но.

ФигМ

| Авторское свидетельство СССР № 754424,кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-30—Публикация

1989-09-26—Подача