Изобретение относится к вычислительной технике и электросвязи и может быть использовано в системах преобразования и передачи информа- ции.

Цель изобретения - увеличение отношения сигнал/шум.

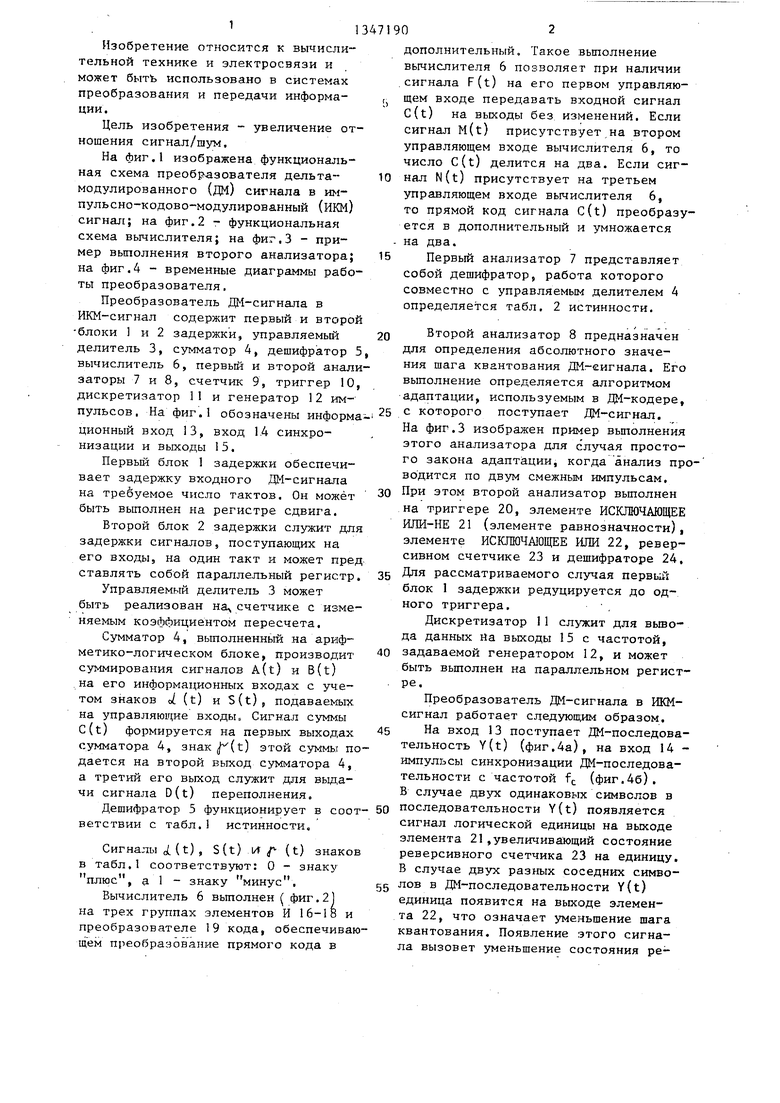

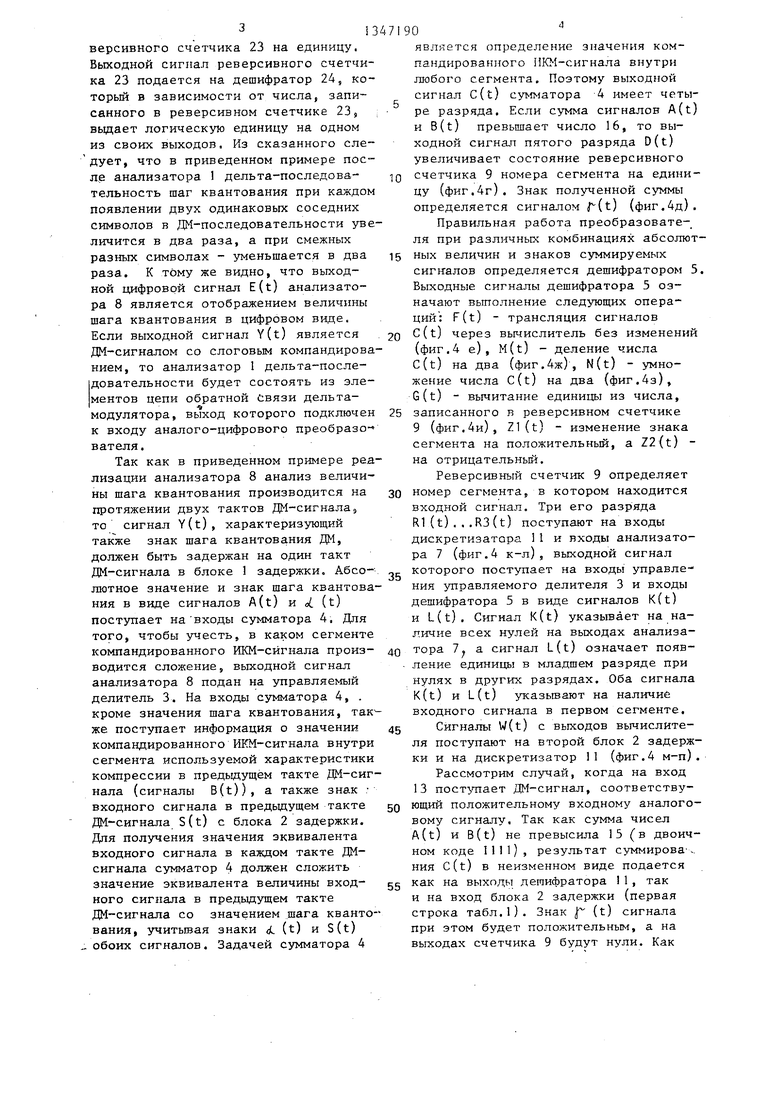

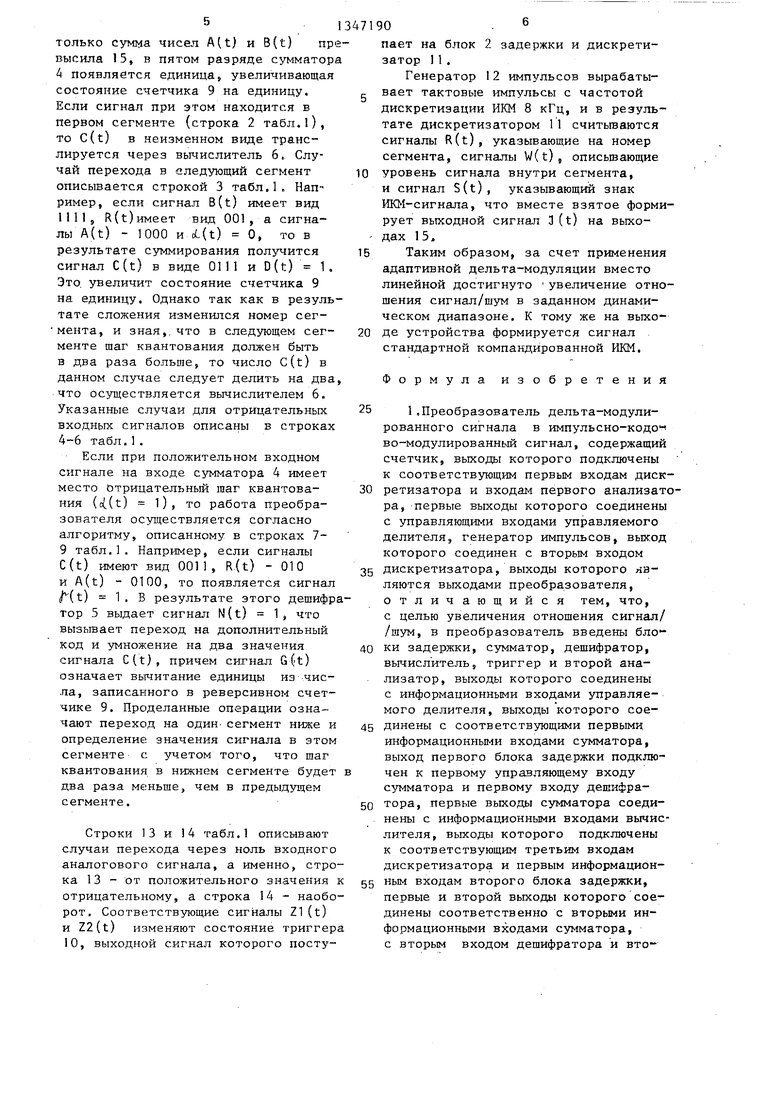

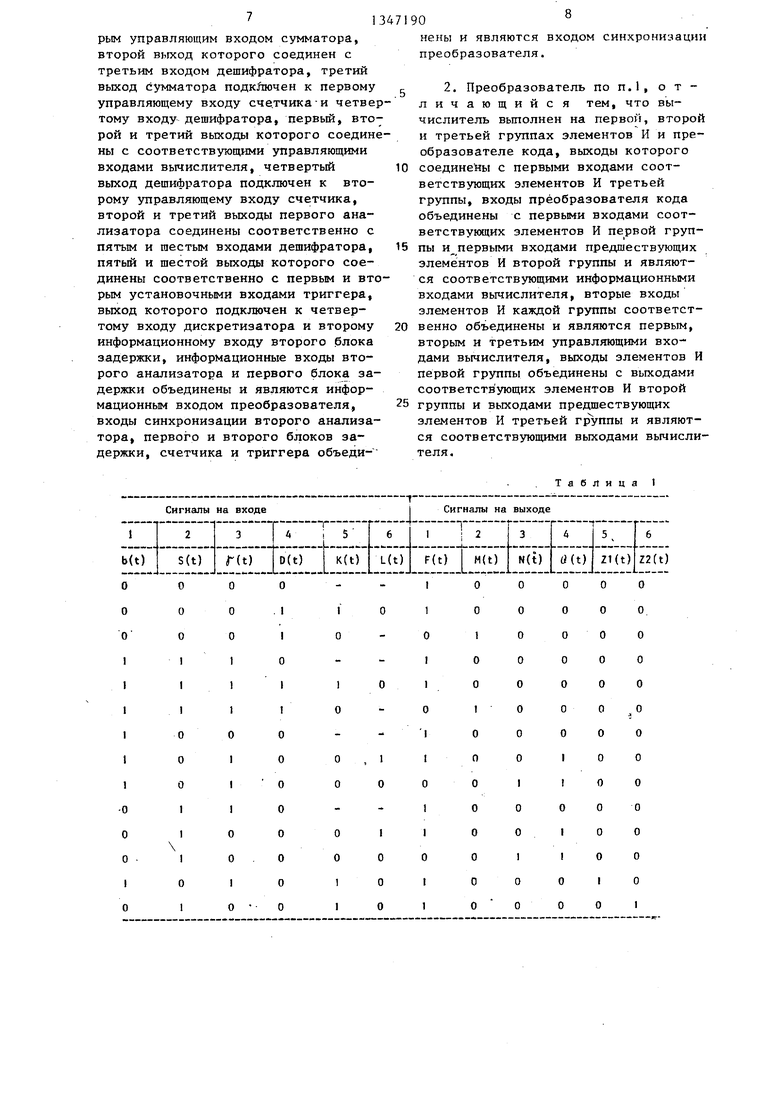

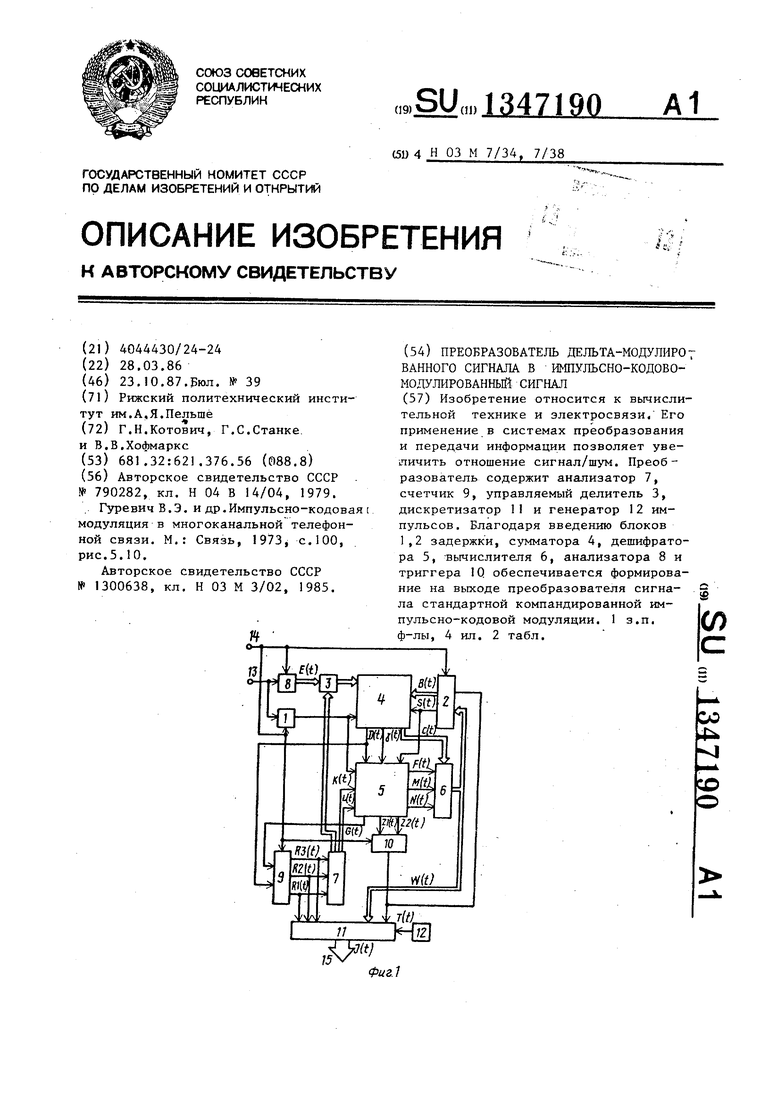

На фиг,1 изображена функциональная схема преобразователя дельта- модулированного (ДМ) сигнала в им- пульсно-кодово-модулированный (ИКМ) сигнал; на фиг.2 - функциональная схема вычислителя; на фи:г.З - пример выполнения второго анализатора; на фиг.4 - временные диаграммы работы преобразователя.

Преобразователь ДМ-сигнала в ИКМ-сигнал содержит первый и второй -блоки 1 и 2 задержки, управляемый делитель 3, сумматор 4, дешифратор 5 вычислитель 6, первый и второй анализаторы 7 и 8, счетчик 9, триггер 10, дискретизатор 1 и генератор 12 импульсов. На фиг.1 обозначены информа ционный вход 13, вход 1.4 синхронизации и выходы 15,

Первый блок 1 задержки обеспечивает задержку входного ДМ-сигнала на требуемое число тактов. Он может быть выполнен на регистре сдвига.

Второй блок 2 задержки служит для задержки сигналов, поступающих на его входы, на один такт и может представлять собой параллельный регистр.

Управляемый делитель 3 может быть реализован на счетчике с изменяемым коэффициентом пересчета.

Сумматор 4, выполненный на арифметико-логическом блоке, производит суммирования сигналов A(t) и B(t) на его информационных входах с учетом знаков oi (t) и S(t)5 подаваемых на управляющие входы. Сигнал суммы C(t) формируется на первых выходах сумматора 4, знак l(t этой суммы подается на второй выход сумматора 4, а третий его выход служит для вьща- чи сигнала D(t) переполнения.

Дешифратор 5 функционирует в соответствии с табл,1 истинности.

Сигналы oL(t), S(t) i/f / (t) знаков в табл, соответствуют: О - знаку плюс, а 1 - знаку минус.

Вычислитель 6 вьтолнен ( фиг,21 на трех группах элементов И 16-18 и преобразователе 19 кода, обеспечивающем преобразование прямого кода в

дополнительный. Такое выполнение вычислителя 6 позволяет при наличии сигнала F(t) на его первом управляющем входе передавать входной сигнал C(t) на выходы без изменений. Если сигнал M(t) присутствует на втором управляющем входе вычислителя 6, то число C(t) делится на два. Если сигнал N(t) присутствует на третьем управляющем входе вычислителя 6, то прямой код сигнала C(t) преобразуется в дополнительный и умножается на два.

Первый анализатор 7 представляет собой дешифратор, работа которого совместно с управляемьм делителем 4 определяется табл, 2 истинности.

Второй анализатор 8 предназначен для определения абсолютного значения шага квантования ДМ-еигнала, Его выполнение определяется алгоритмом адаптации, используемым в ДМ-кодере, с которого поступает ДМ-сигнал. На фиг.3 изображен пример выполнения этого анализатора для случая простого закона адаптации, когда анализ про- водится по двум смежным импульсам, 0 При этом второй анализатор выполнен на триггере 20, элементе ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 21 (элементе равнозначности), элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 22, реверсивном счетчике 23 и дешифраторе 24. 5 Для рассматриваемого случая первый блок 1 задержки редуцируется до одного триггера, .

Дискретизатор 11 служит для вывода данных На выходы 15 с частотой, задаваемой генератором 12, и может быть выполнен на параллельном регистре.

Преобразователь ДМ-сигнала в ИКМ- сигнал работает следующим образом.

На вход 13 поступает ДМ-последова- тельность Y(t) (фиг,4а), на вход 14 - импульсы синхронизации ДМ-последова- тельности с частотой f (фиг,4б). В случае двух одинаковых символов в последовательности Y(t) появляется сигнал логической единицы на выходе элемента 21,увеличивающий состояние реверсивного счетчика 23 на единицу. В случае двух разных соседних симво- 5 лов в ДМ-последовательности Y(t) единица появится на выходе элемента 22, что означает уменьшение шага квантования. Появление этого сигнала вызовет уменьшение состояния ре0

5

0

1

версивного счетчика 23 на единицу. Выходной сигнал реверсивного счетчика 23 подается на дешифратор 2Д, ко- торьш в зависимости от числа, записанного в реверсивном счетчике 23, вьщает логическую единицу на одном из своих выходов. Из сказанного следует, что в приведенном примере после анализатора 1 дельта-последова- тельность шаг квантования при каждом появлении двух одинаковых соседних символов в ДМ-последовательности увеличится в два раза, а при смежных разных символах - уменьшается в два раза. К тому же видно, что выходной цифровой сигнал E(t) анализатора 8 является отображением величины шага квантования в цифровом виде. Если выходной сигнал Y(t) является ДМ-сигналом со слоговым компандирова нием, то анализатор 1 дельта-последовательности будет состоять из элементов цепи обратной Связи дельта- модулятора, выход которого подключен к входу аналого-цифрового преобразо- вателя.

Так как в приведенном примере реализации анализатора 8 анализ величины шага квантования производится на протяжении двух тактов ДМ-сигналаэ то сигнал Y(t), характеризующий также знак шага квантования ДМ, должен быть задержан на один такт

ДМ-сигнала в блоке 1 задержки, Абсолютное значение и знак шага квантования в виде сигналов A(t) и oi (t) поступает на входы сумматора 4, Для того, чтобы учесть, в каком сегменте компандированного ИКМ-сйгнала произ- водится сложение 5 выходной сигнал анализатора 8 подан на управляемый делитель 3. На входы сумматора 4, . кроме значения шага квантования, так - же поступает информация о значении компандированного ИКМ-сигнала внутри сегмента используемой характеристики компрессии в предыдущем такте ДМ-сигнала (сигналы B(t)), а также знак входного сигнала в предьщущем такте ДМ-сигнала S{t) с блока 2 задержки. Для получения значения эквивалента входного сигнала в каждом такте ДМ- сигнала сумматор 4 должен сложить значение эквивалента величины вход- кого сигнала в предыдущем такте ДМ-сигнала со значением шага квантования, учитьгоая знаки «L (t) и S(t) обоих сигналов. Задачей сумматора 4

ig 15 0 5

о

5

о 5 0 g

90

является определение значения компандированного ИКМ-сигнала внутри любого сегмента. Поэтому выходной сигнал C{t) cy {мaтopa 4 имеет четыре разряда. Если сумма сигналов A(t) и B(t) превышает число 16, то выходной сигна,п пятого разряда D(t) увеличивает состояние реверсивного счетчика 9 номера сегмента на единицу (фиг.4г). Знак полученной суммы определяется сигналом rCt) (фиг.4д). Правильная работа преобразовате- ля при различных комбинациях абсолютных величин и знаков суммируемых сигналов определяется дешифратором 5. Выходные сигналы дешифратора 5 означают выполнение следующих операций: F(t) - трансляция сигналов C(t) через вычислитель без изменений (фиг.4 е), M(t) - деление числа C(t) на два (фиг.4ж), N(t) - умножение числа C(t) на два (фиг.4з), G(t) - вычитание единицы из числа, записанного в реверсивном счетчике 9 (фиг,4и), Z1 (t) - изменение знака сегмента на положительный, а Z2(t) - на отрицательньй.

Реверсивный счетчик 9 определяет номер сегмента, в котором находится входной сигнал. Три его разряда R1(t).,.R3(t) поступают на входы дискретизатора I1 и входы анализатора 7 (фиг,4 к-л)5 выходной сигнал которого поступает на входы управления управляемого делителя 3 и входы дешифратора 5 в виде сигналов K(t) и L(t), Сигнал K(t) указывает на наличие всех нулей на выходах анализатора 7у а. сигнал L(t) означает появление единицы в младшем разряде при нулях в других разрядах. Оба сигнала K(t) и L(t) указывают на наличие входного сигнала в первом сегменте.

Сигналь W(t) с выходов вычислителя поступают на второй блок 2 задержки и на дискретизатор 11 (фиг.4 м-п).

Рассмотрим случай, когда на вход 13 поступает ДМ-сигнал, соответствующий положительному входному аналоговому сигналу. Так как сумма чисел A(t) и B(t) не превысила 15 (в двоичном коде 1111) , результат суммирова ния C(t) в неизменном виде подается как на выходы дешифратора 11, так и на вход блока 2 задержки (первая строка табл,1). Знак (t) сигнала при этом будет положительным, а на выходах счетчика 9 будут нули. Как

только чисел A(t) и B(t) превысила 15, в пятом разряде сумматора 4 появляется единица, увеличивающая состояние счетчика 9 на единицу. Если сигнал при этом находится в первом сегменте (строка 2 табл.1), то C(t) в неизменном виде транслируется через вычислитель 6, Случай перехода в следующий сегмент описывается строкой 3 табл.1. Например, если сигнал B(t) имеет вид nil, R(t) имеет вид 00 , а сигналы A(t) - 1000 и (t) 0, то в результате суммирования получится сигнал C(t) в виде 0111 и D(t) 1. Это. увеличит состояние счетчика 9 на единицу. Однако так как в результате сложения изменился номер сег- мента, и зная,, что в следующем сег- менте шаг квантования должен быть в два раза больше, то число C(t) в данном случае следует делить на два что осуществляется вычислителем 6. Указанные случаи для отрицательных входньпс сигналов описаны в строках 4-6 табл.1.

Если при положительном входном сигнале на входе сумматора 4 имеет место Отрицательный шаг квантова- ния (ti(t) 1), то работа преобразователя осуществляется согласно алгоритму, описанному в строках 7- 9 табл.1. Например, если сигналы C(t) имеют вид ООП, R(t) - 010 и A(t) - 0100, то появляется сигнал /(t) 1. В результате этого дешифртор 5 выдает сигнал N(t) 1, что вызьшает переход на дополнительный код и умножение на два значения сигнала C(t), причем сигнал G(it) означает вычитание единицы из числа, записанного в реверсивном счетчике 9. Проделанные операции означают переход на один-сегмент ниже и определение значения сигнала в этом сегменте с учетом того, что шаг квантования в нижнем сегменте будет два раза меньше, чем в предыдущем сегменте.

Строки 13 и 14 табл.1 описывают случаи перехода через ноль входного аналогового сигнала, а именно, строка 13 - от положительного значения отрицательному, а строка 14 - наоборот. Соответствующие сигналы Z1(t) и Z2(t) изменяют состояние триггер 10, выходной сигнал которого посту90. 6

пает на блок 2 задержки и дискрети- затор 11.

Генератор 12 импульсов вырабатывает тактовые импульсы с частотой дискретизации ИКМ 8 кГц, и в результате дискретизатором 11 считьгааются сигналы R(t), указывающие на номер сегмента, сигналы WCt), описьшающие уровень сигнала внутри сегмента, и сигнал S(t), указывающий знак ИКМ-сигнала, что вместе взятое формирует выходной сигнал 3(t) на выходах 15,

Таким образом, за счет применения адаптивной дельта-модуляции вместо линейной достигнуто увеличение отношения сигнал/шум в заданном динамическом диапазоне. К тому же на выходе устройства формируется сигнал стандартной компандированной ИКМ.

Формула изобретения

1.Преобразователь дельта-модули- рованного сигнала в импульсно-кодо во-модулированный сигнал, содержащий счетчик, выходы которого подключены к соответствующим первым входам диск ретизатора и входам первого анализатра, первые выходы которого соединены с управляющими входами управляемого делителя, генератор импульсов, выход которого соединен с вторым входом дискретизатора, выходы которого являются выходами преобразователя, отличающийся тем, что, с целью увеличения отношения сигнал/ /шум, в преобразователь введены блоки задержки, сумматор, дешифратор, вычислитель, триггер и второй анализатор, выходы которого соединены с информационными входами управляемого делителя, выходы которого соединены с соответствующими первыми информационными входами сумматора, выход первого блока задержки подключен к первому управляющему входу сумматора и первому входу дешифратора, первые выходы сумматора соединены с информационными входами вычислителя, выходы которого подключены к соответствующим третьим входам дискретизатора и первым информационным входам второго блока задержки, первые и второй выходы которого соединены соответственно с вторыми информационными входами сумматора, с вторым входом дешифратора и вто/1

рым управляющим входом сумматора, второй выход которого соединен с третьим входом дешифратора, третий

выход сумматора подключен к первому

управляющему входу сче,тчика-и четветому входу дешифратора, первый, второй и третий выходы которого соединны с соответствующими управляющими входами вычислителя, четвертый выход дешифратора подключен к второму управляющему входу счетчика, второй и третий выходы первого анализатора соединены соответственно с пятым и шестым входами дешифратора, пятый и шестой выходы которого соединены соответственно с первым и втрым установочными входами триггера, выход которого подключен к четвертому входу дискретизатора и второму информационному входу второго блока задержки, информационные входы второго анализатора и первого блока задержки объединены и являются информационным входом преобразователя, входы синхронизации второго анализатора, первого и второго блоков задержки, счетчика и триггера объеди

8

иены и являются входом синхронизаци преобразователя.

2. Преобразователь по п.1, отличающийся тем, что вычислитель вьшолнен на первой, второй и третьей группах элементов И и преобразователе кода, выходы которого соединены с первыми входами соответствующих элементов И третьей группы, входы преобразователя кода объединены с первыми входами соответствующих элементов И первой группы и первыми входами предшествующих элементов И второй группы и являются соответствующими информационньми входами вычислителя, вторые входы элементов И каждой группы соответственно объединены и являются первым, вторым и третьим управляющими входами вычислителя, выходы элементов И первой группы объединены с выходами соответств ующих элементов И второй группы и выходами предшествующих элементов И третьей группы и являются соответствующими выходами вычислителя.

Таблица I

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь дельта-модулированного сигнала в импульсно-кодово-модулированный сигнал | 1988 |

|

SU1533006A1 |

| Кодирующее устройство с дельта-модуляцией и импульсно-кодовой модуляцией | 1984 |

|

SU1182681A2 |

| Кодирующее устройство с дельтамодуляцией и импульсно-кодовой модуляцией | 1977 |

|

SU661789A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодомодулированный сигнал | 1985 |

|

SU1282336A1 |

| Адаптивный импульсно-кодовый модулятор | 1985 |

|

SU1300638A1 |

| АНАЛОГОВО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СИГНАЛОВ | 2017 |

|

RU2665245C1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Устройство для измерения характеристики квантования передатчика сигналов с импульсно-кодовой модуляцией | 1980 |

|

SU946005A1 |

| Преобразователь импульсно-кодомодулированных сигналов в дельта-модулированные сигналы | 1985 |

|

SU1264347A1 |

| Преобразователь компандированногодЕльТА-пОТОКА B иКМ СигНАл | 1979 |

|

SU822354A1 |

Изобретение относится к вычислительной технике и электросвязи/ Его применение в системах преобразования и передачи информации позволяет увеличить отношение сигнал/шум. Преобразователь содержит анализатор 7, счетчик 9, управляемый делитель 3, дискретизатор 11 и генератор 12 импульсов. Благодаря введению блоков 1,2 задержки, сумматора 4, дешифратора 5, вычислителя 6, анализатора 8 и триггера 10 обеспечивается формирование на выходе преобразователя сигнала стандартной компандированной им- пульсно-кодовой модуляции. 1 з.п. ф-лы, 4 ил, 2 табл. i (Л со со / Фиг.1

Авторы

Даты

1987-10-23—Публикация

1986-03-28—Подача