II

г«)

сп

со

ОЭ

оэ

31

Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах пердачи сигналов для стыковки каналов с дельта-модуляцией (ДН) с каналами импульсно-кодовой модуляцией (ИКМ).

Цель изобретения - повышение точности преобразования за счет расширения динамического диапазона преобраз емых сигналов.

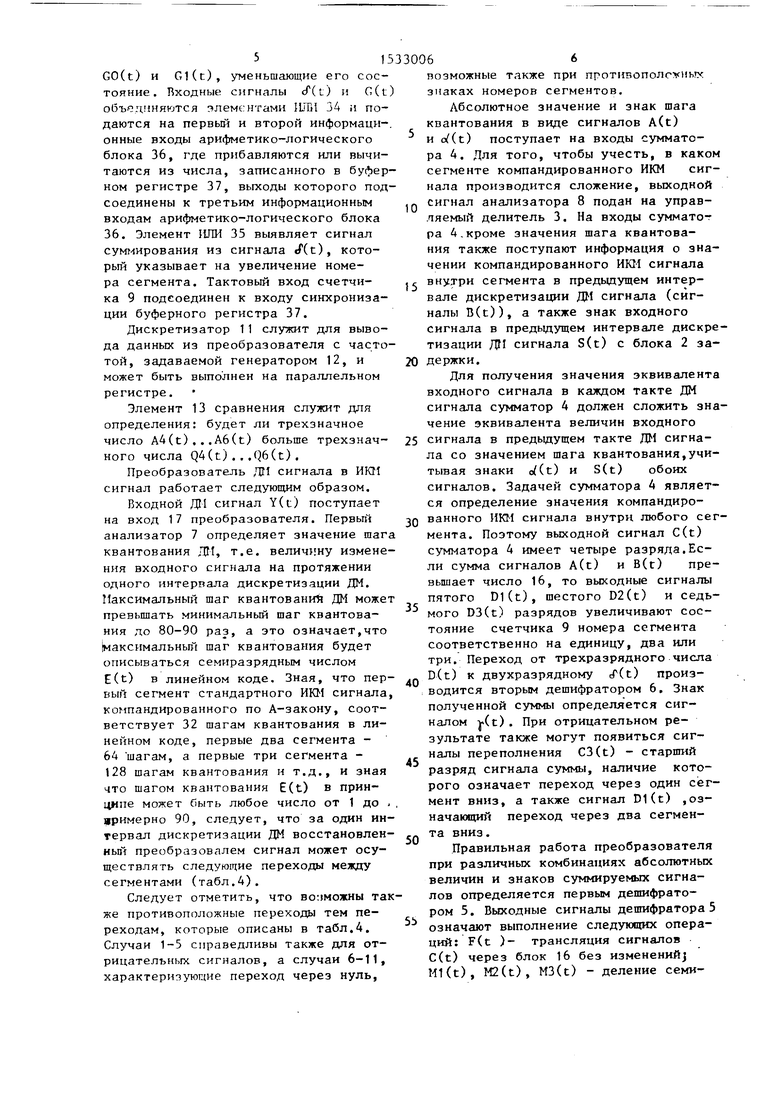

На фиг.1 приведена блок-схема преобразователя j на фиг.2 и 3 - примеры выполнения соответственно блока преобразования кодов и счетчика импульсов .

Преобразователь ДМ сигнала в ИКМ сигнал содержит первый и второй блоки 1 и 2 задержки, управляемый делитель 3, сумматор 4, первый и второ дешифраторы 5 и 6, первый и второй анализаторы 7 и 8 сигнала, счетчик 9 импульсов, триггер 10, дискретиэатор 11, генератор 12 импульсов, элемент 1 сравнения, блок 14 ключей, элемент 1ШИ 15 и блок 16 преобразования кодов. Па фиг.1 обозначены информационный вход 17, вход 18 синхронизации и выходы 19.

Первый блок 1 задержки обеспечивает задержку входного ДМ сигнала на требуемое число тактов. Он может быт выполнен на регистре сдвига. Второй блок 2 задержки служит для задержки сигналов, поступающих на его входы, на один такт и может представлять собой параллельный регистр. Управляемы делитель 3 может быть реализован на счетчике с изменяемым коэффициентом пересчета.

Сумматор 4, выполненный на арифметико-логическом блоке, производит суммирование сигналов А(с) и B(t) на его информационных входах с учетом знаков o((t) и S(t), подаваемых на управляющие входы. Сигнал суммы C(t) формируется на первых выходах сумматора 4. Знак -j-Ct) этой суммы подается на второй выход сумматора 4 а третие его выходы служат для выдачи сигналов D(t) переполнения.которые характеризуют переход входного сигнала на один, два или три сегмента выше.

Первый дешифратор 5 функционирует в соответствии с табл.1. В сигналах e((t) , S(t) и y(t) О соответствует знаку +, а 1 - знаку -. Сиг5

0

0

5

0

5

0

нал Н(г) соответствует случав, когда число A(t) больше числс СКО

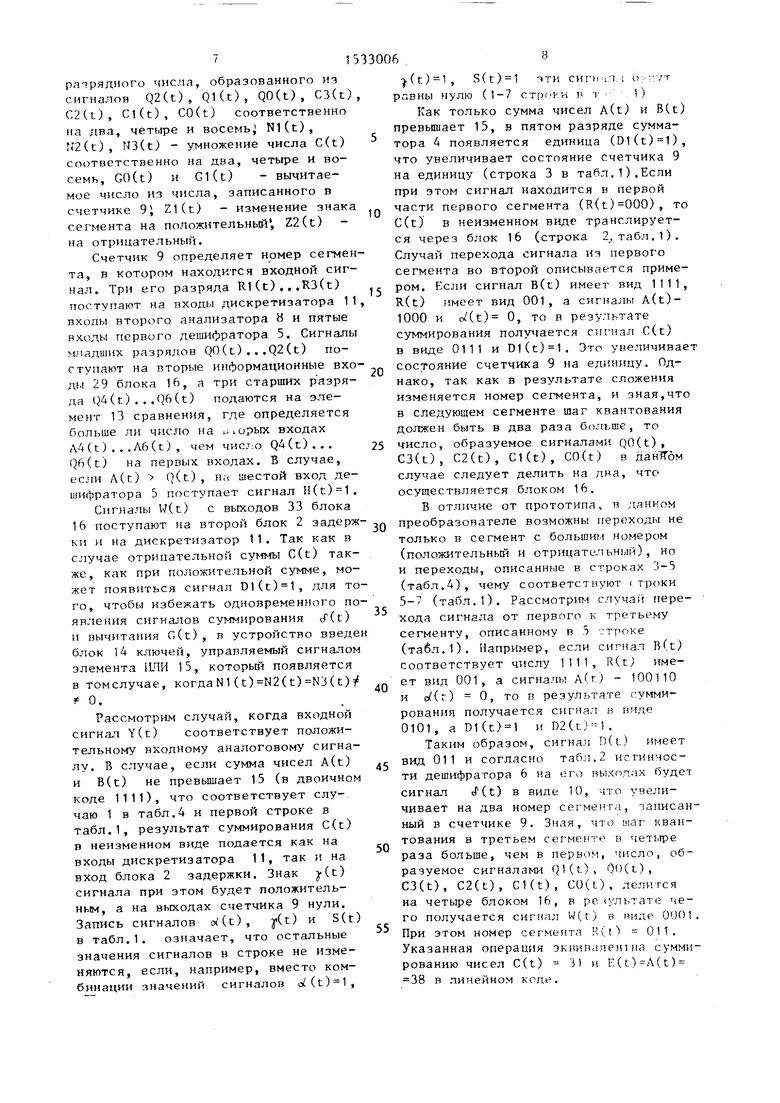

Блок 16 преобразования кодов содержит (фиг.2) преобразователь 20 прямого кода в дополнительный и группы 21-27 элементов И. На фиг.2 обозначены первые и вторые информационные входы 28 и 29, первый, вторые и третьи управляющие входы 30-32 и выходы 33. Такое выполнение блока 16 позволяет при наличии сигнала F(t) на его первом управляющем входе 30 передавать входной сигнал C(t) на выходе 33 без изменений. Если на вторых управляющих входах 31 блока 16 присутствует один из сигналов Ml(t), M2(tJ или M3(t), то число, получаемое при объединении сигналов Q2(t), Ql(t), Q0(t), C3(t), C2(t), Cl(t), C0(t), делится соответственно на 2,4 и 8. Если на третьих управляющих входах 32 блока 16 присутствует один из сигналов Nl(t), N2(t) или N3(t), то прямой код сигнала преобразуется в дополнительный и умножается на два в случае присутствия на входе 32 блока 16 сигнала N(t), на четыре - в случае присутствия сигнала N2(t) и на восемь - при наличии сигнала N3(t).

Второй дешифратор 6 работает согласно табл.2.

Первый анализатор 7 сигнала предназначен для определения абсолютного значения шага квантования ДН сигнала. Его выполнение определяется алгоритмом адаптации входного ДМ сигнала. Второй анализатор 8 сигнала представляет собой дешифратор, работа которого совместно с управляемым делителем 3 и блоком 16 определяется табл.3 истинности.

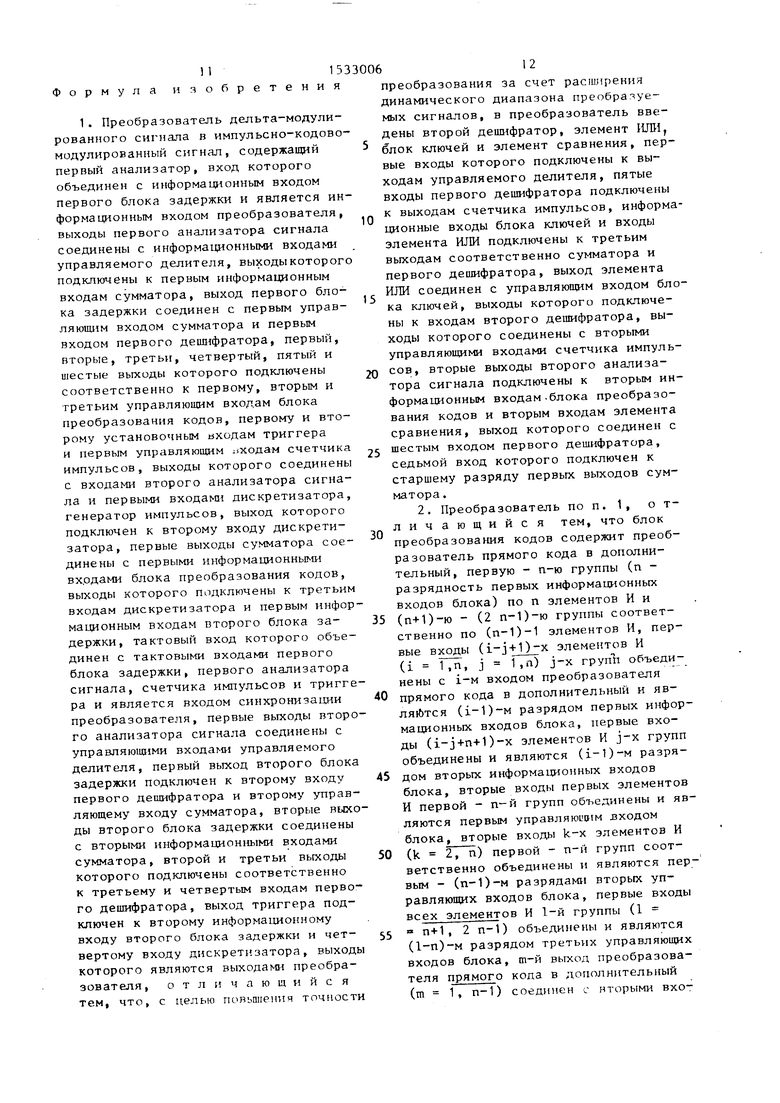

Счетчик 9 импульсов предназначен для определения и хранения номера сегмента, в котором находится входной сигнал. Возможный вариант реализации счетчика 9 показан на фиг.З. Счетчик 9 содержит элемент ИЛИ 34 и 35, арифметико-логический блок 36 и буферный регистр 37. С учетом того, что число, записанное в счетчике 9, за один интервал дискретизации может измениться на один, два и три, то на его первые управляющие входы поступают сигнал fO(t) и cPl(t), увеличивающие состояние счетчика 9, а на вторые управляющие входы - сигналы

G0(t) и Gl(r), уменьшающие его состояние. Входные сигналы f(t) и G(O объединяются neMt нтами ИЛИ ЗА и подаются на первый и второй информационные входы арифметико-логического блока 36, где прибавляются или вычитаются из числа, записанного в буферном регистре 37, выходы которого подсоединены к третьим информационным входам арифметико-логического блока 36. Элемент ИЛИ 35 выявляет сигнал суммирования из сигнала J(t), который указывает на увеличение номера сегмента. Тактовый вход счетчика 9 подсоединен к входу синхронизации буферного регистра 37.

Дискретизатор 11 служит для вывода данных из преобразователя с частотой, задаваемой генератором 12, и может быть выполнен на параллельном регистре.

Элемент 13 сравнения служит для определения: будет ли трехзначное число A4(t)..,A6(t) больше трехзначного числа Q4(tJ..,Q6(t).

Преобразователь ДМ сигнала в ИКМ сигнал работает следующим образом.

Входной ДН сигнал Y(U поступает на вход 17 преобразователя. Первый анализатор 7 определяет значение шага квантования ДН, т.е. величину изменения входного сигнала на протяжении одного интервала дискретизации ДМ. Максимальный шаг квантовании ДМ может превышать минимальный шаг квантования до 80-90 раз, а это означает,что максимальный шаг квантования будет описываться семиразрядным числом E(t) в линейном коде. Зная, что первый сегмент стандартного ИКМ сигнала, компандированного по А-закону, соответствует 32 шагам квантования в линейном коде, первые два сегмента - 64 шагам, а первые три сегмента - 128 шагам квантования и т.д., и зная что шагом квантования E(t) в принципе может быть любое число от 1 до . примерно 90, следует, что за один интервал дискретизации ДМ восстановленный преобразовалем сигнал может осуществлять следующие переходы между сегментами (табл.4).

Следует отметить, что возможны также противоположные переходы тем переходам, которые описаны в табл.4. Случаи 1-5 справедливы также для отрицательных сигналов, а случаи 6-11, характеритуюцие переход через нуль,

0

5

0

5

возможные также при противоположных знаках номеров сегментов.

Абсолютное значение и знак шага квантования в виде сигналов A(t) и o(t) поступает на входы сумматора 4. Для того, чтобы учесть, в каком сегменте компандированного ИКМ сигнала производится сложение, выходной сигнал анализатора 8 подан на управ- аяемый делитель 3. На входы сумматора 4.кроме значения шага квантования также поступают информация о значении компандированного ИШ сигнала внутри сегмента в предыдущем интервале дискретизации ДМ сигнала (сигналы В(с)), а также знак входного сигнала в предыдущем интервале дискретизации ДМ сигнала S(t) с блока 2 задержки.

Для получения значения эквивалента входного сигнала в каждом такте ДМ сигнала сумматор 4 должен сложить значение эквивалента величин входного сигнала в предыдущем такте ДМ сигнала со значением шага квантования,учитывая знаки o((t) и S(t) обоих сигналов. Задачей сумматора 4 является определение значения компандированного ИКМ сигнала внутри любого сегмента. Поэтому выходной сигнал C(t) сумматора 4 имеет четыре разряда.Если сумма сигналов A(t) и В(г) превышает число 16, то выходные сигналы пятого D1(t), шестого D2(t) и седьмого D3(t) разрядов увеличивают состояние счетчика 9 номера сегмента соответственно на единицу, два или три. Переход от трехразрядного числа D(t) к двухразрядному cf(t) производится вторым дешифратором 6. Знак полученной суммы определяется сигналом f(t). При отрицательном результате также могут появиться сигналы переполнения C3(t) - старший разряд сигнала суммы, наличие которого означает переход через один сегмент вниз, а также сигнал Dl(t) .означающий переход через два сегмента вниз.

Правильная работа преобразователя при различных комбинациях абсолютных величин и знаков суммируемых сигналов определяется первым дешифратором 5. Выходные сигналы дешифратора 5 означают выполнение следующих операций: F(t )- трансляция сигналов C(t) через блок 16 без изменений M1(t), M2(t), M3(t) - деление семи0

0

5

0

i

разрядного числа, образованного нз сигналов Q2(t), Ql(t), Q0(t), C3(t) C2(i), Cl(t), C0(t) соответственно на два, четыре и восемь N1(t), N2(t), N3(t) - умножение числа C(t) соответственно на два, четыре и восемь, G0(t) и G(t) - вычитаемое число из числа, записанного в счетчике 9 Z1(t) - изменение знака сегмента на положительный , Z2(t) - на отрицательный.

Счетчик 9 определяет номер сегмента, в котором находится входной сигнал. Три его разряда R1(t)..,R3(t) поступают на пходы дискретизатора 11 входы второго анализатора 8 и пятые входы первого дешифратора 5. Сигналы младших разрядов Q0(t)...Q2(t) поступают на вторые информационные входы 29 блока 16, а три старших разряда Q4(t)..,Q6(t) подаются на элемент 13 сравнения, где определяется больше ли число на 1орых входах A4(t) . . .A6(t) , чем чис.т.о Q4(t)... Q6(t) на первых входах. В случае, если А(О Q(t), на шестой вход дешифратора 5 поступает сигнал H(t)1.

Сигналы W(t) с выходов 33 блока 16 поступают на второй блок 2 задержки и на дискретизатор 11. Так как в случае отрицательной суммы C(t) так- как при положительной сумме, може,

жет появиться сигнал Dl(t)1, для того, чтобы избежать одновременного появления сигналов суммирования cT(t) и вычитания C,(t) , в устройство введе блок 14 ключей, управляемый сигналом элемента ИЛИ 15, который появляется в томслучае, когдаN1 (t)N2(t) N3(t)/ 0.

Рассмотрим случай, когда входной сигнал Y(t) соответствует положительному входному аналоговому сигналу. В случае, если сумма чисел A(t) и B(t) не превышает 15 (в двоичном коде 1111), что соответствует случаю 1 в табл.4 и первой строке в табл.1, результат суммирования C(t) в неизменном виде подается как на входы дискретизатора 11, так и на вход блока 2 задержки. Знак у С с) сигнала при этом будет положительным, а на выходах счетчика 9 нули. Запись сигналов ex (t), (t) и S(t) в табл.1. означает, что остальные значения сигналов в строке не изменяются, если, например, вместо комбинации значений сигналов o((t)1,

10

15

20

330068

j. (t) 1 , S( t) 1 яти сиги п 1 о /т равны нулю (1-7 и т 1)

Как только сумма чисел A(t) и B(t) превышает 15, в пятом разряде сумматора 4 появляется единица (Dl(t)l), что увеличивает состояние счетчика 9 на единицу (строка 3 в табл.1).Если при этом сигнал находится в первой части первого сегмента (R(t)000), то C(t) в неизменном виде транслируется через блок 16 (строка .1). Случай перехода сигнала из первого сегмента во второй описывается примером. Если сигнал B(t) имеет вид 1111, R(t) имеет вид 001, а сигналы A(t)- 1000 и c/(t) 0, то в результате суммирования получается сигнал C(t) в виде 0111 и Dl(t)1. Это увеличивает состояние счетчика 9 на единицу. Однако, так как в результате сложения изменяется номер сегмента, и зная,что в следующем сегменте шаг квантования должен быть в два раза больше, то 25 число, образуемое сигналами Q0(t), C3(t), C2(t), C1(t), C0(t) в данЯом случае следует делить на два, что осуществляется блоком 16.

В отличие от прототипа, в данном преобразователе возможны переходы не только в сегмент с большим номером (положительный и отрицательный), но и переходы, описанные в строках 3-5 (табл.4), чему соответствуют строки 5-7 (табл.1). Рассмотрим случай перехода сигнала от первого к третьему сегменту, описанному в 5 строке (табл.1). Например, если сигнал B(t) соответствует числу 1111, R(rJ имеет вид 001, а сигналы АС г) - 100110 и 0(4 г) 0, то в результате суммирования получается сигнал в виде 0101, a D1 (t) 1 и П2( .

Таким образом, сигнал П(О имеет

30

35

40

вид 011 и согласно табл.2 истинности дешифратора 6 на его выходах будет сигнал J4t) в виде 10, что увеличивает на два номер сегмента, записанный в счетчике 9. Зная, что шаг квантования в третьем сегменте в четыре раза больше, чем в первом, число, образуемое сигналами Q1(t), QO(L), C3(t), C2(t), C1(t), C0(t), делится на четыре блоком 16, в результате чего получается сигнал W(r) в виде 0001. При этом номер сегмента R(O 011. Указанная операция эквипапентна суммированию чисел C(t) 31 и E((t) 38 в линейном коде.

Случаи, когда при положительном входном сигнале на входе сумматора 4 подается отрицательный шаг квантования или наоборот, а знак сигнала после вычитания не меняется (сигнал не проходил через нуль), приведены в строках 8-1J (табл. 1). Например, если сигнал C(t) имеет вид 0011, R(t) 010, a A(t) 0 0100 (переход от второго сегмента в первьм - строка 10, табл. 1), то появляется сигнал y(t) 1, означающий переход сигнала на один сегмент ниже. В результате этого дешифратор 5 выдает сигнал N1(t) 1, что вызывает переход на дополнительный код и умножение на два значения сигнала C(t), Причем сигнал G(t) в виде О 1 означает вычитание единицы из числа, записанного в счетчике 9. Проделанные операции означают переход на один сегмент ниже и определение значения сигнала в этом сегменте с учетом того, что шаг квантования в нижнем сегменте в два раза меньше, чем в предыдущем сегменте.

Строки 11-13 (табл. 1) означают противоположные переходы случаям, описанным в строках 3-5 (табл. 4), Например, случай перехода от числа 70 к 48 в линейном коде (переход от третьего сегмента в первый), соответствует строке 11 в табл. 1. В таком случае сигнал B(t) соответствует числу 0001, R(t) имеет вид 011, а сигналы E(t) 0110000, A(t) 1100, o((t) 1, и в результате суммирования появляются сигналы y(t) и C3(t) 1, которые поступают на входы сумматора 4 и наличие которых означает переход на два сегмента ниже. В результате этого дешифратор 5 выдает сигнал N2(t) 1, что вызывает переход на дополнительный код и умножение на четыре значения сигнала C(t), а сигнал G(t) в виде 10 уменьшает состояние счетчика 9 от трех к одному.

В результате проводятся операции, означающие переход на два сегмента ниже, и учитывается обстоятельство, что шаг квантования в (1-2)-м сег- (менте в четыре раза меньше, чем в i-м сегменте. Следует отметить, что при наличии сигнала N(t) блоь 14 ключей не пропускает сигналы D(t) для предотвращения одновременного попадания сигналов J4t) и G(t) на входы счетчика 9. Такое может случиться только тогда, когда имеет место пе

5

0

5

0

5

0

5

реход от четвертого сегмента в п (строка 13, табл. 1), когда появл ег ся сигнал D1(t) 1.

Строки 6-11 (табл. 4)описывают случаи перехода через нуль входного аналогового сигнала и они соответствуют строкам 14-19 (табл. 1) истинности дешифратора 5. Существенным признаком данных случаев является наличие сигнала H(t) 1,означающего, что сигнал приращения A(t) больше числа, образуемого сигналами Q(t). Так как сигнал Q(t) содержит только информацию о старшем разряде цифрового эквивалента входного сигнала (табл. 3), то для того, чтобы определить, больше ли цифра, отображенная сигналом A(t), чем цифра, отображенная сигналом Q(t) вне сегмента (так как имеет место переход через границы сегмента), достаточно сравнить элементом 13 сравнения три старших разряда сигналов A4(t)-A6(t) и Q4(t)-Q6(t). Это позволяет отличить случаи, описанные в строках 9-13 в табл. 1 (вычитание при положительном сигнале и суммирование при отрицательном сигнале без перехода через нуль) от случаев перехода через нупь, описанных в строках 14-19 (табл. 1)5 и дает возможность учесть комбинации номеров сегментов, между которыми меняется значение сигнала, с тем, чтобы правильно определить сигналы изменения знака Z1(t) (от положительного сигнала к отрицательному) и Z2(t) (обратно), а также сигналы M(t) и N(t), управляющие операциями деления и перемножения сигналов блоком 16. Соответствующие сигналы Z1(t) и Z2(t) изменяют состояние триггера 10, выходной сигнал которого поступает на блок 2 задержки и дискретизатор 11.

Генератор 12 импульсов вырабатывь- ет тактовые импульсы с частотой дискретизации ИКМ. В результате дискре- тизатором 11 считываются сигналы R(t), указывающие на номер сегмента, сигналы W(t), описывающие уровень сигнала внутри сегмента,, и сигнал S(t), указывающий знак ИКМ сигнала, что формирует выходной сигнал I(t).

Таким образом, расширен динамический диапазон передаваемых сигналов при обеспечении заданного отношения сигнал-шум восстановленного сигнала.

Формула изобретения

1. Преобразователь дельта-модули- рованного сигнала в импульсно-кодово модулированный сигнал, содержащий первый анализатор, вход которого объединен с информационным входом первого блока задержки и является информационным входом преобразователя, выходы первого анализатора сигнала соединены с информационными входами управляемого делителя, выходы которого подключены к первым информационным входам сумматора, выход первого блока задержки соединен с первым управляющим входом сумматора и первым входом первого дешифратора, первый, вторые, третьи, четвертый, пятый и шестые выходы которого подключены соответственно к первому, вторым и третьим управляющим входам блока преобразования кодов, первому и второму установочным ьходам триггера и первым управляющим входам счетчика импульсов, выходы которого соединены с входами второго анализатора сигнала и первыми входами дискретизатора, генератор импульсов, выход которого подключен к второму входу дискрети- затора, первые выходы сумматора соединены с первыми информационными входами блока преобразования кодов, выходы которого подключены к третьим входам дискретизатора и первым информационным входам второго блока задержки, тактовый вход которого объединен с тактовыми входами первого блока задержки, первого анализатора сигнала, счетчика импульсов и триггера и является входом синхронизации преобразователя, первые выходы второго анализатора сигнала соединены с управляющими входами управляемого делителя, первый выход второго блока задержки подключен к второму входу первого дешифратора и второму управляющему входу сумматора, вторые выходы второго блока задержки соединены с вторыми информационными входами сумматора, второй и третьи выходы которого подключены соответственно к третьему и четвертым входам первого дешифратора, выход триггера подключен к второму информационному входу второго блока задержки и четвертому входу дискретизатора, выходы которого являются выходами преобразователя, отличающийся тем, что, с целью повышения точности

5

преобразования за счет расширения динамического диапазона преобразуемых сигналов, в преобразователь введены второй дешифратор, элемент ИЛИ,

блок ключей и элемент сравнения, первые входы которого подключены к выходам управляемого делителя, пятые входы первого дешифратора подключены к выходам счетчика импульсов, информационные входы блока ключей и входы элемента ИЛИ подключены к третьим выходам соответственно сумматора и первого дешифратора, выход элемента ИЛИ соединен с управляющим входом блока ключей, выходы которого подключены к входам второго дешифратора, выходы которого соединены с вторыми управляющими входами счетчика импульсов, вторые выходы второго анализатора сигнала подключены к вторым информационным входам-блока преобразования кодов и вторым входам элемента сравнения, выход которого соединен с

5 шестым входом первого дешифратора, седьмой вход которого подключен к старшему разряду первых выходов сумматора .

2. Преобразователь по п. 1, отличающийся тем, что блок преобразования кодов содержит преобразователь прямого кода в дополнительный, первую - n-ю группы (п - разрядность первых информационных входов блока) по п элементов И и

5 (п+1)-ю - (2 п-1)-ю группы соответственно по (п-1)-1 элементов И, первые входы (i-j+1)x элементов И (i 1,n, j 1,n) j-x групп объединены с i-м входом преобразователя

0 прямого кода в дополнительный и являются (1-1)-м разрядом первых информационных входов блока, первые входы (i-j+n+1)-x элементов И j-x групп объединены и являются (1-1)-м разря5 дом вторых информационных входов

блока, вторые входы первых элементов И первой - п-и групп объединены и являются первым управляющим входом блока, вторые входы k-x элементов И

0 (k 2, п) первой - n-й групп соответственно объединены и являются первым - (п-1)-м разрядами вторых управляющих входов блока, первые входы всех элементов И 1-й группы (1

5 я п+1, 2 п-1) объединены и являются (1-п)-м разрядом третьих управляющих входов блока, m-й выход преобразователя прямого кода в дополнительный (т 1 , п-1) соединен ,- вторыми вхо0

13

14

1533006

дамн m-x элементов И (п+1)-й-с выходами (j+n-l)-x элементов И

(2 п-1)-й групп, выходы всех элемен-(1 п+1, 2 п-1) 1-х групп и являются

тов И j-й группы (,n) объединены(j-l)-M разрядом выходов блока.

Т«вяии«

14

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь дельта-модулированного сигнала в импульсно-кодово-модулированный сигнал | 1986 |

|

SU1347190A1 |

| Адаптивный импульсно-кодовый модулятор | 1985 |

|

SU1300638A1 |

| Кодирующее устройство с дельта-модуляцией и импульсно-кодовой модуляцией | 1984 |

|

SU1182681A2 |

| Кодирующее устройство с дельтамодуляцией и импульсно-кодовой модуляцией | 1977 |

|

SU661789A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодомодулированный сигнал | 1985 |

|

SU1282336A1 |

| Адаптивный импульсно-кодовый модулятор | 1982 |

|

SU1127086A2 |

| Устройство для измерения характеристики квантования передатчика сигналов с импульсно-кодовой модуляцией | 1980 |

|

SU946005A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Преобразователь дельта-модулированного сигнала в сигнал с импульсно-кодовой модуляцией | 1984 |

|

SU1216831A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи сигналов для стыковки каналов ДИ и ИКМ позволяет повысить точность преобразования за счет расширения динамического диапазона преобразуемых сигналов. Преобразователь содержит блоки 1, 2 задержки, управляемый делитель 3, сумматор 4, дешифратор 5, анализаторы 7, 8 сигнала, счетчик 9 импульсов, триггер 10, дискретизатор 11, генератор 12 импульсов и блок 16 преобразования кодов. Благодаря введению дешифратора 6, элемента 13 сравнения, блока 14 ключей и элемента ИЛИ 15 выбор нужного сегмента характеристики компрессии осуществляется точнее и быстрее. 1 з.п.ф-лы, 3 ил., 4 табл.

Таблица 4

1533006

928

Wt) Qify doty од aOTcw cofr)

Фиг.г

| Преобразователь компандированногодЕльТА-пОТОКА B иКМ СигНАл | 1979 |

|

SU822354A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодово-модулированный сигнал | 1986 |

|

SU1347190A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-30—Публикация

1988-05-12—Подача