1

Изобретение относится к автоматиke и вычислительной технике и может найти применение для выполнения множительно-делительных операций над вели чинами, представленными в цифровом и аналоговом виде с получение результата в цифровой или цифроаналоговой форме с плавающей запятой.

Известно множительно-делительное устройство, содержащее генератор тактовых импульсов, коммутаторы, генератор синхроимпульсов, элементы памяти, компаратор, цифроаналоговый преобразователь, распределитель импульсов, группу элементов И и регистр 1Устройство-обладает высоким быстродействием, однако имеет пониженную точность выполнения множительноделительных операций.

Известно также множительно-делительное устройство, содержащее блок управления, коммутаторы, кодоуправляемый делитель напряжения, ключи.

операционный усилитель, компаратор, блок пребразования в код и аналоговый запоминающий блок Г 2 J.

Устройство обладает широкими функциональными возможностями, однако также имеет пониженную точность выполнения множительно-делительных операций .

Наиболее близким к предлагаемому является множительно-делительное

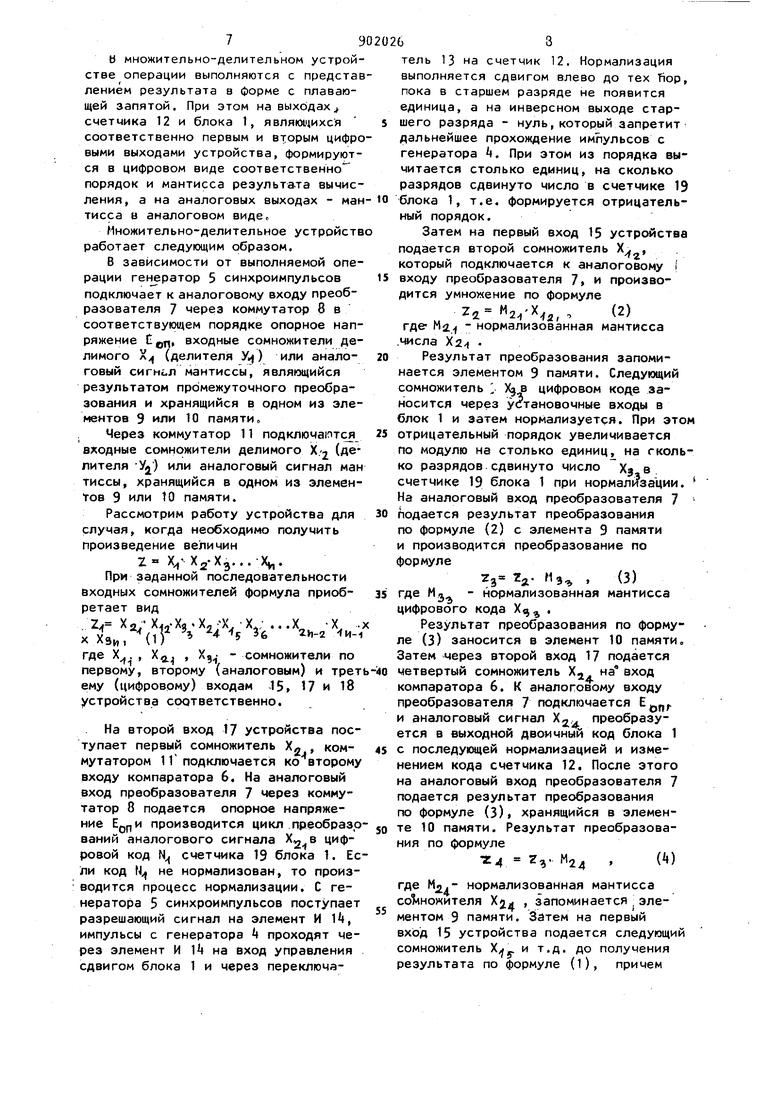

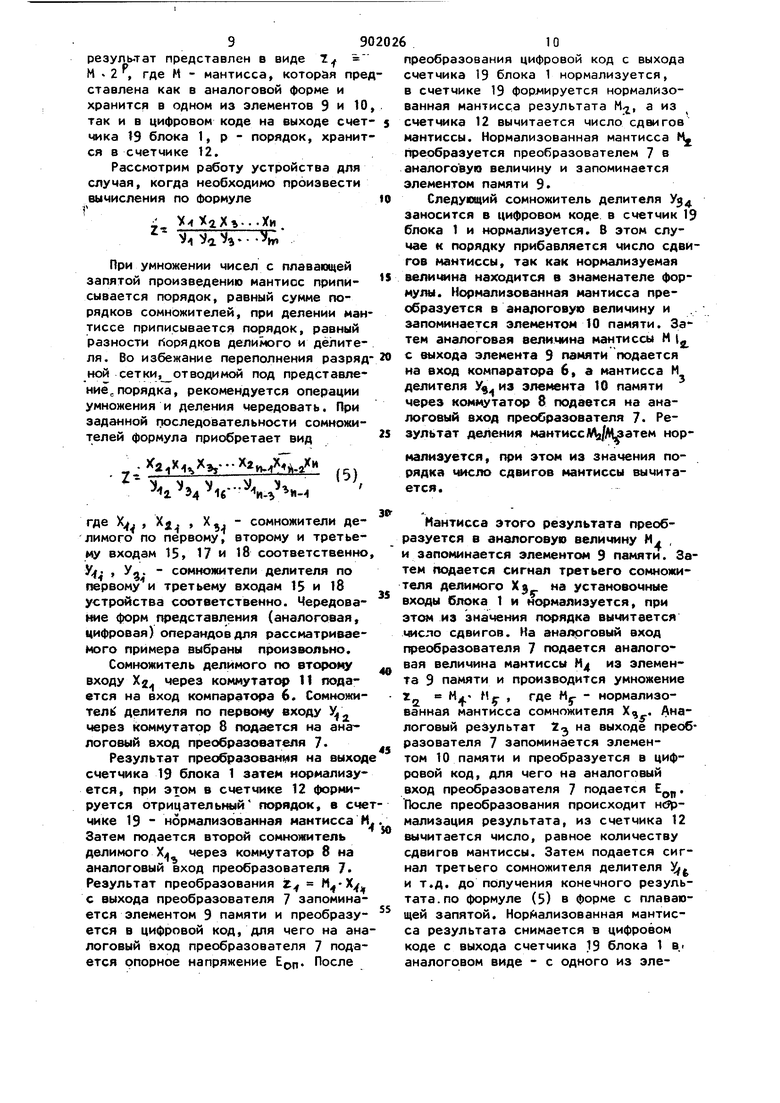

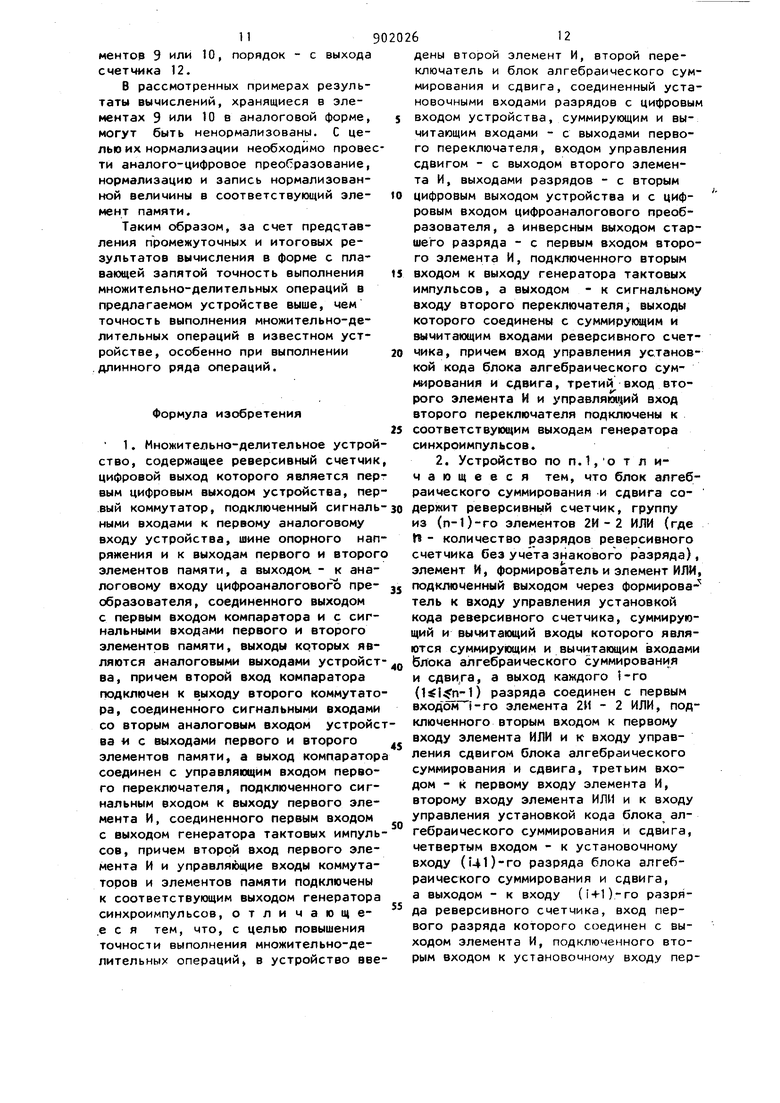

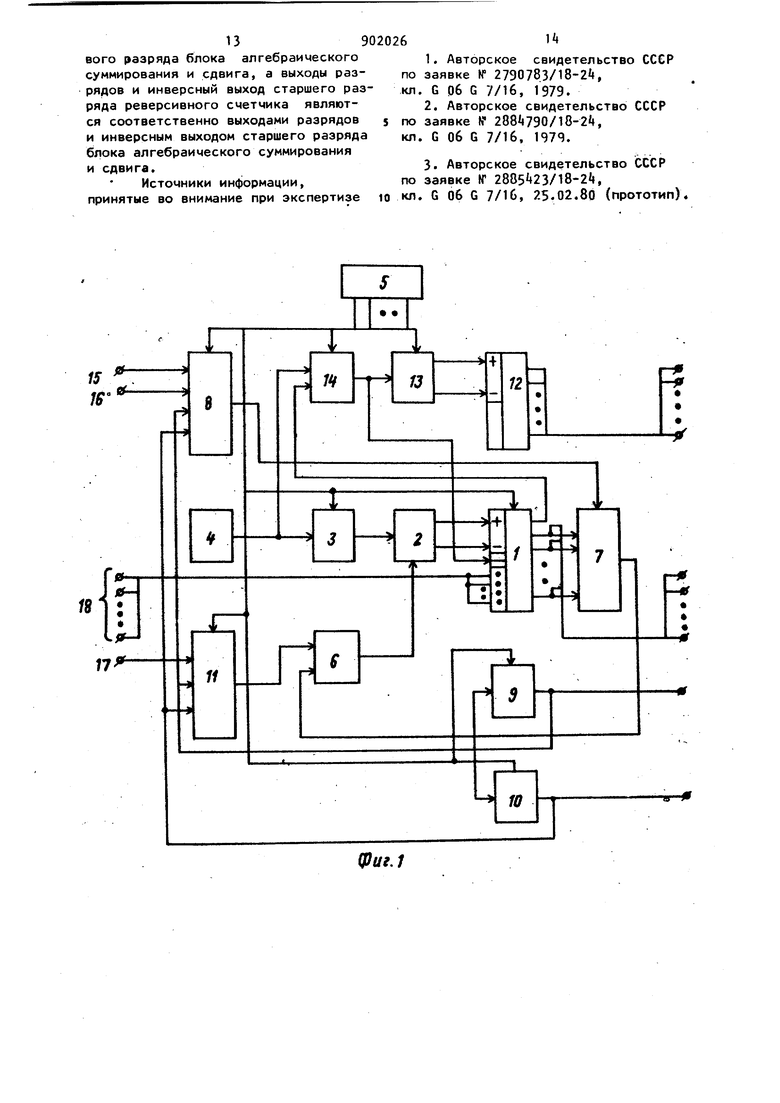

10 устройство, содержащее реверсивный счетчик, цифровой выход которого является первым цифровым выходом устройства, первый коммутатор, подключенный сигнальными входами к перво15му аналоговому входу устройства, шине опорного напряжения и к выходам первого и второго элементов памяти,а выходом - к аналоговому входу цифроаналргового преобразователя, сое20диненного выходом с первым входом компаратора и с сигнальными входами первого и второго элементов памяти выходы которых являются аналоговыми 390 выходами устройства,, причем второй вход компаратора подключен к выходу второго коммутатора, соединенного сигнальными входами со вторым аналоговым входом устройства и с выходами первого и второго элементов памяти, а выход компаратора соединен с управляющим входом первого переключателя, подключенного сигнальным входом к выходу первого элемента И, соединенного первым входом с выходом гёнератора тактовых импульсов, причем второй вход первого элемента И и управляющие входы коммутато1 08 и элементов памяти подключены к соответствующим выходам генератора синхроимпульсов, а реверсивный счётчик соединен суммирующим и вычитающим входами с выходами первого переключателя, установочными входами -, с цифровым входбм устройства, а выходом - с цифровым входом цифроаналогового преобразователя 3 j. Недостатком известного устройства является пониженная точность выполнения множительно-делительных операций. Так, при выполнении ряда операций деления на аналого-цифровом преоб разоаателе результат на выходе счетчика постоянно уменьшается, что при определенном количестве операций приводит к перемещению младших разря дов за пределы разрядной сетки и их потере. При умножении на цифроаналоговом преобразователе его выходное напряжение всегда меньше опорного напряжения и при выполнении длинного ряда операций выходной сигнал уменьшается, а при некотором количестве сомножителей становится соизмеримым с дрейфом нуля аналоговых элементов, что снижает трчность вычисления. Цель изобретения - повышение точ- ности выполнения множительно-делительных операций. Поставленная цель достигается тем что в м(;1ожительно-делительное устрой ство, содержащее реверсивный счетчик цифровой выход которого является пер вым цифровым выходом устройства, пер вый коммутатор, подключенный сигналь ными входами к первому аналоговому входу устройства, шине опорного напряжения и к выходам первого и второг элементов памяти, а выходом - к ана логовому входу цифроаналогового преобразователя, соединенного выходом, с первым входом компаратора и с сиг6нальными входами первого и второго элементов памяти, выходы которых являются аналоговыми выходами устройства, причем второй вход компаратора подключен к выходу второго коммутатора, соединенного сигнальными входами со вторым аналоговым входом устройства и с выходами первого и второго элементов памяти, а выход компаратора соединен с управляющим входом первого переключателя, подключенного сигнальным входом к выходу первого элемента И, соединенного первым входом с выходом генератора тактовых импульсов, причем второй вход первого элемента И и управляющие входы коммутаторов и элементов памяти подключены к соответствующим выходам генератора -синхроимпульсов, введены второй элемент И, второй переключатель и блок алгебраического суммирования и сдвига, сое- диненный установочными входами разрядов с цифровым входом устройства, суммирующим и вычитающим входами - с выходами первого переключателя, входом управления сдвигом - с выходом второго элемента И, выходами разрядов - с вторым цифровым выходом устройства и с цифровым входом цифроаналогового преобразователя, а инверсным выходом старшего разряда - с первым входом второго элемента И, подключенного вторым входом к выходу генератора тактовых импульсов, а выходом - к сигнальному входу второго переключателя, выходы которого соединены с суммирующим ч вычитающим входами реверсивного счетчика, причем вход управления установкой кода блока алгебраического суммирования и сдвига, третий вход вт(фого элемента И и управляющий вход второго переключателя подключены к соответствующим выходам генератора синхроимпульсов. Кроме того, блок алгебраического суммирования и сдвига содержит реверсивный счетчик, группу из (n-l)-ro элементов 2И-2ИЛИ (где п - количество разрядов реверсивного счетчика без учета знакового разряда), элемент И, формирователь и элемент ИЛИ, подключенный выходом через формирователь к входу управления установкой коДа реверсивного счетчика, суммирующий и вычитающий входы которого являются суммирующим и вычитающим входами блока алгебраического суммирования и сдвига, а выход каждого i-ro ( 1) разряда соединен с первым входом i-ro элемента 2И-2ИЛИ, подключенного вторым входом к первому входу элемента ИЛИ и к входу упра ления сдвигом блока алгебраического суммирования.и сдвига, третьим входом - к первому входу элемента И, второму входу элемента ИЛИ и к входу управления установкой кода блока алгебраического суммирования и сдвига четвертым, входом - к установочному входу (ч-1)-го разряда блока алгебраического суммирования и сдвига, а выходом-к входу (i-t-O-ro разряда реверсивного счетчика, вход первого разряда которого соединен с выходом элемента И, подключенного вторым входом к установочному входу первого разряда блока алгебраического суммирования и сдвига, а выходы разрядов и инверсный выход старшего разряда |эеверсивного счетчика являются соответственно выходами разрядов и инверсным выходом старшего разряда бло ка алгебраического суммирования и сдвига. На фиг. 1 изображена блок-схема множительно-делительного устройства; на фиг. 2 - функциональная схема бло ка алгебраического суммирования и сдвига. Множительно-делительное устройств содержит блок 1 алгебраического сумм рования и сдвига, первый переключатель 2, первый элемент И 3, генератор тактовых импульсов, генератор синхроимпульсов, компаратор 6, цифро аналоговый преобразователь 7, первый коммутатор 8, первый и второй элемен ты 9 и 10 памяти, второй коммутатор 11, реверсивный 12, второй переключатель 13 и второй элемент И 14. Коммутатор 8 подключен сигнальными входами к первому аналоговому входу 15 устройства, шине 16 опорного напряжения и к выходам эле гентбв 9 и 10 памяти, а выходом - к аналоговому входу цифроаналогового преобразователя 7. Выход преобразо-вателя 7 соединен с первым входом компаратора- бис сигнальными входами элементов 9 и 10 памяти, выходы которых являются аналоговыми выходами устройства. Второй вход компаратора 6 подключен к выходу коммутатора 11, соединенного сигнальными входами со вторым аналоговым входом 17 устройства и с выходами элементов 3 И 10 памяти. Выход компаратора 6 соединен с управляющим входом переключателя 2, сигнальным вход Kotopoго подключен к выходу элемента И 3. соединенного первым входом с выходом генератора тактовых импульсов. Блок 1 алгебраического суммирования и сдвига соединен установочными входами разрядов с цифровым входом 18 устройства, суммирующим и вычитающим входами - с выходами переключателя 2, входом управления сдвигом с выходом элемента И 1, выходами разрядов - с цифровым входом преобразователя 7, а инверсным выходом старшего разряда - с первым входом элемента И-14, подключенного вторым входом к выходу генератора k, а выходом - к сигнальному входу переключателя 13. Выходы переключателя 13 соединены с суммирующим и вычитающим входами реверсивного счетчика 12. Второй вход элемента И 3, третий вход элемента И 14, вход управления установкой кода блока 1 и управляющие входы переключателя 13, коммутаторов 8 и 11 и элементов 9 и 10 памяти подключены к соответствующим выходам генератора 5 синхроимпульсов. Блок 1 алгебраического суммирования и сдвига может быть выполнен, например, содержащим (фиг. 2) реверсивный счетчик 19, группу из {п-1)-го элементов 2И - 2 ИЛИ 20 (где п - количество разрядов счетчика 19), элемент И 21, формирователь 22 и элемент ИЛИ 23, подключенный выходом через формирователь 22 к входу управления установкой кода счетчика 19. Суммирующий и вычитающий входы счетчика 19 являются суммирующим и вычитающим входами блока 1, а выход каждого 1-го (к )разряда соединен с первым входом i-ro элемента 2И 2 ИЛИ 20, подключенного вторым входом к первому входу элемента ИЛИ 23 и к входу управления сдвигом блока 1, третьим входбм - к первому входу элемента И 21, второму входу элемента ИЛИ 23 и к входу управления установкой кода блока 1, четвертым входом - к установочному входу (14-1)-го разряда блока 1, а выходом - к входу ()-ro разряда счетчика 19, вход первого разряда которого соединен с выходом элемента И 21, подключенного вторым входом к установочному входу/ первого (младшего) разряда блока 1.

В множительно-делительном устройстве операции выполняются с представлением результата в форме с плавающей запятой. При этом на выхбдах счетчика 12 и блока 1, являю1цихся соответственно первым и вторым цифровыми выходами устройства, формируются в цифровом виде соответственно порядок и мантисса результата вычисления, а на аналоговых выходах - ман тисса в аналоговом виде. Множительно-делительное устройств работает следующим образом. В зависимости от выполняемой операции генератор 5 синхроимпульсов подключает к аналоговому входу преобразователя 7 через коммутатор 8 в соответствующем порядке опорное напряжение Cj,n, входные сомножители делимого л (делителя У,.|) или аналоговый сигнь-л мантиссы, являющийся результатом промежуточного преобразования и хранящийся в одном из элементов 9 или 10 памяти о Через коммутатор 11 подключаются входные сомножители делимого Х.2 (делителя У) или аналоговый сигнал ман тиссы, хранящийся в одном из элеменtoB 9 или 10 памяти. Рассмотрим работу устройства для случая, когда необходимо получить произведение величин Z- Хд-Х.-.ЛПри заданной последовательности входных сомножителей формула приобретает вид Zx Xrt, ХчуХа « Хл Х. .. .X Х ххзи, (И 5 ги-2 -ги- сомножители по первому, второму (аналоговым) и трет ему (цифровому) входам 15, 17 и 18 устройства соответственно. На второй вход 17 устройства поступает первый сомножитель Xg , коммутатором 1 Г подключается ковторому входу компаратора 6. На аналоговый вход преобразователя 7 через коммутатор 8 подается опорное напряжение ЕррИ производится цикл преобразр ваний аналогового сигнала в цифровой код N счетчика 19 блока 1. Ес ли код N не нормализован, то производится процесс нормализации. С генератора 5 синхроимпульсов поступает разрешающий сигнал на элемент И 14, импульсы с генератора Ц проходят через элемент И И на вход управления сдвигом блока 1 и через переключатель 13 на счетчик 12. Нормализация выполняется сдвигом влево до тех fiop, пока в старшем разряде не появится единица, а на инверсном выходе старшего разряда - нуль, который запретит дальнейшее прохождение импульсов с генератора Ц. При этом из порядка вычитается столько единиц, на сколько разрядов сдвинуто число в счетчике 19 блока 1, т.е. формируется отрицательный порядок. Затем на первый вход 15 устройства подается второй сомножитель X, который подключается к аналоговому | входу преобразователя 7 и производится умножение по формуле 2 , (2) где Мд. - нормализованная мантисса .числа Xsxf Результат преобразования запоминается элементом 9 памяти. Следующий сомножитель 1 ) в цифровом коде заносится через установочные входы в блок 1 и затем нормализуется. При этом отрицательный порядок увеличивается по модулю на столько единиц, на гколько разрядов сдвинуто число Ха в счетчике 19 блока 1 при нормализации. На аналоговый вход преобразователя 7 Подается результат преобразования по формуле (2) с элемента 9 памяти и производится преобразование по формуле 2з а,- з,, . (3) где М - йормализованная мантисса цифрового кода Х . Результат преобразования по формуле (З) заносится в элемент 10 памяти. Затем через второй вход 17 подается четвертый сомножитель Х на вход компаратора 6. К аналоговому входу преобразователя 7 подключается Е и аналоговый сигнал Х,. преобразуется в выходной двоичный код блока 1 с последующей нормализацией и изменением кода сметчика 12. После этого на аналоговый вход преобразователя 7 подается результат преобразования по формуле (3) хранящийся в элементе 10 памяти. Результат преобразования по формуле TS4 г. MI где Мд,- нормализованная мантисса соТ ножителя Хо., , запоминается элементом 9 памяти. Затем на первый вход 15 устройства подается следующий сомножитель Х и т.д. до получения результата по формуле (1), причем резулытат представлен в виде 1 М . 2 , где И - мантисса, которая пре ставлена как в аналоговой форме и хранится в одном из элементов 9 и 10 так и в цифровом коде на выходе счет чика 19 блока 1, р - порядок, хранит ся в счетчике 12. Рассмотрим работу устройства для случая, когда необходимо произвести вычисления по формуле У йХг-. -Уи Vi VaV -irr, При умножении чисел с плавающей запятой произведению мантисс приписывается порядок, равный сумме порядков сомножителей, при делении ман тиссе приписывается порядок, равный разности |1орядков делимого и делителя. Во избежание переполнения разряд ной сетки,отводимой под представление порядка, рекомендуется операции умножения и деления чередовать. При заданной последовательности сомножителей формула приобретает вид ,---Х2 У./и где Х. , Хд|, , Х - сомножители делимого по первому, второму и третьему входам 15, 17 и 18 соответственно -l сомножители делителя по первому и третьему входам 15 и 18 устройства соответственно. Чередование форм представления (аналоговая, цифровая) операндов для рассматриваемого примера выбраны произвольно. Сомножитель делимого по sropoiiiy входу Xg. через коммутатор 11 подается на вход компаратора 6. Сомножител| делителя по перво14у входу У через коммутатор 8 подается на аналоговый вход преобразователя 7« Результат преобразования на выход счетчика 19 блока 1 затем нормализуется, при этом в счетчике 12 формируется отрицательный порядок, в сче чике 13 нормализованная мантисса Н Затем подается второй сомножитель делимого Xjj через коммутатор 8 на аналоговый вход преобразователя 7 Результат преобразования г , с выхода преобразователя 7 запоминается элементом 9 памяти и преобразуется в цифровой код, для чего на ана логовый вход преобразователя 7 подается опорное напряжение После преобразования цифровой код с выхода счетчика 19 блока 1 нормализуется, в счетчике 19 формируется нормализованная мантисса результата M-j, а из счетчика 12 вычитается число сдвигов мантиссы. Нормализованная мантисса М преобразуется преобразователем 7 в аналоговую величину и запоминается элементом памяти 9 Следующий сомножитель делителя У заносится в цифровом коде в счетчик 19 блока 1 и нормализуется. В этом случае к порядку прибавляется число сдвигов мантиссы, так как нормализуемая велиьмна находится в знаменателе формулы. Нормализованная мантисса преобразуется в аналоговую величину и запоминается элементом 10 памяти. Затем аналоговая величина мантиссы М 1 с выхода элемента 9 памяти подается на вход компаратора 6, а мантисса М делителя элемента 10 памяти через коммутатор 8 подается на аналоговый вход преобразователя 7. Результат деления мантиссАА}/Д атем нормализуется, при этом из значения порядка число сдвигов мантиссы вычитается. Мантисса этого результата преобразуется в аналоговую величину Н , и запоминается элементом 9 памяти. Затем гкэдается сигнал третьего сомножителя делимого Xj на установочные входы блока 1 и нормализуется, при из значения порядка вычитается число сдвигов. На анапрговый вход г шобразователя 7 подается аналоговая величина мантиссы Нд из элемента 9 памяти и производится умножение Z М,. М , где Hj- - нормализованная мантисса сомножителя Х . Аналоговый результат 2 на выходе преобразователя 7 запоминается элементом 10 памяти и преобразуется в цифровой код, для чего на аналоговый вход преобразователя 7 подается Е. После преобразования происходит нб мализация результата, из счетчика 12 вычитается число, равное количеству сдвигов мантиссы. Затем подается сигнал третьего сомножителя делителя У и т.д. до получения конечного результата, по формуле (З) в форме с плавающей запятой. Нормализованная мантисса результата снимается в цифровом коде с выхода счетчика 19 блока 1 в. аналоговом виде - с одного из элементор 9 или 10, порядок - с выхода счетмика 12. В рассмотренных примерах результаты вычислений, хранящиеся в элементах 9 или 10 в аналоговой форме, могут быть ненормализованы. С целью их нормализации необходимо провес ти аналого-цифровое преобразование, нормализацию и запись нормализованной величины в соответствующий элемент памяти. Таким образом, за счет представления промежуточных и итоговых результатов вычисления в форме с плавающей запятой точность выполнения множительно-делительных операций в предлагаемом устройстве выше, чем точность выполнения множительно-делительных операций в известном устройстве, особенно при выполнении .длинного ряда операций. Формула изобретения 1. Множительно-делительное устрой ство, содержащее реверсивный счетчик цифровой выход которого является пер вым цифровым выходом устройства, пер вый коммутатор, подключенный сигналь ными входами к первому аналоговому входу устройства, шине опорного нап ряжения и к выходам первого и второг элементов памяти, а выходок - к аналоговому входу цифроаналогового преобразователя, соединенного выходом с первым входом компаратора и с сигнальными входами первого и второго элементов памяти, выходы которых являются аналоговыми выходами устройст ва, причем второй вход компаратора подключен к выходу второго коммутато ра, соединенного сигнальными входами со вторым аналоговым входом устройс ва и с выходами первого и второго элементов памяти, а выход компаратор соединен с управляющим входом первого переключателя, подключенного сигнальным входом к выходу первого элемента И, соединенного первым входом с выходом генератора тактовых импуль сое, причем второй вход первого элемента И и управляющие входы коммутаторов и элементов памяти подключены к соответствующим выходом генератора синхроимпульсов, отличающееся тем, что, с целью повышения точности выполнения множительно-делительных операций, в устройство вве даны второй элемент И, второй переключатель и блок алгебраического суммирования и сдвига, соединенный установочными входами разрядов с цифровым входом устройства, суммирующим и вычитающим входами - с выходами первого переключателя, входом управления сдвигом - с выходом второго элемента И, выходами разрядов - с вторым цифровым выходом устройства и с цифровым входом цифроаналогового преобразователя , а инверсным выходом старшего разряда - с первым входом второго элемента И, подключенного вторым входом к выходу генератора тактовых импульсов, а выходом - к сигнальному входу второго переключателя, выходы которого соединены с суммирующим и вычитающим входами реверсивного счетчика, причем вход управления установкой кода блока алгебраического суммирования и сдвига, третий вход второго элемента И и управлявший вход второго переключателя подключены к соответствующим выходам генератора синхроимпульсов. 2. Устройство по п.1,о т л ичающееся тем, что блок алгебраического суммирования и сдвига содержит реверсивный счетчик, группу из (п-1)-го элементов 2И - 2 ИЛИ (где количество разрядов реверсивного счетчика без учета знакового разряда), элемент И, формирователь и элемент ИЛИ, подключенный выходом через формирователь к входу управления установкой кода реверсивного счетчика, суммирующий и вычитающий входы которого являются суммирующим и вычитающим входами ёлока алгебраического суммирования и сдвига, а выход каждого I-го () разряда соединен с первым вхоДом i-ro элемента 2И - 2 ИЛИ, подключенного вторым входом к первому входу элемента ИЛИ и к входу управления сдвигом блока алгебраического суммирования и сдвига, третьим входом - к первому входу элемента И, второму входу элемента ИЛИ и к входу управления установкой кода блока алгебраического суммирования и сдвига, четвертым входом - к установочному входу (i4l)-ro разряда блока алгебраического суммирования и сдвига, а выходом - к входу (i4-1)-го разряда реверсивного счетчика, вход первого разряда которого соединен с выходом элемента И, подключенного вторым входом к установочному входу пер13902026

вого разряда блока алгебраимеского суммирования и сдвига, а выходы раз- по рядов и инверсный выход старшего раз- кл ряда реверсивного счетчика являются соответственно выходами разрядов s по и инверсным выходом старшего разряда кл блока алгебраического суммирования и сдвига.

Источники информации,по

принятые во внимание при экспертизе ю кл

1.Авторское свидетельство СССР заявке К 2790783/18-Z f,

. G Рб G 7/16, 1979.

2.Авторское свидетельство СССР заявке № 288i 790/l8-2t,

. G Об G 7/16, 197Я.

3.Авторское свидетельство СССР заявке № 2885 23/18-2,

. G Об G 7/16, 25,02.80 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1980 |

|

SU883920A2 |

| Следящий функциональный преобразователь | 1976 |

|

SU634308A1 |

| Цифровой коррелятор | 1980 |

|

SU894719A1 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

| Множительно-делительное устройство | 1976 |

|

SU674042A1 |

| Логарифмирующее устройство | 1979 |

|

SU858011A1 |

| Вычислительное устройство | 1986 |

|

SU1320819A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Множительное устройство | 1980 |

|

SU900293A1 |

| АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2121712C1 |

Фиг.1

кода г

фиг. 2

Авторы

Даты

1982-01-30—Публикация

1980-06-05—Подача