1

Изобретение относится к электротехнике и может быть использовано для сглаживания пульсаций выпрямленного напряжения в устройствах, обеспечивающих высокое быстродействие передачи сигнала обратной связи в системе автоматического регулирования.

Цель изобретения - улучшение эффективности путем повьпления точности передачи входного сигнала.

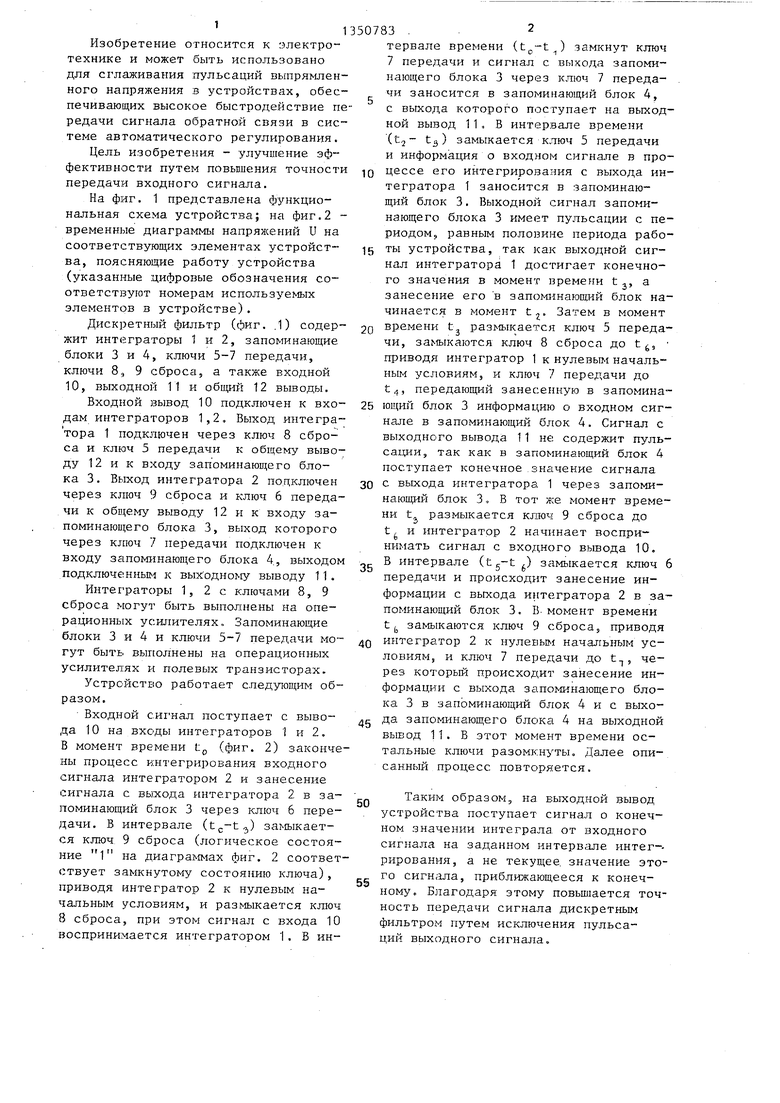

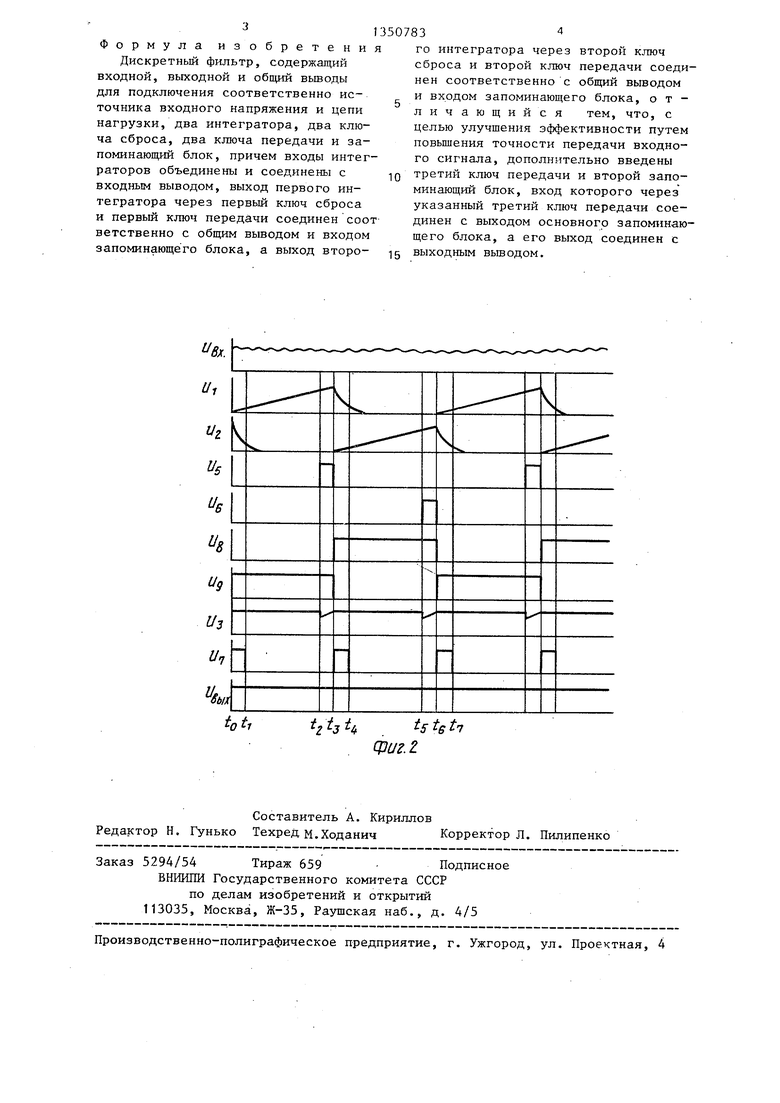

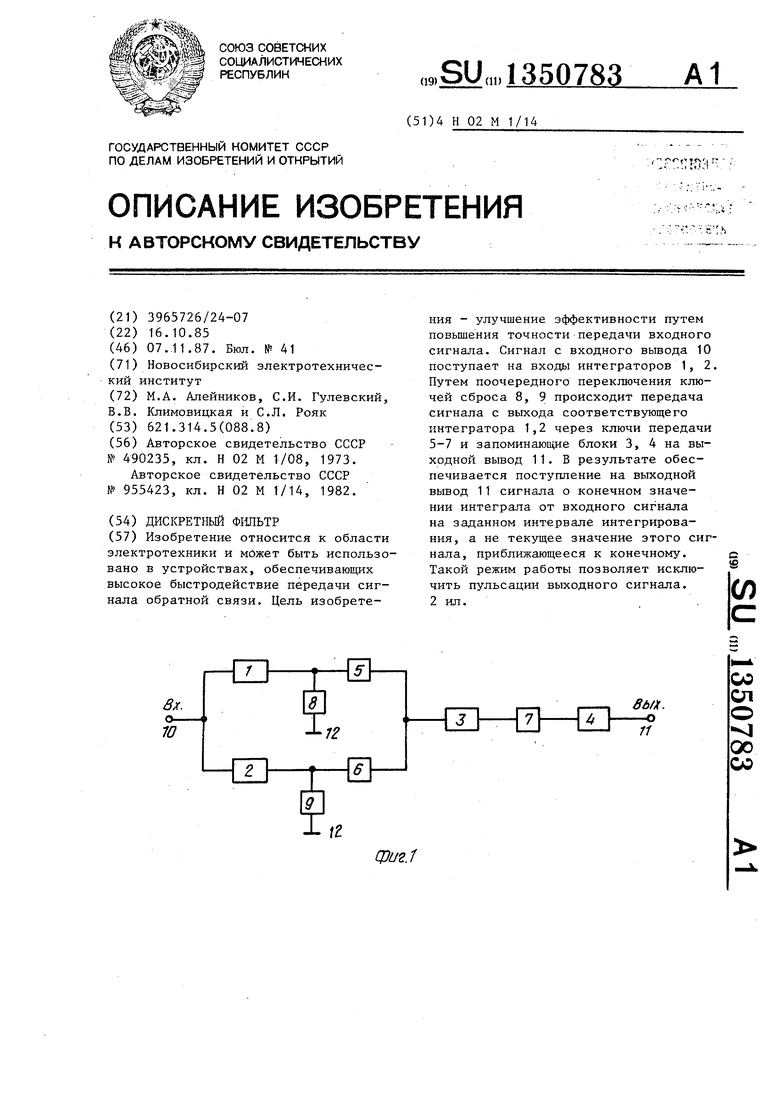

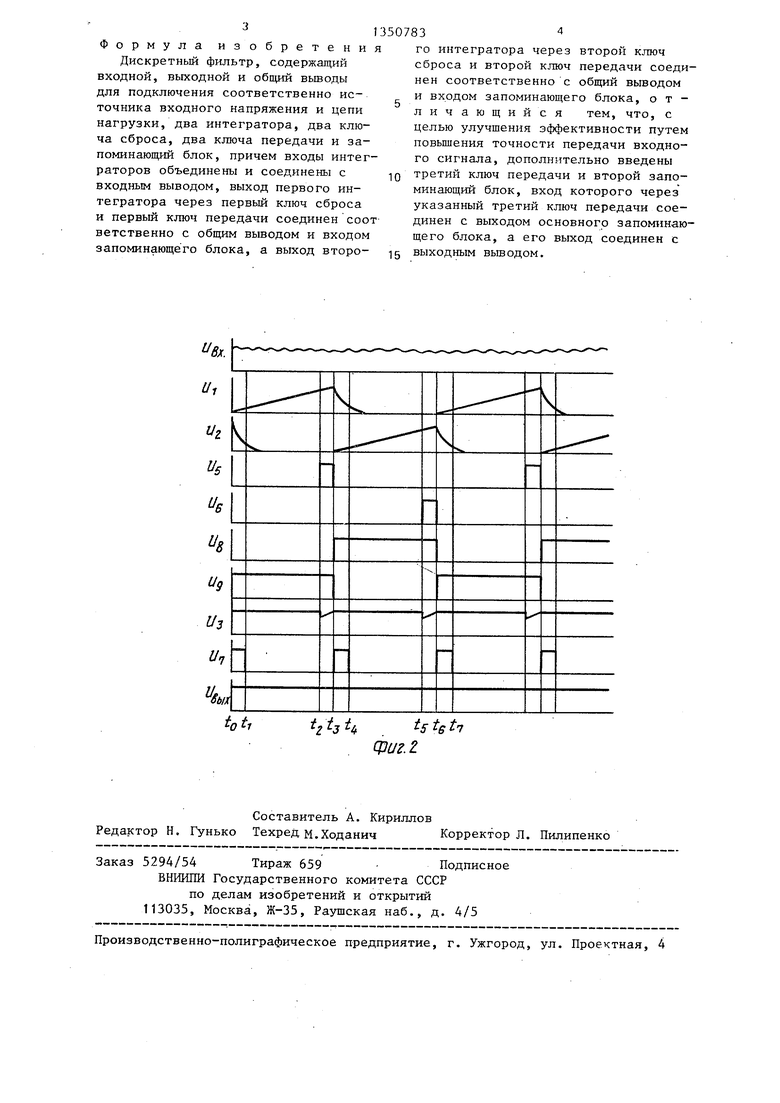

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - временные диаграммы напряжений U на соответствующих элементах устройства, поясняющие работу устройства (указанные цифровые обозначения соответствуют номерам используемых элементов в устройстве).

Дискретный фильтр (фиг. .1) содержит инт 2граторы 1 и 2, запоминающие блоки 3 и 4, ключи 5-7 передачи, ключи 8., 9 сброса, а также входной 10, выходной 11 и общий 12 выводы.

Входной вывод 10 подключен к входам интеграторов 1,2, Выход интегра- тора 1 подключен через ключ 8 сброса и ключ 5 передачи к общему выводу 12 и к входу запоминающего блока 3. Выход интегратора 2 подключен через ключ 9 сброса и ключ 6 передачи к общему выводу 12 и к входу запоминающего блока 3, выход которого через Kjno4 7 передачи подключен к входу запоминающего блока 4, выходом подключенным к выходному выводу 11.

Интеграторы 1,2с ключами 8, 9 сброса могут быть выпохснены на операционных усилителях. Запоминающие блоки 3 и 4 и ключи 5-7 передачи могут быть выполнены на операционных усилителях и полевых транзисторах.

Устройство работает следующим образом.

Входной сигнал поступает с вывода 10 на входы интеграторов 1 и 2. В момент времени t (фиг. 2) закончены процесс интегрирования входного сигнала интегратором 2 и занесение сигнала с выхода интегратора 2 в запоминающий блок 3 через ключ 6 передачи. В интервале (,,,) замыкается ключ 9 сброса (логическое состояние 1 на диаграммах фиг. 2 соответствует замкнутому состоянию ключа), приводя интегратор 2 к нулевьм начальным условиям, и размыкается ключ 8 сброса, при этом сигнал с входа 10 воспринимается интегратором 1. В ин1350783 .2

тервале времени () замкнут ключ 7 передачи и сигнал с выхода запоминающего блока 3 через ключ 7 переда- . чи заносится в запоминающий блок 4, с выхода которого поступает на выходной вывод 11, В интервале времени

( t3) замыкается ключ 5 передачи и информация о входном сигнале в про1Q цессе его интегрирования с выхода интегратора 1 заносится в запоминающий блок 3. Выходной сигнал запоминающего блока 3 имеет пульсации с периодом, равным половине периода рабо15 ты устройства, так как выходной сигнал интегратора 1 достигает конечного значения в момент времени tj, а занесение его в запоштнающий блок начинается в момент t. Затем в момент

20 времени t размык ается ключ 5 передачи, зa ыкaютcя ключ 8 сброса до t, приводя интегратор 1 к нулевым начальным условиям, и ключ 7 передачи до t, передающий занесенную в запомина25 ющнй блок 3 информацию о входном сигнале в запоминающий блок 4. Сигнал с выходного вывода 11 не содержит пульсации, так как в запоминающий блок 4 поступает конечное .значение сигнала с выхода интегратора 1 через запоми35

40

45

50

55

30

нающий блок 3, В тот же момент времени t, размыкается ключ 9 сброса до

t, и интегратор 2 начинает воспринимать сигнал с входного вывода 10. В интервале ( ) замыкается ключ 6 передачи и происходит занесение информации с выхода интегратора 2 в запоминающий блок 3. В. момент времени t JJ замыкаются ключ 9 сброса, приводя интегратор 2 к нулевым нач.алы1ым условиям, и ключ 7 передачи до t-j, через который происходит занесение информации с выхода запоминающего блока 3 в запоминающий блок 4 и с выхода запоминающего блока 4 на выходной вывод 11. В этот момент времени остальные ключи разомкнуты. Далее описанный процесс повторяется.

Таким образом, на выходной вывод устройства поступает сигнал о конечном значении интеграла, от входного сигнала на заданном интерв;ше рштег-- рирования, а не текущее, значение этого сигн;1ла, приближающееся к конечному. Благодаря этому повьшшется точность передачи сигнала дискретньм фильтром путем исключения пульсаций выходного сигнала.

( t3) замыкается ключ 5 передачи и информация о входном сигнале в процессе его интегрирования с выхода интегратора 1 заносится в запоминающий блок 3. Выходной сигнал запоминающего блока 3 имеет пульсации с периодом, равным половине периода работы устройства, так как выходной сигнал интегратора 1 достигает конечного значения в момент времени tj, а занесение его в запоштнающий блок начинается в момент t. Затем в момент

времени t размык ается ключ 5 передачи, зa ыкaютcя ключ 8 сброса до t, приводя интегратор 1 к нулевым начальным условиям, и ключ 7 передачи до t, передающий занесенную в запоминающнй блок 3 информацию о входном сигнале в запоминающий блок 4. Сигнал с выходного вывода 11 не содержит пульсации, так как в запоминающий блок 4 поступает конечное .значение сигнала с выхода интегратора 1 через запоми

5

0

5

0

5

нающий блок 3, В тот же момент времени t, размыкается ключ 9 сброса до

t, и интегратор 2 начинает воспринимать сигнал с входного вывода 10. В интервале ( ) замыкается ключ 6 передачи и происходит занесение информации с выхода интегратора 2 в запоминающий блок 3. В. момент времени t JJ замыкаются ключ 9 сброса, приводя интегратор 2 к нулевым нач.алы1ым условиям, и ключ 7 передачи до t-j, через который происходит занесение информации с выхода запоминающего блока 3 в запоминающий блок 4 и с выхода запоминающего блока 4 на выходной вывод 11. В этот момент времени остальные ключи разомкнуты. Далее описанный процесс повторяется.

Таким образом, на выходной вывод устройства поступает сигнал о конечном значении интеграла, от входного сигнала на заданном интерв;ше рштег-- рирования, а не текущее, значение этого сигн;1ла, приближающееся к конечному. Благодаря этому повьшшется точность передачи сигнала дискретньм фильтром путем исключения пульсаций выходного сигнала.

3

Формула изобретения

Дискретный фильтр, содержащий входной, выходной и общий вьюоды для подключения соответственно источника входного напряжения и цепи нагрузки, два интегратора, два ключа сброса, два ключа передачи и запоминающий блок, причем входы интеграторов объединены и соединены с входным выводом, выход первого интегратора через первый ключ сброса и первый ключ передачи соединен соот ветственно с общим выводом и входом запоминающего блока, а выход второ

Лл

tot

Составитель А. Кириллов Редактор Н. Гунько Техред м.Ходанич Корректор Л. Пилипенко

Заказ 5294/54 Тираж 659 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

50783

го интегратора через второй ключ сброса и второй ключ передачи соединен соответственно с общий выводом и входом запоминающего блока, отличающийся тем, что, с целью улучшения эффективности путем повьпления точности передачи входного сигнала, дополнительно введены 10 третий ключ передачи и второй запоминающий блок, вход которого через указанный третий ключ передачи соединен с выходом основного запоминающего блока, а его выход соединен с 15 выходным выводом.

tstBt-j

Фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Датчик напряжения вентильного преобразователя постоянного тока | 1980 |

|

SU917276A2 |

| Дискретный фильтр | 1980 |

|

SU955423A1 |

| Амплитудно-фазовый анализатор гармоник периодических напряжений | 1985 |

|

SU1303950A2 |

| Устройство для определения средних значений сигналов (его варианты) | 1982 |

|

SU1190271A1 |

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ ПРОИЗВОЛЬНОЙ ФОРМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2034302C1 |

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347028A1 |

| Устройство для моделирования упругого гистерезиса | 1980 |

|

SU966708A1 |

| Датчик пульсирующего напряжения | 1982 |

|

SU1116503A1 |

| Источник калиброванных напряжений | 1985 |

|

SU1283726A1 |

Изобретение относится к области электротехники и может быть использовано в устройствах, обеспечивающих высокое быстродействие передачи сигнала обратной связи. Цель изобретения - улучшение эффективности путем повышения точности передачи входного сигнала. Сигнал с входного вывода 10 поступает на входы интеграторов 1, 2. Путем поочередного переключения ключей сброса 8, 9 происходит передача сигнала с выхода соответствующего интегратора 1,2 через ключи передачи 5-7 и запоминающие блоки 3, 4 на выходной вывод 11. В результате обеспечивается поступление на выходной вывод 11 сигнала о конечном значении интеграла от входного сигнала на заданном интервале интегрирования, а не текущее значение этого сигнала, приближающееся к конечному. Такой режим работы позволяет исключить пульсации выходного сигнала. 2 ил.. . с € (Л 6bfX. ОО сл о 00

| Датчик напряжения вентильного преобразователя постоянного тока | 1973 |

|

SU490235A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Дискретный фильтр | 1980 |

|

SU955423A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-11-07—Публикация

1985-10-16—Подача