Изобретение относится к измерительной технике, предназначено для измерения средних значений сигналов и может быть использовано в установках технической диагностики, спектрально- го состава шумов и вибраций, режимов работы различных промьгаленных объектов, а также.в медицине при измерении среднего давления крови в тече- ние каждого сердечного цикла, определении среднего выдыхаемого объема СО в каждом дыхательном цикле,

Цель изобретения - повьшение точности измерения за счет введения пе- ременного масштаба интегрирования и расширения диапазона вариаций времени усреднения.

I

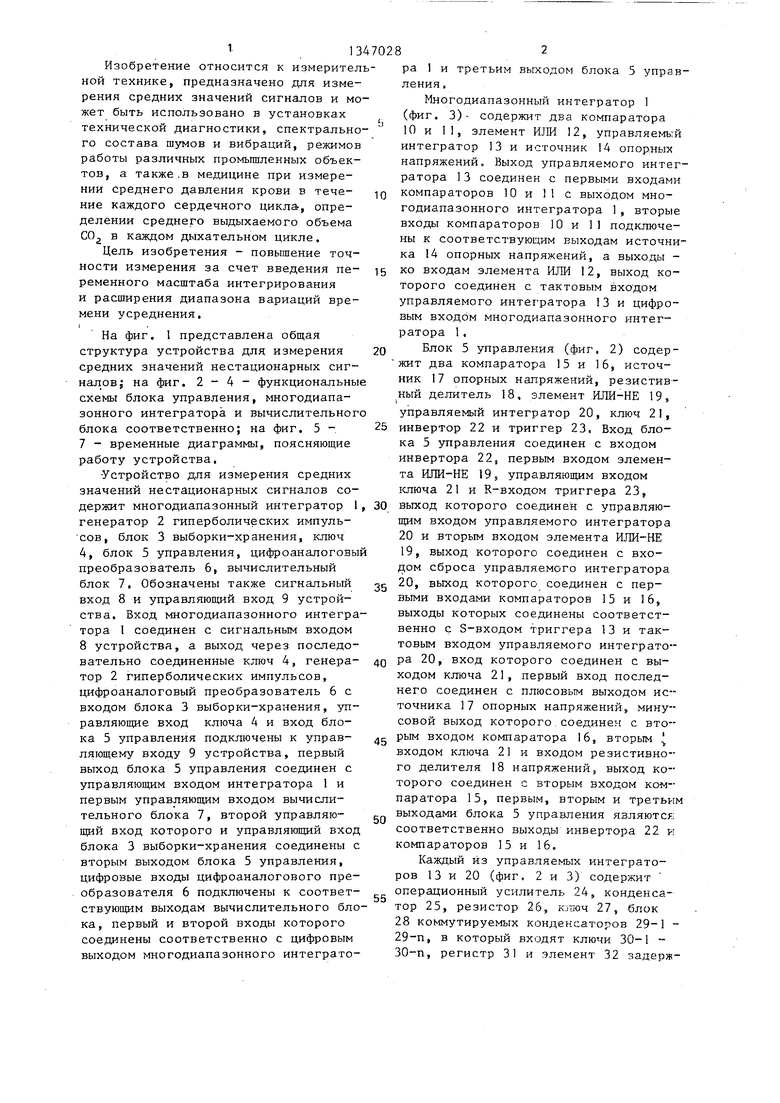

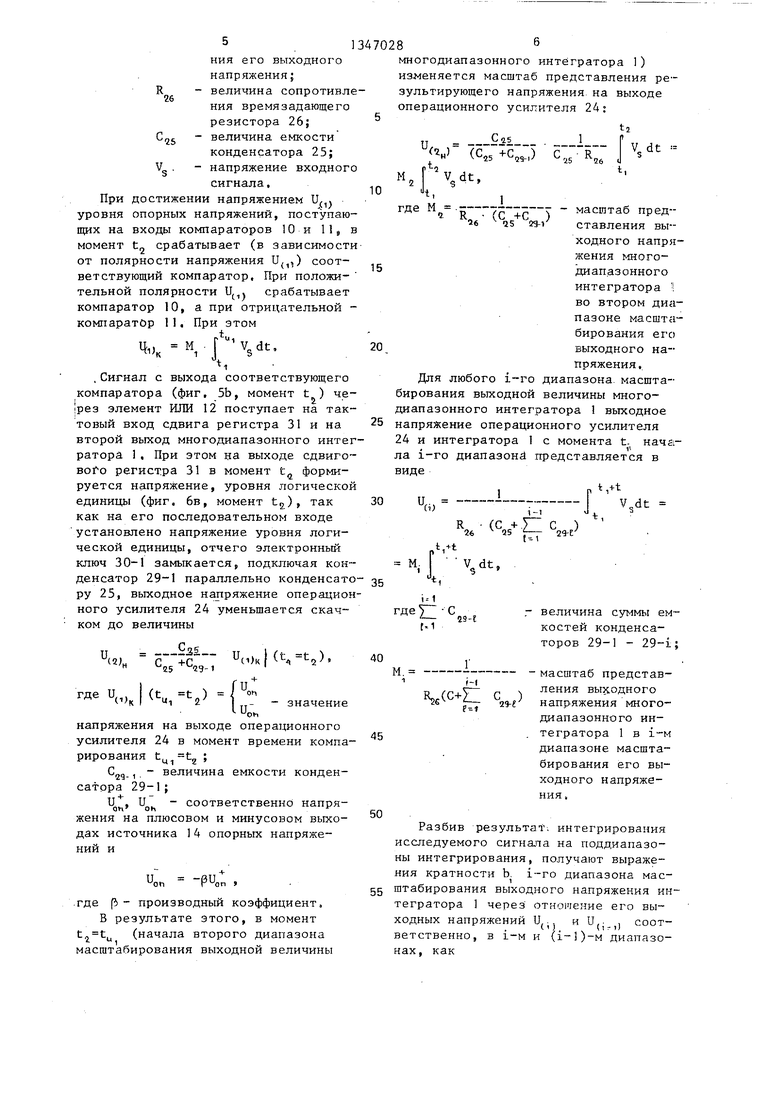

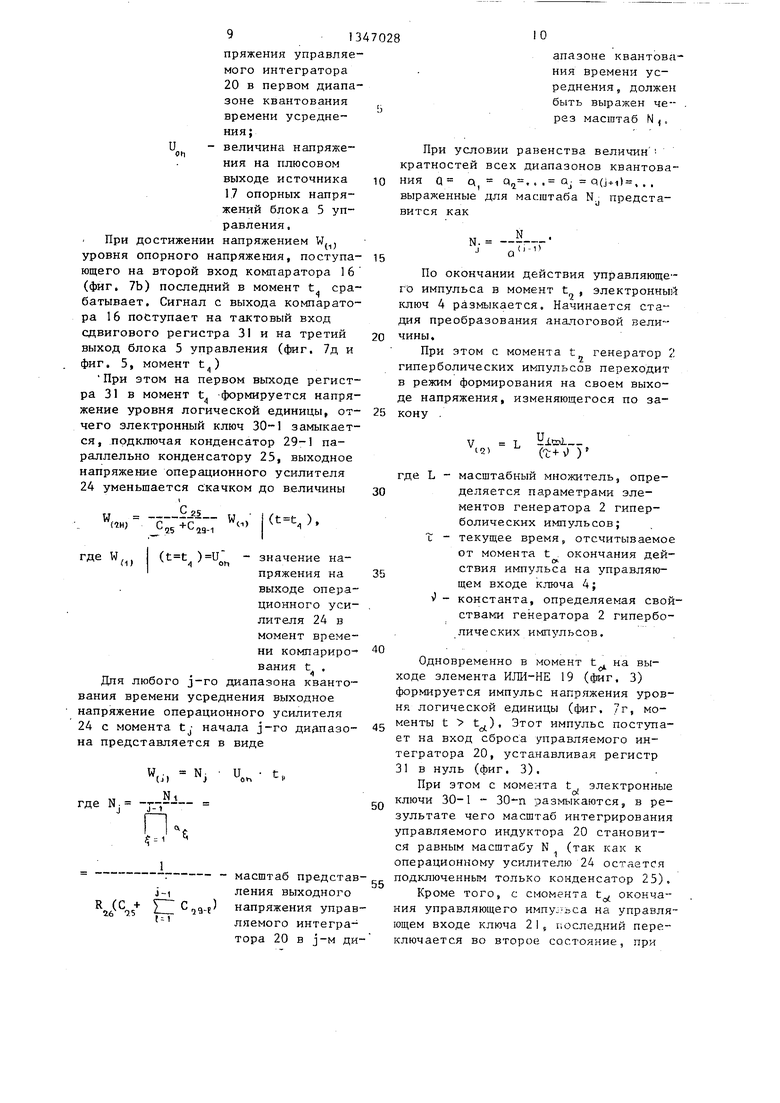

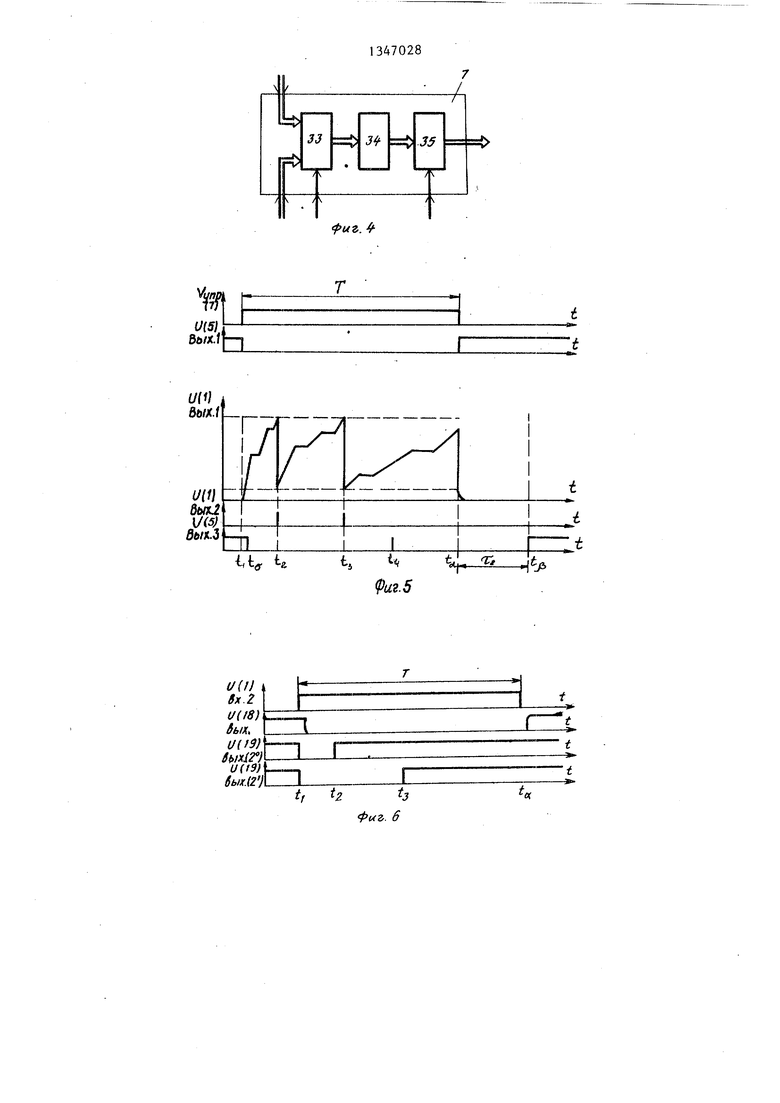

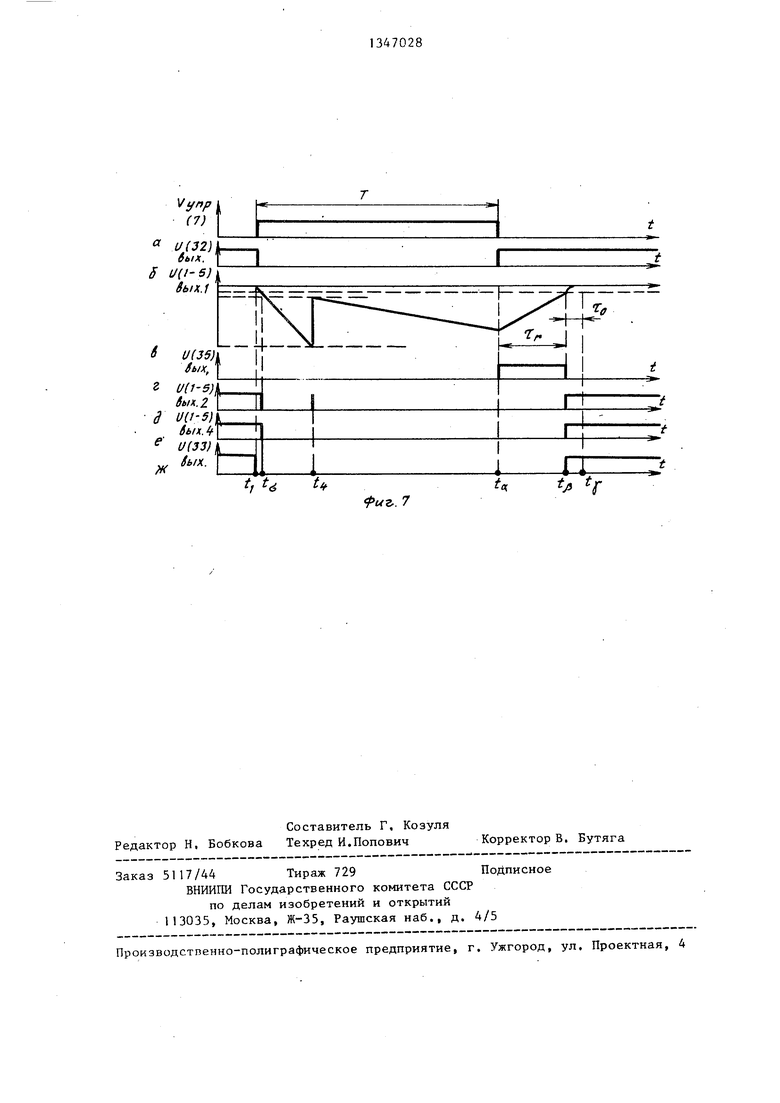

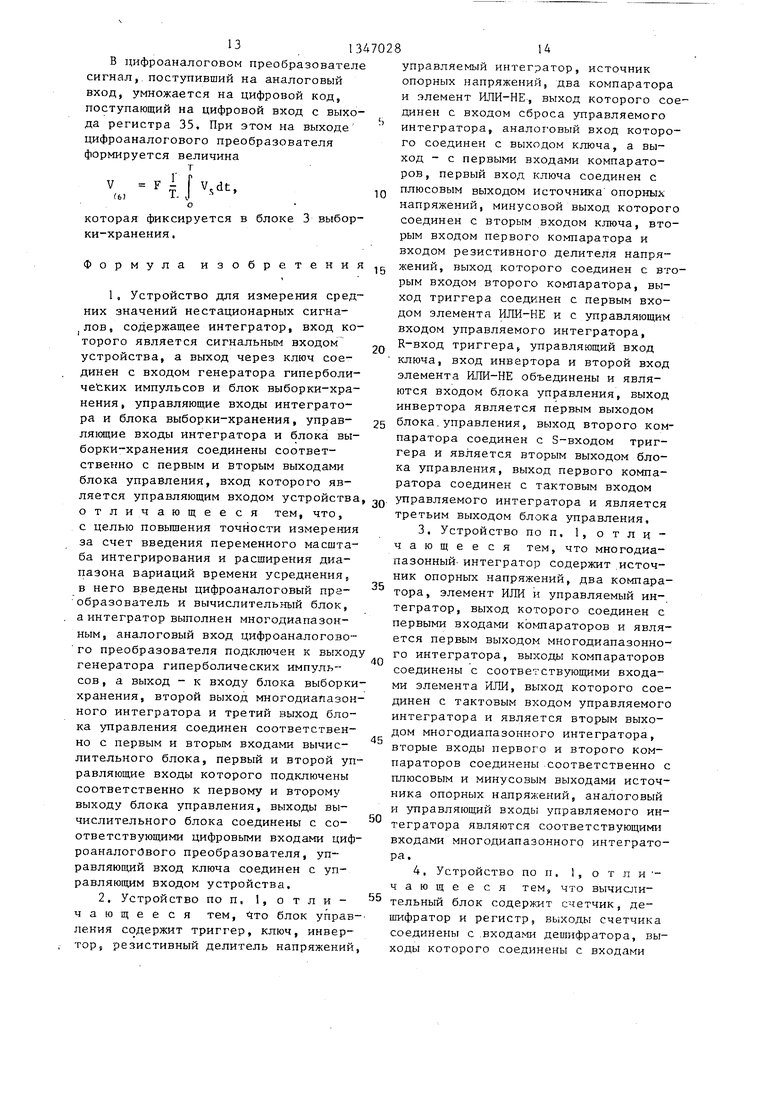

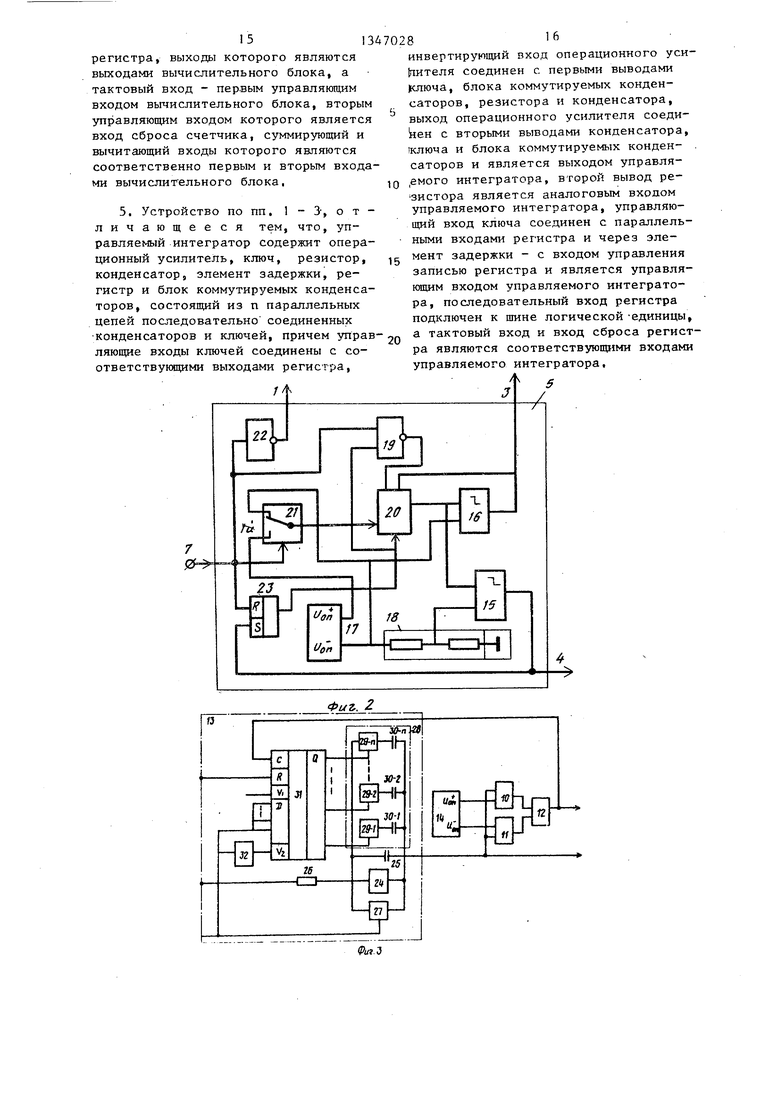

На фиг, 1 представлена общая структура устройства для измерения средних значений нестационарных сигналов; на фиг. 2 - 4 - функциональные схемы блока управления, многодиапазонного интегратора и вычислительного блока соответственно; на фиг. 5 -

7- временные диаграммы, поясняющие работу устройства.

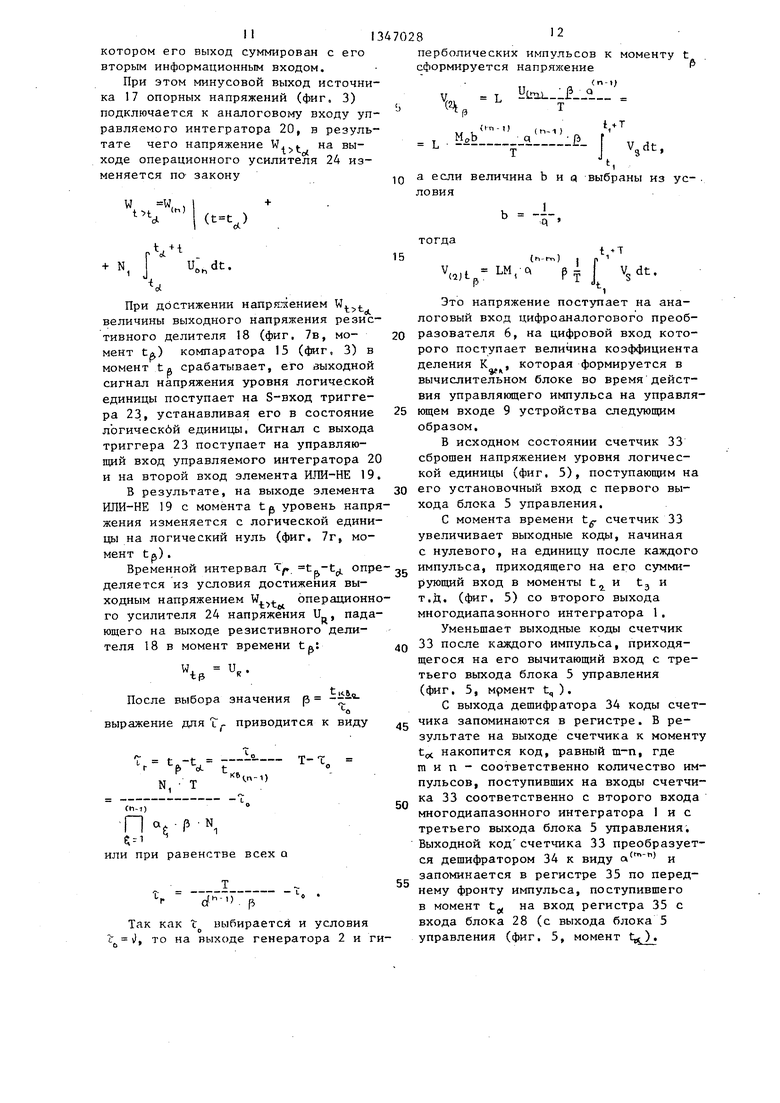

-Устройство для измерения средних значений нестационарных сигналов содержит многодиапазонный интегратор 1 генератор 2 гиперболических импуль- сов, блок 3 выборки-хранения, ключ 4, блок 5 управления, цифроаналоговый преобразователь 6, вычислительный блок 7. Обозначены также сигнальный вход 8 и управляющий вход 9 устройства. Вход многодиапазонного интегратора 1 соединен с сигнальным входом

8устройства, а выход через последовательно соединенные ключ 4, генера- тор 2 гиперболических импульсов, цифроаналоговый преобразователь 6 с входом блока 3 выборки-хранения, уп- равляюЕ1ие вход ключа 4 и вход блока 5 управления подключены к управ- ляющему входу 9 устройства, первый выход блока 5 управления соединен с управляющим входом интегратора 1 и первым управляющим входом вычислительного блока 7, второй управляю- щий вход которого и управляющий вход блока 3 выборки-хранения соединены с вторым выходом блока 5 управления, цифровые входы цифроаналогового преобразователя 6 подключены к соответ- ствующим выходам вычислительного блока, первый и второй входы которого соединены соответственно с цифровым выходом многодиапазонного интегратора и третьим выходом блока 5 упра.в ления.

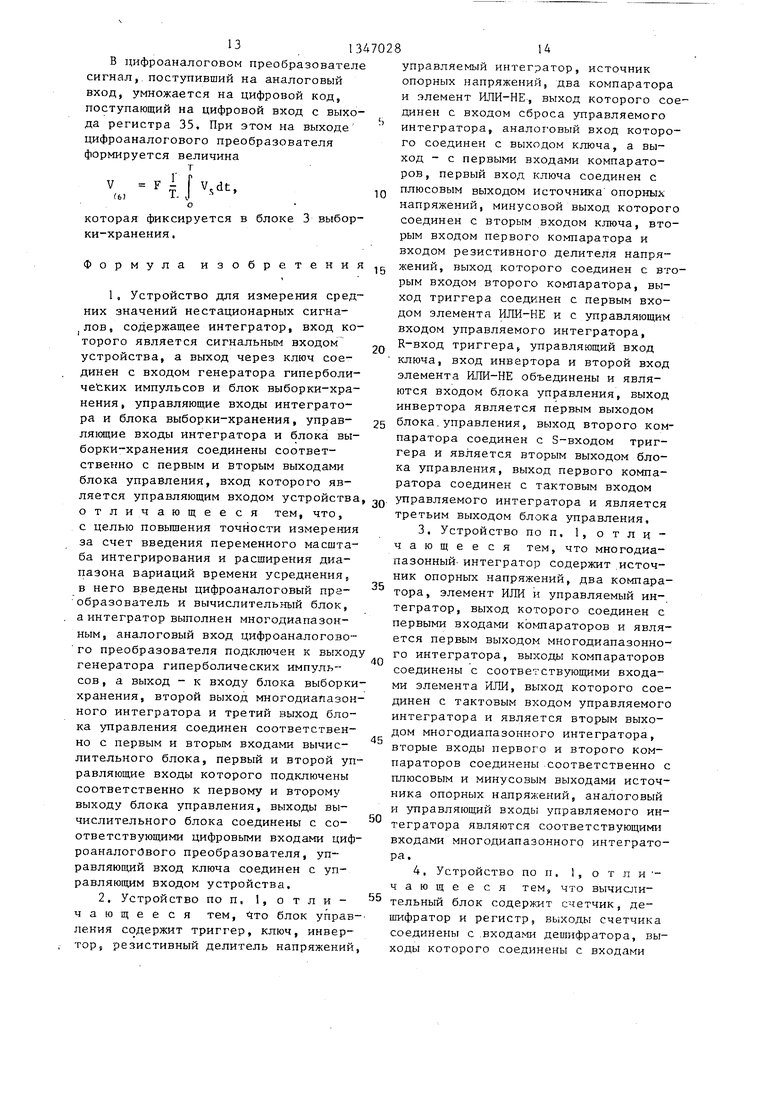

Многодиапазонный интегратор 1 (фиг. 3)- содержит два компаратора 10 и 11, злемент ШШ 12, управляемый интегратор 13 и источник 14 опорных напряжений. Выход управляемого интегратора 13 соединен с первыми входами компараторов 10 и 11 с выходом многодиапазонного интегратора 1, вторые входы компараторов 10 и 11 подключены к соответствующим выходам источника 14 опорных напряжений, а выходы - ко входам элемента ИЛИ 12, выход которого соединен с тактовым входом управляемого интегратора 13 и цифровым входом многодиапазонного интегратора 1.

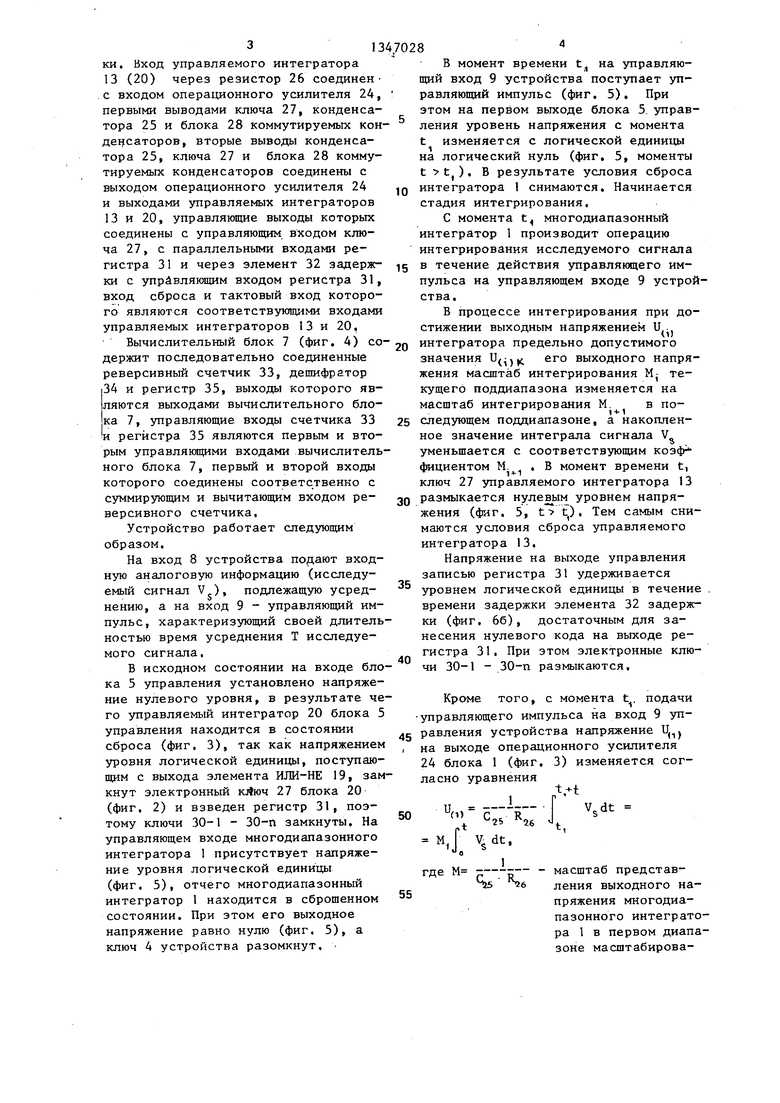

Блок 5 управления (фиг, 2) содержит два компаратора 15 и 16, источник 17 опорных напряжений, резистив- ный делитель 18, элемент .ИЛИ-НЕ 19, управляемый интегратор 20, ключ 21, инвертор 22 и триггер 23. Вход блока 5 управления соединен с входом инвертора 22, первым входом элемента ИЛИ-НЕ 19, управляющим входом ключа 21 и R-входом триггера 23, выход которого соединен с управляющим входом управляемого интегратора 20 и вторым входом элемента ИЛИ-НЕ

19,выход которого соединен с входом сброса управляемого интегратора

20,выход которого соединен с первыми входами компараторов 15 и 16, выходы которых соединены соответственно с S-входом триггера 13 и тактовым входом управляемого интегратора 20, вход которого соединен с выходом ключа 21, первый вход последнего соединен с плюсовым выходом источника 17 опорных напряжений, минусовой выход которого.соединен с вторым входом компаратора 16, вторым входом ключа 21 и входом резистивно- го делителя 18 напряжений, выход которого соединен с вторым входом компаратора 15, первым, вторым и третьи выходами блока 5 управления являются; соответственно выходы инвертора 22 к компараторов 15 и 16.

Каждый из управляемых интеграторов 13 и 20 (фиг. 2 и 3) содержит операционный усилитель 24 конденсатор 25, резистор 26, кгаоч 27, блок 28 коммутируемых конденсаторов 29-1 - 29-п, в который входят ключи 30-1 ЗО-п, регистр 31 и элемент 32 задерж

313

ки. Вход управляемого интегратора 13 (20) через резистор 26 соединен- с входом операционного усилителя 24, первыми выводами ключа 27, конденсатора 25 и блока 28 коммутируемых конденсаторов, вторые выводы конденсатора 25, ключа 27 и блока 28 коммутируемых конденсаторов соединены с выходом операционного усилителя 24 и выходами управляемых интеграторов 13 и 20, управляющие выходы которых соединены с управляющим входом ключа 27, с параллельными входами регистра 31 и через элемент 32 задержки с управляющим входом регистра 31, вход сброса и тактовый вход которого являются соответствующими входами управляемых интеграторов 13 и 20.

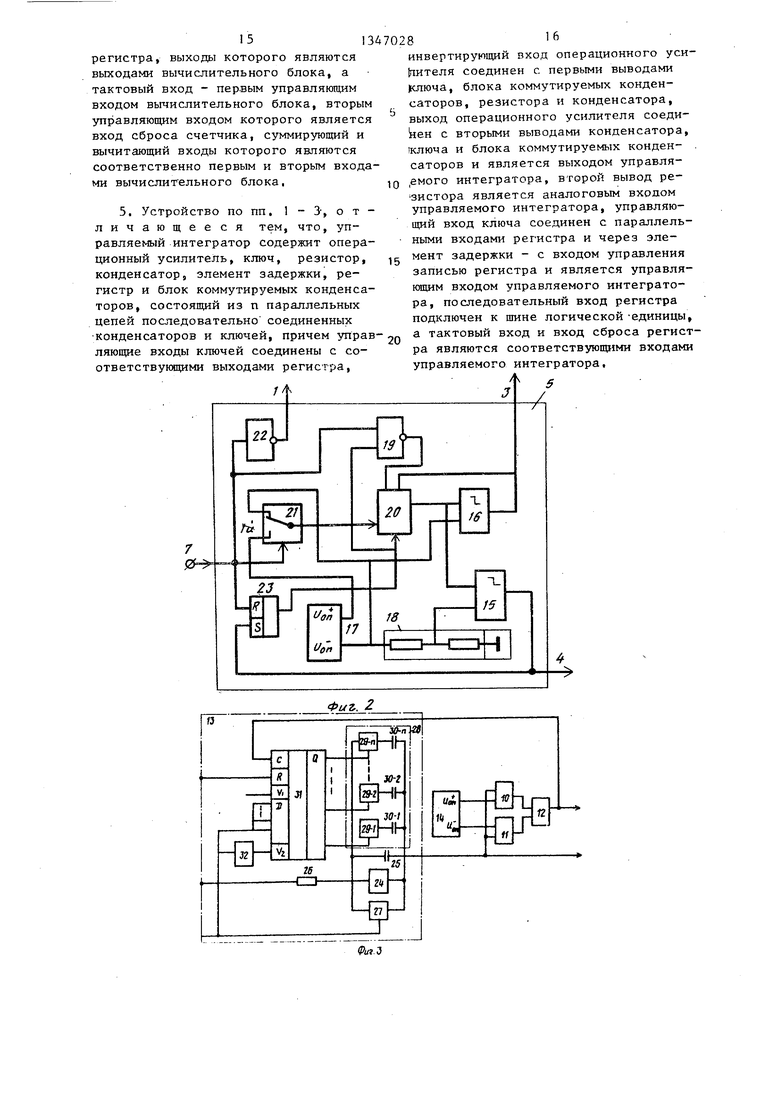

Вычислительный блок 7 (фиг, 4) содержит последовательно соединенные реверсивный счетчик 33, дешифратор 34 и регистр 35, выходы которого являются выходами вычислительного блока 7, управляющие входы счетчика 33 и регистра 35 являются первым и вторым управляющими входами вычислительного блока 7, первый и второй входы которого соединены соответственно с суммирующим и вычитающим входом реверсивного счетчика.

Устройство работает следующим образом.

На вход 8 устройства подают входную аналоговую информацию (исследуемый сигнал V ), подлежащую усреднению, а на вход 9 - управляющий импульс, характеризующий своей длительностью время усреднения Т исследуемого сигнала.

В исходном состоянии на входе блока 5 управления установлено напряжение нулевого уровня, в результате чего управляемый интегратор 20 блока 5 управления находится в состоянии сброса (фиг. 3), так как напряжением уровня логической единицы, поступающим с выхода элемента ИЛИ-НЕ 19, замкнут электронный кЛюч 27 блока 20 (фиг. 2) и взведен регистр 31, поэтому ключи 30-1 - 30-п замкнуты. На управляющем входе многодиапазонного интегратора 1 присутствует напряжение уровня логической единицы (фиг. 5), отчего многодиапазонный интегратор 1 находится в сброщенном состоянии. При этом его выходное напряжение равно нулю (фиг. 5), а ключ 4 устройства разомкнут.

0

5

В момент времени t, на управляющий вход 9 устройства поступает управляющий импульс (фиг, 5), При этом на первом выходе блока 5. управления уровень напряжения с момента t изменяется с логической единицы на логический нуль (фиг, 5, моменты t tj). В результате условия сброса интегратора 1 снимаются. Начинается стадия интегрирования.

С момента t многодиапазонный интегратор 1 производит операцию интегрирования исследуемого сигнала в течение действия управляющего импульса на управляющем входе 9 устройства.

В процессе интегрирования при достижении выходным напряжением К . 0 интегратора предельно допустимого значения U()jt его выходного напряжения масщтаб интегрирования М текущего поддиапазона изменяется на

масштаб интегрирования М. в последующем поддиапазоне, а накопленное значение интеграла сигнала V уменьщается с соответствующим коэф- фициентом М. , В момент времени ti ключ 27 управляемого интегратора 13 размыкается нулевым уровнем напряжения (фиг. 5, t t). Тем самым снимаются условия сброса управляемого интегратора 13.

Напряжение на выходе управления записью регистра 31 удерживается уровнем логической единицы в течение времени задержки элемента 32 задержки (фиг. 66), достаточным для занесения нулевого кода на выходе регистра 31. При этом электронные ключи 30-1 - 30-п размыкаются.

Кроме того, с момента Ц. подачи управляющего импульса на вход 9 уп- 45 равления устройства напряжение Ц I на выходе операционного усилителя 24 блока 1 (фиг, 3) изменяется согласно уравнения 1

Uo)

.Г

V,dt,

,Vt

Vgdt

t,

где М

(6

масштаб представления выходного напряжения многодиапазонного интегратора 1 в первом диапазоне масштабирова26

iS

ния его выходного напряжения;

R. - величина сопротивления времязадающего резистора 26; величина емкости конденсатора 25; V . - напряжение входного

сигнала.

При достижении напряжением U, уровня опорных напряжений, nocTVnaro- щих на входы компараторов 10 и 11, в момент tn срабатывает (в зависимости от полярности напряжения U,,) соответствующий компаратор. При положи- тельной полярности Ц, срабатывает компаратор 10, а при отрицательной компаратор 11, При этом -t,,

).

м .

.Сигнал с выхода соответствующего компаратора (фиг, 5Ь, момент t ) че|рез элемент ИЛИ 12 поступает на тактовый вход сдвига регистра 31 и на второй выход многодиапазонного интегратора , При этом на выходе сдвиго- Bofo регистра 31 в момент t формируется напряжение, уровня логической единицы (фиг, 6в, момент tg), так как на его последовательном входе установлено напряжение уровня логической единицы, отчего электронный ключ 30-1 замыкается, подключая конденсатор 29-1 параллельно конденсате- ру 25, выходное напряжение операционного усилителя 24 уменьшается скачком до величины

..

+с

-29-1

ио)).

Д Ч),

Ч г

и„

- значение

напряжения на выходе операционного усилителя 24 в момент времени компа- рирования ;

1

- величина емкости конденсатора 29-1 ;

и , и - соответственно напряоп Oh

жения на плюсовом и минусовом выходах источника 14 опорных напряжений и

и„

-pUon ,

где р- производный коэффициент. В результате этого, в момент (начала второго диапазона масштабирования выходной величины

347028

многодиапазонного интегратора 1) изменяется масштаб представления результирующего напряжения на выходе операционного усилителя 24:

1

t2

V

Itj t,

(С dt.

25 QS-i

) с„-к

25

26

t,

где М,.-1

26

(С +С ) -25 гз-г

масштаб представления выходного напряжения многодиапазонногоинтегратора во втором диапазоне масштабирования его выходного напряжения.

Для любого i-го диапазона, масштабирования выходной величины многодиапазонного интегратора 1 выходное напряжение операционного усилителя

24 и интегратора 1 с момента t. ла i-ro диапазон представляетс виде

t,+t

(0

1

1-1

R - (С+г: с J

i:

V

26

25

М

с:

1

уч-г

,

0 5

0

5

i--1

где С

М.

гз-е

i. f-i

R,,(c+r: с,:

г величина суммы емкостей конденсаторов 29-1 - 29-i;

- масштаб представления вы ;одного напряжения многодиапазонного интегратора 1 в диапазоне масштабирования его выходного напряжения ,

Разбив результат, интегрирования исследуемого сигнала на поддиапазоны интегрирования, получают выражения кратности Ь, i-ro диапазона мас- штабирования выходного напряжения интегратора 1 через отягчение его выU .

и и

соот

и (i-J)-M диапазо

и

(1-1)

При этом, масштабы М. представления выходных напряжений интегратора 1 в i-x диапазонах масштабирования его выходного напряжения могут быть выражены через масштаб Mj, представления выходного напряжения интегратора в первом диапазоне согласно

1-1

М.

«, П ь.

(

в частности, при равенстве всех коэффициентов b b. Ь„ ... b: b .., (т.е. при равенстве кратностей всех диапазонов масштабирования выходного напряжения интегратора 1)

(i-1)

М. М. b I 1

Одновременно, в течение действия на управляющем входе 9 устройства управляющего импульса, характеризующего своей длительностью время усреднения Т исследуемого сигнала, блок 5 управления формирует также на третьем выходе в соответствующие моменты времени сигналы меток времени,характеризующие границы заранее заданных времен- ных интервалов, на KOToiJbie квантуется управляющий импульс, т.е. последний

с момента t начала своего действия разбивается блоком 5 на диапазоны квантования по времени.

Границам окончания этих последовательно расположенных во времени диапазонов квантования соответствуют моменты времени t„

-ЦЬ -KSj

t, t,,, «.. соответственно,

bj (j+l)

отсчитанные от момерта t

-KR: -КК/...,

и определяющие моменты появления соответствующих сигналов меток времени на третьем выходе блока 5 управления, с которого

С.приходом в момент t на вход блока 5 управления импульса напряжения уровня логической единицы (фиг. 7а) уровни напряжений на выходах элементов 22 и 23 (фиг. 3) меняются на противоположные (фиг. 76 и ж). В результате, ключ 27 управляемого интегратора 20 (фиг. 2) размыкается нулевым уровнем напряжения, поступающим, с выхода триггера 23 (тем самым снимаются условия сброса управляемого интегратора 20).

Кроме того, с момента t, прихода 35 управляющего импульса на управляющий вход ключа 21 последний переключается в состояние, при котором его вы- ход скоммутирован с его первым информационным входом.

0 При этом плюсовой выход источника 17 опорных напряжений (фиг. 2), подключается к аналоговому входу управляемого интегратора 20 (фиг. 2), в результате чего напряжение WM

они поступают на второй вход вычисли- 45 на выходе операционного усилителя 24

управляемого интегратора 20 для первого диапазона квантования времени усреднения (квантования по времени импульса управления) изменяется сог- 50 ласно

1

тельного блока 7 (фиг. 1).

Если кратность а j-ro диапазона квантования времени усреднения Т выразить через отношение его границ, определенных моментами t и

К5;

согласно уравнения

с,. R.M

Vt

0. bLu,

К6(,.,)

Кб,

окончания

то в моменты времени t j-x диапазонов квантования, отсчитанные от момента t, начала действия упоавляющего импульса, могут быть

3470288

выражены через нижнюю границу первого диапазона квантования ласно уравнения

где t,

К6„

- момент времени, отсчитан- ный от момента t .

В частности, при равенстве .всех коэффициентов Q о а. . . CL , ... (т.е. при квантовании управляющего импульса на кратные временные интервалы)

Х- tKbo

С логического инвертора 22 напряжение уровня логической единицы (фиг. 76) поступает на выход блока 5 управления (фиг. 5).

С.приходом в момент t на вход блока 5 управления импульса напряжения уровня логической единицы (фиг. 7а) уровни напряжений на выходах элементов 22 и 23 (фиг. 3) меняются на противоположные (фиг. 76 и ж). В результате, ключ 27 управляемого интегратора 20 (фиг. 2) размыкается нулевым уровнем напряжения, поступающим, с выхода триггера 23 (тем самым снимаются условия сброса управляемого интегратора 20).

Кроме того, с момента t, прихода управляющего импульса на управляющий вход ключа 21 последний переключается в состояние, при котором его вы- ход скоммутирован с его первым информационным входом.

При этом плюсовой выход источника 17 опорных напряжений (фиг. 2), подключается к аналоговому входу управляемого интегратора 20 (фиг. 2), в результате чего напряжение WM

1

с,. R.M

t,

Vt

N,Jl где N

dt N

t,

25

26

- масштаб представления выходного на91347028

пряжения управляемого интегратора 20 в первом диапазоне квантования времени усреднения;и - величина напряжеOh

НИН на плюсовом выходе источника 1.7 опорных напряжений блока 5 уп- вится как равления.

При достижении напряжением ровня опорного напряжения, поступа- 15 щего на второй вход компаратора 16 фиг. 7Ь) последний в момент t сраатывает. Сигнал с выхода компаратоа 16 поступает на тактовый вход

f)

При усл кратностей 10 ния 0 а выраженные

По окон го импульс ключ 4 раз дия преобр чины.

сдвигового регистра 31 и на третий выход блока 5 управления (фиг, 7д и фиг, 5, момент t)

При этом на первом выходе регистра 31 в момент t, формируется напряжение уровня логической единицы, от- чего электронный ключ замыкается, подключая конденсатор 29-1 параллельно конденсатору 25, выходное напряжение операционного усилителя 24 уменьшается скачком до величины

25

С 25

W

О)

().

где W

(1)

(,)u,;

значение напряжения на выходе операционного усилителя 24 в момент времени компариро- вания t ,

Для любого j-ro диапазона квантования времени усреднения выходное напряжение операционного усилителя 24 с момента tj начала j-ro диапазона представляется в виде

W

NJ

(j) Nt

N:

J-1

. масштаб представJ-,ления выходного

(С ZZr QS-f напряжения управ- - ляемого интегратора 20 в J-M ди

вится как

апазоне квантования времени усреднения, должен

быть выражен че- .

рез масштаб N j.

При условии равенства величин кратностей всех диапазонов квантова- ния 0 а, Q. .. . QJ ci(J-n . . . выраженные для масштаба N,, предстао

N. J

N

() Л )

По окончании действия управляющего импульса в момент t , электронный ключ 4 размыкается. Начинается стадия преобразования аналоговой величины.

При этом с момента t генератор 2 гиперболических импульсов переходит в режим формирования на своем выходе напряжения, изменяющегося по закону .

L

У1,1

(г+) )

где L - масштабный множитель, определяется параметрами элементов генератора 2 гиперболических импульсов; X - текущее время, отсчитываемое от момента t . окончания действия импульса на управляющем входе ключа 4; - константа, определяемая свойствами генератора 2 гиперболических импульсов.

Одновременно в момент t . на выходе элемента ИЛИ-НЕ 19 (фиг, 3) формируется импульс напряжения уровня логической единицы (фиг, 7г, мо- менты t t). Этот импульс поступает на вход сброса управляемого интегратора 20, устанавливая регистр 31 в нуль (фиг, 3).

При этом с момента t, электронные

ключи 30-1 - размыкаются, в результате чего масщтаб интегрирования управляемого индуктора 20 становится равным масштабу N (так как к операционному усилителю 24 остается подключенным только конденсатор 25). Кроме того, с смомента t окончания управляющего импу лъса на управляющем входе ключа 2I; последний переключается во второе состояние, при

И13470:

котором его выход суммирован с его вторым информационным входом.

При этом минусовой выход источника 17 опорных напряжений (фиг, 3) подключается к аналоговому входу уп- равляемого интегратора 20, в результате чего напряжение W

на выходе операционного усилителя 24 изменяется по закону

,

w,

(f )

( -V

I

Uo.dt.

При достижении напркзсением W величины выходного напряжения резис- тивного делителя 18 (фиг, 7в, мо- мент tu) компаратора 15 (фиг, 3) в момент tа срабатывает, его выходной сигнал напряжения уровня логической единицы поступает на S-вход триггера 23, устанавливая его в состояние логическбй единицы. Сигнал с выхода триггера 23 поступает на управляющий вход управляемого интегратора 20 и на второй вход элемента ИЖ-НЕ 19.

В результате, на выходе элемента ИЛИ-НЕ 19 с момента tp уровень напряжения изменяется с логической единицы на логический нуль (фиг. 7г, момент tp).

Временной интервал Т t-t опре- деляется из условия достижения выходным напряжением W операционного усилителя 24 напряжения U , падающего на выходе резистивного делителя 18 в момент времени

% - После выбора значения р

tKi

выражение для f приводится к виду g

N, Т

«(п--(} -7.

СП-1)

Л , .1 или при равенстве всех

Т 55

г

Так как t выбирается и условия 1), то на выходе генератора 2 и ги8 2

перболических импульсов к моменту t

сформируется напряжение

V

.

L yL

(n-t

L

M.,b

(t п - I)

(n-1 )

v

I VHt.

a если величина b и q выбраны из ус-. ловия

1

тогда

(м-гг,;

t.

(аИр ЬМ,-й

Р I

.

0 5

0

jg 0

g

0

5

Это напряжение поступает на аналоговый вход цифроаналогового преобразователя 6, на цифровой вход которого поступает величина коэффициента деления К , которая формируется в вычислительном блоке во время действия управлякицего импульса на управляющем входе 9 устройства следующим образом.

В исходном состоянии счетчик 33 сброшен напряжением уровня логической единицы (фиг, 5), поступающим на его установочный вход с первого выхода блока 5 управления,

С момента времени t счетчик 33 увеличивает выходные коды, начиная с нулевого, на единицу после каждого импульса, приходящего на его суммирующий вход в моменты t. и t и т,д. (фиг. 5) со второго выхода многодиапазонного интегратора 1.

Уменьщает выходные коды счетчик 33 после каждого импульса, приходящегося на его вычитающий вход с третьего выхода блока 5 управления (фиг. 5, мрмент ц).

С выхода дешифратора 34 коды счетчика запоминаются в регистре. В результате на выходе счетчика к моменту t накопится код, равный m-n, где тип- соответственно количество импульсов, поступивших на входы счетчика 33 соответственно с второго входа многодиапазонного интегратора 1 и с третьего выхода блока 5 управления. Выходной код счетчика 33 преобразуется дешифратором 34 к виду и запоминается в регистре 35 по переднему фронту импульса, поступившего в момент t на вход регистра 35 с входа блока 28 (с выхода блока 5 управления (фиг. 5, момент t).

В цифроаналоговом преобразователе сигнал, поступивший на аналоговый вход, умножается на цифровой код, поступающий на цифровой вход с выхода регистра 35, При этом на выходе цифроаналогового преобразователя формируется величина

V F (6)

1.

которая фиксируется в блоке 3 выборки-хранения.

Формула изобре тения

1, Устройство для измерения средних значений нестационарных сигналов, содержащее интегратор, вход которого является сигнальным входом устройства, а выход через ключ соединен с входом генератора гиперболи- чеЬких импульсов и блок выборки-хранения , управляющие входы интегратора и блока выборки-хранения, управ- ля1сяцие входы интегратора и блока выборки-хранения соединены соответственно с первым и вторым выходами блока управления, вход которого является управляющим входом устройства отличающееся тем, что, с целью повышения точности измерения за счет введения переменного масштаба интегрирования и расширения диапазона вариаций времени усреднения, в него введены цифроаналоговый праобразователь и вычислительный блок, а интегратор выполнен многодиапазонным, аналоговый вход цифроаналогово го преобразователя подключен к выход

генератора гиперболических импуль-- сов, а выход - к входу блока выборки- хранения, второй выход многодиапазонного интегратора и третий выход блока управления соединен соответственно с первым и вторым входами вычислительного блока, первый и второй управляющие входы которого подключены соответственно к первому и второму выходу блока управления, выходы вычислительного блока соединены с со- ответствующими цифровыми входами циф- роаналогОвого преобразователя, управляющий вход ключа соединен с управляющим входом устройства,

2, Устройство по п. 1, о т л и - чающее ся тем, :iTo блок управления содержит триггер, ключ, инвертор, резистивный делитель напряжений

0

g

п 5 Q

0

5

управляемый интегратор, источник опорных напряжений, два компаратора и элемент ИЛИ-НЕ, выход которого соединен с входом сброса управляемого интегратора, аналог овый вход которого соединен с выходом ключа, а выход - с первыми входами компараторов, первый вход ключа соединен с плюсовым выходом источника опорных напряжений, минусовой выход которого соединен с вторым входом ключа, вторым входом первого компаратора и входом резистивного делителя напряжений, выход которого соединен с вторым входом второго компаратора, выход триггера соединен с первым входом элемента ИЛИ-НЕ и с управляющим входом управляемого интегратора, R-вход триггера, управляющий вход ключа, вход инвертора и второй вход элемента ИЛИ-НЕ объединены и являются входом блока управления, выход инвертора является первым выходом блока.управления, выход второго компаратора соединен с S-входом триггера и является вторым выходом блока управления, выход первого компаратора соединен с тактовым входом управляемого интегратора и является третьим выходом блока управления,

3,Устройство по п, 1, о т л и - чающееся тем, что многодиапазонный- интегратор содержит источник опорных напряжений, два компаратора, элемент ИЛИ и управляемый интегратор, выход которого соединен с первыми входами компараторов и является первым выходом многодиапазонного интегратора, выходы компараторов соединены с соответствующими входами элемента ИЛИ, выход которого соединен с тактовым входом управляемого интегратора и является вторым выходом многодиапазонного интегратора, вторые входы первого и второго компараторов соединены соответственно с плюсовым и минусовым выходами источника опорных иапрялсений, аналоговый и управляющий входы управляемого интегратора являются соответствующими входами многодиапазонного интегратора,

4,Устройство по п, , о т л и - чающееся тем, что вычислительный блок содержит счетчик, дешифратор и регистр, выходы счетчика соединены с .входами дешифратора, выходы которого соединены с входами

регистра, выходы которого являются выходами вычислительного блока, а тактовый вход - первым управляющим входом вычислительного блока, вторым управляющим входом которого является вход сброса счетчика, суммирующий и вычитающий входы которого являются соответственно первым и вторым входами вычислигельного блока,

5, Устройство по пп, 1 3-, о т - личающееся тем, что, управляемый интегратор содержит операционный усилитель, ключ, резистор, конденсатор, элемент задержки, регистр и блок коммутируемых конденсаторов, состоящий из п параллельных цепей последовательно соединенных конденсаторов и ключей, причем управляющие входы ключей соединены с соответствующими выходами регистра.

0

5

0

инвертирующий вход операционного уси- 1г1ителя соединен с первыми выводами люча, блока коммутируемых конденсаторов, резистора и конденсатора, выход операционного усилителя соеди- нен с вторыми выводами конденсатора, 1ключа и блока коммутируемых конденсаторов и является выходом управля- ,емого интегратора, второй вывод ре- зистора является аналоговым входом управляемого интегратора, управляющий вход ключа соединен с параллельными входами регистра и через элемент задержки - с входом управления записью регистра и является управляющим входом управляемого интегратора, последовательный вход регистра подключен к шине логической -единицы, а тактовый вход и вход сброса регистра являются соответствующими входами управляемого интегратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1337784A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347027A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ ПРОИЗВОЛЬНОЙ ФОРМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2034302C1 |

| Устройство для автоматической смены масштабов в аналоговой вычислительной машине | 1983 |

|

SU1080153A1 |

| Амплитудно-фазовый анализатор гармоник | 1985 |

|

SU1272272A2 |

| Устройство для имитации цифрового сигнала ошибки следящего привода | 1987 |

|

SU1472870A1 |

| Устройство для управления вентильным преобразователем со слежением | 1988 |

|

SU1607061A1 |

| Амплитудно-фазовый анализатор гармоник периодических напряжений | 1985 |

|

SU1303950A2 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1251184A1 |

Изобретение может быть использовано в установках технической диаг-. ностики спектрального состава шумов и вибраций, режимов работы различных промышленных объектов, а также в медицине при измерении среднего давления крови в течение каждого сердечного цикла, среднего выдыхаемого объема двуокиси углерода при каждом дыхательном цикле. Цель изобретения - повышение точности измерений за счет использования переменного масштаба интегрирования и расширения диапазона вариаций времени усреднения, Для этого в устройство, содержащее интегратор 1, генератор 2, гиперболических импульсов, блок 3 выборки-хранения, ключ 4, блок 5 управления, дополнительно введены цифроаналоговый преобразователь 6 и вычислительный блок 7, а интегратор 1 выполнен многодиапазонным. Устройство имеет сигнальный вход 8 и управляющий-вход 9. Работа устройства поясняется временными диаграммами, приведенными в описании изобретения, где также даны функциональные схемы блока управления, многодиапазонного интегратора и вычислительного блока. 4 з.п. ф-лы, 7 ил. (Л со 4 о ю 00 Фиг,.1

Фиг,. 2

33

c

риг.

J

J5

Щ1)

дм1

(/(s{ ВЫХ..З

it te

. ($

Vynp (7)

и (32} бых.

U(l-5) Вы X.I

ж

f,

и

.. 7

| Справочник по нелинейным схемам./ Под ред | |||

| Д | |||

| Шейнгольда | |||

| М.: Мир, 1977, .с | |||

| Способ получения бензидиновых оснований | 1921 |

|

SU116A1 |

| Способ измерения средних значений нестационарных сигналов | 1980 |

|

SU1073706A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-10-23—Публикация

1985-11-04—Подача