5, регистры 6, 7, 81 11 12, сумматор 10, распределитель И импульсов, введены переключатели 15, 16, токо- граничивающий элемент, выполненный на резисторе }Ь, аналоговое запоминающее устройство 17. Устройство ра- борает по принципу масштабирования разностного сигнала на каждом такте Преобразования с помощью реконфигу- ьируемой цепи обратной связи, состоящей из цифроаналогового преобразователя и операционных масштабирующих

усилителей. Схема устройства позволяет осуществлять сращивание эталонных шкал каждого такта преобразования. Повышение точности устройства достигается путем коррекции напряжения сдвига цепи обратной связи последнего такта преобразования в свободный интервал времени для данной цепи методом периодической компенсации. Использование периодической компенсации цепи обратной связи позволяет в 50 раз снизить погрешность. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1988 |

|

SU1569983A1 |

| Устройство аналого-цифрового преобразования | 1991 |

|

SU1807559A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1320901A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1378061A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ | 1991 |

|

RU2007024C1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Вычислительный преобразовательНАпРяжЕНия B КОд | 1979 |

|

SU822347A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Электроразведочная станция | 1987 |

|

SU1469489A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

Изобретение относится к измерительной технике и может быть использовано в информационно-измерительных системах, гибридных вычислительных комплексах, в системах автоматики, регулирования и контроля. Изобретение позволяет повысить точность. Это достигается тем, что в последовательно-параллельный аналого-цифровой преобразователь, содержащий операционные масштабирующие усилители 1, 2, 3, цифроаналоговые преобразователи 9, 13, переключатель 4, аналого-цифровой преобразователь 5, регистры 6, 7, 8, 11, 12, сумматор 10, распределитель 14 импульсов, введены переключатели 15, 16, токоограничивающий элемент, выполненный на резисторе 19, аналоговое запоминающее устройство 17. Устройство работает по принципу масштабирования разностного сигнала на каждом такте преобразования с помощью реконфигурируемой цепи обратной связи, состоящей из цифроаналогового преобразователя и операционных масштабирующих усилителей. Схема устройства позволяет осуществлять сращивание эталонных шкал каждого такта преобразования. Повышение точности устройства достигается путем коррекции напряжения сдвига цепи обратной связи последнего такта преобразования в свободный интервал времени для данной цепи методом периодической компенсации. Использование периодической компенсации цепи обратной связи позволяет в 50 раз снизить погрешность. 2 ил.

Изобретение относится к измерительой технике и может быть использовано информационно-измерительных систеах, гибридных вычислительных комплеках автоматики, регулирования и контоля.

Цель изобретения - повышение точ- ости преобразователя.

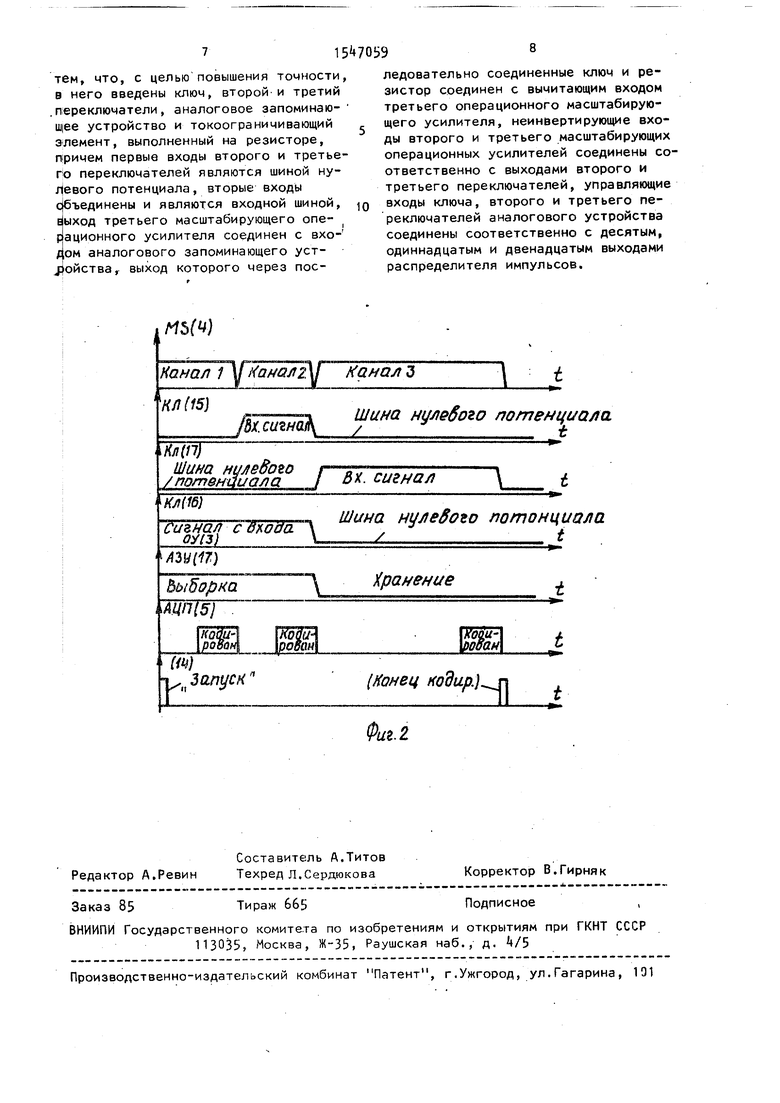

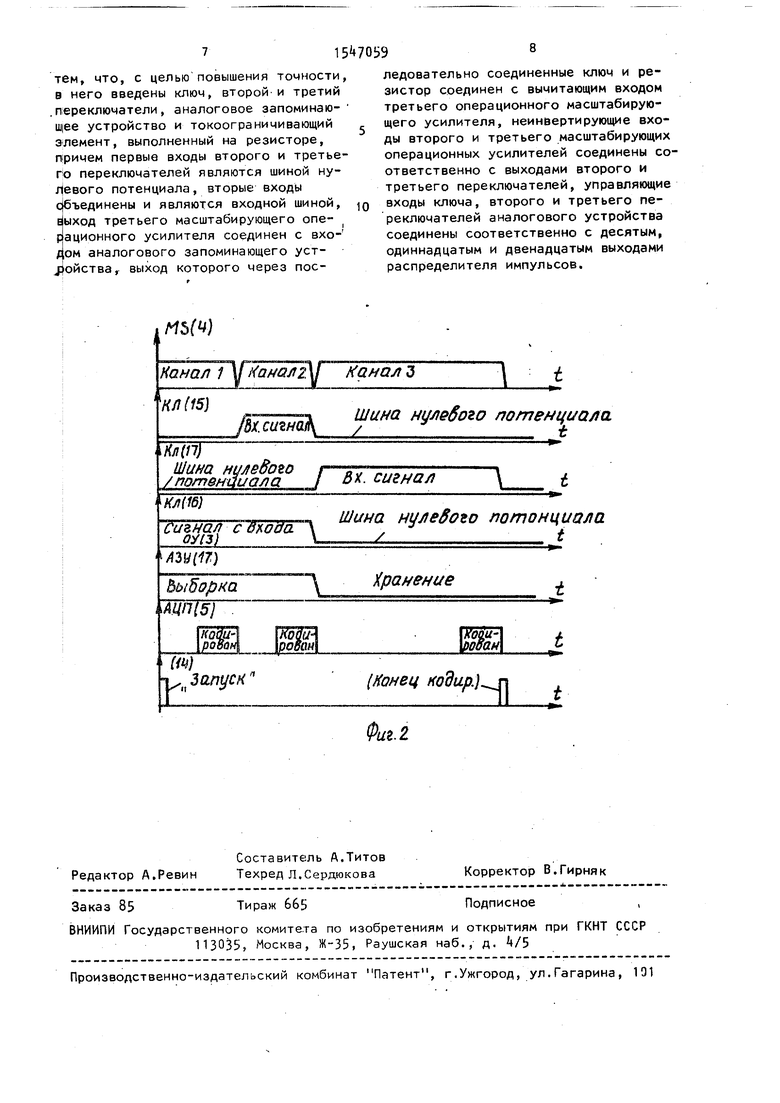

На фиг.1 изображена функциональная схема предлагаемого преобразователя; на фиг.2 - временные диаграммы. Поясняющие работу преобразователя. Преобразователь содержит операционные масштабирующие усилители (ОМУ) 1-3, переключатель k, АЦП 5, регистры 6-8, ЦАП 9, сумматор 10, регистры 11 и 12, ЦАП 13, распреде- Ьчтель 1 импульсов, переключатели 15 и 16, аналоговое запоминающее устройство (АЗУ) 17, ключ 18 и токо- ограничивающий элемент, выполненный На резисторе 19.

Преобразователь работает следующим образом.

Входной аналоговый сигнал через операционный масштабирующий усилитель 1, который работает в режиме Повторителя напряжения, поступает через переключатель k на вход АЦП 5. После выдержки времени для установления переходных процессов с распределителя 14 при наличии сигнала Запуск поступает сигнал запуска с АЦП 5. Результат кодирования заносится в регистр 6, с выхода которого он поступает на первый вход сумматора 10 и вход ЦАП Э. На этом первый такт работы последовательно-параллельного преобразователя завершается. Второй такт работы начинается с переключения переключателя 4 на связь входа АЦП 5 с выходом второго

5

операционного масштабирующего усилителя 2, неинвертирующий вход которого

0 в это же время переключается от шины нулевого потенциала к входной шине. В результате на входе АЦП 5 формируется сигнал, равный разности входного сигнала и аналогового эквивалента

5 результата первого такта кодирования, умноженный на масштабный коэффициент. Заземление входа операционного масштабирующего усилителя 2 на первом такте работы преобразователя

0 исключает перегрузку и насыщение

каскадов усилителя, что-ведет к сокращению времени установления сигнала на его выходе. После установления сигнала на информационном входе АЦП 5 с заданной точностью с распределителя Н вновь дается команда запуска АЦП 5. Результат кодирования заносится в регистр 7. Причем, если масштабный коэффициент операционно0 го масштабирующего усилителя был равен К0, то данные регистра 7 поступают на третий вход сумматора ТО со сдвигом вправо на Р разрядов, при этом должно выполняться условие

5

if 2P

,

а знак результата кодирования второго такта должен распространяться на все старшие разряды входной шины 0 сумматора 10.

Следует отметить, что если разрешающая способность АЦП 5 выше Р, то требования к блокам , 2 и 9 по точности ослабевают, как это было показано выше, и здесь могут быть использованы элементы низкой точности.

С момента записи результата ES регистр 7 заканчивается второй такт ра5

Ооты последовательно-параллельного АЦП и начинается третий такт работы преобразователя. При этом по команде с распределителя И заносится результат двух предыдущих тактов преобразования с выхода сумматора 10 в регистр 11. Переключатель 16 переключает вход операционного масштабирующего усилителя 3 с шины нулевого потенциала к входной шине. Ключ 18 замыкается и подает напряжение коррекции с выхода АЗУ 17 на вычитающий вход операционного масштабирующего усилителя 3. Само АЗУ 17 переводится в режим хранения. Переключатель 16 исключает насыщение каскадом операционного масштабирующего усилителя 3 на предыдущих этапах кодирования и заземляет его вход на это время с целью осуществления коррекции нуля канала обратной связи и формирование разностного сигнала. Выход АЗУ 17 в режиме коррекции отключается ключом 18 от вычитающего входа операционного масштабирующего усилителя 3, что позволяет получить сигнал ошибки, усиленный в К раз, что равносильно снижению собственной погрешности АЗУ в К раз. Процесс выборки напряжения ошибки осуществляется в каждом цикле преобразования во время первого и второго тактов кодирования, f.e. при положении переключателя 16 на замыкание на землю. Роль АЗУ 17 заключается в периодическом переносе сигнала ошибки с выхода усилителя на его вычитающий вход.

Кодирование и формирование выходн го сигнала на третьем такте работы преобразователя осуществляется аналогично второму такту. После завершения кодирования АЦП 5 на третьем такте результат заносится в регистр 8 складывается с результатом двух предыдущих тактов кодирования в сумматоре 10 и окончательно с выхода сумматора заносится в регистр 12.

Так как к цепи обратной связи и формированию разностного сигнала на последнем такте преобразования, как показано выше, предъявляются повы- шенные требования по точности и быстродействию, то в преобразователе предусмотрена реконфигурация этой цепи, которая заключается в использовании на первых двух этапах быстродействующей цепи обратной связи

0

5

низкой точности, а на третьем этапе кодирования используется быстродействующая цепь, точность которой повышается методом периодической коррекции.

Формула изобретения Последовательно-параллельный аналого-цифровой преобразователь, содержащий первый, второй и третий операционные масштабирующие усилители, первый и второй цифроаналоговые преобразователи, первый переключатель, аналого-цифровой преобразователь, первый, второй, третий, четвертый и пятый регистры, сумматор и распределитель импульсов, неинвертирующий вход первого операционного масштабирующего усилителя является входной шиной, выходы первого, второго и третьего операционных масштабирующих усилителей соединены соответственно с первым, вторым и третьим информационными входами первого переключа0

0

5

5

0

5

формационным входом аналого-цифрового преобразователя, выход которого соединен с информационными выходами первого, второго и третьего регистров, выходы последнего из которых соединены с соответствующими входами первого цифроаналогового преобразователя и с первыми входами сумматора, выходы первого и второго регистров соединены соответственно с вторыми и третьими входами сумматора, выход которого соединен с информационными входами четвертого и пятого регистров, выходы последнего из которых являются выходной шиной, выходы четвертого регистра соединены с соответствующими входами второго цифроаналогового преобразователя, выходы первого и второго цифроаналоговых преобразователей соединены соответственно с вычитающими входами второго и третьего операционных масштабирующих усилителей, первый, второй, третий, четвертый, пятый, шестой и седьмой выходы распределителя импульсов соединены соответственно с управляющими входами первого переключателя, аналого-цифрового преобразователя, первого, второго, третьего, четвертого и пятого регистров, восьмой выход распределителя импульсов является шиной Конец кодирования, а вход является шиной Запуск, отличающийся

тем, что, с целью повышения точности, в него введены ключ, второй-и третий .переключатели, аналоговое запоминаю- Ш|ее устройство и токоограничивающий элемент, выполненный на резисторе, причем первые входы второго и третьего переключателей являются шиной ну- л евого потенциала, вторые входы объединены и являются входной шиной, выход третьего масштабирующего one- ( рационного усилителя соединен с вхо- Јрм аналогового запоминающего устройства, выход которого через посMSM

Редактор А.Ревин

Составитель А.Титов Техред Л.Сердюкова

Заказ 85

Тираж 665

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. V5

ледовательно соединенные ключ и резистор соединен с вычитающим входом третьего операционного масштабирующего усилителя, неинвертирующие входы второго и третьего масштабирующих операционных усилителей соединены соответственно с выходами второго и третьего переключателей, управляющие входы ключа, второго и третьего переключателей аналогового устройства соединены соответственно с десятым, одиннадцатым и двенадцатым выходами распределителя импульсов.

Корректор В.Гирняк

Подписное

| Аналого-цифровой преобразователь | 1979 |

|

SU839046A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Бородянский М.Е., Моравский Е.И | |||

| Многоканальный аналого-цифровой преобразователь в системах вектор - -канак | |||

| - Приборы и техника эксперимента, 1986, V 2, с | |||

| Способ размножения копий рисунков, текста и т.п. | 1921 |

|

SU89A1 |

| АН fix () ПОСЛЕДОВАТЕЛЬНО-ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | |||

Авторы

Даты

1990-02-28—Публикация

1987-07-08—Подача