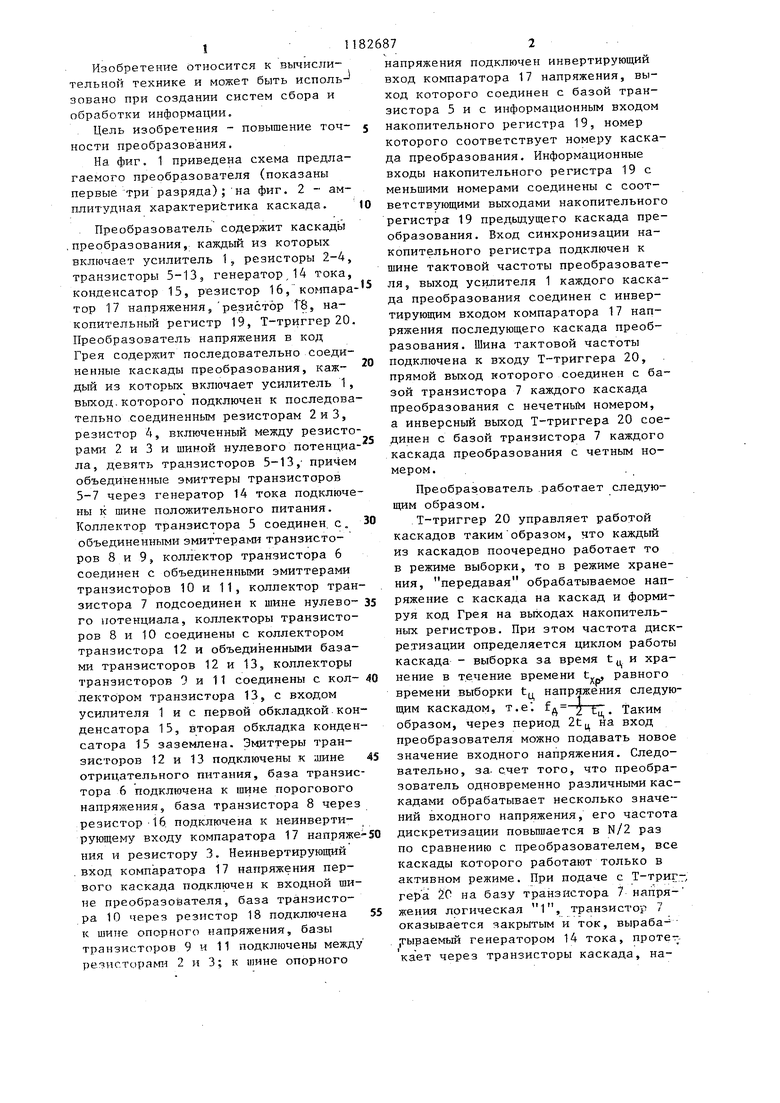

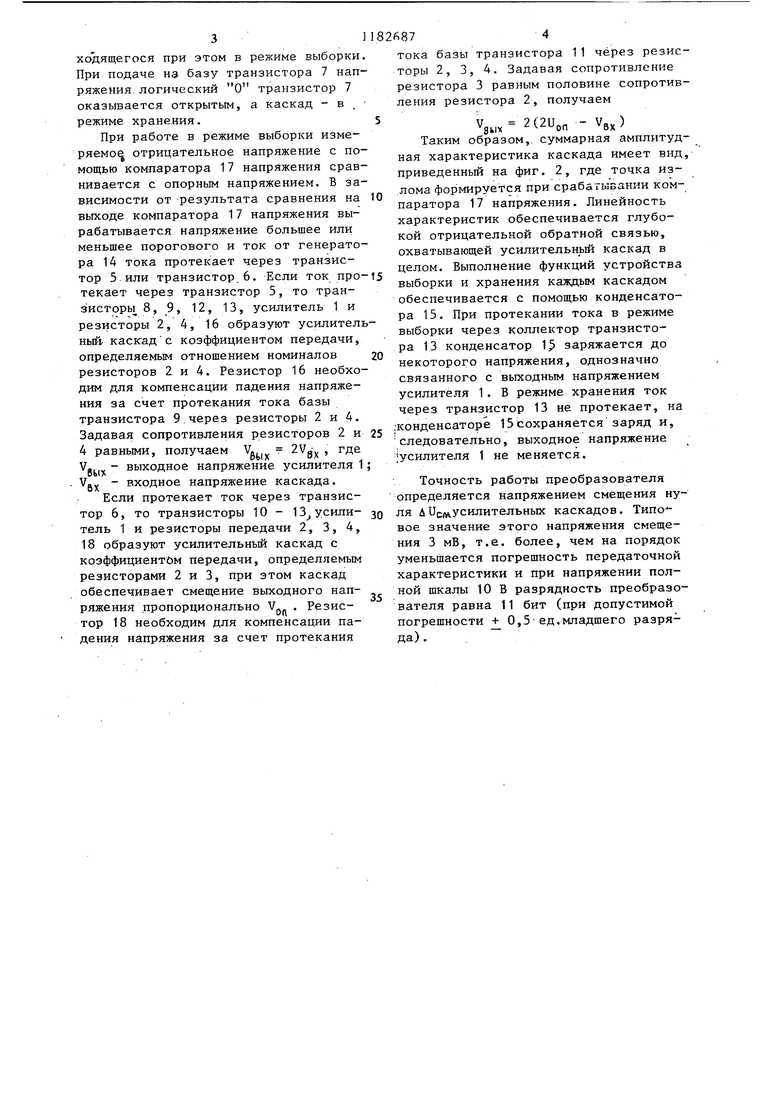

1 1 Изобретение относится к вычислительной технике и может быть исполь зовано при создании систем сбора и обработки информации. Цель изобретения повышение точности преобразования. На фиг. 1 приведена схема предлагаемого преобразователя (показаны первые три разряда);на фиг. 2 - амплитудная характериЬтика каскада. Преобразователь содержит каскады .преобразования, каждый из которых включает усилитель 1, резисторы 2-4, транзисторы 5-13, генератор,14 тока, конденсатор 15, резистор 16, компара тор 17 напряжения,резистор 18, накопительный регистр 19, Т-триггер 20 Преобразователь напряжения в код Грея содержит последовательно соединенные каскады преобразования, каждый из которых включает усилитель 1, выход.которого подключен к последова тельно соединенным резисторам 2 и 3, резистор 4, включенный между резисто рами 2 и 3 и шиной нулевого потенциа ла, девять транзисторов 5-13,- причем объединенные эмиттеры транзисторов 5-7 через генератор 14 тока подключе ны к шине положительного питания. Коллектор транзистора 5 соединен, с. объединенными эмиттерами транзисторов 8 и 9, коллектор транзистора 6 соединен с объединенными эмиттерами транзисторов 10 и 11, коллектор тран зистора 7 подсоединен к шине нулевого потенциала, коллекторы транзисторов 8 и 10 соединены с коллектором транзистора 12 и объединенными базами транзисторов 12 и 13, коллекторы транзисторов 9 и 11 соединены с коллектором транзистора 13, с входом усилителя 1 и с первой обкладкой кон денсатора 15, вторая обкладка конден сатора 15 заземлена. Эмиттеры транзисторов 12 и 13 подключены к ;иине отрицательного питания, база транзис тора 6 подключена к гаине порогового напряжения, база транзистора 8 через резистор-16 подключена к неинвертирующему входу компаратора 17 напряже ния и резистору 3. Неинвертирующий вход компаратора 17 напряжения первого каскада подключен к входной шине преобразователя, база транзистора 10 через резистор 18 подключена к шине опорного напряжения, базы транзисторов 9 и 11 подключены между ре.янсторами 2 и 3; к шине опорного 872 напряжения подключен инвертирующий вход компаратора 17 напряжения, выход которого соединен с базой транзистора 5 и с информационным входом накопительного регистра 19, номер которого соответствует номеру каскада преобразования. Информационные входы накопительного регистра 19 с меньшими номерами соединены с соответствующими выходами накопительного регистра- 19 предьщущего каскада преобразования. Вход синхронизации накопительного регистра подключен к шине тактовой частоты преобразователя, выход усишителя 1 каждого каскада преобразования соединен с инвертирующим входом компаратора 17 напряжения последующего каскада преобразования. Шина тактовой частоты подключена к входу Т-триггера 20, прямой выход которого соединен с базой транзистора 7 каждого каскада преобразования с нечетным номером, а инверсный выход Т-триггера 20 соединен с базой транзистора 7 каждого каскада преобразования с четным номером. Преобразователь работает следующим образом. Т-триггер 20 управляет работой каскадов такимобразом, что каждый из каскадов поочередно работает то в режиме выборки, то в режиме хранения, передавая обрабатываемое напряжение с каскада на каскад и формируя код Грея на выходах накопительных регистров. При этом частота дискретизации определяется циклом работы каскада - выборка за время t. и хранение в течение времени t,, равного времени выборки t напряжения следующим каскадом, т.е . ff,. Таким образом, через период 2t на вход преобразователя можно подавать новое значение входного напряжения. Следовательно, за. счет того, что преобразователь одновременно различными каскадами обрабатывает несколько значений входного напряжения, его частота дискретизации повьпиается в N/2 раз по сравнению с преобразователем, все каскады которого работают только в активном режиме. При подаче с Т-триг-, гера 20 на базу транзистора 7 напряженил логическая 1, транзисто-р 7 оказывается закрытым и ток, выраба;гыраемый генератором 14 тока, проте-кает через транзисторы каскада, находящегося при этом в режиме выборки При подаче нз базу транзистора 7 нап ряжения логический О транзистор 7 оказывается открытым, а каскад - в . режиме хранения. При работе в режиме выборки измеряемо отрицательное напряжение с по мощью компаратора 17 напряжения срав нивается с опорным напряжением. В за висимости от результата сравнения на выходе компаратора 17 напряжения вырабатывается напряжение большее или меньшее порогового и ток от генератора 14 тока протекает через транзистор 5 или транзистор 6. Если ток протекает через транзистор 5, то транзисторы 8,9, 12, 13, усилитель 1 и резисторы 2, 4, 16 образуют усилитель ный каскад с козффициентом передачи, определяемым отношением номиналов резисторов 2 и 4. Резистор 16 необходим для компенсации падения напряжения за счет протекания тока базы транзистора 9.через резисторы 2 и 4. Задавая сопротивления резисторов 2 и 4 равными, получаем V 2Vgj( , где Вых выходное напряжение усилителя 1 Vg - входное напряжение каскада. Если протекает ток через транзистор 6, то транзисторы 10 - 13 усилитель 1 и резисторы передачи 2, 3, 4, 18 образуют усилительньй каскад с коэффициентйм передачи, определяемым резисторами 2 и 3, при этом каскад обеспечивает смещение выходного напряжения пропорционально V.J . Резистор 18 необходим для компенсации падения напряжения за счет протекания тока базы транзистора 11 через резисторы 2, 3, 4. Задавая сопротивление резистора 3 равным половине сопротивления резистора 2, получаем Vx 2(2U,n VB,) Таким образом,, суммарная амплитудная характеристика каскада имеет вид, приведенный на фиг. 2, где точка излома формируется при срабатывании компаратора 17 напряжения. Линейность характеристик обеспечивается глубокой отрицательной обратной связью, охватывающей усилительньш каскад в целом. Выполнение функций устройства выборки и хранения каждьм каскадом обеспечивается с помощью конденсатора 15. При протекании тока в режиме выборки через коллектор транзистора 13 конденсатор 1 заряжается до некоторого напряжения, однозначно связанного с выходным напряжением усилителя 1. В режиме хранения ток через транзистор 13 не протекает, на конденсаторе 15сохраняется заряд и, следовательно, выходное напряжение усилителя 1 не меняется. Точность работы преобразователя определяется напряжением смещения нуя А Псмусилительных каскадов. значение этого напряжения смещения 3 мВ, т.е. более, чем на порядок меньшается погрешность передаточной арактеристики и при напряжении полной шкалы 10 В разрядность преобразователя равна 11 бит (при допустимой огрешности + 0,5-ед.младшего разряа) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для хранения и выборкииНфОРМАции | 1979 |

|

SU841058A1 |

| Устройство для хранения и выборки информации | 1981 |

|

SU982096A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU780048A1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1152040A1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ АППАРАТОВ ТОКОВОЙ ЗАЩИТЫ | 1990 |

|

RU2024888C1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1104587A1 |

ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД ГРЕЯ, содержащий последовательно соединенные каскады преобразования, каждый из которых вьтолнен на усилителе, выход которого соединен с первым выводом первого резистора, второй вывод которого через второй резистор соединен с входной шиной, а через третий резистор - с шиной нулевого потенциала, первый вывод четвертого резистора соединен с шиной опорного напряжения, пятый резистор , первый транзистор, о т л и ч а ю- щийся тем, что, с целью повышения точности преобразования, в него введен Т-триггер, а в каждый из каскадов преобразования введены генератор тока, компаратор напряжения, конденсатор, накопительный регистр, восемь транзисторов, при этом эмиттеры первого, второго и третьего транзисторов объединены и через генератор тока соединены с шиной питания положительной полярности, коллектор первого транзистора соединен с шиной нулевого потенциала, коллектор второго транзистора соединен с эмиттерами четвертого и пятого транзисторов, коллектор третьего транзистора соединен с эмиттерами шестого и седьмого транзисторов, база третьего транзистора соединена с шиной порогового напряжения, база четвертого транзистора через пятый резистор соединена с первым входом компаратора напряжения и является входом каскада, база пятого транзистора объединена с базой седьмого транзистора и соединена с вторым выводом первого резистора, коллектор четвертого транзистора объединен с коллекторами шестого и восьмого транзисторов и соединен с. базами восьмого и девятого транзисторов, эмиттеры которых объединены и соединены с шиной питания отрицательной полярности, коллектор пятого @ транзистора объединен с коллекторасл ми седьмого и девятого транзисторов и соединен с входом усилителя и первой обкладкой конденсатора, вторая обкладка которого соединена с шиной нулевого потенциала, база шестого транзистора соединена с вторьм выводом четвертого резистора, второй сх вход компаратора напряжения соединеу to с шиной порогового напряжения, а выО) ход - с базой второго транзистора и 00 соответствующим информационным вхо дом накопительного регистра, выход которого соединен с соответствующим информационным входом накопительного регистра последующего каскада, а вход синхронизации объединен с входами синхронизации накопительных регистров всех каскадов, входом Т-триггера и соединен с шиной тактовой частоты, прямой выход Т-триггера соединен с базами первых транзисторов нечетных каскадов, а инверсный выход - с базами первьгх транзисторов . четных каскадов.

| Патент США № 3577135, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Запальная свеча для двигателей | 1924 |

|

SU1967A1 |

| Преобразователь напряжения в код Грея | 1982 |

|

SU1018233A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-09-30—Публикация

1984-04-20—Подача