1

Изобретение относится к области вычислительной и информационно-изме- Ьителышй техники и может быть использовано в автоматизированных системах сбора и обработки данных с интерферометров термоядерных установок

Цель изобретения - расширение частотного диапазона и новышение информативности.

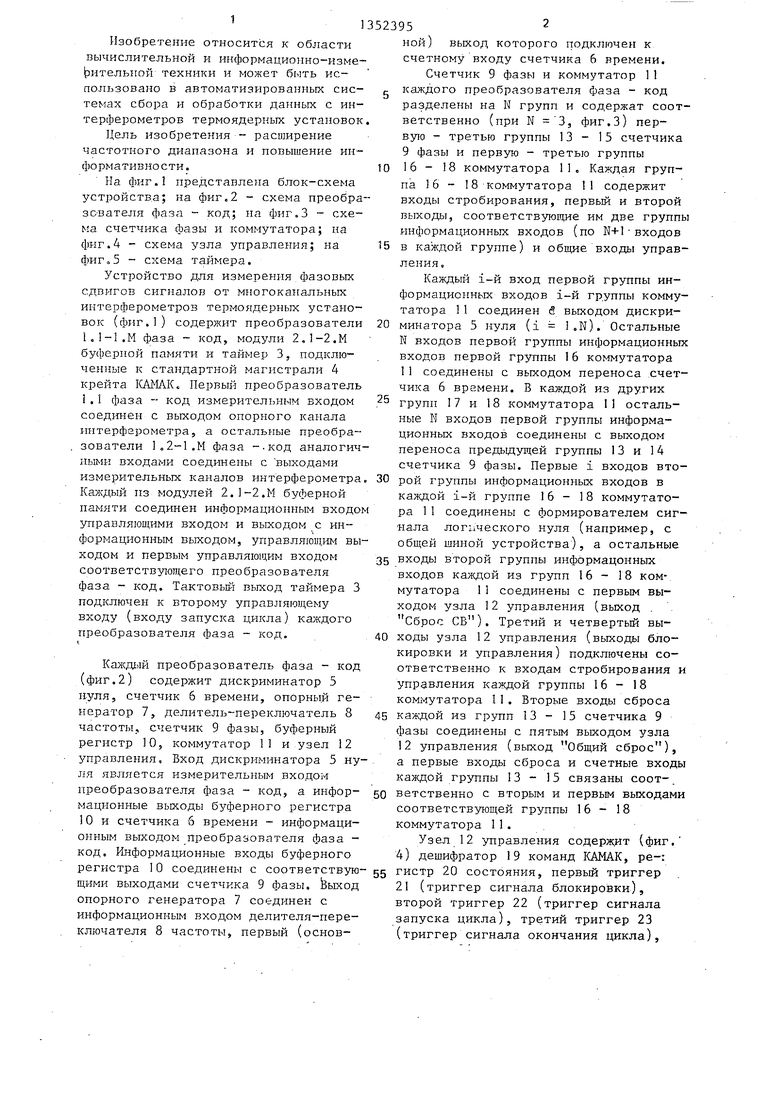

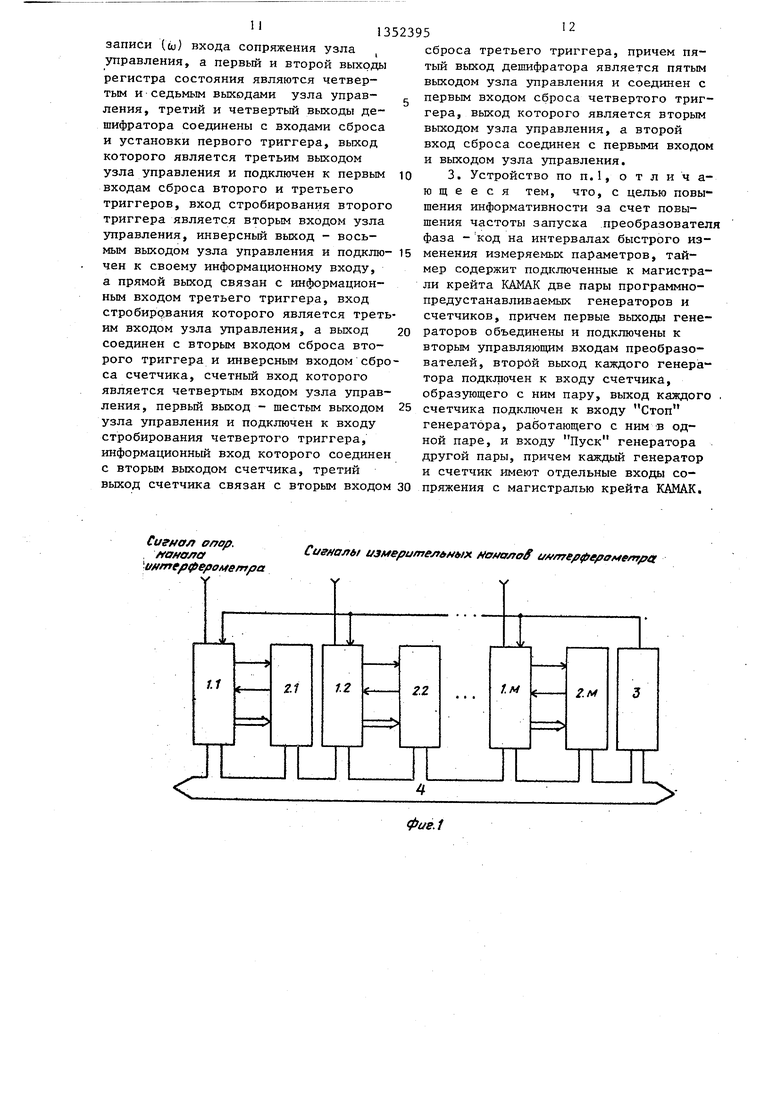

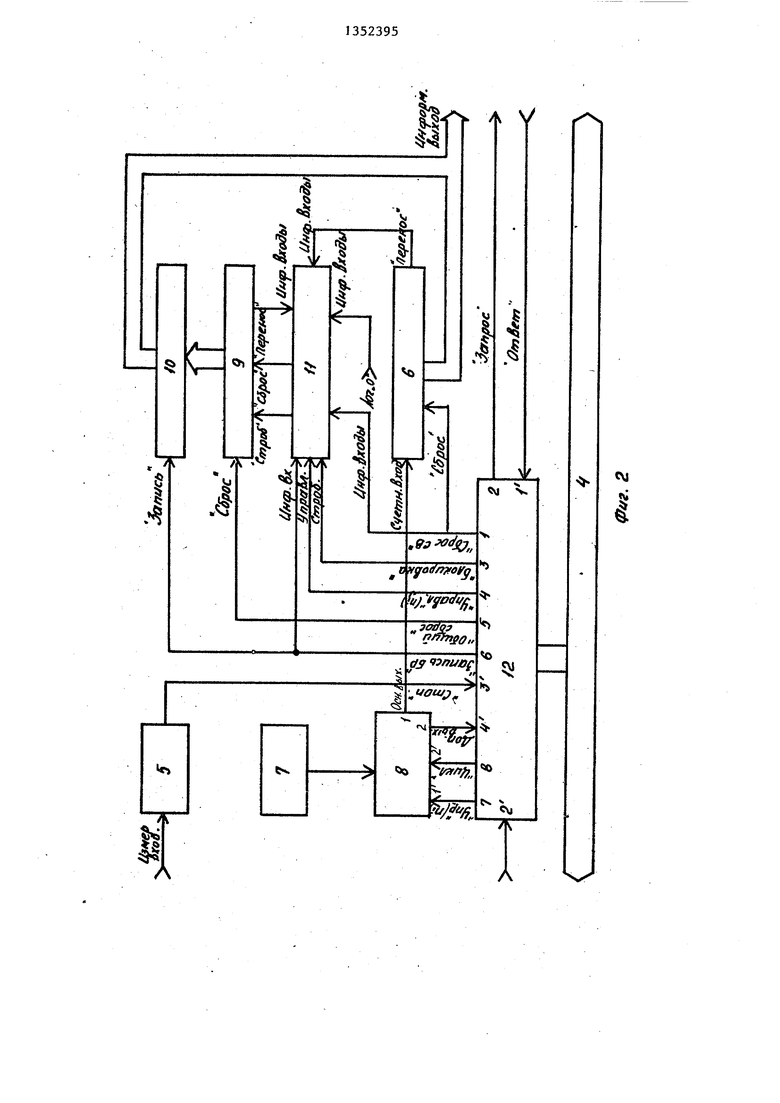

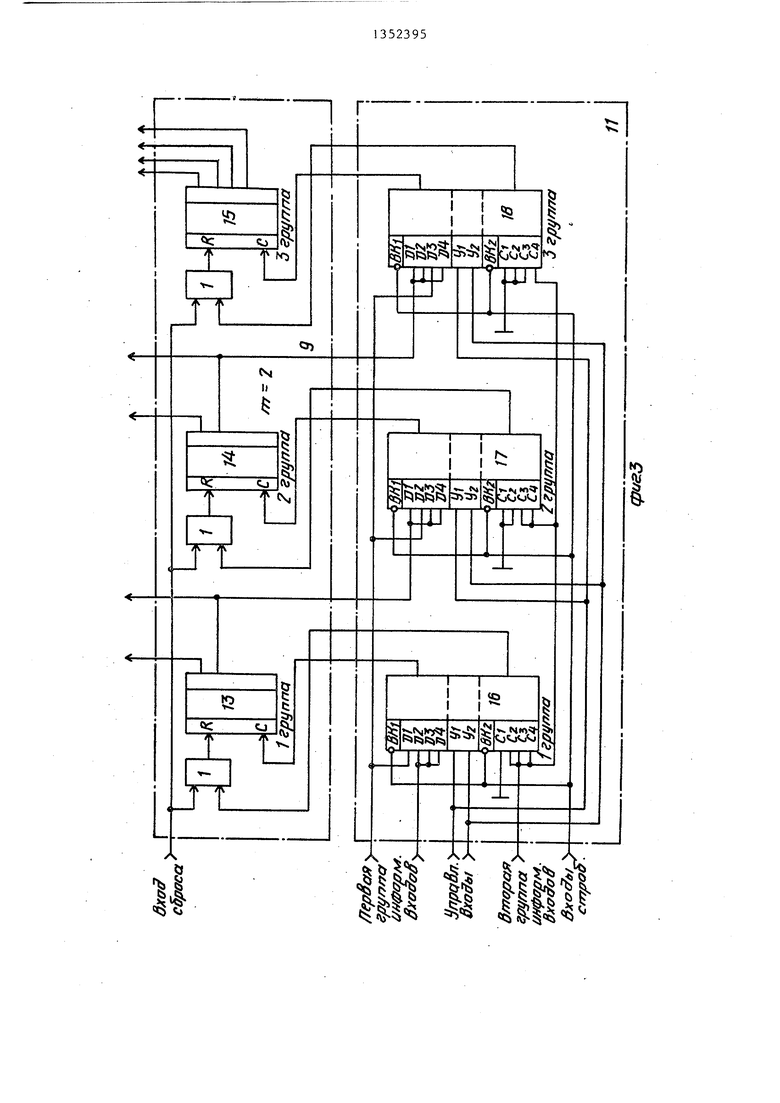

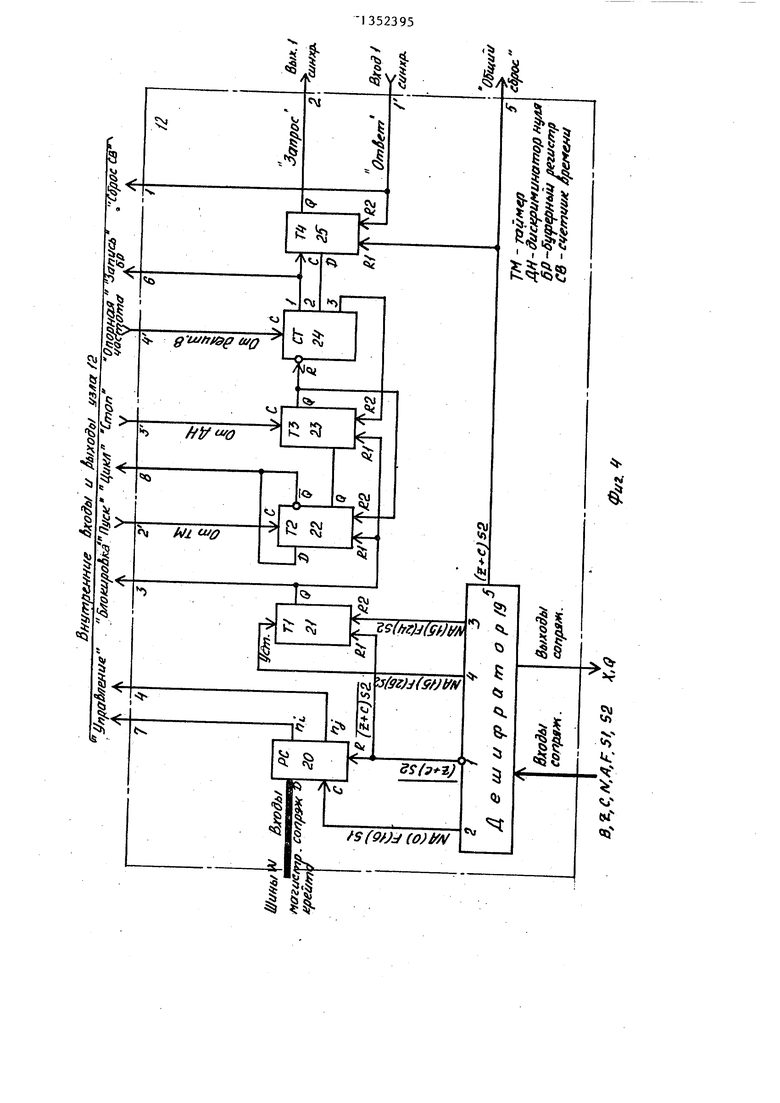

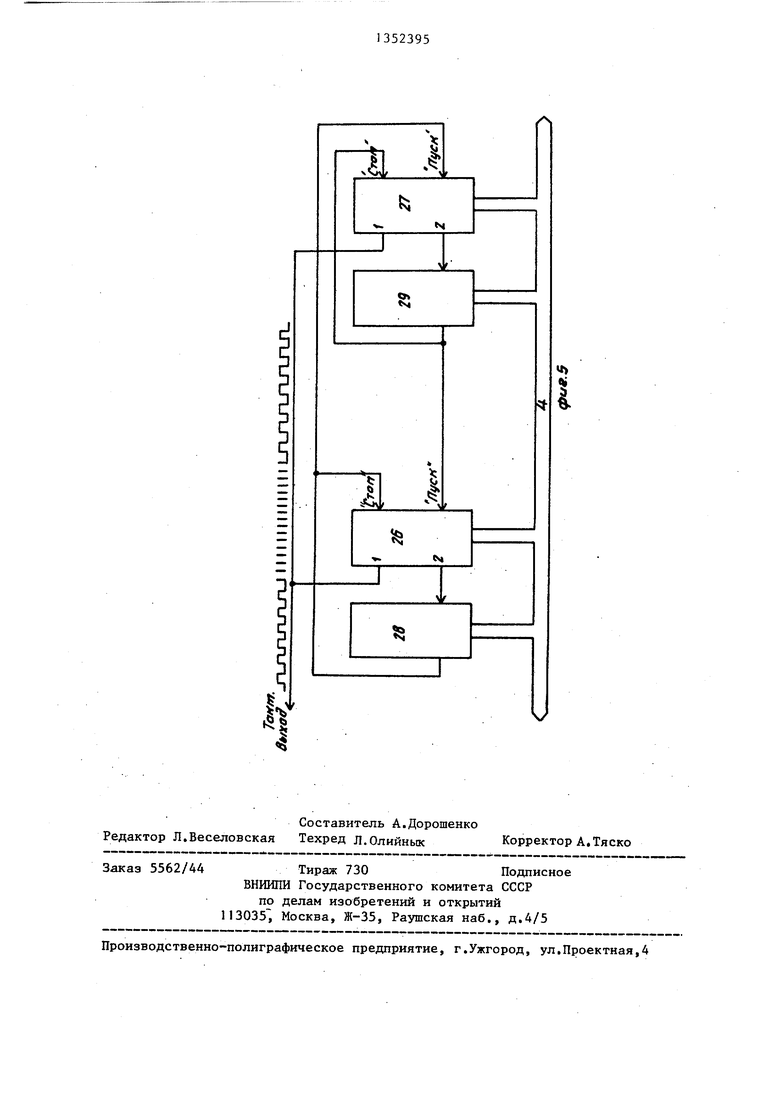

На фиг.1 нредставлена блок-схема устройств.а; на фиг.2 - схема преобра зо-вателя фаза - код; на фиг.З - схе- a счетчика фазы и коммутатора; на фиг.4 - схема узла управления; на фиг о 5 - схема таймера.

Устройство для измерения фазовых сдвигов сигналов от мггогоканальных интерферометров термоядерных установок (фиг.1) содержит преобразователи 20 минатора 5 нуля (i I.N). Остальные

1.1-1.М фаза - код, модули 2,1-2.М буферной памяти и таймер 3, подключенные к стандартной магистрали 4 крейта КАМАКс Первый преобразователь .1 фаза код измерительным входом соедга-ген с выходом опорного канала интерферометра, а остальные преобразователи 1.2-1.М фаза -.код аналогичными входами соединены с выходами

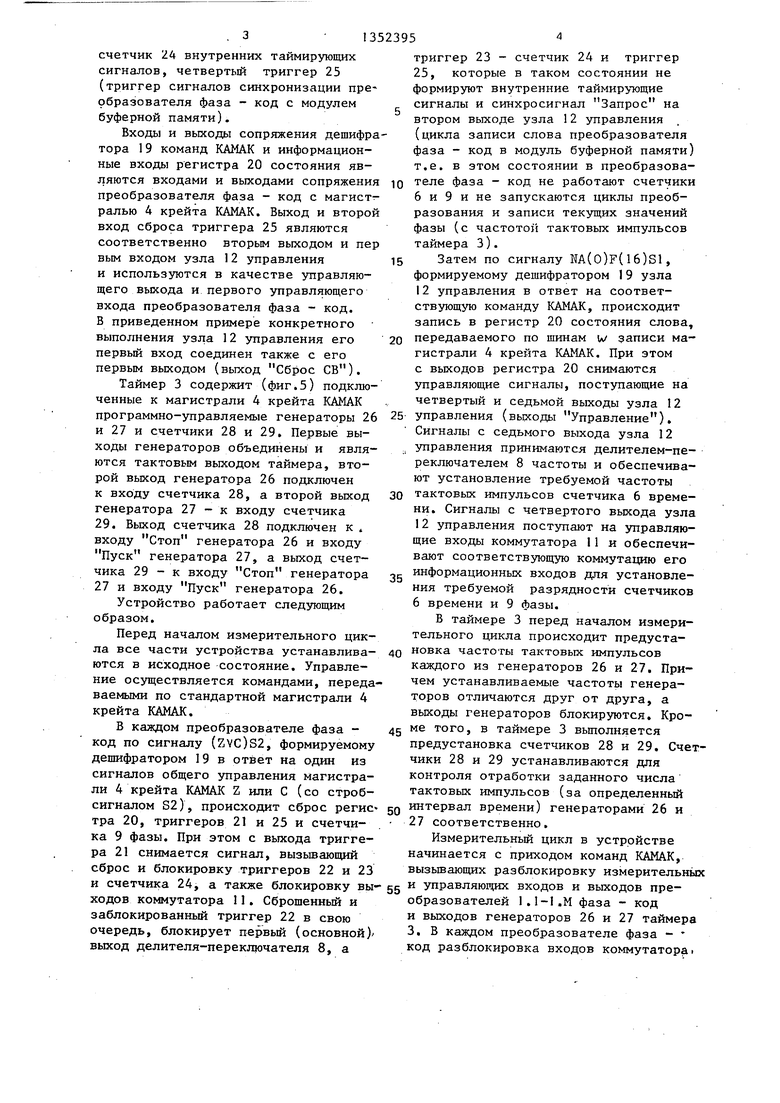

N входов первой группы информационных входов нервой группы 16 коммутатора 11 соединены с выходом переноса .счетчика 6 времени. В каждой из других .2 групп 17 и 18 коммутатора I остальные N входов первой группы информационных входов соединены с выходом переноса предьщущей группы 13 и 14 счетчика 9 фазы. Первые i входов вто- измерительных каналов интерферометра. 30 рой группы информационных входов в Каждый из модулей 2.1-2.М буферной каждой i-й группе 16-18 коммутатора 1 1 соединены с формирователем сигнала логического нуля (например, с общей шиной устройства), а остальные 35 входы второй группы информацонных входов каждой из групп 16 - 18 ком-, мутатора 1I соединены с первым выходом узла 12 управления (выход . Сброс СВ). Третий и четвертый вы- 40 ходы узла 12 управления (выходы блокировки и управления) подключены со- Калсд1 ш преобразователь фаза - код (фиг.2) содержит дискриминатор 3 нуля, счетчик 6 времени, опорный генератор 7, делитель-переключатель 8 частоты., счетчик 9 фазы, буферный регистр 10, коммутатор 11 и узел 12 управления. Вход дискриминатора 5 ну-, ля является измерительным входом

50

памяти соединен информационным входом управляющими входом и выходом с информационным выходом, управляющим выходом и первым управляюпдим входом соответствующего преобразователя фаза - код. Тактовый выход таймера 3 подключен к второму управляющему входу (входу запуска цикла) каждого преобразователя фаза - код.

ответственно к входам стробирования и управления каждой группы 16 - 18 коммутатора II. Вторые входы сброса 45 каждой из групп 13 - 15 счетчика 9 фазы соединены с пятым выходом узла 12 управления (выход Общий сброс), а первые входы сброса и счетные входы каждой группы 13-15 связаны соот-. ветственно с вторым и первым выходами соответствующей группы 16 - 18 коммутатора 11.

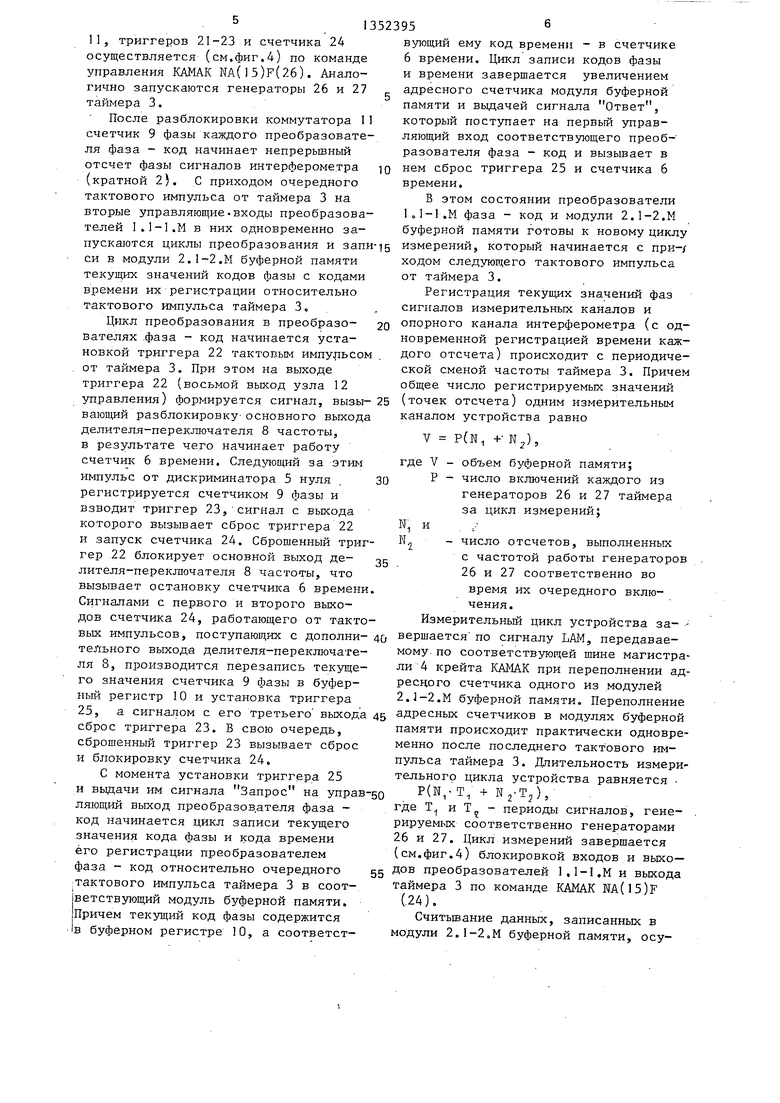

Узел 12 управления содерж,ит (фиг. 4) дешифратор 19 команд КАМАК, ре-:

преобразователя фаза - код, а информационные выходы буферного регистра 10 и счетчика 6 времени - информационным выходом преобразователя фаза - код. Информационные входы буферного регистра 10 соединены с соответствую- 55 гистр 20 состояния, первый триггер щими выходами счетчика 9 фазы. Выход 21 (триггер сигнала блокировки), опорного генератора 7 соединен с второй триггер 22 (триггер сигнала информационным входом делителя-пере- запуска цикла), третий триггер 23 ключателя 8 частоты, первый (основ- (триггер сигнала окончания цикла).

52395

ной

выход которого подключен к счетному входу счетчика 6 времени. Счетчик 9 фазы и коммутатор 11

с каждого нреобразователя фаза - код разделены на N групп и содержат соответственно (при N 3, фиг.З) первую - третью группы 13-15 счетчика 9 фазы и первую - третью группы

10 16 - 18 коммутатора 11, Каждая группа 16 - 18 коммутатора 11 содержит входы стробирования, первый и второй выходы, соответствующие им две группы информационных входов (по N+1входов

15 в каждой группе) и общие входы управления.

Каждый i-й вход первой группы информационных входов i-й группы коммутатора 11 соединен & выходом дискриN входов первой группы информационных входов нервой группы 16 коммутатора 11 соединены с выходом переноса .счетчика 6 времени. В каждой из других групп 17 и 18 коммутатора I остальные N входов первой группы информационных входов соединены с выходом переноса предьщущей группы 13 и 14 счетчика 9 фазы. Первые i входов вто- 0 рой группы информационных входов в каждой i-й группе 16-18 коммутатора 1 1 соединены с формирователем сигнала логического нуля (например, с общей шиной устройства), а остальные 5 входы второй группы информацонных входов каждой из групп 16 - 18 ком-, мутатора 1I соединены с первым выходом узла 12 управления (выход . Сброс СВ). Третий и четвертый вы- 0 ходы узла 12 управления (выходы блокировки и управления) подключены со-

0

ответственно к входам стробирования и управления каждой группы 16 - 18 коммутатора II. Вторые входы сброса 5 каждой из групп 13 - 15 счетчика 9 фазы соединены с пятым выходом узла 12 управления (выход Общий сброс), а первые входы сброса и счетные входы каждой группы 13-15 связаны соот-. ветственно с вторым и первым выходами соответствующей группы 16 - 18 коммутатора 11.

Узел 12 управления содерж,ит (фиг. 4) дешифратор 19 команд КАМАК, ре-:

5 гистр 20 состояния, первый триггер 21 (триггер сигнала блокировки), второй триггер 22 (триггер сигнала запуска цикла), третий триггер 23 (триггер сигнала окончания цикла).

счетчик 24 внутренних таймирующих сигналов, четвертый триггер 25 (триггер сигналов синхронизации преобразователя фаза - код с модулем буферной памяти).

Входы и выходы сопряжения дешифратора 19 команд КАМАК и информационные входы регистра 20 состояния являются входами и выходами сопряжения преобразователя фаза - код с магистралью 4 крейта КАМАК. Выход и второй вход сброса триггера 25 являются соответственно вторым выходом и пер вым входом узла 12 управления и используются в качестве управляющего выхода и первого управляющего входа преобразователя фаза - код. В приведенном примере конкретного выполнения узла 12 управления его первый вход соединен также с его первым выходом (выход Сброс СВ).

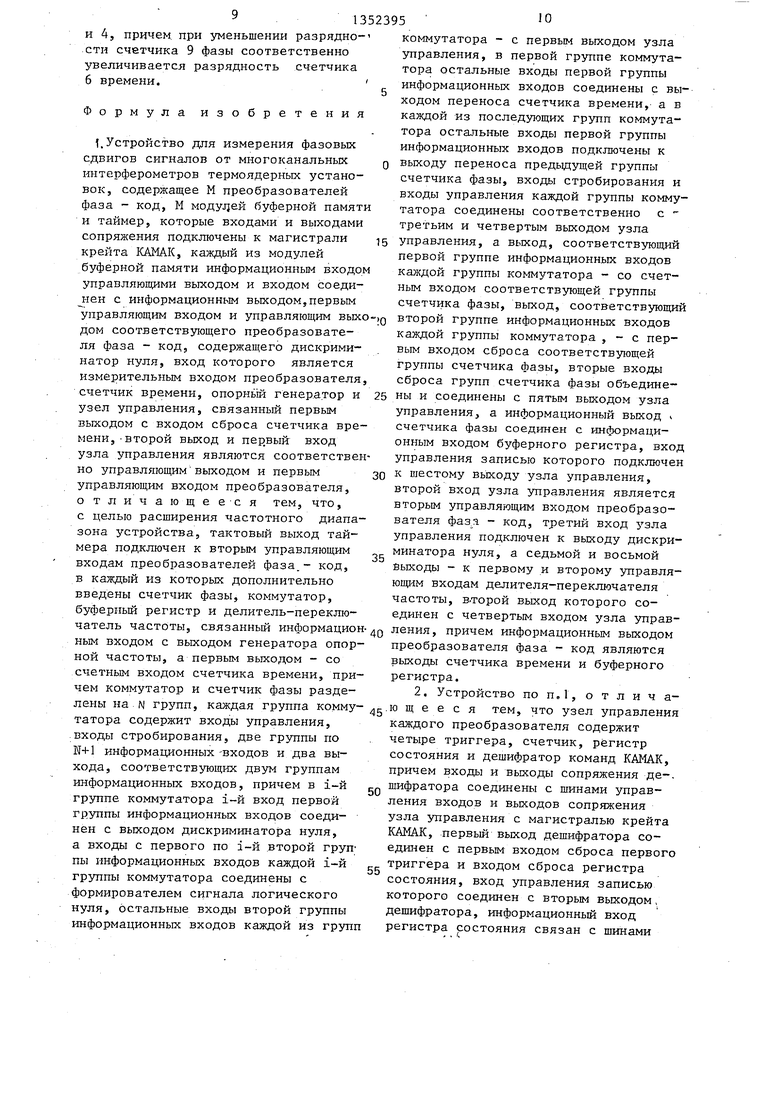

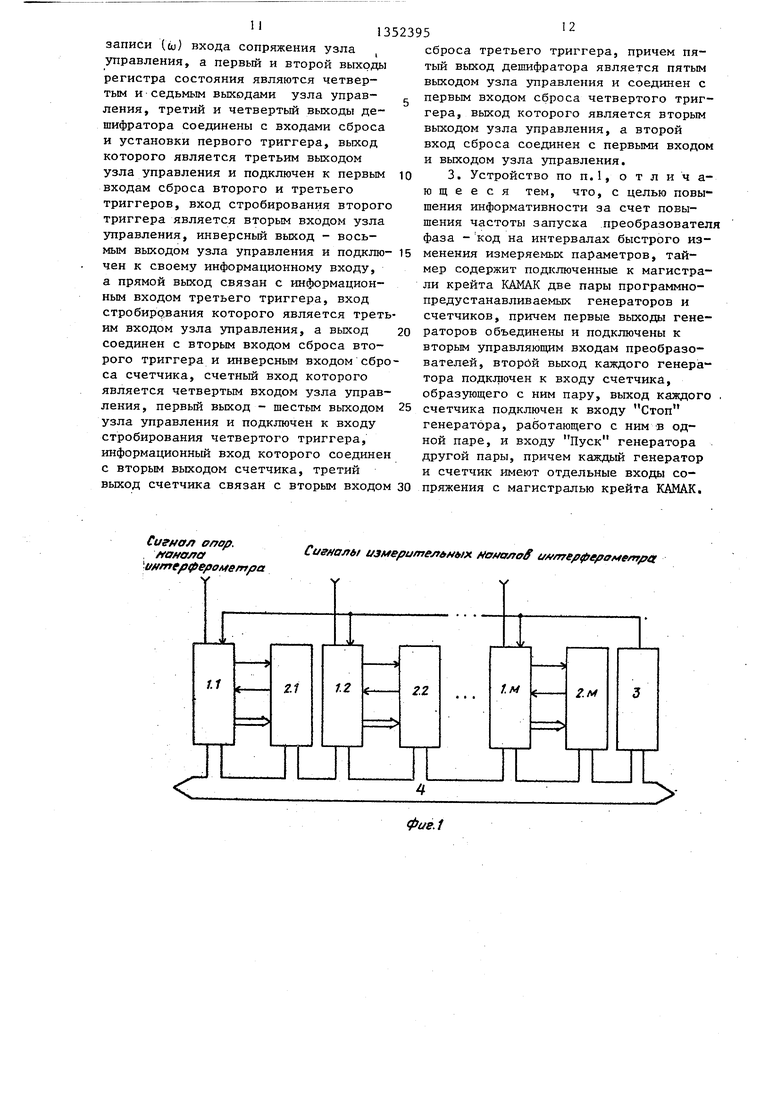

Таймер 3 содержит (фиг.5) подключенные к магистрали 4 крейта КАМАК программно-управляемые генераторы 26 и 27 и счетчики 28 и 29. Первые выходы генераторов объединены и являются тактовым выходом таймера, второй выход генератора 26 подключен к входу счетчика 28, а второй выход генератора 27 - к входу счетчика 29. Выход счетчика 28 подключен к . входу Стоп генератора 26 и входу Пуск генератора 27, а выход счетчика 29 - к входу Стоп генератора 27 и входу Пуск генератора 26.

Устройство работает следующим образом.

Перед началом измерительного цикла все части устройства устанавливаются в исходное состояние. Управление осуществляется командами, передаваемыми по стандартной магистрали 4 крейта КАМАК.

В калсдом преобразователе фаза - код по сигналу (ZYC)S2, формируемому дешифратором I9 в ответ на один из сигналов общего управления магистрали 4 крейта КАМАК Z или С (со строб- сигналом S2), происходит сброс регистра 20, триггеров 21 и 25 и счетчика 9 фазы. При этом с выхода триггера 21 снимается сигнал, вызьшающий сброс и блокировку триггеров 22 и 23

и счетчика 24, а также блокировку вы- 55 управляющих входов и выходов пре- ходов коммутатора 11. Сброшенный и образователей 1.I-I.M фаза - код заблокированный триггер 22 в свою выходов генераторов 26 и 27 таймера очередь, блокирует первый (основной)/ 3. В каждом преобразователе фаза - - выход делителя-переключателя 8, а код разблокировка входов коммутатору.

10

15

20

2395

триггер 23 - счетчик 24 и триггер 25, которые в таком состоянии не формируют внутренние таймирующие сигналы и синхросигнал Запрос на втором выходе узла 12 управления . (цикла записи слова преобразователя фаза - код в модуль буферной памяти) т.е. в этом состоянии в преобразователе фаза - код не работают счетчики 6 и 9 и не запускаются циклы преобразования и записи текущих значений фазы (с частотой тактовых импульсов таймера 3).

Затем по сигналу М(0)Г( 16)81, формируемому дешифратором 19 узла 12 управления в ответ на соответствующую команду КАМАК, происходит запись в регистр 20 состояния слова, передаваемого по шинам w записи магистрали 4 крейта КАМАК. При этом с выходов регистра 20 снимаются управляющие сигналы, поступающие на четвертый и седьмой выходы узла 12 25 управления (вькоды Управление). Сигналы с седьмого выхода узла 12 управления принимаются делителем-переключателем 8 частоты и обеспечивают установление требуемой частоты тактовых импульсов счетчика 6 времени. Сигналы с четвертого выхода узла 12 управления поступают на управляющие входы коммутатора 11 и обеспечивают соответствующзто коммутацию его информационных входов для установления требуемой разрядности счетчиков 6 времени и 9 фазы.

Б таймере 3 перед началом измерительного цикла происходит предустановка частоты тактовых импульсов каждого из генераторов 26 и 27. Причем устанавливаемые частоты генераторов отличаются друг от друга, а выходы генераторов блокируются. Кроме того, в таймере 3 выполняется предустановка счетчиков 28 и 29. Счетчики 28 и 29 устанавливаются для контроля отработки заданного числа тактовых импульсов (за определенный интервал времени) генераторами 26 и 27 соответственно.

Измерительный цикл в устройстве начинается с приходом команд КАМАК, вызьтающих разблокировку измерительных

30

35

40

45

50

11, триггеров 21-23 и счетчика 24 осуществляется (см.фиг,4) по команде управления КАМАК NA(15)F(26). Аналогично запускаются генераторы 26 и 27 таймера 3.

После разблокировки коммутатора I1 счетчик 9 фазы каждого преобразователя фаза - код начинает непрерьшньй отсчет фазы сигналов интерферометра (кратной 2). С приходом очередного тактового импульса от таймера 3 на вторые управляющие-входы преобразователей 1.1-1.М в них одновременно запускаются циклы преобразования и запи- з измерений, который начинается с при-/

си в модули 2,1-2,М буферной памяти текущих значений кодов фазы с кодами времени их регистрации относительно тактового импульса таймера 3,

Цикл преобразования в преобразователях .фаза - код начинается установкой триггера 22 тактовым импульсом от таймера 3. При этом на выходе триггера 22 (восьмой выход узла 12

20

ходом следующего тактового импульса от таймера 3,

Регистрация текущих значений фаз сигналов измерительных каналов и опорного канала интерферометра (с од новременной регистрацией времени каж дого отсчета) происходит с периодиче ской сменой частоты таймера 3, Приче общее число регистрируемых значений

управления) формируется сигнал, вызы- 25 (точек отсчета) одним измерительным

вающий разблокировку основного выхода делителя-переключателя 8 частоты, в результате чего начинает работу счетчик 6 времени, Следутощий за этим импульс от дискриминатора 5 нуля регистрируется счетчиком 9 фазы и взводит триггер 23, сигнал с выхода которого вызывает сброс триггера 22 и запуск счетчика 24, Сброшенный триггер 22 блокирует основной выход де- лителя-переключателя 8 частоты, что вызывает остановку счетчика 6 времени Сигналами с первого и второго выходов счетчика 24, работающего от т-акто вых импульсов, поступающих с дополни- тельного выхода делителя-переключателя 8, производится перезапись текущего значения счетчика 9 фазы в буфер- ньш регистр 10 и установка триггера

25, а сигналом с его третьего выхода 45 адресных счетчиков в модулях буферной

сброс триггера 23, В свою очередь, сброшенный триггер 23 вызывает сброс и блокировку счетчика 24,

С момента установки триггера 25 и выдачи им сигнала Запрос на упра ляющий выход преобразов.ателя фаза - код начинается цикл записи текущего значени.я кода фазы и кода времени его регистрации преобразователем фаза - код относительно очередного :тактового импульса таймера 3 в соответствующий модуль буферной памяти. Причем текущий код фазы содержится IB буферном регистре 10, а соответст

2395б

вующий ему код времени - в счетчике 6 времени. Цикл записи кодов фазы и времени завершается увеличением адресного счетчика модуля буферной памяти и выдачей сигнала Ответ, который nocTjmaeT иа первый управляющий вход соответствующего преоб- разователя фаза - код и вызывает в нем сброс триггера 25 и счетчика 6 времени,

В этом состоянии преобразователи 1 J-1,M фаза - код и модули 2,1-2,М буферной памяти готовы к новому циклу

0

0

ходом следующего тактового импульса от таймера 3,

Регистрация текущих значений фаз сигналов измерительных каналов и опорного канала интерферометра (с одновременной регистрацией времени каждого отсчета) происходит с периодической сменой частоты таймера 3, Причем общее число регистрируемых значений

каналом устройства равно

V P(Ni + N),

- объем буферной памяти;

- число включений каждого из

генераторов 26 и 27 таймера

за цикл измерений;

- число отсчетов, выполненных

с частотой работы генераторов 26 и 27 соответственно во время их очередного включения ,

Измерительный цикл устройства за- - вершается по сигналу LAM, передаваемому, по соответствующей шине магистрали 4 крейта КАМАК при переполнении ад- ресдого счетчика одного из модулей 2,-2.М буферной памяти. Переполнение

памяти происходит практически одновременно после последнего тактового импульса таймера 3, Длительность измерительного цикла устройства равняется

P(N,- T; + Nj-T,,),

где Т, и

Т. , периоды сигналов, гене50

рируемых соответственно генераторами 26 и 27, Цикл измерений завершается (см,фиг,4) блокировкой входов и выхо- gg дов преобразователей 1,1-1.М и выхода таймера 3 по команде КАМАК M(15)F (.24),

Считьюание данных, записанных в модули 2,1-2.М буферной памяти, осуществляется по стандартной магистрали 4 крейта КАМАК с использованием соответствующих команд чтения.

Фаза If (t) сигнала опорного кана- ла интерферометра в любой момент времени очередного цикла преобразования устройства определяется выражением

25r-f.t,

где fp - частота сигналов опорного

канала интерферометра; t - время относительно очередного тактового импульса таймера 3. Фаза Vf,(t) сигнала п-го измерительного канала интерферометра (кратная 2 Г) может быть определена только в момент t,, прихода импульса от дискриминатора 5 нуля соответствующего преобразователя фаза - код во время измерительного цикла устройства. В связи с этим текущее значение фазового сдвига Lf (t ) сигнала п-го канала интерферометра определяется следующим образом: /)y,{tj ( - c/,(t,) 2(Nt -и о)

т„

2T() + ( )Jb,

{)

где N

N

N

текущее значение кода счетчика 9 фазы преобразователя фаза - код п-го измерительного канала; текущее значение кода счетчика 9 фазы преобразователя

счетчика времени; fp - промежуточная частота сигналов интерферометра; Т - период сигнала измерительного канала интерферометра. Таким образом, максимальная величина fg , определяющая точность отсчетов /1(/ (t) согласно формуле (1), и максимальная величина Т определяют значение т. Наибольшее значение m должно составлять около 10 бит для регистрации данных с лазерных интерферометров, обеспечивающих на выходе сигналы с периодом Tj около 100 мкс.

35

N: При этом абсолютная погрешность отсчетов устройства не превышает. 2 nTj/T 0,36°, если fg 10 МГц, т.е. соответствует классу точности известных типов лазерных интерферо- 1.1 фаза - код опорного ка- ю метров.

нала;Для работы устройства во всем частекущее значение кода счет- тотном диапазоне от 10 КГц до 2 МГц чика 6 времени преобразова- сигналов промежуточной частоты нз- теля фаза - код п-го изме- вестных типов интерферометров с мини- рительного канала; 45 мольной разрядностью информационных текущее значение кода счет- слов преобразователей 1.1-1.М, записываемых в модули 2.1-2.М буферной

чика 6 времени преобразователя 1.1 фаза - код опорного канала;

Т.- период тактовых импульсов счетчика 6 времени преобразователей фаза - код; Т - период сигналов опорного

канала интерферометра. Счетчики 9 фазы разрядностью п обеспечивают определение разности фаз сигналов в следующих пределах:

О i ,)if(t) 27Г(2 - 1) . (2)

50

памяти, в каждом преобразователе фаза - код устройства с помощью коммутатора 11 имеется возможность устанавливать соответствующую разрядность счетчика 6 времени и счетчика 9 фазы. Причем при увеличении разрядности m счетчика временн можно 55 уменьшить разрядность п счетчика фазы.

На фиг.З показан вариант коммута- ;тора 11, позволяющий установить разрядность счетчика 9 фазы равной 8,6

Так как значение /di/Ct) прямо пропорционально длине волны интерферометра то оно достигает максимальной величины при использовании СВЧ-интерфе- рометра, имеющих наибольшую длину волны. Для СВЧ-интерферометров миллиметрового и субмиллиметрового диапазонов Ч мчкс -- Поэтому максимальное значение п разрядности счетчика 9 фазы устройства согласно формуле (2) должно быть равно 8 битам. Разрядность m счетчика 6 времени может быть найдена из выражения

f5.

ЛМ п 2

от

I 7/

-р

fB-{Tj

МО tC )

(3)

где fg - частота тактовых импульсов

счетчика времени; fp - промежуточная частота сигналов интерферометра; Т - период сигнала измерительного канала интерферометра. Таким образом, максимальная величина fg , определяющая точность отсчетов /1(/ (t) согласно формуле (1), и максимальная величина Т определяют значение т. Наибольшее значение m должно составлять около 10 бит для регистрации данных с лазерных интерферометров, обеспечивающих на выходе сигналы с периодом Tj около 100 мкс.

50

памяти, в каждом преобразователе фаза - код устройства с помощью коммутатора 11 имеется возможность устанавливать соответствующую разрядность счетчика 6 времени и счетчика 9 фазы. Причем при увеличении разрядности m счетчика временн можно 55 уменьшить разрядность п счетчика фазы.

На фиг.З показан вариант коммута- ;тора 11, позволяющий установить разрядность счетчика 9 фазы равной 8,6

и 4, причем, при уменьшении разрядно- сти счетчика 9 фазы соответственно увеличивается разрядность счетчика 6 времени.

Формула изобретения

i.Устройство для измерения фазовых сдвигов сигналов от многоканальных интерферометров термоядерных установок, содержащее М преобразователей

фаза - код, М мoдyJJeй буферной памяти и таймер, которые входами и выходами сопряжения подключены к магистрали д крейта КАМАК, каждый из модулей буферной памяти информационным входом управляющими выходом и входом соединен с информационным выходом,первым управляющим входом и управляющим выхо- д второй группе информационных входов дом соответствзтощего преобразовате- каждой группы коммутатора , - с перкоммутатора - с первым выходом узла управления, в первой группе коммутатора остальные входы первой группы информационных входов соединены с выходом переноса счетчика времени, а в каждой из последующих групп коммутатора осталы-гые входы первой группы информационных входов подключены к выходу переноса предьщущей группы счетчика фазы, входы стробирования и входы управления каждой группы комму татора соединены соответственно с - третьим и четвертым выходом узла управления, а выход, соответствующий первой группе информационных входов каждой группы коммутатора - со счетным входом соответствующей группы счетчика фазы, выход, соответствующий

ля фаза - код, содержащего дискриминатор нуля, вход которого является измерительным входом преобразователя счетчик времени, опорньн генератор и узел управления, связанный первым выходом с входом сброса счетчика времени, -второй выход и первый вход узла управления являются соответственно управляющим выходом и первым управляющим входом преобразователя, о тличающее-ся тем, что, с целью расширения частотного диапазона устройства, тактовый выход таймера подключен к вторым управляющим входам преобразователей фаза.- код, в каждый из которых дополнительно введены счетчик фазы, коммутатор, буферный регистр и делитель-переключатель частоты, связанный информацион- р ления, причем информационным выходом ным входом с выходом генератора опор- преобразователя фаза - код являются ной частоты, а первым выходом - со счетным входом счетчика времени, привыходы счетчика времени и буферного регистра.

чем коммутатор и счетчик фазы разделены на N групп, каждая группа комму- ц.ю щ е е с я тем, что узел управления

татора содержит входы управления, входы стробирования, две группы по Ы+1 информационных -входов и два выхода, соответствующих двум группам информационных входов, причем в i-й группе коммутатора i-й вход первой группы информационных входов соединен с выходом дискриминатора нуля, а входы с первого по i-й второй груп; пы информационных входов каждой i-й группы коммутатора соединены с формирователем сигнала логического нуля, остальные входы второй группы информационных входов каждой из групп

второй группе информационных входов каждой группы коммутатора , - с перкоммутатора - с первым выходом узла управления, в первой группе коммутатора остальные входы первой группы информационных входов соединены с выходом переноса счетчика времени, а в каждой из последующих групп коммутатора осталы-гые входы первой группы информационных входов подключены к выходу переноса предьщущей группы счетчика фазы, входы стробирования и входы управления каждой группы коммутатора соединены соответственно с - третьим и четвертым выходом узла управления, а выход, соответствующий первой группе информационных входов каждой группы коммутатора - со счетным входом соответствующей группы счетчика фазы, выход, соответствующий

вым входом сброса соответствующей группы счетчика фазы, вторые входы сброса групп счетчика фазы объедине5 ны и соединены с пятым выходом узла управления, а информационный выход счетчика фазы соединен с информационным входом буферного регистра, вход управления записью которого подключен

0 к шестому выходу узла управления, второй вход узла управления является вторьм управляющим входом преобразователя фазд - код, третий вход узла управления подключен к выходу дискри- минатора нуля, а седьмой и восьмой йыходы - к первому и второму управляющим входам делителя-переключателя частоты, в.торой выход которого соединен с четвертым входом узла управления, причем информационным выходом преобразователя фаза - код являются

выходы счетчика времени и буферного регистра.

2. Устройство по п.Г, о т л и ч а-

0

каждого преобразователя содержит четыре триггера, счетчик, регистр состояния и дешифратор команд КАМАК, причем входы и выходы сопряжения де-. шифратора соединены с шинами управления входов и выходов сопряжения узла управления с магистралью крейта КАМАК, первый выход дешифратора соединен с первым входом сброса первого триггера и входом сброса регистра состояния, вход управления записью которого соединен с вторым выходом, дешифратора, информационный вход регистра состояния связан с шинами

11

записи ((и) входа сопряжения узла управления, а первый и второй выходы регистра состояния являются четвертым и седьмым выходами узла управления, третий и четвертый выходы дешифратора соединены с входами сброса и установки первого триггера, выход которого является третьим выходом узла управления и подключен к первьм входам сброса второго и третьего триггеров, вход стробирования второго триггера является вторым входом узла управления, инверсный выход - восьмым выходом узла управления и подклю- чен к своему информационному входу, а прямой выход связан с информационным входом третьего триггера, вход стробиро.вания которого является треть

135

им входом узла управления, а выход

соединен с вторым входом сброса второго триггера и инверсным входом сброса счетчика, счетный вход которого является четвертьш входом узла управления, первый выход - шестым выходом узла управления и подключен к входу стробирования четвертого триггера, информационный вход которого соединен с вторым выходом счетчика, третий выход счетчика связан с вторым входом

Сигко/1 ofjop. , ffotfo/ra о те фе/ ол4ет/за

Сигмолы измерительных ffoffcr/roff t/ me/ e/yfff4fmfle

15 10

25

ЗО

2395

сброса третьего триггера, причем пятый выход дешифратора является пятым выходом узла зтравления и соединен с первым входом сброса четвертого триггера, выход которого является вторым выходом узла управления, а второй вход сброса соединен с первыми входом и выходом узла управления,

3. Устройство по П.1, отличающееся тем, что, с целью повышения информативности за счет повышения частоты запуска преобразователя фаза - код на интервалах быстрого изменения измеряемых параметров, таймер содержит подключенные к магистрали крейта КАМАК две пары программно- предустанавливаемых генераторов и счетчиков, причем первые вькоды генераторов объединены и подключены к вторым управляющим входам преобразователей, вторбй выход каждого генератора подключен к входу счетчика, образующего с ним пару, выход каждого . счетчика подключен к входу Стоп генератора, работающего с ним в одной паре, и входу Пуск генератора другой пары, причем каждый генератор и счетчик имеют отдельные входы сопряжения с магистралью крейта КАМАК.

20

-,

i

«)

г

;

I

VJ

V A/t

S

л

К- н

llfr 1

щ

V

I

«м

«VJ

,93 S(.,

с Vyo ffffOlfg

V. y

loagy nffhtfOH

(/S 4:)/fUJOf «

0

ГУ

,40WJ

t

M

rtf

OJ

QO

:t,.

SO

s

сч,

л

h

ii

Составитель А.Дорошенко Редактор Л.Веселовская Техред Л.Олийнык Корректор А.Тяско

Заказ 5562/44

Тираж 730Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Л .«

:

«

1,

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для автоматического определения характеристик аналого-цифровых преобразователей в динамическом режиме | 1987 |

|

SU1520655A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Тепловой расходомер | 1983 |

|

SU1161826A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1222098A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Устройство для проверки функциональных блоков | 1980 |

|

SU1008745A1 |

Изобретение относится к области вычислительной и информационно-измерительной техники и может быть использовано в автоматизированных системах сбора -и обработки данных с интерферометров термоядерных установок. Целью изобретения является расширение частотного диап-азона и повышение информативности. Устройство содержит М преобразователей фаза - код (ПФК), М модулей буферной памяти и таймер, которые подключены к магистрали крей- та КАМАК. Каждый из модулей буферной памяти связан по информационному входу с информационным выходом соответствующего ПФК, первый управляющий вход которого и управляющий выход подключены к управляющим выходу и входу модуля буферной памяти. Вторые управляющие входы всех ЦФК соединены с тактовым выходом таймера. Каждый ПФК состоит из дискриминатора нуля, вход которого является измерительным входом ПФК, счетчика времени, опорного генератора, узла управления, делителя переключателя частоты, коммутатора, счетчика фазы и буферного регистра. Информационным выходом ПФК являются выходы счетчика времени и буферного регистра. Выполнение счетчика фазы в виде отдельных групп, взаимосвязь которых между собой, а также с остальными блоками ПФК осуществляется через разделенный на такое же количество групп коммутатор, позволяет по командам, поступающим по магистрали крейта КАМАК, оперативно увеличивать разрядность счетчика времени за счет использования одной или нескольких групп счетчика фазы. 2 з.п ф-лы, 5 ил. оэ СП 5 со со СП

| Говорящий кинематограф | 1920 |

|

SU111A1 |

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| и др | |||

| Цифровые модули в стандарте КАМАК | |||

| ПОВОРОТНЫЙ ЭЛЕКТРИЧЕСКИЙ ПЕРЕКЛЮЧАТЕЛЬ | 1925 |

|

SU3846A1 |

| Korten М., Soltwisch Н | |||

| Data acquisition and processing system for the HCN interferometer | |||

| Diagnostic at the TEXTOR experiment | |||

| Proc | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-11-15—Публикация

1983-09-28—Подача