управляющий вход с первым выходом . коммутатора, а выход с первым входом первого элемента ИЛИ, второй и третий входы которого соединены соот ветственно с первым входом блока м вторым выходом коммутатора, вход и третий выход .которого подключены соответственно к третьему входу блока

и первому входу второго элемента ИЛИ, вторым входом соединенного с выходом узла ручного запуска устройства ввода, выходы первого и второго элементов ИЛИ соединены с вторым выходом блока, а входы первого элемента ИЛИ и выход второго элемента ИЛИ подключены к первому выходу блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для сопряжения ведущей и N ведомых цифровых вычислительных машин | 1988 |

|

SU1531104A1 |

| Устройство для сопряжения цифровых вычислительных машин | 1976 |

|

SU608151A1 |

| Программируемый контроллер | 1991 |

|

SU1833870A1 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Устройство ввода-вывода | 2020 |

|

RU2753980C1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство сопряжения | 1974 |

|

SU519704A1 |

| Адаптер канал-канал | 1982 |

|

SU1067492A1 |

| Устройство для отображения информации | 1983 |

|

SU1091154A1 |

1. УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ФУНКЦИОНАЛЬНЫХ БЛОКОВ, содержащее Мультиплексор входных сигналов, выход которого соединен с входом регистра данных, блок управления вводом информации, генератор синхроимпульсов, сервисный регистр, буфер- . ный регистр, счетчик, компаратор и формирователь испытательных сигналов, о т л и ч IU е е с я тем, что, с целью сокращения времени проверки, в него введены регистр адреса, регистр комднд, дешифра ор адреса, дешифратор команд, блок ручного ввода, блок переключения режимов работы и блок индикации, причем первый и ; второй информационные входы мульти;плексора входных сигналов соединё ны соответственно с информационным ;входом устройства и выходом блока ручного ввода, выход с входами регистра-адреса и регистра команд, а адресный вход с первым выходом блока переключения режимов работы, :вторым выходом подключенного к входу генератора синхроимпульсов, выход которого соединен с (Тактовой шиной магистрали ввода-вывода устройства и первым входом формирователя испытательных сигналов, вторым ёходом подключенного через дешифратор команд к выходу регистра команд и управляющей шине магистрали ввода-вывода устройства, а третьим входом к адресной шине магистрали ввода-вывода и через дешифратор адреса к выходу регистра адреса, выход регистра данных соединен с информационной шиной магистрали ввода-вывода и первыми входами сервисного и буферного регистров, вторые входы которых поц ключены к выходу формирователя испы-: тательных сигналов, к команднеЛ шине магистрали ввода-вывода, к первому. входу блока управления вводом информации и через счетчик к первому входу блока индикации, вторым входом соединенного-спервым выходом блока управления вводом информации, вторс Ьыход которого соединен с выходом синхронизации ввода информации устройстве, а второй, третий и четвер.тый входы соответственно с выходом сервисного регистра, управляющей миной магистрали ввода-вывода и выходом компаратора, первый вход которо го подключен к выходу буферного ре:гистра, а второй - к информационной ,шине магистрали ввода-вывода. 2. Устройство по п. 1, о т л и -; чающееся тем, что блок уп- ; , равления вводом информации содержит узел сравнения, коммутатор, узел ручного запуска устройства ввода и |два элемента ИЛИ, причем первый и ;второй информационные входы узла сравнения соединены соответственно с вторым и четвертым входами блока,

1

Изобретение относится к вычислиteльнoй технике и может быть использовано для тестового контроля программно-управляемых блоков в системе КАМАК.

Известны устройства для тестового контроля логических блоков, содержащие блок ввода, блок управления, коммутатор, компаратор, блок эталонов, регистр контроля параметров, регистр данных, схему сравнения, блок индикации и вывода и блок формирования временной задержки 1 .

Недостаток этих устройств состоит в ограниченной области применения.

Наиболее близким к предлагаемому по сущности технического решения является устройство для контроля больших интегральных схем, содержащее группу формирователей входных сигналов, выходы которой соединены с входом испытуемой схемы,, а вход соединен с выходом памяти и одним входом компаратора, второй вход которого соединен с выходом испытуемой схемы, а выход через регистр ошибок с вхоом индикации неисправности ЦВМ, схему сравнения, первым входом полключрнную через регистр адреса к первому информационному выходу ЦВМ, вторым входом к выходу счетчика и входу памяти , а выходом к одному входу элемента И, другой вход которого соединен с генератором тактовых импульсов, а выход с входом счетчика и первыми входами, коммутатора и буферного регистра, второй вход которого подключен к второму информационному выходу ЦВМ, а выход к второму входу коммутатора, третьим входом соединенного через регистр управления с управляющим выходом ЦВМ, четвертым вхоом - с первым выходом триггера реима, а выходом - с вторым входом амяти, третий вход которой подключен к второму выходу триггера режима, входом соединенного с выходом задания режима ЦВМ t JНедостаток этого устройства состоит в большом времени проверки и больших аппаратурных затратах, что обусловлено невозможностью оперативной Проверки одного или группы блоков без выключения из работы объекта и, необходимостью использования ЦВМ для контроля.

Цель изобретения - сокращение времени проверки и сокращение аппаратурных затрат.

Поставленная цель достигается тем что в устройство, содержащее мультиплексор входных сигналов, выход которого соединен с входом регистра данных, блок управления вводом информации, генератор синхроимпульсов, сервисный регистр, буферный регистр, счетчик, компаратор и формирователь испытательных сигналов, введены регистр адреса, регистр команд, дешифратор адреса, дешифратор команд, блок ручного ввода, блок переключения режимов работы и блок индикации, причем первый и второй информационные входы мультиплексора входных сиг налов соединены соответственно с информационным входом устройства и выходом блока ручного ввода, выход с входами регистра адреса и регистра команд, а адресный вход - с первым выходом блока переключения режимов работы, вторым выходом подключенного к входу генератора синхроимпульсов, выход которого соединен с тактовой шиной магистрали ввода-вывода устройства и первым входом формирователя испытательйых сигналов, вторым входом подключенного через дешифратор команд к выходу регистра команд и управляющей шине магистрали вводавывода, a третьим входом - к адресной шине магистрали ввода-вывода и через дешифратор адреса к выходу регистра адреса, выход регистра данных соединен с информационной шиной магистрали ввода-вывода и первыми входами сервисного и буферного регистров, вторые входы которых подключены к формирова1теля испытательных сигналов, к командной шине магистрали ввода-вывода, к первому входу блока управления вводом .информации и через счетчик к первому входу блока индикации, вторым входом соединенного с первым выходом блока управления вводом информации, второй выход которого соединен с выходом синхронизации ввода информации устройства, а второй, третий и четвертый входы соответственно с выходом сервисного регистра, управляющей шиной магистрали ввода-вывода и выходом компаратора, первый вход которого подключен к выходу буферного регистра, а второй - к информационной шине магистрали ввода-вывода.

При этом блок управления вводом информации содержит узел сравнения, коммутатор, узел ручного запуска устройства ввода и два элемента ИЛИ, причем первый и второй информационные входы узла сравнения соединены соответртвенно с вторым и четвертым входами блока, управляющий вход с первым выходом коммутатора, а выход с первым входом первого элемента ИЛИ, второй и третий входы которого соединены соответственно с первым входом блока и вторым выходом коммутатора, вход и третий выход которого подключены соответственно к третьему входу блока и первому входу второго элемента ИЛИ, вторым входом соединенного с выходом узла ручного запуска устройства ввода, выходы первого и второго элементов ИЛИ соединены с вторым выходом, блока, а входы первого элемента -ИЛИ и выход второго элемента ИЛИ подключены к первому выходу блока.

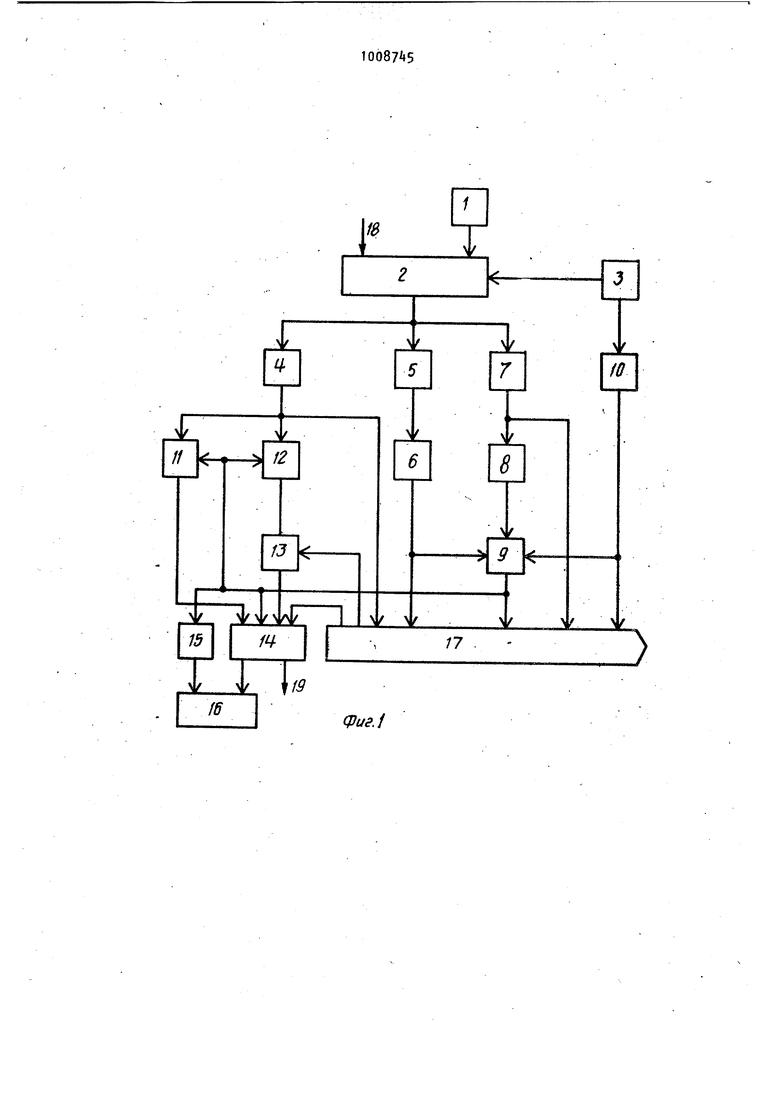

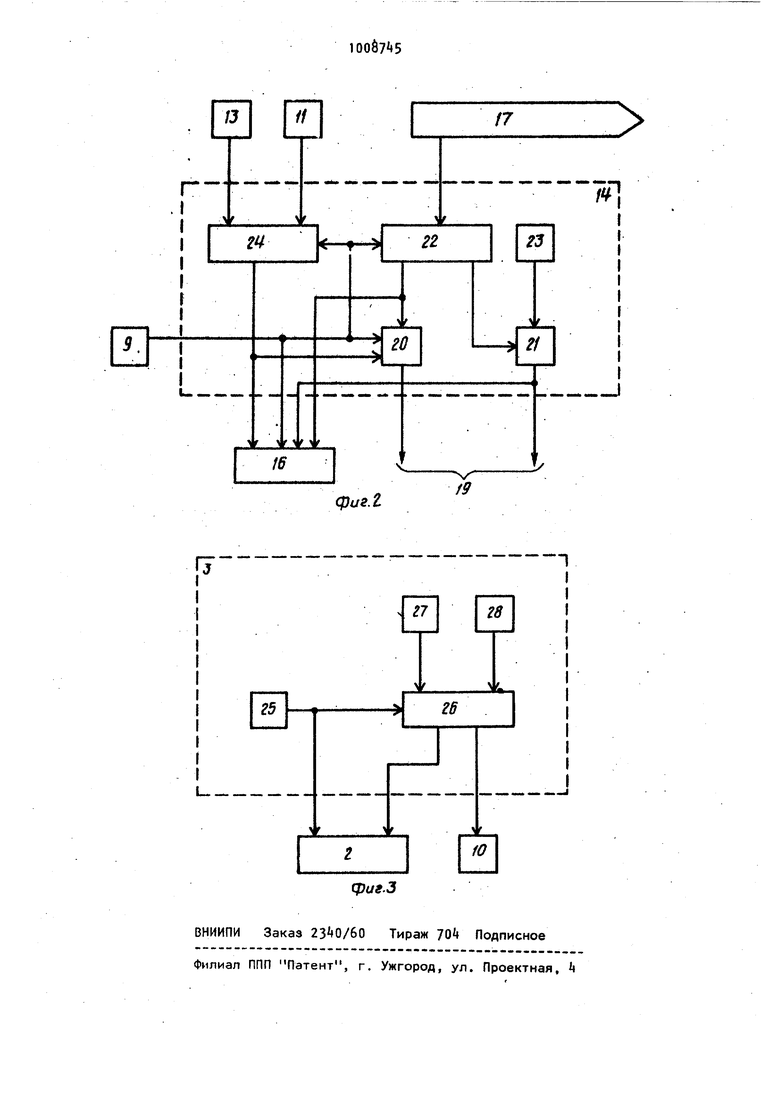

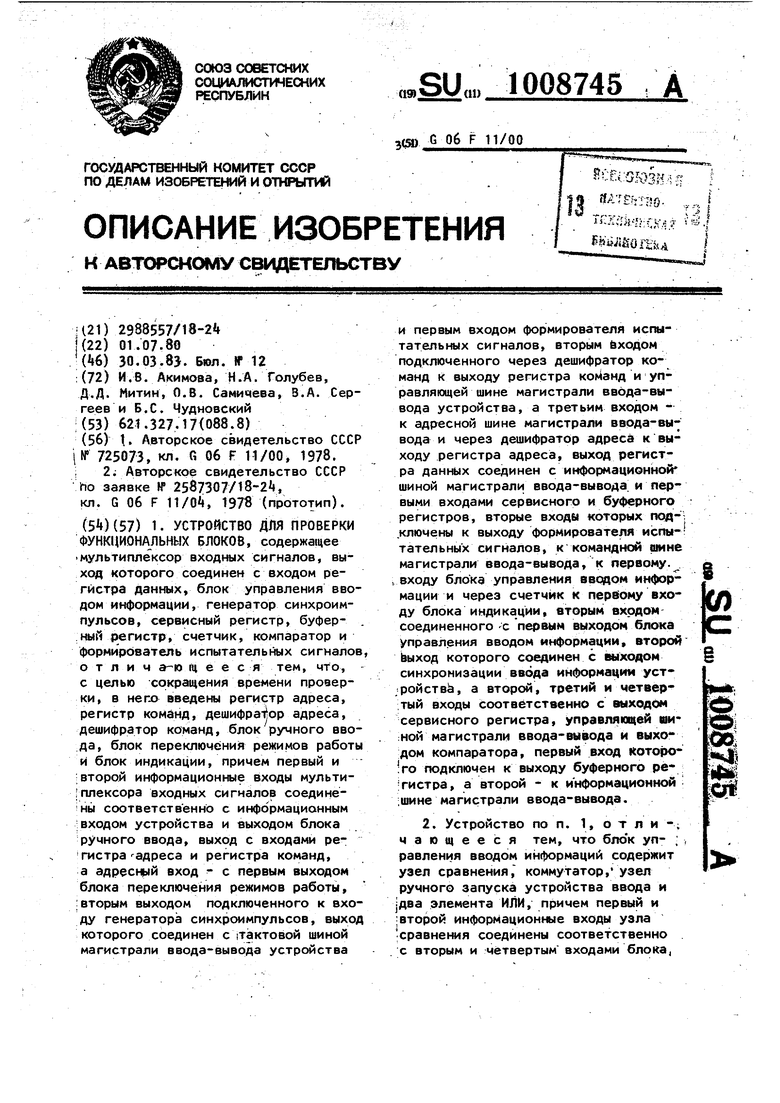

На фиг. 1 представлена блок-схема устройства; на фиг. 2 и 3 - функциональная схема блока управления вводом информации и блока переключения режимов работы.

Устройство (фиг, О содержит блок 1 ручного ввода, мультиплексор 2 .входных сигналов, блок 3 переключения режимов работы, регистр k дан,ных, регистр 5 адреса, дешифратор 6 ;адреса, регистр 7 команд, дешифратор 8 команд, формирователь 9 испытательных сигналов, генератор 10 синхроимпульсов, сервисный регистр 11, буферный регистр 12, компаратор 13 блок Т управления вводом информации, счетчик 15. блок 16 индикации, магистраль 17 ввода-вывода устройства, информационный вход 18 устройства, выход 19 синхронизации ввода информации.

Блок 1 управления вводом информации (фиг. 2 содержит элементы

ИЛИ 20 и 21, коммутатор 22, узел 23 ручного запуска устройства ввода и узел 2k сравнения. Блок 3 переключения режимов работы (фиг. З) состоит из переключателя 25 режимов,

мультиплексора 2б, узла 27 ручного ввода управляющих импульсов и узла 28 ввода управляющих импульсов от устройства ввода информации.

Устройство работает следующим образом.

Устройство рсуществляет провер1ку блоков вычислительной системы, (организованной по стандартам КАМАК. Все блоки этой системы (в том числе

и предлагаемое устройство) подключены к магистрали 17 ввода-вывода, по которой осуществляют взаимные обмены информацией.

Устройство может работать в режимах ручного и автоматизированного контроля.

13 первом режиме (ручного контроля) необходимая информация формируется с помощью наборного поля (например, тумблерного) блока 1, Во втором режиме (автоматизированного контроля) информация поступает по входу 18 от внешнего источника (например, ЭВМ, считыватель с перфоленты или какоголибо устройства, способного хранить программу проверки, наборы испытательных и эталонных наборов и т.п.), причем синхронизация вывода из такого внешнего источника осуществляется по сигналам с выхода 19 и при

помощи узла 28 (внешние связи узла 28 не показаны). Выбор первого или второго режима осуществляете переключателем 25 устанавливающим в соответствующее положение мультиплексоры 2 и 26.

При адресации информации в один из функциональнь1х блоков, который соединен с устройством (контроллером крейта) через магистраль 17, информация с выхода регистра Ч поступает в магистраль 17, где по адресу и субадресу, определенному соответственно дешифратором 6 и регистром 7, выполняется команда, определяемая функцией регистра 7.

Так, например, при формировании входного воздействия на проверяемый блок данные, поступающие с перфоленты, записываются в проверяемый блок по соответствующему субадрех;у. Для синхронизации всех операций в АСК предусмотрен генератор 10 синхроимпульсов, имеющий выход в магистраль 17. При адресации данных в устройство формирователь 9 формирует соответствующие управляющие сигналы для записи данных в буферный регистр 12 либо в сервисный регистр 11.

Буферный регистр 12 предназначен для хранения эталонных значений.

Информация, поступающая в буферный регистр 12 с регистра , запоминается и передаётся в Компаратор 13, S котором осуществляется функция сравнения эталонных данных и данных, поступающих по соответствующим шинам чтения информации из магистрали 17 и из проверяемого брака. На выходе компаратора 13 появляются сигналы результата сравнения двух чисел - с буферного регистра 12 и магистрали 17- Выбор режима осуществляется программно и информация о нем хранится в сервисном регистре 11, Например, при опросе состояний выхода проверяемого блока, когда известно точно, какое должно быть значение проверяемого параметра, выбирается режим равенства; если проверяемый параметр ;имеет поле допуска, устанавливается режим больше или меньше в заБИ- симости от того, с каким пределом (нижним или верхним) будет проводитt ся его сравнение.

Таким образом , после того, как сформированы данные, передаваемые в проверяемый блок, в сервисный регистр 11 заносится информация, определяющая режим работы компаратора 13, и в буферный регистр 12 заносится эталонное значение проверяемого параметра, устройство посылает команду в магистраль 17, по которой на шинах чтения появляется информация о

состоянии выходов проверяемого блока Далее в компараторе 13 осуществляется сравнение двух чисел и результат сравнения анализируется на соответствие выбранному режиму в блоке И. При соответствии результата сравнения выбранному режиму блок It формирует сигнал, разрешающий внешнему источнику информации выдачу очередной порции информации. О противном случае блок И информирует оператора о сбое, выдавая соответствующие сигналы в блок 16, и.производит останов внешнего источника информации.

Блок It может также игнорировать сигналы с цифрового компаратора, выдавая сигналы на останов или пуск внешнего источника информации по сигналам формирователя 9 либо по соответствующим сигналам, поступающим по шинам магистрали 17 от функциональных блоков.

Для локализации места сбоя в устройстве используется счетчик 15 команд, который меняет свое состояние на 1 по сигналу, поступающему с формирователя 9. Порядковый номер каждой исполняемой команды индицируется и при.останове исполнения программы это помогает оператору найти причину отказа.

В блоке 16 индикации предусматривается отображение таких сигналов, как Работа, Стоп по X, Стоп по Q (останов исполнения программы по сигналам, поступающим с магистра ли 17, Стоп по схеме сравнения, (в случае соответствия результата сравнения двух чисел в компараторе выбранному режиму), а тёкже Конец программы и Передача управления оператору. Предусмотрен программный останов при необходимости передать управление оператору. Если возникнет такая необходимость, формирователь 9 посылает сигнал в блок И, что приводит к останову всей системы с соответствующей индикацией в блоке 16.

Таким образом, устройство позволяет осуществлять проверку функционирования блоков системы без изъятия плат из своих рабочих мест, что и снижает время проведения проверки, возможность проверки блоков .без использования ЦВМ, позволяет сократить аппаратурные затраты.

ff

13

2

f

5 r V w

16

фиг.1

/7

/

гз

22

21

N/ /9

Z5

26

| t | |||

| Авторское свидетельство СССР № 725073, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| G Об F И/О, 1978 (прототип). | |||

Авторы

Даты

1983-03-30—Публикация

1980-07-01—Подача