Изобретение относится к вычислительной технике и информационно-измерительной технике и может быть использовано совместно с быстродействующими преобразователями для регисрации однократных и быстропротекаю- щих процессов в экспериментальных исследованиях.

Цель изобретения - повышение информационной емкости и надежности буферного запоминающего устройства.

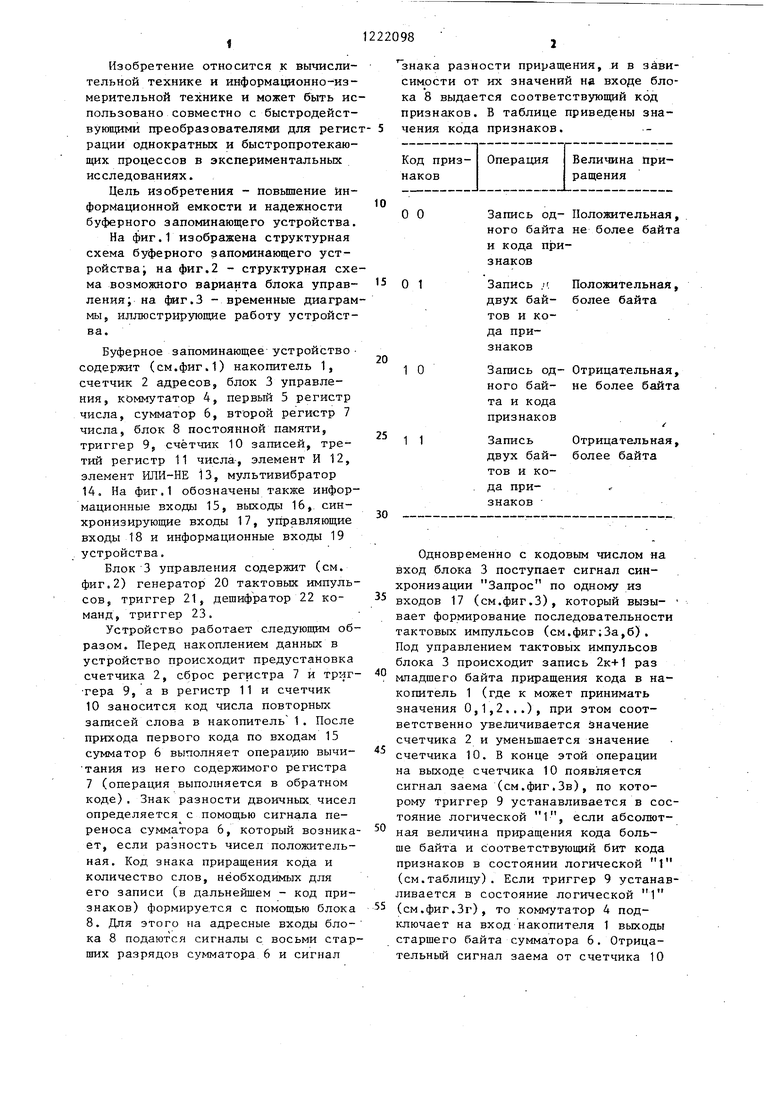

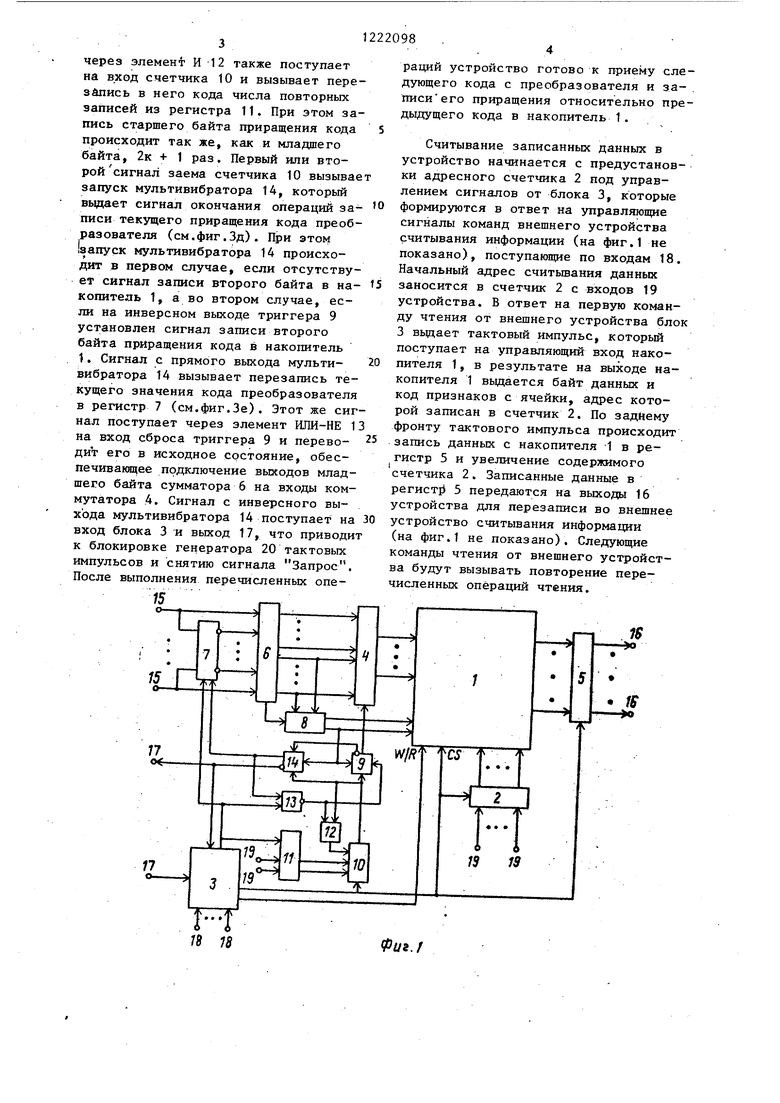

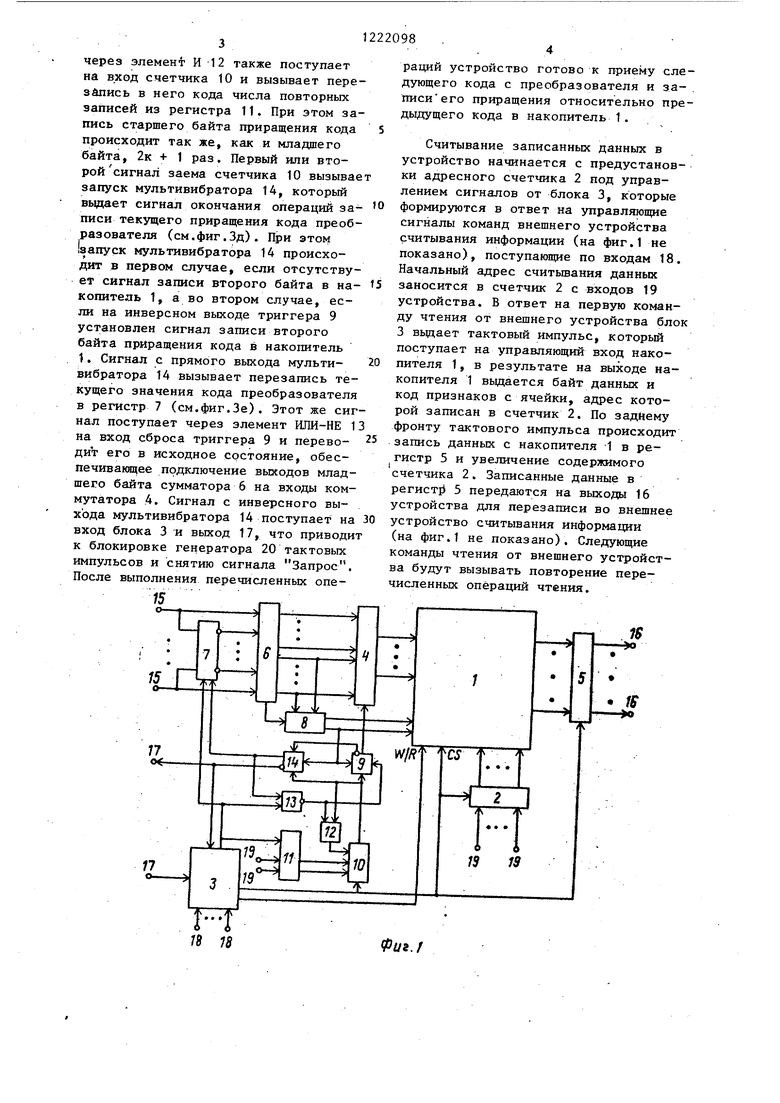

На фиг.1 изображена структурная схема буферного запоминающего устройства; на фиг,2 - структурная схема возможного варианта блока управления; на фиг.З - временные диаграммы, иллюстрирующие работу устройства.

Буферное запоминающее устройство содержит (см.фиг.1) накопитель 1, счетчик 2 адресов, блок 3 управления, коммутатор 4, первый 5 регистр числа, сумматор 6, второй регистр 7 числа, блок 8 постоянной памяти, триггер 9, счётчик 10 записей, третий регистр 11 числа, элемент И 12, элемент ИЛИ-НЕ 13, мультивибратор 14. На фиг.1 обозначены также информационные входы 15, выходы 16, синхронизирующие входы 17, управляющие входы 18 и информационные входы 19 устройства.

Блок 3 управления содержит (см. фиг.2) генератор 20 тактовых импульсов, триггер 21, дешифратор 22 команд, триггер 23.

Устройство работает следующим образом. Перед накоплением данных в устройство происходит предустановка счетчика 2, сброс регистра 7 и триг- гера 9, а в регистр 11 и счетчик 10 заносится код числа повторных записей слова в накопитель 1. После прихода первого кода по входам 15 сумматор 6 выполняет операцию вычи- тания из него содержимого регистра 7 (операция выполняется в обратном коде). Знак разности двоичных чисел определяется с помощью сигнала переноса сумматора 6, который возникает, если разность чисел положительная. Код знака приращения кода и количество слов, необходимых для его записи (в дальнейшем - код признаков) формируется с помощью блока 8. Для этого па адресные входы блока 8 подаются сигналы с восьми старших разрядов сумматора 6 и сигнал

знака разности приращения, и в зависимости от их значений на входе блока 8 выдается соответствующий код признаков. В таблице приведены значения кода признаков.

О о

Запись од- Положительная, ного байта не более байта и кода признаков

Одновременно с кодовьм числом на вход блока 3 поступает сигнал синхронизации Запрос по одному из входов 17 (см.фиг.З), который вызы- вает формирование последовательности тактовых импульсов (см.фиг;3а,б). Под управлением тактовых импульсов блока 3 происходит запись 2к+1 раз мпадшего байта приращения кода в накопитель 1 (где к может принимать значения 0,1,2...), при этом соответственно увеличивается значение счетчика 2 и уменьшается значение счетчика 10. В конце этой операции на выходе счетчика 10 появляется сигнал заема (см.фиг.Зв), по которому триггер 9 устанавливается в состояние логической 1, если абсолютная величина приращения кода больше байта и соответствующий бит кода признаков в состоянии логической 1 (см.таблицу). Если триггер 9 устанав55 (см.фиг.Зг), то коммутатор 4 подключает на вход накопителя 1 выходы старшего байта сумматора 6. Отрицательный сигнал заема от счетчика 10

через элемент И 12 также поступает на вход сметчика 10 и вызывает перезапись в него кода числа повторных записей из регистра 11. При этом запись старшего байта приращения кода происходит так же, как и младшего байта, 2к + 1 раз. Первый или второй сигнал заема счетчика 10 вызывае запуск мультивибратора 14, который вьщает сигнал окончания операций записи текущего приращения кода преобразователя (см.фиг.Зд). При этом запуск мультивибратора 14 происходит в первом случае, если отсутствует Сигнал записи второго байта в накопитель 1, а во втором случае, если на инверсном выходе триггера 9 установлен сигнал записи второго байта приращения кода в накопитель 1. Сигнал с прямого выхода мультивибратора 14 вызывает перезапись текущего значения кода преобразователя в регистр 7 (см.фиг.Зе). Этот же сигнал поступает через элемент ИЛИ-НЕ 1 на вход сброса триггера 9 и переводит его в исходное состояние, обес- печивакяцее подключение выходов младшего байта сумматора 6 на входы коммутатора 4. Сигнал с инверсного выхода мультивибратора 14 поступает на вход блока 3 и выход 17, что приводи к блокировке генератора 20 тактовых импульсов и снятию сигнала Запрос , После выполнения перечисленных операций устройство готово к приему следующего кода с преобразователя и за- . писи его приращения относительно предыдущего кода в накопитель 1.

Считывание записанных данных в

устройство начинается с предустановки адресного счетчика 2 под управлением сигналов от блока 3, которые

формируются в ответ на управляющие сигналы команд внешнего устройства считывания информации (на фиг.1 не показано), поступающие по входам 18. Начальный адрес считьшания данных

заносится в счетчик 2 с входов 19 устройства. В ответ на первую команду чтения от внешнего устройства блок 3 вьщает тактовый импульс, который поступает на управляющий вход нако-

пителя 1, в результате на выходе накопителя 1 выдается байт данных и код признаков с ячейки, адрес которой записан в счетчик 2. По заднему фронту тактового импульса происходит

. запись данных с накопителя 1 в регистр 5 и увеличение содержимого счетчика 2. Записанные данные в регистр 5 передаются на выходы 16 устройства для перезаписи во внешнее

устройство считывания информации (на фиг.1 не показано). Следующие команды чтения от внешнего устройства будут вызывать повторение перечисленных операций чтения.

В/юкиро6ка Установке

ТГ1

78

а - Запроса 3anpoc2 LJ

ff .-JTlTFimJTlJrLr

- у- -уiT

в

8

Редактор О. Орловская

Составитель В. Рудаков

Техред М.Маргентап Корректор М. Шароши

Заказ 5268/2 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений -и открытий 113035, Мо&ква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятиеj г. Ужгород, ул. Проектная, 4

re

фие. I

Запись Strufi

Шито

Lf П

л

фс/е. J

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейно-круговой интерполятор | 1985 |

|

SU1259218A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1589383A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Цифровой процессор спектрометрических импульсов | 1989 |

|

SU1610445A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство адресации памяти | 1988 |

|

SU1575188A1 |

| Буферное запоминающее устройство | 1974 |

|

SU515154A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1980 |

|

SU920834A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| первый н второй регистры числа, блок управления и счетчик адресов, выходы которого подключены к адрес- ньм входам накопителя, выходы которого соединены с входами второго регистра числа, выходы которого являются информационным выходами устройства, .одними из информационных входов которого являются входы первого регистра числа, причем управ- лякнцие входы накопителя, первого и второго регистров чис.за и счетчика .адресов подключены к соответствующим выходам блока управления, отличающееся тем, что, с целью повышения информационной емкости и надежности устройства, в него введены коммутатор, блок постоянной памяти, счетчик записей, мультивибратор, третий регистр числа, триггер, элемент И, элемент ИЛИ-НЕ | |||

| и сумматор, одни из входов которого подключены к одним из информационных входов устройства, другие входы - к инверсным выходам первого регистра числа, информационные выходы сумматора соединены с информационными входами коммутатора, выходы которого соединены с одними из информационных входов накопителя, другие информационные входы которого подключены к выходам блока постоянной памяти, входы которого соединены соответственно с выходом переноса сумматора и одними из информационных выходов сумматора, выход элемента И подключен к одному из входов счетчика записей, другие входы которого соединены с выходами третьего регистра числа, а выход счетчика записей соединен с тактовым входом триггера, первым управляющим входом мультивибратора и первым входом элемента И, второй вход которого соединен с выходом элемента ИЛИ-Н В и установочным входом триггера, пря- | |||

| мой выход которого подключен к управт ляющему входу коммутатора, информа- щюнньй вход триггера и второй управляющий вход мультивибратора соединены с одним из выходов блока постоянной памяти, инверсный выход триг гера соединен с третьим управляющим вхо.п дом мультивибратора, инверсный выход которого подключен к одному из входов блока управления и является синхронизирующим выходом устройства, прямой выкод мультивибратора соединен с одним из управляющих входов первого регистра числа и первым входом элемента ИЛИ-НЕ, второй вход которого и управляющие входы третьего регистра числа и счетчика записей подключены к соответствующим выходам блока управления, информационные входы третьего регистра числа являются другими информационными входами устройства | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-09-30—Публикация

1984-07-12—Подача