ИзоГфетение относится к вычислительной технике, в частности к вопросам построения информационно-измерительных систем и может быть использовано при проектировании контроллеров Крейта в системе КАМАК.

Цель изобретения - повышение быстродействия устройства.

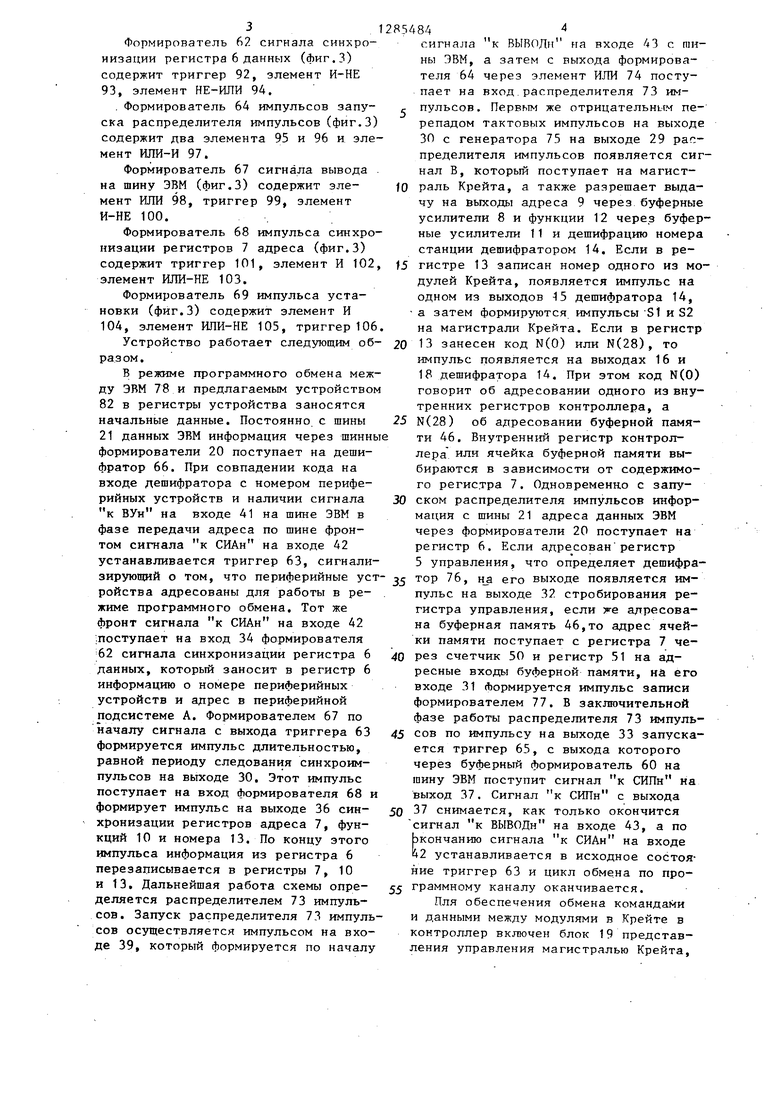

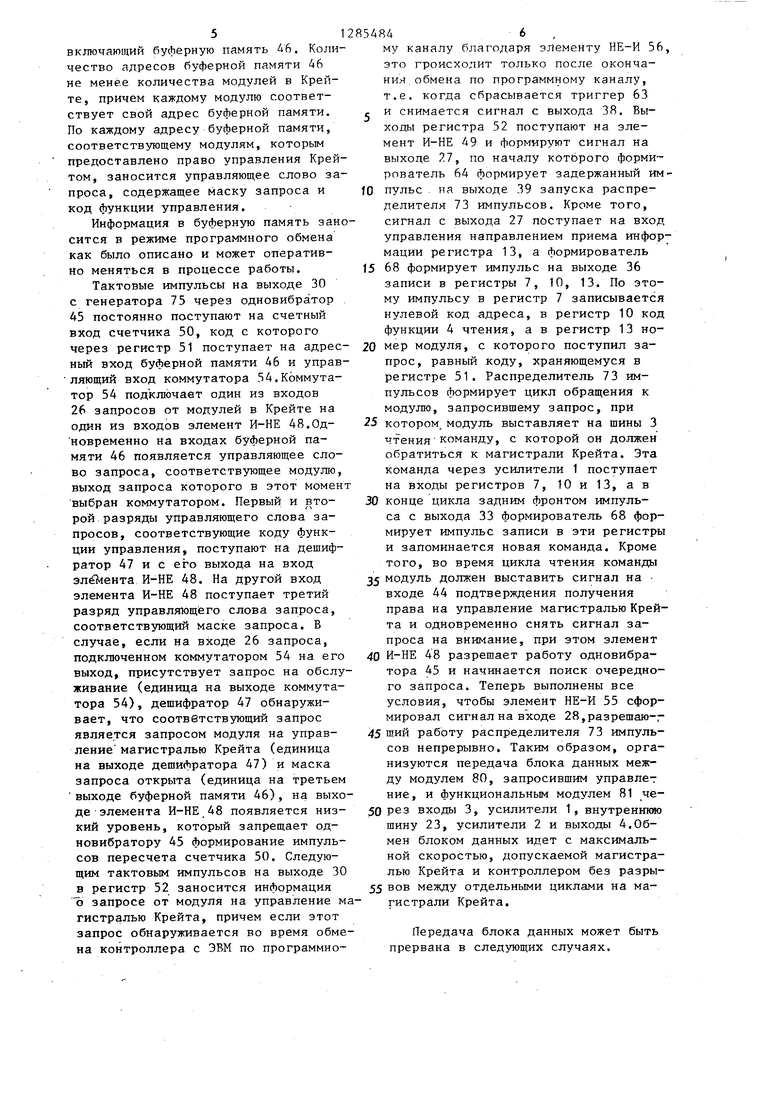

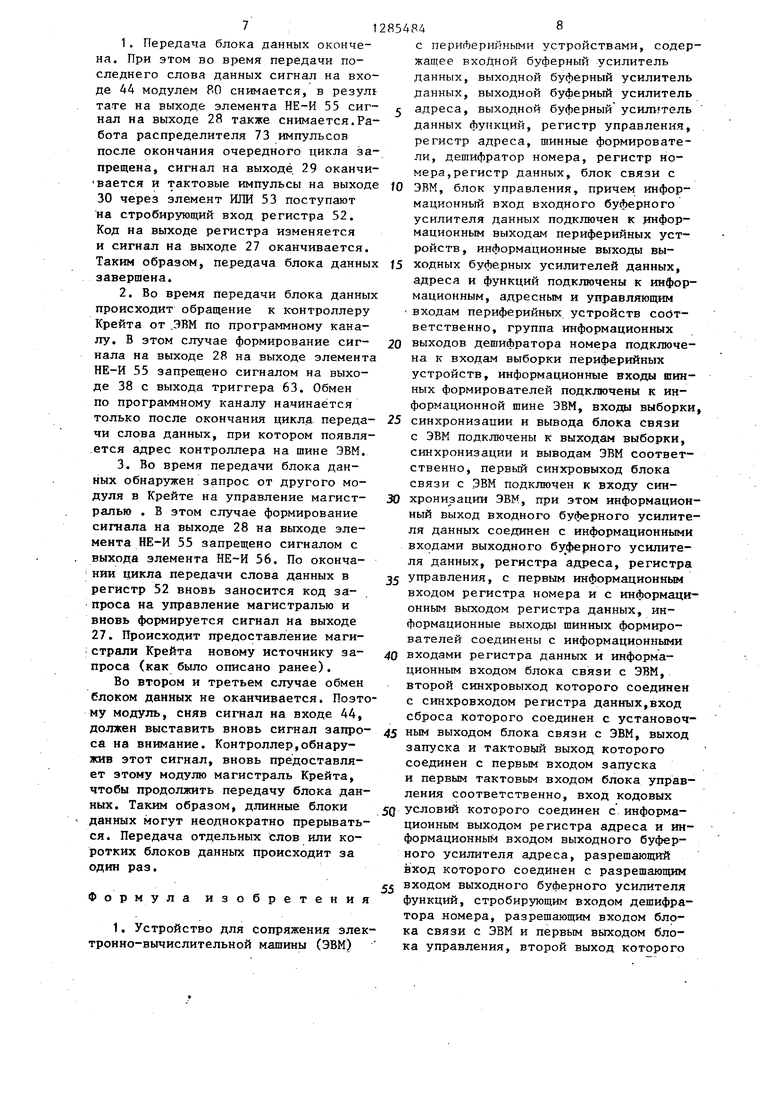

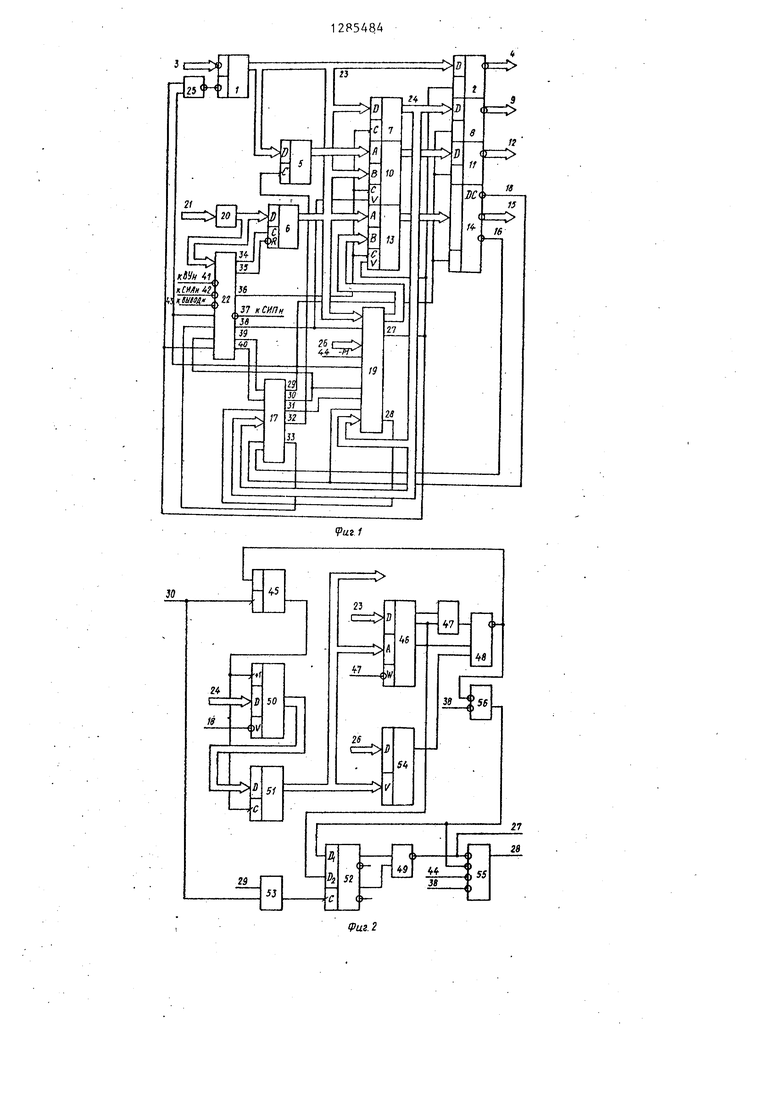

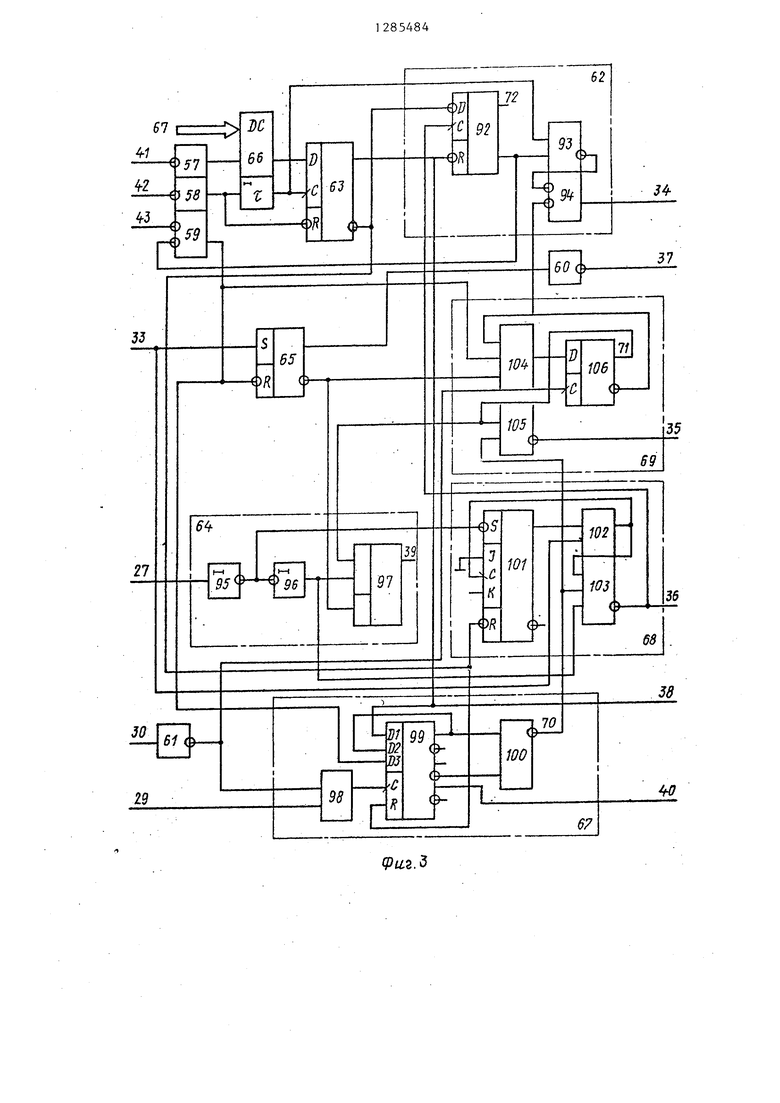

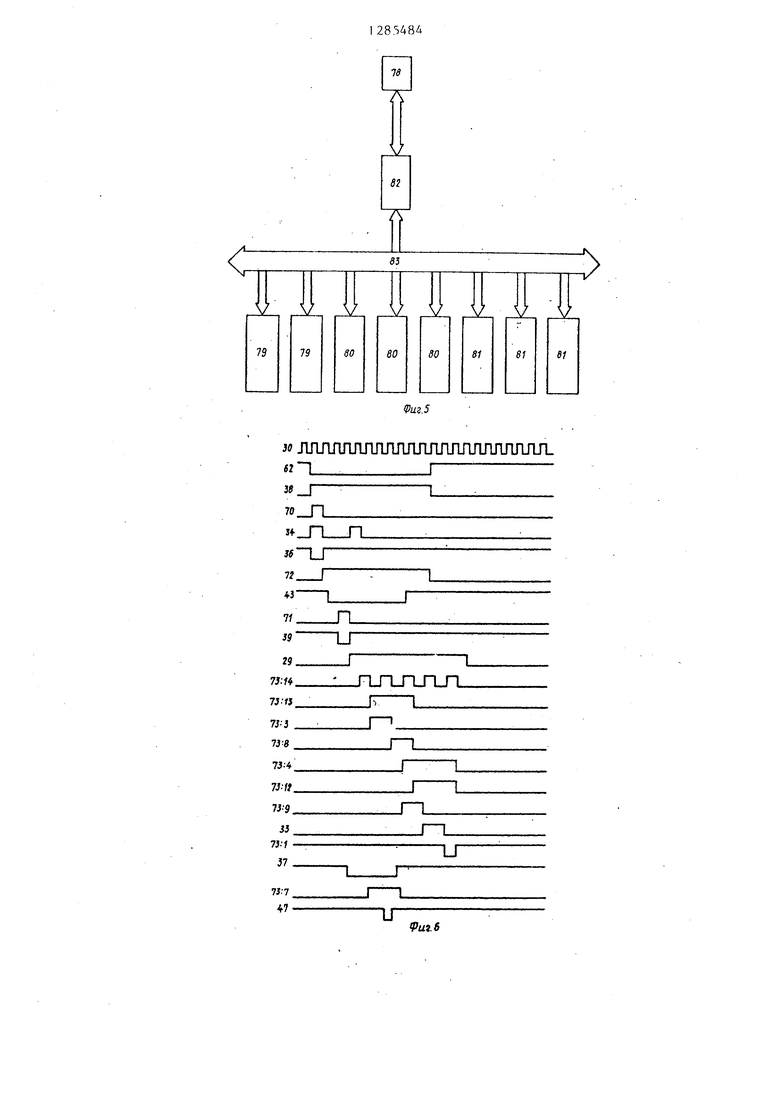

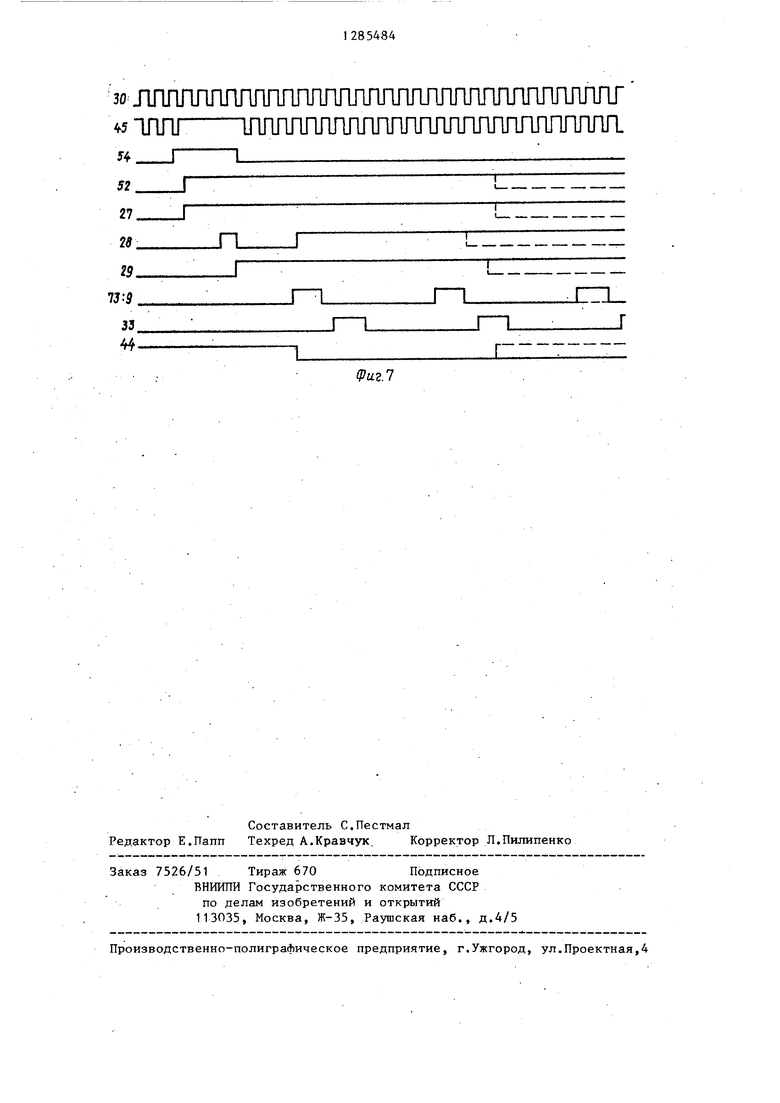

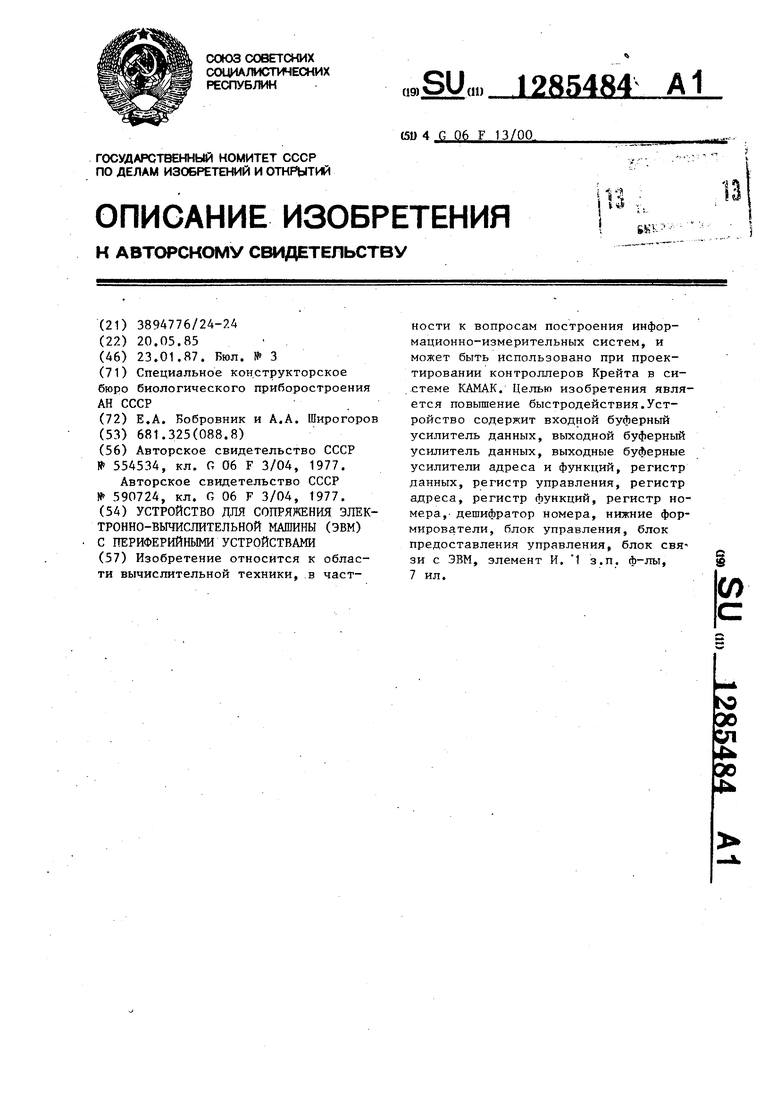

На фиг.1 приведена структурная схема устройства; на фиг.2 - функциональная схема блока предоставления управления; на фиг.З - пример выполнения блока связи с ЭВМ; на фиг.4 - пример выполнения блока управления; на фиг.З - пример системы, в состав которой может входить предлагаемое устройство; на Лиг.6 - временная диаграмма работы устройства в режиме программного обмена с шиной ЭВМ; на фиг. 7 - временна я диаграмма работы устройства при получении запроса на предоставление управления от периферийных устройств.

Устройство (фиг.1) содержит входные 1 и выходные 2 буферные усилители выходных 3 и входных 4 данных пе- ,риферийных устройств, регистр 5 управления, регистры 6 данных, регистр 7 адреса с выходными буферными усилителями 8 линий 9 адреса канала периферийных устройств, регистр 10 Фзшкции с выходными буферными усилителями 11 линий 12 функций канала периферийных устройств, регистр 13 но- мер а с дешифратором 14 номера, информационные выходы 15 дешифратора номера, выход 16 адресования регистров устройства дешифратора номера, блок 17 управления, выход 18 дешифратора номера, блок 19 предоставления управления, шинные формирователи 20 линий 21 данных шины ЭВМ и блок 22 связи с ЭВМ, внутренние информа - ционные шины 23 и 24, элемент И 25, группу 26 входов запросов от периферийных устройств. На фиг,1 обозначены также входы и выходы 27 - 44 устройства.

Блок 19 предоставления управления (фиг.2) содержит.одновибратор 45, буферную память 46, дешифратор 47, второй элемент И-НЕ 48, первый эле- ме.нт И-НЕ 49, счетчик.50, первый 51 и второй 52 регистры, элемент ИЛИ 53, коммутатор 54, первый 55 и второй 56 элементы НЕ-И.

Блок связи с ЭВМ (фиг.З) содержит буферные формирователи 57 - 60 сигна

лов, элемент НЕ 61, формирователь 62 сигнала синхронизации регистра 6 данных, триггер 63 режима.программного | обмена, формирователь 64 импульсов

запуска распределителя импульсов, триггер 65, дешифратор 66, формирователь 67 сигнала вывода на шину ЭВМ при программном обмене с данным устройством, формирователь 68 импульса синхронизации регистров адреса 7, функций 10, номера 13, формирователь- 69 импульса установки. На фиг.З обозначены также выходы 70 - 72 внутренг них узлов блока.

Блок управления (фиг.4) содержит распределитель 73 импульсов, элемент ИЛИ 74, генератор 75 импульсов,дешифратор 76, формирователь 77 импульсов записи.

На фиг.5 представлен пример исполь. зования предлагаемого устройства в системе.

Система содержит ЭВМ 78. В случае, если периферийные устройства входят в систему КАМАК, то предлагаемое устройство будет контроллером Крейта КАМАК, а канал периферийной системы- магистралью Крейта КАМАК.К магистрали Крейта КАМАК подключаются модули, представляющие собой одноплатные микроэвм 79 (модули расширения контроллера), работающие самостоятельно и имеющие возможность обращать ся через контроллер Крейта к любому

модулю в Крейте, модули, являющиеся источниками 80 программ и способные через контроллер Крейта передавать команды и обмениваться данными с любым модулем в Крейте, и другие функциональные модули 81, связанные с внешним оборудованием или выполняющие свои специфические функции (аналого-цифровые и цифроаналоговые преобразователи, входные и-выходные регистры, счетчики, таймеры, синхронизаторы, адаптеры внешних устройств и др.). В общем случае периферийные устройства могут быть связаны с ЭВМ через устройство 82 и канал 83 периферийных устройств.

Распределитель,73 импульсов

(фиг.4) содержит два регистра84 и

85, триггер 86, элемент И 87,эле- мент НЕ-И 88.

Формирователь 77 импульсовзаписи (фиг.4) содержит элементИ 89, элемент НЕ-И 90, элемент И-НЕ91.

3.

Формирователь 62 сигнала синхронизации регистра 6 данных (фиг.З) содержит триггер 92, элемент И-НЕ 93, элемент НЕ-ИЛИ 94.

. Формирователь 64 импульсов запуска распределителя импульсов (фиг.З содержит два элемента 95 и 96 и элемент ИЛИ-И 97.

Формирователь 67 сигнала вывода на шину ЭВМ (фиг.З) содержит элемент ИЛИ 98, триггер 99, элемент И-НЕ 100.

Формирователь 68 импульса синхронизации регистров 7 адреса (фиг.З) содержит триггер 101, элемент И 102 элемент ИЛИ-НЕ 103.

Формирователь 69 импульса установки (фиг.З) содержит элемент И 104, элемент ИЛИ-НЕ 105, триггер 10

Устройство работает следующим образом.

В режиме программного обмена между ЭВМ 78 и предлагаемым устройство 82 в регистры устройства заносятся начальные данные. Постоянно с шины 21 данных ЭВМ информация через шинн формирователи 20 поступает на дешифратор 66. При совпадении кода на входе дешифратора с номером периферийных устройств и наличии сигнала к ВУн на входе 41 на шине ЭВМ в фазе передачи адреса по шине фронтом сигнала к СИАн на входе 42 устанавливается триггер 63, сигнали

зирующий о том, что периферийные уст- тор 76, н его выходе появляется им- ройства адресованы для работы в ре- . жиме программного обмена. Тот же фронт сигнала к СИАн на входе 42 ;поступает на вход 34 формирователя 62 сигнала синхронизации регистра 6 40 данных, который заносит в регистр 6 информацию о номере периферийных устройств и адрес в периферийной подсистеме А. Формирователем 67 по началу сигнала с выхода триггера 63 45 формируется импульс длительностью, равной периоду следования синхроимпульсов на выходе 30. Этот импульс поступает на вход формирователя 68 и формирует импульс на выходе 36 син- 50 хронизации регистров адреса 7, функций 10 и номера 13. По концу этого импульса информация из регистра 6 перезаписывается в регистры 7, 10 и 13. Дальнейшая работа схемы опре- 55 деляется распределителем 73 импульсов. Запуск распределителя 73 импульсов осуществляется импульсом на входе 39, который формируется по началу

пульс на выходе 32 стробирования регистра управления, если же адресована буферная память 46,то адрес ячейки памяти поступает с регистра 7 через счетчик 50 и регистр 51 на адресные входы буферной памяти, на его входе 31 Нормируется импульс записи формирователем 77. В заключительной фазе работы распределителя 73 импульсов по импульсу на выходе 33 запускается триггер 65, с выхода которого через буферный формирователь 60 на шину ЭВМ поступит сигнал к СИПн на выход 37. Сигнал к СШТн с выхода 37 снимается, как только окончится сигнал к ВЫВОДн на входе 43, а по Ькончанию сигнала к СИАн на входе 42 устанавливается в исходное состояние триггер 63 и цикл обмена по программному каналу оканчивается.

Пля обеспечения обмена командами и данными между модулями в Крейте в контроллер включен блок 19 представления управления магистралью Крейта,

o

5

сигнала к ВЫВОДн на входе 43 с гаи- ны ЭВМ, а затем с выхода формирова- через элемент ИЛИ 74 посту64

теля

пает на вход распределителя 73 импульсов. Первым же отрицательннм перепадом тактовых импульсов на выходе 30 с генератора 75 на выходе 29 раг:- пределителя импульсов появляется сигнал В, Который поступает на магистраль Крейта, а также разрешает выдачу на выходы адреса 9 через буферные усилители В и функции 12 через буферные усилители 11 и дешифрацию номера станции дешифратором 14. Если в регистре 13 записан номер одного из модулей Крейта, появляется импульс на одном из выходов 5 дешифратора 14, а затем формируются импульсы Si и S2 на магистрали Крейта. Если в регистр 13 занесен код N(0) или N(28), то импульс появляется на выходах 16 и 18 дешифратора 14. При этом код N(0) говорит об адресовании одного из внутренних регистров контроллера, а 5 N(28) об адресовании буферной памяти 46. Внутренний регистр контроллера или ячейка буферной памяти выбираются в зависимости от содержимого регистра 7. Одновременно с запуском распределителя импульсов информация с шины 21 адреса данных ЭВМ через формирователи 20 поступает на регистр 6. Если адресован регистр 5 управления, что определяет дешифра0

тор 76, н его выходе появляется им-

пульс на выходе 32 стробирования регистра управления, если же адресована буферная память 46,то адрес ячейки памяти поступает с регистра 7 через счетчик 50 и регистр 51 на адресные входы буферной памяти, на его входе 31 Нормируется импульс записи формирователем 77. В заключительной фазе работы распределителя 73 импульсов по импульсу на выходе 33 запускается триггер 65, с выхода которого через буферный формирователь 60 на шину ЭВМ поступит сигнал к СИПн на выход 37. Сигнал к СШТн с выхода 37 снимается, как только окончится сигнал к ВЫВОДн на входе 43, а по Ькончанию сигнала к СИАн на входе 42 устанавливается в исходное состояние триггер 63 и цикл обмена по программному каналу оканчивается.

Пля обеспечения обмена командами и данными между модулями в Крейте в контроллер включен блок 19 представления управления магистралью Крейта,

включающий буферную память 46. Количество адресов буферной памяти 46 не менее количества модулей в Крей- те, причем каждому модулю соответствует свой адрес буферной памяти. По каждому адресу буферной памяти, соответствующему модулям, которым предоставлено право управления Крей- том, заносится управляющее слово запроса, содержащее маску запроса и код функции управления.

Информация в буферную память заносится в режиме программного обмена как было описано и может оперативно меняться в процессе работы.

Тактовые импульсы на выходе 30 с генератора 75 через одновибратор А5 постоянно поступают на счетный вход счетчика 50, код с которого через регистр 51 поступает на адресный вход буферной памяти 46 и управ- ляющий вход коммутатора 54.Коммутатор 54 подключает один из входов 26 запросов от модулей в Крейте на один из входов элемент И-НЕ 48.Од- новременно на входах буферной памяти 46 появляется управляющее слово запроса, соответствующее модулю, выход запроса которого в этот момен выбран коммутатором. Первый и второй разряды управляющего слова запросов, соответствующие коду функции управления, поступают на дешифратор 47 и с его выхода на вход И-НЕ 48. На другой вход элемента И-НЕ 48 поступает третий разряд управляющего слова запроса, соответствующий маске запроса, В случае, если на входе 26 запроса, подключенном коммутатором 54 на его выход, присутствует запрос на обслуживание (единица на выходе коммутатора 54), дешифратор 47 обнаруживает, что соответствующий запрос является запросом модуля на управление магистралью Крейта (единица на выходе дешифратора 47) и маска запроса открыта (единица на третьем выходе буферной памяти 46), на выходе элемента И-НЕ 48 появляется низкий уровень, который запрещает од- новибратору 45 формирование импульсов пересчета счетчика 50. Следующим тактовым импульсов на выходе 30 в регистр 52 заносится информация 6 запросе от модуля на управление мгистралью Крейта, причем если этот запрос обнаруживается во время обмена контроллера с ЭВМ по программному каналу благодаря элементу НЕ-И 56, это гроисходит только после окончания, обмена по программному каналу, т.е. когда сбрасывается триггер 63

и снимается сигнал с выхода 38. Выходы регистра 52 поступают на элемент И-НЕ 49 и формируют сигнал на выходе 27, по началу которого формирователь 64 формирует задержанный импульс . па выходе 39 запуска распределителя 73 импульсов. Кроме того, сигнал с выхода 27 поступает на вход управления направлением приема информации регистра 13, а формирователь

68 формирует импульс на выходе 36 записи в регистры 7, 10, 13. По этому импульсу в регистр 7 записывается нулевой код адреса, в регистр 10 код функции 4 чтения, а в регистр 13 номер модуля, с которого поступил запрос, равный коду, храняющемуся в регистре 51. Распределитель 73 импульсов формирует цикл обращения к модулю, запросивщему запрос, при

котором модуль выставляет на шины 3 чтения команду, с которой он должен обратиться к магистрали Крейта. Эта команда через усилители 1 поступает на входы регистров 7, 10и13, а в

конце цикла задним фронтом импульса с выхода 33 формирователь 68 формирует импульс записи в эти регистры и запоминается новая команда. Кроме того, во время цикла чтения команды

модуль должен выставить сигнал на входе 44 подтверждения получения права на управление магистралью Крейта и одновременно снять сигнал запроса на внимание, при этом элемент

И-НЕ 48 разрешает работу одновибра- тора 45 и начинается поиск очередного запроса. Теперь выполнены все условия, чтобы элемент НЕ-И 55 сформировал сигнал на входе 28,разрешаю-г

щий работу распределителя 73 импульсов непрерывно. Таким образом, организуются передача блока данных между модулем 80, запросившим управлет ние, и функциональным модулем 81 через входы 3, усилители 1, внутреннкио шину 23, усилители 2 и выходы 4.Обмен блоком данных идет с максимальной скоростью, допускаемой магистралью Крейта и контроллером без разрыВОВ между отдельными циклами на магистрали Крейта,

Передача блока данных может быть прервана в следующих случаях.

1. Передача блока данных окончена. При этом во время передачи последнего слова данных сигнал на входе 44 модулем 80 снимается, в резул тате на выходе элемента НЕ-И 55 сигнал на выходе 28 также снимается.Работа распределителя 73 импульсов после окончания очередного цикла запрещена, сигнал на выходе 29 оканчи- вается и тактовые импульсы на выходе 30 через элемент ИЛИ 53 поступают на стробирующий вход регистра 52. Код на выходе регистра изменяется и сигнал на выходе 27 оканчивается.

Таким образом, передача блока данных }5 ходных буферных усилителей данных.

завершена.

2.Во время передачи блока данны происходит обращение к контроллеру Крейта от ЭВМ по программному каналу. В этом случае формирование сигнала на выходе 28 на выходе элемент НЕ-И 55 запрещено сигналом на выходе 38 с выхода триггера 63. Обмен

по программному каналу начинается только после окончания цикла передачи слова данных, при котором появля- .ется адрес контроллера на шине ЭВМ.

3.Во время передачи блока данных обнаружен запрос от другого модуля в Крейте на управление магистралью . В этом случае формирование сигнала на выходе 28 на выходе элемента НЕ-И 55 запрещено сигналом с выхода элемента НЕ-И 56. По окончании цикла передачи слова данных в регистр 52 вновь заносится код запроса на управление магистралью и вновь формируется сигнал на выходе 27. Происходит предоставление маги;страли Крейта новому источнику запроса (как было описано ранее).

Во втором и третьем случае обмен блоком данных не оканчивается. Поэтому модуль, сняв сигнал на входе 44, должен выставить вновь сигнал запроса на внимание. Контроллер,обнаружив этот сигнал, вновь предоставляет этому модулю магистраль Крейта, чтобы продолжить передачу блока данных. Таким образом, длинные блоки данных могут неоднократно прерываться. Передача отдельных слов или коротких блоков данных происходит за один раз.

Формула изобретения

1. Устройство для сопряжения электронно-вычислительной машины (ЭВМ)

с периЛерийными устройствами, содержащее входной буферный усилитель данных, выходной буферный усилитель данных, выходной буферный усилитель адреса, выходной буферный усилитель данных функций, регистр управления, регистр адреса, шинные формирователи, дешифратор номера, регистр номера, регистр данных, блок связи с ЭВМ, блок управления, причем информационный вход входного буферного усилителя данных подключен к информационным выходам периферийных устройств , информационные выходы выадреса и функций подключены к информационным, адресным и управляющим входам периферийных устройств соответственно, группа информационных

выходов дешифратора номера подключена к входам выборки периферийных устройств, информационные входы шинных формирователей подключены к информационной шине ЭВМ, входы выборки,

синхронизации и вывода блока связи с ЭВМ подключены к выходам выборки, синхронизации и выводам ЭВМ соответственно, первый синхровыход блока связи с ЭВМ подключен к входу синхронизации ЭВМ, при этом информационный выход входного буферного усилителя данных соединен с информационными входами выходного буферного усилителя данных, регистра адреса, регистра

управления, с первым информационным входом регистра номера и с информационным выходом регистра данных, информационные выходы шинных формирователей соединены с информационными

входами регистра данных и информационным входом блока связи с ЭВМ, второй синхровыход которого соединен с синхровходом регистра данных,вход сброса которого соединен с установочным выходом блока связи с ЭВМ, выход запуска и тактовый выход которого соединен с первым входом запуска и первым тактовым входом блока управления соответственно, вход кодовых

условий которого соединен с. информационным выходом регистра адреса и информационным входом выходного буферного усилителя адреса, разрешающий вход которого соединен с разрешающим

входом выходного буферного усилителя функций, стробирующим входом дешифратора номера, разрешающим входом блока связи с ЭВМ и первым выходом блока управления, второй выход которого

соединен с стробирующим входом блока связи с ЭВМ, установочный вход которого соединен с третьим выходом блока управления, четвертый выход которого соединен с синхровходом регистра, управления, разрешающий и вто рой тактовый входы блока управления- соединены с первым и вторым информационными выходами дешифратора номера соответственно, информационный вход которого соединен с информационным выходом регистра номера, синхро- вход которого соединен с синхровходо регистра адреса и с третьим синхровхдом блока связи с ЭВМ, отлича- ю щ е е с я тем, что, с целью повышения быстродействия, в него вв едены регистр функций., блок предоставления управления и элемент И, причем групп

входов запросов блока предоставления управления подключена к выходам за- -просов периферийных устройств,первый разрешающий вход блока предоставления управления подключен к выходам разрешения периферийных устройств, при этом разрешающий выход блока связи с ЭВМ соединен с разрешающим входом регистра функций и вторым разрешающим входом блока предоставления управления, первый информаци- онньй вход которого соединен формационным выходом регистра данных и с первым информационным входом регистра функций; второй информацион- ныйг вход которого соединен с информационным выходом регистра управления, информационный вход выходного буферного усилителя функций соединен с информационным выходом регистра функций, синхровход которого соединен с третьим синхровыходом блока связи с ЭВМ, вход запуска которого соединен с разрешающим входом выходного б ферного усилителя данных, с разрешающим входом регистра номера, с разрешающим выходом блока предоставления управления, с первым входом элемента И, второй В1СОД которого соединен с первым выходом блока управления, второй вход запуска которого соединен с выходом запуска блока предоставления управления, стробирующий вход которого соединен с вторым выходом блока управления, пятый выход которого соединен с первым входом записи блока предоставления управления, второй вход записи которого соединен с первым информационным выходом дешифра

тора номера, выход элемента И соединен г разрешающим входом входного буферного усилителя данных, информационный выход регистра адреса соединен с вторым информационным входом блока предоставления управления, информационный выход которого соединен с вторым информационным входом регистра номера, причем блок предоставления управления содержит буферную память, дешифратор, коммутатор, два регистра, счетчик, одновибратор, элемент ИЛИ, два элемента И-НЕ, два элемента НЕ-И, причем синхровход од- новибратора соединен с первым входом элемента ИЛИ и является стробирующим входом блока предоставления управления, информационный вход буферной памяти и информационный вход счетчика являются первым и вторым информационными входами блока предоставления управления соответственно, входы записи буферной памяти и счетчика являются первым и вторым

входами записи блока предоставления управления соответственно, первый вход первого элемента НЕ-И является первым разрешающим входом блока предоставления управления, второй

вход первого элемента НЕ-И соединен с первым входом второго элемента НЕ- И и является вторым разрешающим входом блока предоставления управления, второй вход элемента ИЛИ является

третьим разрешающим входом блока предоставления управления, информационный выход первого регистра соединен с управляющим входом коммутатора, с адресным входом буферной памяти

и является информационным выходом блока предоставления управления, груТ па информационных входов коммутатора образует группу входов запросов блока предоставления управления, выход

первого элемента И-НЕ соединен с третьим входом первого элемента НЕ-И и является выходом резрешения блока предоставления управления, выход первого элемента НЕ-И является выходом запуска блока предоставления управления, при этом в блоке предостав-г ления управления выход элемента ШШ соединен с синхровходом второго регистра, первый информационный вход

которого соединен с четвертым входом первого элемента НЕ-И и с выходом второго элемента НЕ-И, второй вход которого соединен с выходом второго элемента И-НЕ и с разрешаюп им входом

одновибратора, выход которого соединен с синхровходом первого регистра и со счетным входом счетчика, выход которого соединен с информационным входом первого регистра, первый и второй входы первого элемента И-НЕ соединены с первым и вторым выходами второго регистра соответственно,второй информационный вход которого соединен с цервым информационным выхо- дом буферной памяти и с первым входом дешифратора, второй вход которог соединен с первым информационным выходом буферной памяти, третий информационный выход которой соединен с первым входом второго элемента И-НЕ, второй и третий входы которого соединены с выходами дешифратора и коммутатора соответственно,

2, Устройство поп,1, отличающееся тем, что блок управления содержит генератор импульсов, дешифратор, два регистра, триггер, элемент ИЛИ, два элемента И, два эле мента НЕ-И, элемент И-НЕ, причем первый и второй входы элемента ИЛИ являются первым и вторым входами за- пуска блока управления, первый управляющий вход дешифратора соединен с первым входом элемента И-НЕ и является первым тактовым входом блока управления, второй управляющий вход дешифратора является вторым тактовым входом блока управления, информацион- ный вход дешифратора является входом кодовых условий блока управления, первый единичный выход триггера соединен с нулевыми входами первого и второго регистров, с первым информа- ционным входом триггера и является первым выходом блока управления, первый вход первого элемента НЕ-И явля-ч ется разрешающим входом блока управления, выход генератора импульсов соединен с синхровходом триггера, с первым входом первого элемента И и является вторым выходом блока управления, первый единичный выход второго регистра является третьим выходом блока управления, выход дешифратора является четвертым выходом блока управления, выход элемента И-НЕ является пятым виходом блока управления, при этом в блоке управления выход элемента ИЛИ соединен с первым входом второго элемента НЕ-И и с вторым информационным входом триггера, третий информационный вход которого соединен с выходом второго элемента НЕ-И, второй вход которого соединен с первым нулевым выходом второго регистра и с первым информационным входом первого регистра, второй и третий информационные входы которого соединены с первыми нулевыми и еди- ничными выходами первого регистра соответственно, второй нулевой выход которого соединен с первым информационным входом второго регистра и с вторым входом элемента И-НЕ,третий выход которого соединен с выходом первого элемента НЕ-И, второй вход которого соединен с вторым единичным выходом первого регистра,третий единичный выход которого соединен с вторым информационным входом . второго регистра, третий информационный вход которого соединен с вторым единичным выходом второго регистра, третий единичный выход которого со-- единен с четвертым ц 1формационным входом первого регистра и с первым входом второго элемента И, выход которого соединен с четвертым информационным входом второго регистра, синхровход которого соединен с синхровходом первого регистра и с нулевым выходом триггера, второй единичный выход которого соединен с вторым входом первого элемента И, выход которого соединен с четвертью элементом И-НЕ, четвертый единичный выход первого регистра соединен с третьим управляющим входом дешифратора, второй нулевой выход второго регистра соединен с вторым входом второго элемента И.

.3

53

73

79

во

W jmiuirmjmnnnnnnjiririJuijmriJL

80

81

81

61

JL

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1991 |

|

SU1837303A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения масс-спектрометра с ЭВМ | 1988 |

|

SU1580379A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1381534A1 |

Изобретение относится к области вычислительной техники,.в частности к вопросам построения информационно-измерительных систем, и может быть использовано при проектировании контроллеров Крейта в системе КАМАК. Целью изобретения является повьшение быстродействия.Устройство содержит входной буферный усилитель данных, выходной буферный усилитель данных, выходные буферные усилители адреса и функций, регистр данных, регистр управления, регистр адреса, регистр функций, регистр номера,- дешифратор номера, нижние формирователи, блок управления, блок предоставления управления, блок свя зи с ЭВМ, элемент И. 1 з.п. ф-льт, 7 ил. W О эо сд 4 X

7J. f - J7.

7J. 7 . 47.

TJ

LI

Риг 6

30 ЛПЛ 1ЛПГШтПЛЛ 1Л

5-1ППГ1ГШЛЛЛЛ ШЛЛЛГ111ГитГ

| Устройство для сопряжения периферийной системы с электронной вычислительной машиной | 1975 |

|

SU554534A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство управления периферийной системой | 1975 |

|

SU590724A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-23—Публикация

1985-05-20—Подача