Изобретение относится к радиотехнике и может быть использовано в радиолокации и в системах дальней связи при построении широкодиапазонных генераторов синусоидальных колебаний с прецизионной формой кривой выходного сигнала.

Цель изобретения.- расширение диапазона генерируемых частот и повышение спектральной чистоты выходного сигнала.

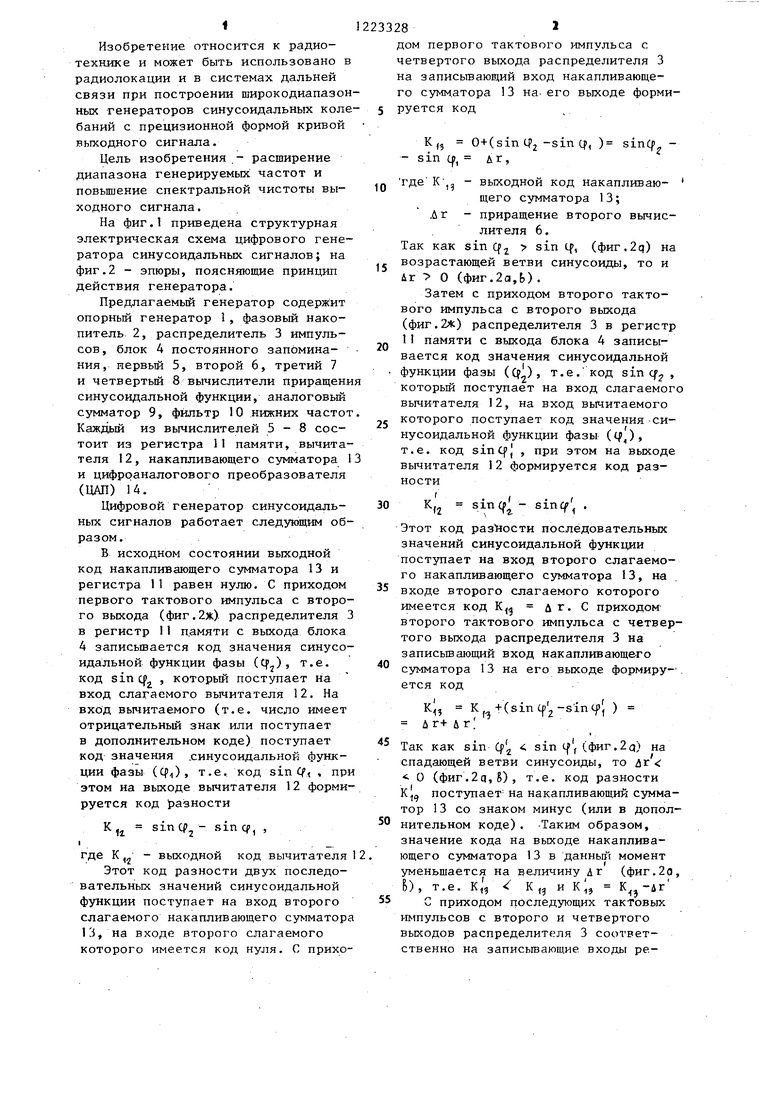

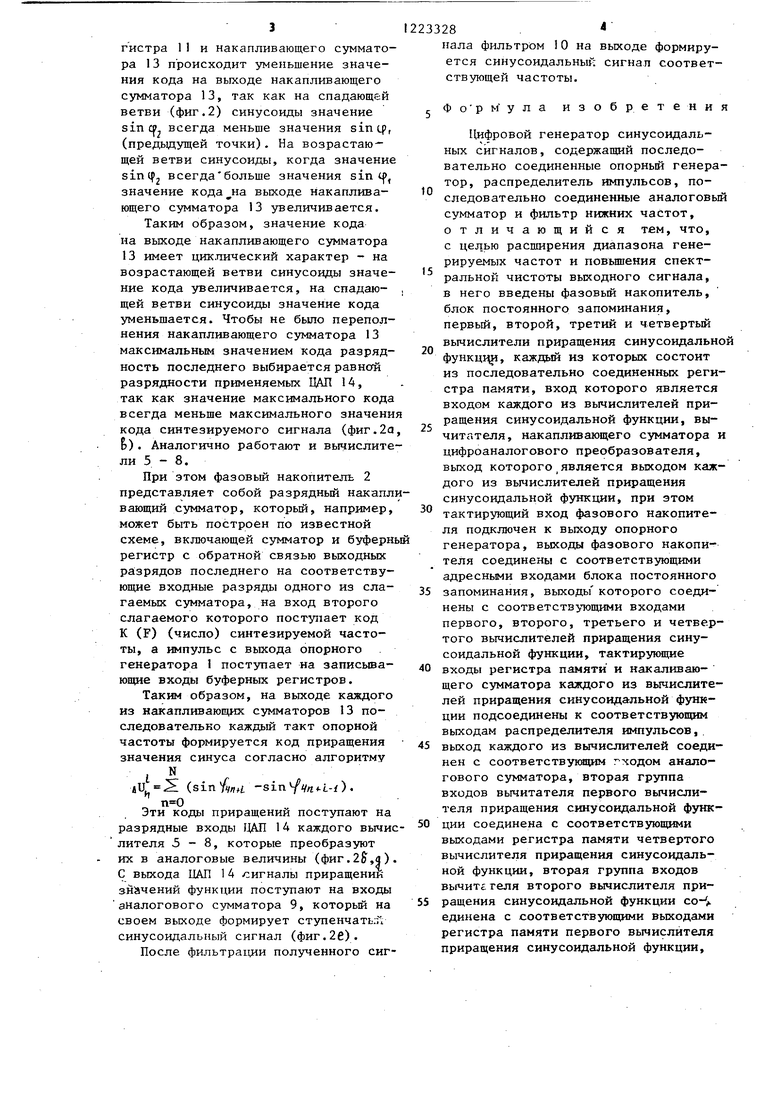

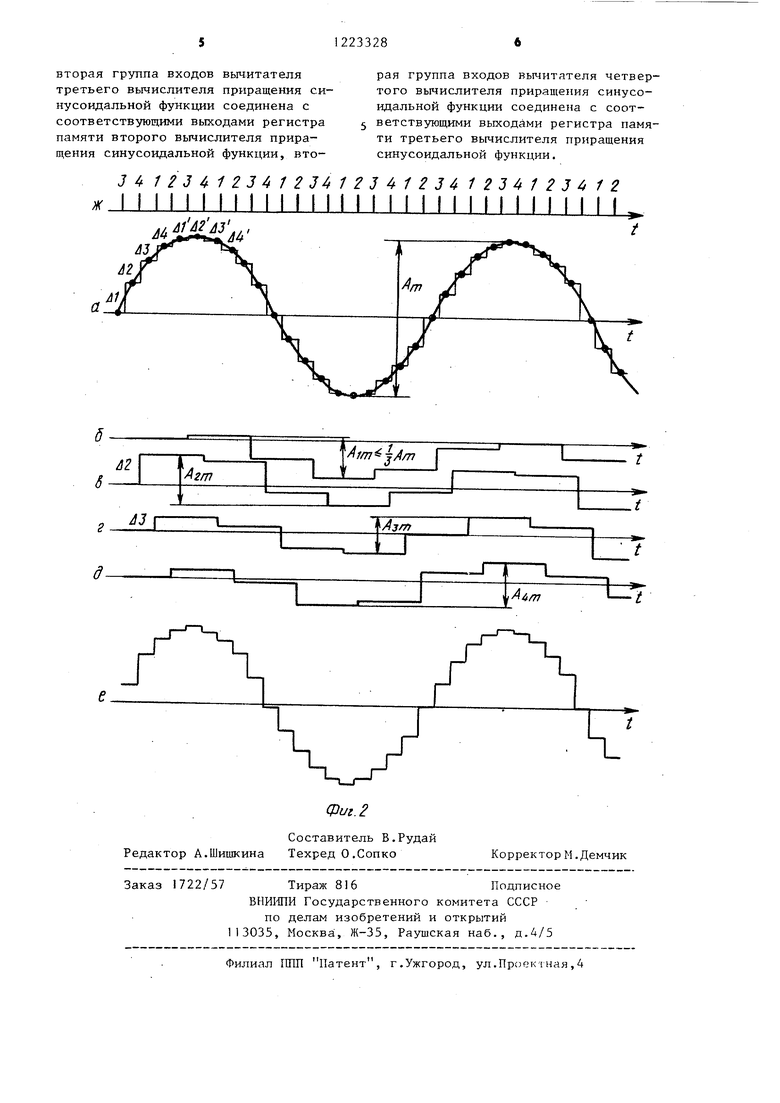

На фиг.1 приведена структурная электрическая схема цифрового генератора синусоидальных сигналов; на фиг.2 - эпюры, поясняющие принцип действия генератора.

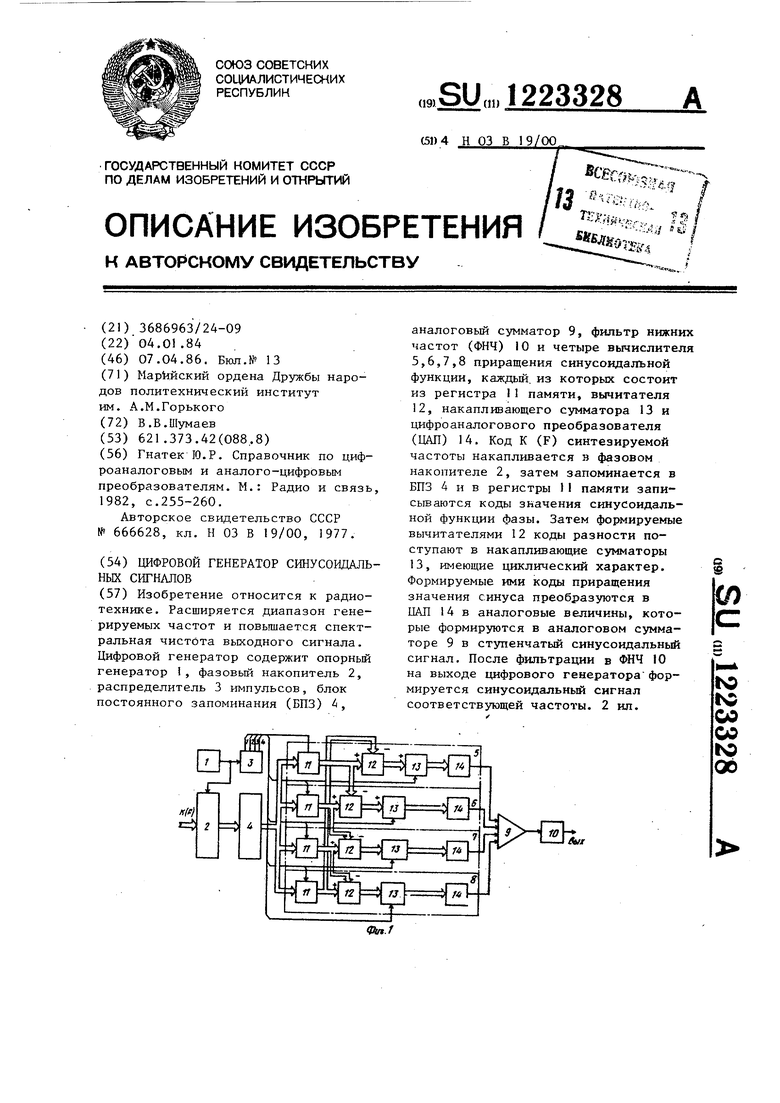

Предлагаемый генератор содержит опорный генератор 1, фазовый накопитель 2, распределитель 3 импульсов , блок 4 постоянного запоминания, первый 5, второй 6, третий 7 и четвертый 8 вычислители приращени синусоидальной функции, аналоговый сумматор 9, фильтр 10 нижних частот Каждый из вычислителей 5 - 8 состоит из регистра 11 памяти, вычита- теля 12, накапливающего сумматора 1 и цифрраналогового преобразователя (ЦАП) U.

Цифровой генератор синусоидальных сигналов работает следующим образом.

В исходном состоянии выходной код накапливающего сумматора 13 и регистра 11 равен нулю. С приходом первого тактового импульса с второго вьсхода (фиг.2ж) распределителя 3 в регистр I1 памяти с выхода блока 4 записьшается код значения синусоидальной функции фазы (4 j), т.е. код sincf , который поступает на вход слагаемого вычитателя 12. На вход вычитаемого (т.е. число имеет отрицательный знак или поступает в дополнительном коде) поступает код значения .синусоидальной функции фазы (Cf), т.е. код sin О, , при этом на выходе вычитателя 12 формируется код разности

К

11

sin СР - sin cf, ,

где К - выходной код вычитателя 1 2,

Этот код разности двух последовательных значений синусоидальной функции поступает на вход второго слагаемого накапливающего сумматора 13, на входе второго слагаемого которого имеется код нуля. С прихо12233282

дом первого тактового импульса с четвертого выхода распределителя 3 на записьшающий вход накапливающего сумм.атора 13 на его выходе формируется код

К.(, 0+(sin ср siri Ч ) sinCf - - sin q), Аг,

где К , - выходной код накапливаю-

щего сумматора 13; ,й г - приращение второго вычислителя 6,

Так как sin qij sin ц, (фиг.2д) на , возрастающей ветви синусоиды, то и Лг О (фиг.2а,Е) .

Затем с приходом второго тактового импульса с второго выхода (фиг.2ж) распределителя 3 в регистр 11 памяти с выхода блока 4 записывается код значения синусоидальной функции фазы (Q ), т.е. код sin q- , который поступает на вход слагаемого вычитателя 12, на вход вычитаемого которого поступает код значения синусоидальной функции фазы (t,), т.е. код sinCp, , при этом на выходе вычитателя 12 формируется код разности

0

5

2 Этот код разТности последовательных значений синусоидальной функции поступает на вход второго слагаемого накапливающего сумматора 13, на входе второго слагаемого которого имеется код К д г. С приходом второго тактового импульса с четвертого выхода распределителя 3 на записьшающий вход накапливающего сумматора 13 на его выходе формиру- . ется код

i Kj +CsinCf. j-sin J ) ir+ &г;

5

Так как sin Cf2 sin t|i, (фиг.2(з) на спадающей ветви синусоиды, то лг О (фиг.2а,6), т.е. код разности к|д поступает на накапливающий сумматор 13 со знаком минус (или в допол- 0 нительном коде). -Таким образом, значение кода на выходе накапливающего сумматора 13 в данный момент уменьшается на величину дг (фиг.2о.

5

&),

т.е. К

К

Э

и К

1

К,,-4Г

С приходом последзпощих тактовых импульсов с второго и четвертого выходов распределителя 3 соответственно на записьгоающие входы рег истра 1 1 и накапливающего сумматора 13 происходит уменьшение значения кода на выходе накапливающего сумматора 13, так как на спадающей ветви (фиг.2) синусоиды значение sin ср всегда меньше значения sintf, (предыдущей точки). На возрастающей ветви синусоиды, когда значение sin( всегда больше значения sin tj) значение выходе накапливающего сумматора 13 увеличивается.

Таким образом, значение кода на выходе накапливающего сумматора 13 имеет циклический характер - на возрастающей ветви синусоиды значение кода увеличивается, на спадаю- , щей ветви синусоиды значение кода уменьшается. Чтобы не было переполнения накапливающего сумматора 13 максимальным значением кода разрядность последнего выбирается равной разрядности применяемых ЦАП 14, так как значение максимального кода всегда меньше максимального значения кода синтезируемого сигнала (фиг.2а, D). Аналогично работают и вычислители 5 - 8.

При этом фазовый накопитель 2 представляет собой разрядный накапливающий сумматор, которьй, например, может быть построен по известной схеме, включающей сумматор и буферный регистр с обратной связью выходных ра:зрядов последнего на соответствующие входные разряды одного из слагаемых сумматора, на вход второго слагаемого которого поступает код К (F) (число) синтезируемой частоты, а импульс с выхода опорного генератора 1 поступает на записывающие входы буферных регистров.

Таким образом, на выходе каждого из накапливающих сумматоров 13 последовательно каждый такт опорной частоты формируется код приращения значения синуса согласно алгоритму

I N iU S ( -sin i/n -L-i ).

Эти коды приращений поступают на

азрядные входы 1ДАП 14 каждого вычисителя 5-8, которые преобразуют х в аналоговые величины (фиг.28,а ). выхода ШШ 14 /сигналы приращении йачений функции поступают на входы налогового сумматора 9, который на воем выходе формирует ступенчать;;; инусоидальный сигнал (фиг.26).

После фильтрации полученного сиг0

5

0

5

0

5

0

5

нала фильтром IО на выходе формируется синусоидальный сигнал соответствующей частоты.

Фо рм ула изобретения

Цифровой генератор синусоидальных сигналов, содержащий последовательно соединенные опорньй генератор, распределитель импульсов, последовательно соединенные аналоговый сумматор и фильтр нижних частот, отличающийся тем, что, с целью расширения диапазона генерируемых частот и повышения спектральной чистоты выходного сигнала, в него введены фазовый накопитель, блок постоянного запоминания, первый, второй, третий и четвертый вычислители приращения синусоидальной функц, каждый из которых состоит из последовательно соединенных регистра памяти, вход которого является входом каждого из вычислителей приращения синусоидальной функции, вы- читателя, накапливающего сумматора и цифроаналогового преобразователя, выход которого,является выходом каждого из вычислителей приращения синусоидальной функции, при этом тактирующий вход фазового накопителя подключен к выходу опорного генератора, выходы фазового накопителя соединены с соответствующими адресными входами блока постоянного запоминания, выходы которого соединены с соответствующими входами первого, второго, третьего и четвертого вычислителей приращения синусоидальной функции, тактирующие входы регистра памяти и накаливаю- щего сумматора каждого из вычислителей приращения синусоидальной функции подсоединены к соответствующим выходам распределителя импульсов,. выход каждого из вычислителей соединен с соответствукщим гходом аналогового сумматора, вторая группа входов вычитателя первого вычислителя приращения синусоидальной функции соединена с соответствующими выходами регистра памяти четвертого вычислителя приращения синусоидальной функции, вторая группа входов вычитг теля второго вычислителя приращения синусоидальной функции co-V единена с соответствующими выходами регистра памяти первого вычислителя приращения синусоидальной функции.

вторая группа входов вычитателя третьего вычислителя приращения синусоидальной функции соединена с соответствующими выходами регистра памяти второго вычислителя приращения синусоидальной функции, втоJ4 12J41234r2J412341234 1 2 3 4 f 2 J 12

И I И I I t I И I ММ I И I I I I I И I И i I I

рая группа входов вычитателя четвертого вычислителя приращения синусоидальной функции соединена с соот- ветствующими выходами регистра памяти третьего вычислителя приращения синусоидальной функции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор сигналов | 1988 |

|

SU1626314A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1394393A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1988 |

|

SU1647901A1 |

| Устройство для формирования базисно-тригонометрических функций | 1990 |

|

SU1792542A3 |

| Устройство для выполнения преобразования Фурье | 1987 |

|

SU1424027A1 |

| Устройство для отображения графической информации на газоразрядной индикаторной панели | 1982 |

|

SU1108488A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Цифровой синтезатор частот | 1983 |

|

SU1190457A1 |

Изобретение относится к радиотехнике. Расширяется диапазон генерируемых частот и повышается спектральная чистота выходного сигнала. Цифровой генератор содержит опорньш генератор 1, фазовый накопитель 2, распределитель 3 импульсов, блок постоянного запоминания (БПЗ) 4, «( } аналоговый сумматор 9, фильтр нижних частот (ФНЧ) 10 и четыре вычислителя 5,6,7,8 приращения синусоидальной функции, каждый, из которых состоит из регистра 11 памяти, вычитателя 12,накапливающего сумматора 13 и цифроаналогового преобразователя (ЦАП) 14. Код К (F) синтезируемой частоты накапливается в фазовом накопителе 2, затем запоминается в БПЗ 4 и в регистры 1I памяти записываются коды значения синусоидальной функции фазы. Затем формируемые вычитателями 12 коды разности поступают в накапливающие сумматоры 13,имеющие циклический характер. Формируемые ими коды приращения значения синуса преобразуются в 11АП 14 в аналоговые величины, которые формируются в аналоговом сумматоре 9 в ступенчатый синусоидальный сигнал. После фильтрации в ФНЧ 10 на выходе цифрового генератора формируется синусоидальный сигнал соответствующей частоты. 2 нл. i W N9 tC 00 СА to 00

Редактор А.Шишкина

фиг. 2

Составитель В.Рудай Техред О.Сопко

Заказ 1722/57 Тирал 816Подписное

ВИИШИ Государственного комитета СССР

по делам изобретений и открытий 1)3035, Москва:, Ж-35, Раушская наб., д.4/5

Филиал ГШП Патент, г.Ужгород, ул.Проектная,4

Корректор М.Демчик

| Гнатек Ю.Р | |||

| Справочник по циф- роаналоговым и аналого-цифровым преобразователям | |||

| М.: Радио и связь, 1982, с.255-260 | |||

| Цифровой генератор синусоидального сигнала | 1977 |

|

SU666628A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-07—Публикация

1984-01-04—Подача