Ь5

ел

со со

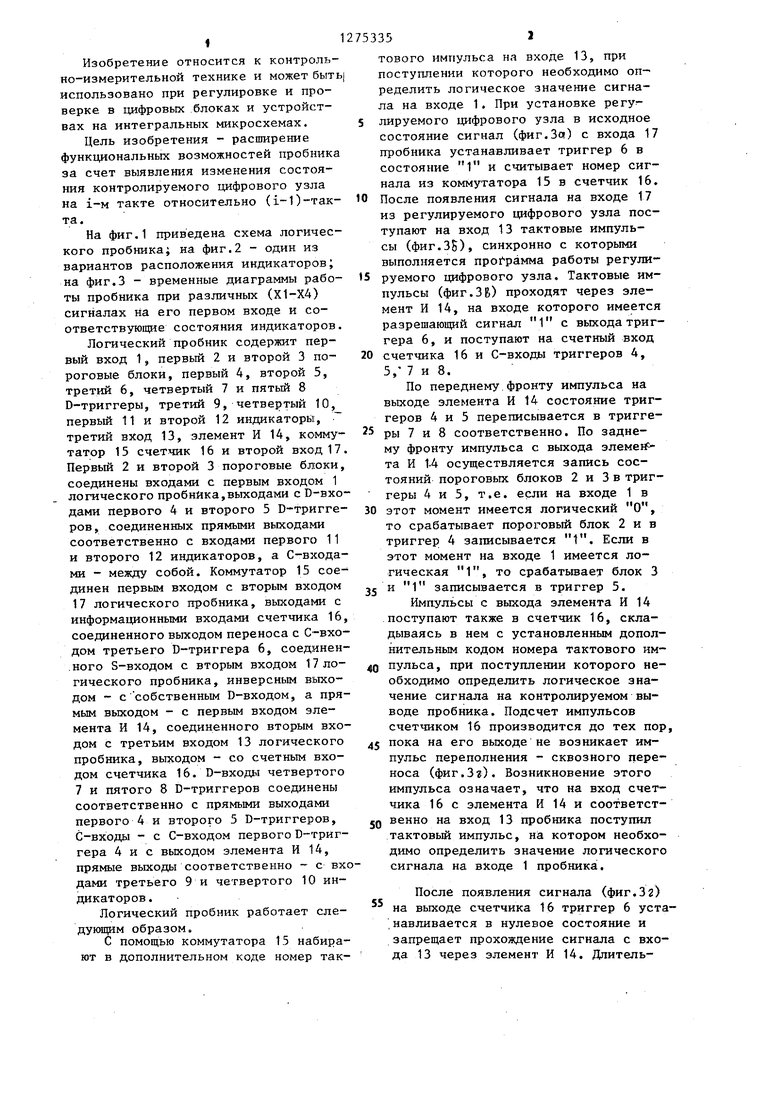

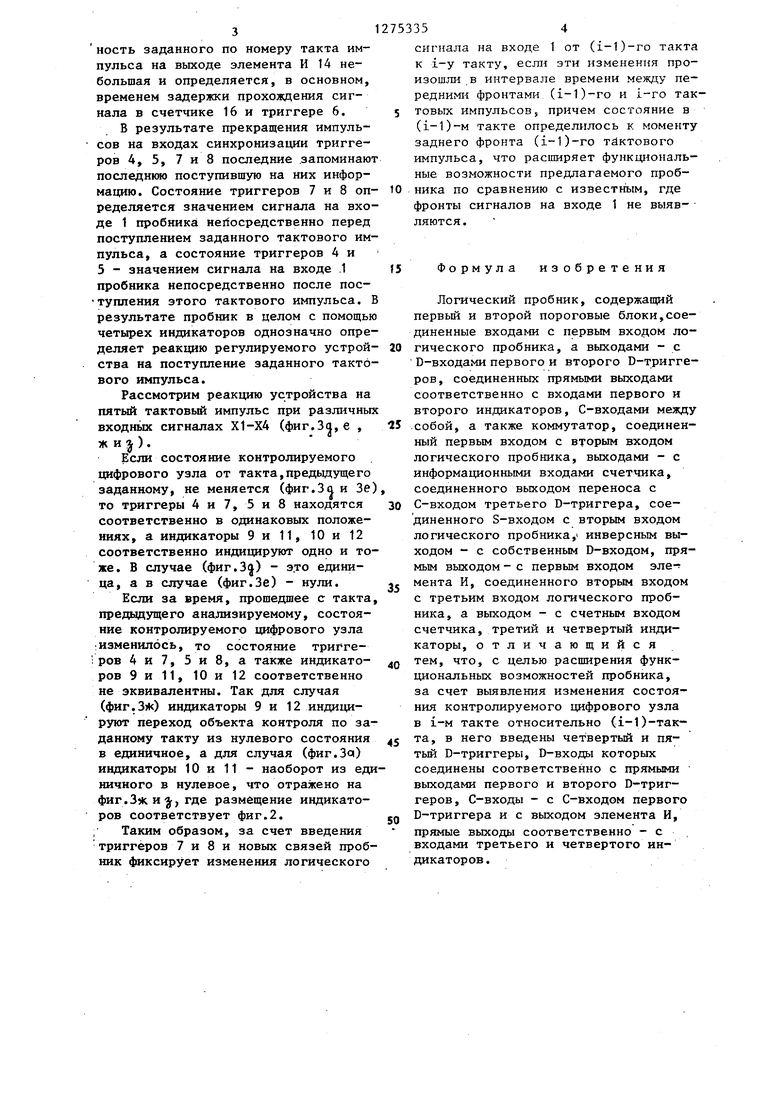

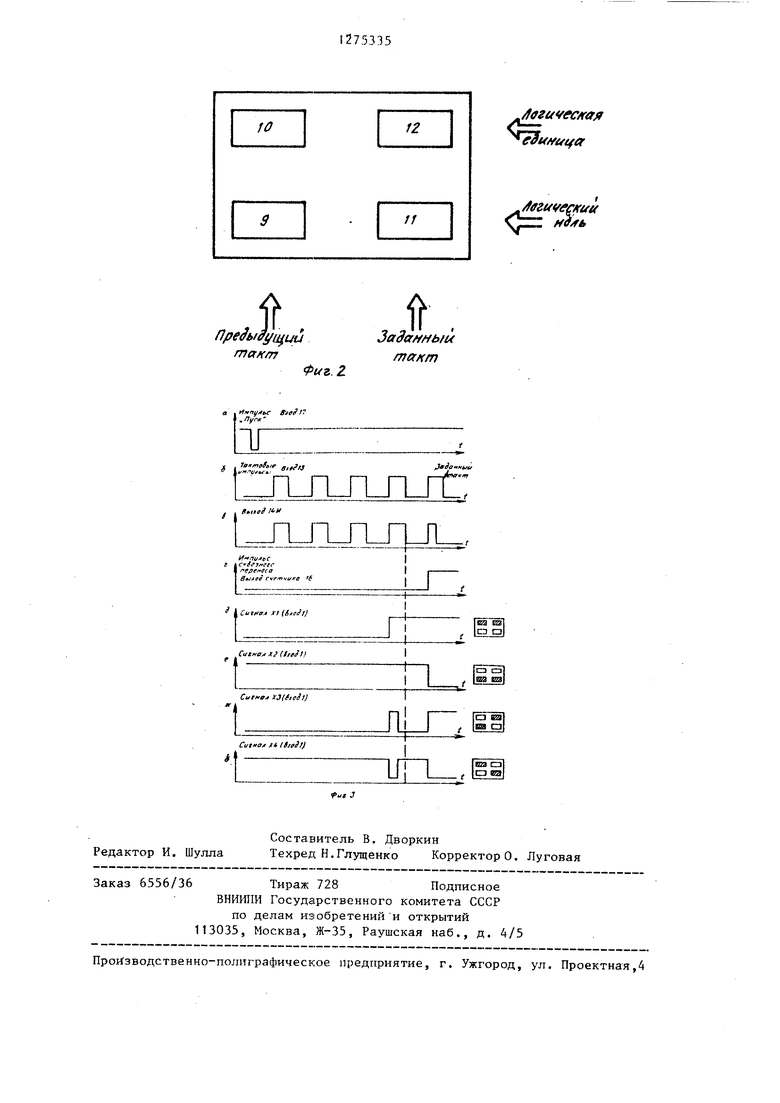

ел I Изобретение относится к контрольно-измерительной технике и может быть использовано при регулировке и проверке в цифровьк блоках и устройствах на интегральных микросхемах. Цель изобретения - расширение функциональных возможностей пробника за счет выявления изменения состояния контролируемого цифрового узла на i-M такте относительно (i-1)-такта. На фиг.1 приведена схема логического пробника; на фиг.2 - один из вариантов расположения индикаторов; на фиг.З - временные диаграммы работы пробника при различных (Х1-ХА) сигналах на его первом входа и соответствующие состояния индикаторов. Логический пробник содержит первый вход 1, первый 2 и второй 3 пороговые блоки, первый 4, второй 5, третий 6, четвертый 7 и пятый 8 D-триггеры, третий 9, четвертый 10, первый 11 и второй 12 индикатора, третий вход 13, элемент И 14, коммутатор 15 счетчик 16 и второй вхо-д 17 Первь1й 2 и второй 3 пороговые блоки, соединены входами с первым входом 1 логического пробника,выходами с D-BXO дами первого 4 и второго 5 D-триггеров, соединенных прямыми выходами соответственно с входами первого 11 и второго 12 индикаторов, а С-входами - между собой. Коммутатор 15 соединен первым входом с вторым входом 17 логического пробника, выxoдalvш с информационными входами счетчика 16 соединенного выходом переноса с С-входом третьего D-триггера 6, соединен.ного S-входом с вторым входом 17 логического пробника, инверсным выходом - ссобственным D-входом, а прямым выходом - с первым входом элемента И 14, соединенного вторым входом с третьим входом 13 логического пробника, выходом - со счетным входом счетчика 16. D-входы четвертого 7 и пятого 8 D-триггеров соединены соответственно с прямыми выходами первого 4 и второго 5 D-триггеров, С-входы - с С-входом первого D-триггера 4 и с вькодом элемента И 14, прямые выходы соответственно - с вх дами третьего 9 и четвертого 10 индикаторов . Логический пробник работает следующим образом. С помощью коммутатора 15 набирают в дополнительном коде номер так35Iтового импульса на входе 13, при поступлении которого необходимо определить логическое значение сигнала на входе 1« При установке регу лируемого цифрового узла в исходное состояние сигнал (фиг.Зд) с входа 17 пробника устанавливает триггер 6 в состояние 1 и считывает номер сигнала из коммутатора 15 в счетчик 16. После появления сигнала на входе 17 из регулируемого цифрового узла поступают на вход 13 тактовые импульсы (фиг.35), синхронно с которыми выполняется npotpaMMa работы регулируемого цифрового узла. Тактовые импульсы (фиг.ЗР) проходят через элемент И 14, на входе которого имеется разрешающий сигнал 1 с выхода триггера 6, и поступают на счетный вход счетчика 16 и С-входы триггеров 4, 5, 7 и 8. По переднему.фронту импульса на выходе элемента И 14 состояние триггеров 4 и 5 переписывается в триггерь1 7 и 8 соответственно. По заднему фронту импульса с выхода элемента И 1-4 осуществляется запись состояний пороговых блоков 2 и 3 в триггеры 4 и 5, т.е. если на входе 1 в этот момент имеется логический О, то срабатывает пороговый блок 2 и в триггер 4 записывается 1. Если в этот момент на входе 1 имеется логическая 1, то срабатьшает блок 3 и 1 записывается в триггер 5. Имаульсы с выхода элемента И 14 поступают также в счетчик 16, складываясь в нем с установленным дополнительным кодом номера тактового импульса, при поступлении которого необходимо определить логическое значение сигнала на контролируемом выводе пробника. Подсчет импульсов счетчиком 16 производится до тех пор, пока на его выходе не возникает импульс переполнения - сквозного переноса (фиг.Зг). Возникновение этого импульса означает, что на вход счетчика 16 с элемента И 14 и соответственно на вход 13 пробника поступил тактовьй импульс, на котором необходимо определить значение логического сигнала на входе 1 пробника. После появления сигнала (фиг.Зг) на выходе счетчика 16 триггер 6 уста,навливается в нулевое состояние и запрещает прохождение сигнала с входа 13 через элемент И 14. Длительность заданного по номеру такта импульса на выходе элемента И 14 небольшая и определяется, в основном, временем задержки прохождения сигнала в счетчике 16 и триггере 6. В результате прекращения импульсов на входах синхронизации триггеров 4, 5, 7 и 8 последние .запоминают последнкяо поступившую на них информацию. Состояние триггеров 7 и 8 определяется значением сигнала на входе 1 пробника непосредственно перед поступлением заданного тактового импульса, а состояние триггеров 4 и 5 - значением сигнала на входе .1 пробника непосредственно после постугатения этого тактового импульса. В результате пробник в целом с помощью четырех индикаторов однозначно определяет реакцию регулируемого устройства на поступление заданного тактового импульса. Рассмотрим реакцию устройства на пятый тактовый импульс при различных входньк сигналах Х1-Х4 (фиг.За,е , Ж и ). Если состояние контролируемого цифрового узла от такта,предьщущего заданному, не меняется (фиг.За и Зе) то триггеры 4 и 7, 5 и 8 находятся соответственно в одинаковых положениях , а индикаторы 9и 11, 10и 12 соответственно индицируют одно и тоже. В случае (фиг.З) - это единица, а в случае (фиг.Зе) - нули. Если за время, прошедшее с такта, предвдущего анализируемому, состояние контролируемого цифрового узла :изменилось, то состояние тригге: ров 4и7, 5и8, а также индикаторов 9и 11, Юн 12 соответственно не эквивалентны. Так для случая (фиг.З)К) индикаторы 9 и 12 индицируют переход объекта контроля по заданному такту из нулевого состояния в единичное, а для случая (фиг.За) индикаторы 10 и 11 - наоборот из еди ничного в нулевое, что отражено на фиг.Зжи, где размещение индикаторов соответствует фиг.2. Таким образом, за счет введения триггеров 7 и 8 и новых связей пробник фиксирует изменения логического 354 сигнала на входе 1 от (i-1)-го такта к i-y такту, ecjni эти изменения произошли в интервале времени между пеpeднимli фронтами (i-l)-ro и i-ro тактовых импульсов, причем состояние в (i-l)-M такте определилось к моменту заднего фронта (i-1)-ro тактового импульса, что расширяет функц11ональные возможности предлагаемого пробника по сравнению с известным, где фронты сигналов на входе 1 не выявляются. Формула изобретения Логический пробник, содержащий первый и второй пороговые блоки,соединенные входами с первым входом логического пробника, а выходами - с D-входами первого и второго D-триггеров, соединенных прямьмй выходами соответственно с входами первого и второго индикаторов, С-входами между .собой, а также коммутатор, соединенный первым входом с вторым входом логического пробника, выходами - с информационными входами счетчика, соединенного выходом переноса с С-входом третьего D-триггера, соединенного S-входом с вторым входом логического пробника, инверсным выходом - с собственным D-входом, прямым выходом - с первым входом эле- мента И, соединенного вторым входом с третьим входом логического пробника, а выходом - с счетным входом счетчика, третий и четвертый индикаторы, отличающийся тем, что, с целью расширения функциональных возможностей пробника, за счет выявления изменения состояния контролируемого цифрового узла в i-M такте относительно (1-1)-такта, в него введены четвертый и пятый D-триггеры, D-входы которых соединены соответственно с прямыми выходами первого и второго D-триггеров, С-входы - с С-входом первого D-триггера и с выходом элемента И, прямые выходы соответственно - с входами третьего и четвертого индикаторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический пробник | 1984 |

|

SU1242863A1 |

| Логический пробник | 1981 |

|

SU970281A1 |

| Логический пробник | 1986 |

|

SU1352421A1 |

| Логический пробник | 1983 |

|

SU1132268A1 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Логический пробник | 1986 |

|

SU1352420A1 |

| ЛОГИЧЕСКИЙ ПРОБНИК | 1991 |

|

RU2041473C1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

Изобретение относится к контрольно-измерительной технике. Может использоваться при проверке цифровых блоков и устройств на интегральных микросхемах. Цель изобретения - расширение функциональных возможностей достигается путем выявления изменения состояния контролируемого цифрового узла в i-M такте относительно

| Зонд для проверки сигналов цифровых микросхем | 1974 |

|

SU513330A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логический пробник | 1981 |

|

SU970281A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-12-07—Публикация

1985-07-12—Подача