через одновибратор с единичным входо второго триггера, нулевой вход которого соединен с входом сброса первого счетчика, выходы которого соединены с информационными входами второго дешифратора, третий выход которого соединен с третьим входом второго элемента И, вьйсод которого соединен с входом записи блока записи, четвертый, пят|)1Й, шестой и седьмой, выходы второго дешифратора соединены с соответ ствующими входами первого элемента 1ЩИ, выход которого соединен с третьим входом третьего элемента И, вькод которого соединен с входом считывания блока записи, прямой и инверсные выходы вто .рого разряда п-разрядного регистра соединены с первыми входами четвертого и пятого элементов И соответственно, группа вькодов регистра тестов соединена с группой управляющих входов коммутатора входов/выходов, управляющий вход которого соединен с вьЕкодом четвертого элемента И, информационные выходы коммутатора входов/выходов соединены с соответствую щими входами/выходами контролируемого логического блока, первая группа информационных входов схемы сравне,ния соединена с группой выходов регистра тестов, вторая группа информационных входов схемы сравнения соединена с группой выходов контролируемого логического блока,.выход равно схемы сравнения соединен с вторым входом пятого элемента И, тре тий вход которого соединен с четвертым выходом первого дешифратора и вторым входом четвертого элемента И, третий и шестой выходы первого де }Ифратрра соединены с входом записи регистра теста и первым входом шесто го элемента И соответственно, инверс ны выходы третьего и четвертого разрядов п-разрядного регистра сое2динены с вторым входом шестого элемента И и с входом сброса второго счетчика, выходы которого соединены с информационными входами первого дешифратора, третий вход шестого элемента ,И соединен с инверсным выходом первого триггера, единичный вход которого соединен с выходом пятого элемента И, третий вход которого соединен с инв.ерсньм выходом второго разряда п-разрядного регистра, девятый выход второго дешифратора соединен с нулевым входом второго триггера и вторым входом первого элемента И, первый йход второго элемента ИЛИ подключен к кнопке пуска, второй вход второго элемента ИЛИ соединен с выходом шестого элемента И, выход второго элемента ИЛИ соединен с входом считывания блока памяти, выход генератора контрольных импульсов соединен с информационным входом ключа, управляющий вход которого соединен с выходом триггера задания режима контроля, группа выходов счетчика соединена с первой группой информационных входов элемента сравнения, вторая группа информационных входов которого соединена через соответствующие ключи группы с шиной, задания эталона, единичный вход триггера задания режима контроля соединен с входом установки устройства, информационный чход контролируемого логического блока подключен через переключатель режима контроля к информационному выходу ключа и к инфор.мационному входу олока определения неисправности типа обрыва, выходы регистра тестов соединены с информационными входами коммутатора входов (выходов, информационные выходы которых соединены с соответструюш ми входами/выходами, контролируемого логического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1793441A2 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКиВ, содержащее блок памяти, схему сравнения, регистр теста, блок управления, элемент сравнения, причем блок управления содержит первый триггер, выходы тестовой информации блока памяти соединены с информационньми входами блока записи, выходы которого соединены с информационными входами регистра теста, информационные выходы которого соединены с соответст,вующими входами/вькодами контролируемого логического блока, о т л и чающееся тем, что, с целью повьшения достоверности контроля и расширения функциональных возможностей за счет контроля логических блоков, содержащих логические элементы типа счетчиков, оно содержит генератор контрольных импульсов, счетчик, ключ, триггер задания geжима контроля, группу переключателей, переключатель режима контроля, коммутатор входов/выходов, а блок управления содержит триггер, одновибратор, первый и второй счетчики, кнопку сбросаi кнопку пуска, дешифратор тактов контроля, два дешифратора, два элемекта ИЛИ, генератор тактовых импульсов,, шесть элементов И, п-разрядный регистр, причем выходы тактовой информации блока памяти соединены .с информационными вхо- дами дешифратора тактов контроля, первый выход которого соединен с первым входом первого элемента И,. выход которого соединен с единичным входом первого разряда,п-разрядного регистра,, единичные входы второго, третьего и четвертого разрядов которого соединены с вторым, третьим и четвертым выходами дешифратора тактов контроля, нулевой вход первого разряда п-разрядного регист-. ра соединен с четвертым выходомСЛ дешифратора такта контроля, нулевой вход второго разряда п-разрядного регистра соединен со стробирующим выходом первого дешифратора и нулевым входом четвертого разряда п-разрядного регистра, нулевой вход третьего разряда п-разрядного регистра соединен с выходом равно элемента сравнения и нулевым входом триггера задания режима контроля, вход сброса а-разрядного регистра подключен к кнопке сброса И соединен с нулевыми входами первого и второго триггеров, входом сброса счетчика и нулевым входом триггера задания режима контроля, прямой выход первого разряда п-разрядного регистра Iсоединен с первыми входами второго и третьего элементов И, вторые входы которых соединены с выходом генератора тактовых импульсов блока управления и с синхровходами первого и второго счетчиковj выход метки конца тестов блока памяти соединен

Изобретение относится к вычислительной технике и может быть использовано для контроля логических блоков различных электронньпс цифровых систем.

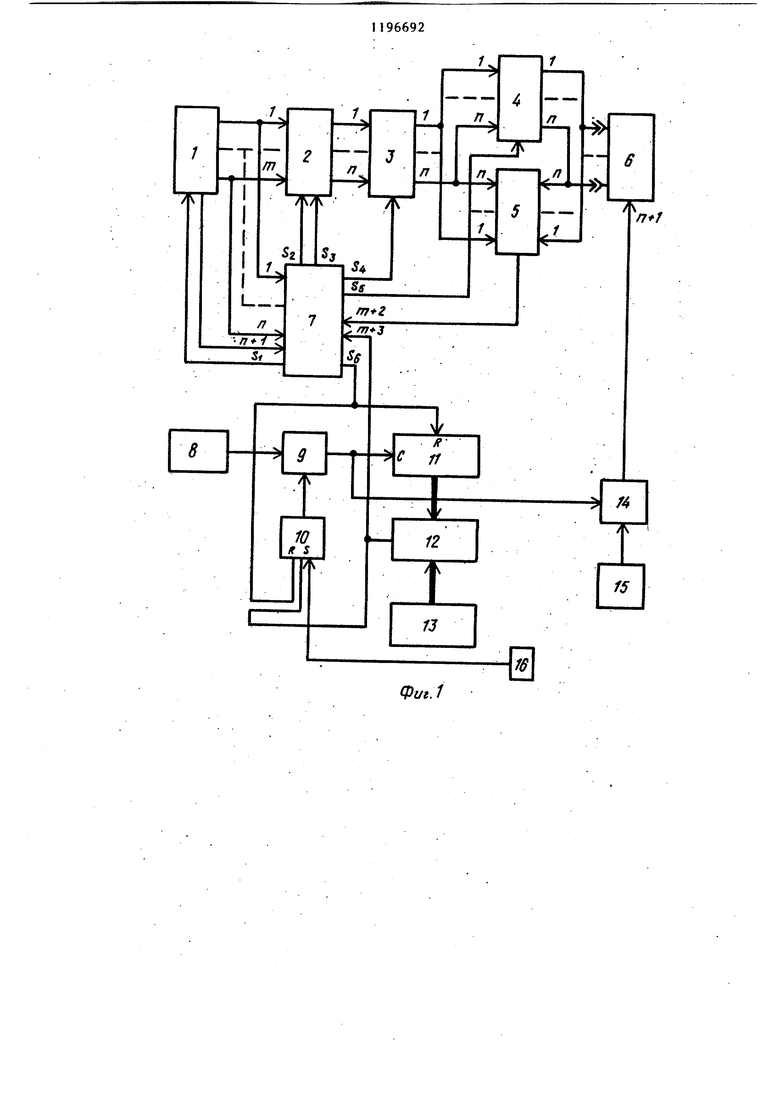

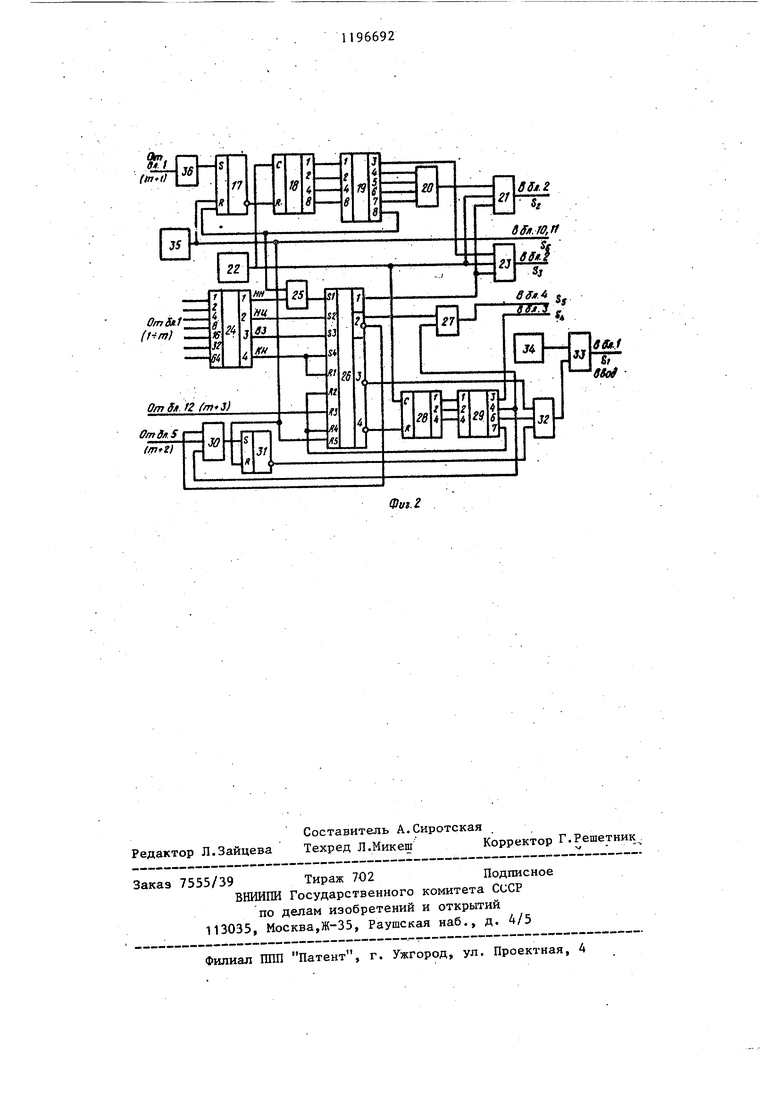

Цель изобретения - повьш1енне достоверности контроля и расширение функционал| ных возможностей за счет контроля логических блоков, 3 На фиг. 1 и 2 изображено устройс во для контроля логических блоков. Устройство содержит блок 1 памяти, блок 2 записи, регистр 3 теста, Ьсоммутатор 4 входов/выходов, схему 5 сравнения,контролируемый логичес кий блок 6, блок 7 управления, генератор 8 контрольньпс импульсов, ключ 9, триггер 10 режима контроля, счетчик 11, элемент 12 сравнения, группа переключателей 13, переключа тель 14 режима контроля, блок 15 определения неисправности типа обры ва, кнопку 1б установки. Ьлок управления (фиг. 2) содержит триггер 17, счетчик 18, дешифра тор 19, элемент ИЛИ 20, элемент И 21, генератор 22 тактовых импульсов, элемент И 23, дешифратор 24 . тактов контроля, элемент И 25, п-ра рядный регистр 26, элемент И 27, счетчик 28, дешифратор 29, элемент И 30, триггер 31, элемент И 32, эле мент ИЛИ 33, кнопку 34 пуска, кнопку 35. сброса, однойиоратор 36. Блок 15 определения неисправност типа обрыва представляет соОой логи ческий пробник с щупом, которьй может быть выполнен по авт. св. № 799118. щуп зонда переключателем 14 с режима контроля, который представля ет из себя механический пер,еключатель -на два положения, может подключаться либо к блоку 15, либо к ключу 9. Для управления триггером 10 предусмотрена кнопка 16 установки. Блок памяти может быть выполнен на базе стандартного устройства под готовки данных (например, на базе устройства Аккорд-05 ), в состав которого входят накопитель на магнитной ленте и дисплейньй модуль. Запись тестового набора в блок памя ти производится символами в коде ГОСТ 13052-74. Для формирования про извольного п-разрядного набора, сос тоящего из О и 1, используются символы, 4 младших разрядов которых отображают комбинации от 0000 до 1111. . Таким образом, п-разрядный набор организуется из п/4 символов. Тесто вые наборы обрамляются определенным метками, указывающими на начало (НН и конец (КН) набора. Еабор, определяющий входные и выходные цепи ТЭЗа 24 дополняется после НН соответствующей меткой (НЦ), а набор, предусматривающий подключение зонда к внутренним точкам ТЭЗа, меткой (ВЗ) перед КН. Информация о месте подключения зонда и количества подаваемых импульсов воспроизводится на дисплейном модуле при считывании теста с кассетного накопителя. Из блока памяти в блок записи поступают только i младших разряда каждого символа, а в блок управления дпя различения меток (типа КО, КН, НЦ, ВЗ) полные коды. Коммутатор входы/выходы служит для коммутации входов и выходов блока 6 и выполнен на базе п-разрядного регистра и п-к.оммутирующих элементов, управляемых сигналами с выходов данного регистра (1 на выходе i-ой ячейки регистра означает, что i-ая цепь ТЭЗа - входная цепь) , коммутирующие элементы соединяют соответствующие выходы регистра тёста с входными цепями контролируемого логического блока 6.Ввод наборов для контроля блока 6осуществляется а:втоматически с блокировкой ввода при несравнении реакции блока 6 с эталонным набором. Перед тестированием логического блока 6 .кнопкой 35 Сброс в блоке 7управления триггеры 17 и 31 и празрядный регистр 26, счетчик 11 и триггер 10 устанавливаются в нулевое состояние. Процесс тестирования начинается нажатием кнопки 34 .Пуск блока 7 управления. В результате на выходе элемента ИЛИ 33 формируется сигнал S , разрешающий Ввод набора из блока 1 памяти в блок 2 записи и блок7 управления. Символы, образующие набор, поступают из блока 1 памяти в блок 7 в сопровождении сигнала, который подается на (т ч- 1)-й вход блока 7. По этому сигналу устанавливается в 1 триггер 17, в результате чего происходит модификация счетчика 18 от генератора 22 импульсов, состояния счетчика дешифратора дешифрируются дешифратором 19. Сигналы с выходов дешифратора 19 используются « для организации записи 4 младших разрядов каждого символа набора в первые 4-е ячейки блока 2 записи (.сигнал Sj, формируемый элементом И 23)} сдвига информации на 4-е разряда и. в блоке 2 записи при формиро вании п-разрядного набора (сигналы Sjj, формируемые элементами ИЛИ 20 и И 21). По достижении счетчиком 18 состояния 9 сигналом с дешифратора 19 триггер 17 устанавливается в О и прием символа в блок записи 2 завершается. Аналогично принимаются .последующие символы набора. Сигналы S , к Sj выдаются в олок 2 записи по прочтению дешифратором 24 метки НН. При этом в 1-ю ячейку п-разрядрегистра 26 записьшается 1 и разблокируются элементы И 21 и И 23. При вводе первого набора, определяющего входные и выходные цепи контролируемого блока 6, по прочтению метки НЦ дешифратор 24 записывает 1 во 2-ю ячейку п-разрядного реги ра 26, в результате чего разблокиру ется элемент И 27, формирующий сигнал Sj. При распознавании метки кон ца набора КН по сигналу с дешифратора 24 устанавливается в 1 4-я ячейка п-разрядного регистра 26. Пр этом разрешается модификация счетчи ка 28 импульсами генератора 22 тактовых импульсов, состояние счетчика дешифрируется дешифратором 29. По достижению счетчиком 28 состояний: 3 формируется сигнал-S), но которому производится перезапись набора из блока 2 в блок 3, 4 элемент И 27 вьщает сигнал Sf, по которому производится переза пись набора цепей из блока 3 в блок 6 элементами И 32 и ИЛИ 33 фор мируется запрос S f на считьтание последующего набора/ 7 производится установка в О ячеек 2 и ч регистра 26. После записи набора через коммутатор 4 входов/выходов входные цепи контролируемого блока 6 подключаются к соответствующим ячейкам регистра 3 тестов, из регистра тестов 3 тесто вый набор подается на первую группу входов схемы 5 сравнения и одновременно через коммутатор входа/выходов на контролируемьш блок 6. На вторую группу входов схемы 5 поступает информация с выходов блока 6. Результат сравнения с выхода схемы 5 выдается на элемент И 30 блока 7 управления, результат строоируется сигналом с дешифратора 29 по достижению счетчиком 28 состояния 4. При от- сутствии ошибки сравнения реакции контролируемого блока 6 и эталонного набора элементы И 32 и ИЛИ 33 при состоянии счетчика 28, равным 6. формируют сигналы запроса S на ввод следующего набора. В случае ошибки триггер 31 устанавливается в 1, блокируется элемент И 32, и на прямой выход триггера 31 подается сигнал ошибки, которьш индицирует оператору наличие ошибки. Отличие фактической реакции контролируемого от эталонной определяется с помощью элементов индикации, входящих в схему 5 сравнения. Если процедурой проверки контролируемого блока 6 предусматривается подача определенного количества импульсов на одну из внутренних контрольных точек блока 6 с помощью блока 15 определения неисправностей, то в тестовый набор вводится метка включения ВЗ. При распознавании ВЗ дешифратора 24 в 3-ю ячейку п-разрядного регистра 26 записьшается l, блокируется элемент И 32-, и запрос на считывание очередного набора (сигнал ЗУ) не формируется. При подведении щупа блока 15 к указанной точке контролируется наличие контакта щупа. После чего щуп блока 15 переключателем 14 режима контроля подключается к ключу 9 и через кнопку 1б подается сигнал на установку в l триггера 10. При зтом отпирается ключ 9, импульсы с генератора 8 контролируемых импульсов подаются на счетчик 11 и одновременно через переключатель 14 на контрольную точку. При совпадении кодов счетчика 11 кода, набранного на переключателях группы 13, элемент 12 сравнения производит сброс триггера 10 и установку в О 3-ей ячейки п-разрядного регистра 26 блока управления. После чего кнопкой 34 Пуск блока 7 формируется запрос на ввод очередного набора.

Фиг.1

| УСТРОЙСТВО для ПРОВЕРКИ ФУНКЦИОНИРОВАНИЯ ЛОГИЧЕСКИХ СХЕМ | 0 |

|

SU354415A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| В П Т Б ФОНД v3^!>&PT(ia I | 0 |

|

SU390526A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-01—Подача