Изобретение относится к вычислительной технике и предназначено для исследования стационарных случайных процессов, представленных неравноотстоящими отсчетами.

Целью изобретения является повышение быстродействия.

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока управленияj на фиг. 3 - структурная схема квадратора.

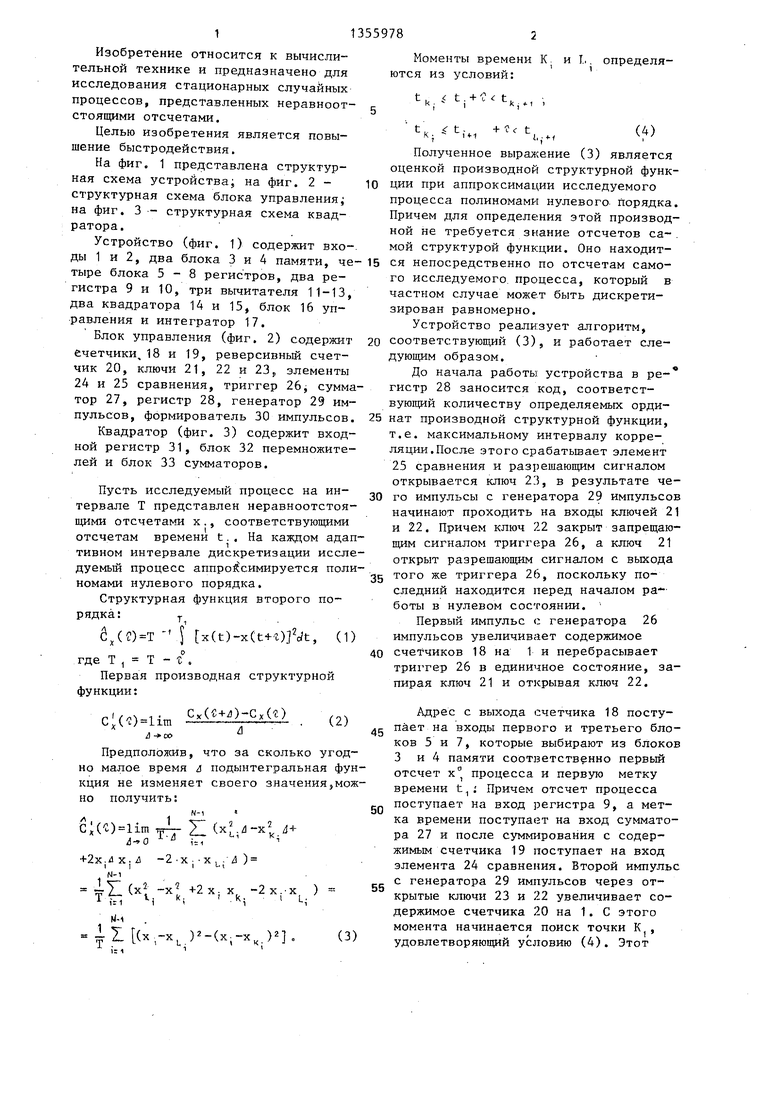

Устройство (фиг. 1) содержит вхо-.

Моменты времени К, и L. определяются из условий:

Ч, t.t

К; ,4l

+ Jf t

(,(

(4)

Полученное выралсение (3) является оценкой производной структурной функ 10 ции при аппроксимации исследуемого процесса полиномами нулевого Порядка Причем для определения этой производ ной не требуется знание отсчетов самой структурой функции. Оно находитды 1 и 2, два блока 3 и 4 памяти, че- 15 ся непосредственно по отсчетам само- тыре блока 5-8 регистров, два регистра 9 и 10, три вычитателя 11-13, два квадратора 14 и 15, блок 16 управления и интегратор 17.

го исследуемого, процесса, который в частном случае может быть дискрети- зирован равномерно.

Устройство реализует алгоритм.

Устройство реализует алгоритм.

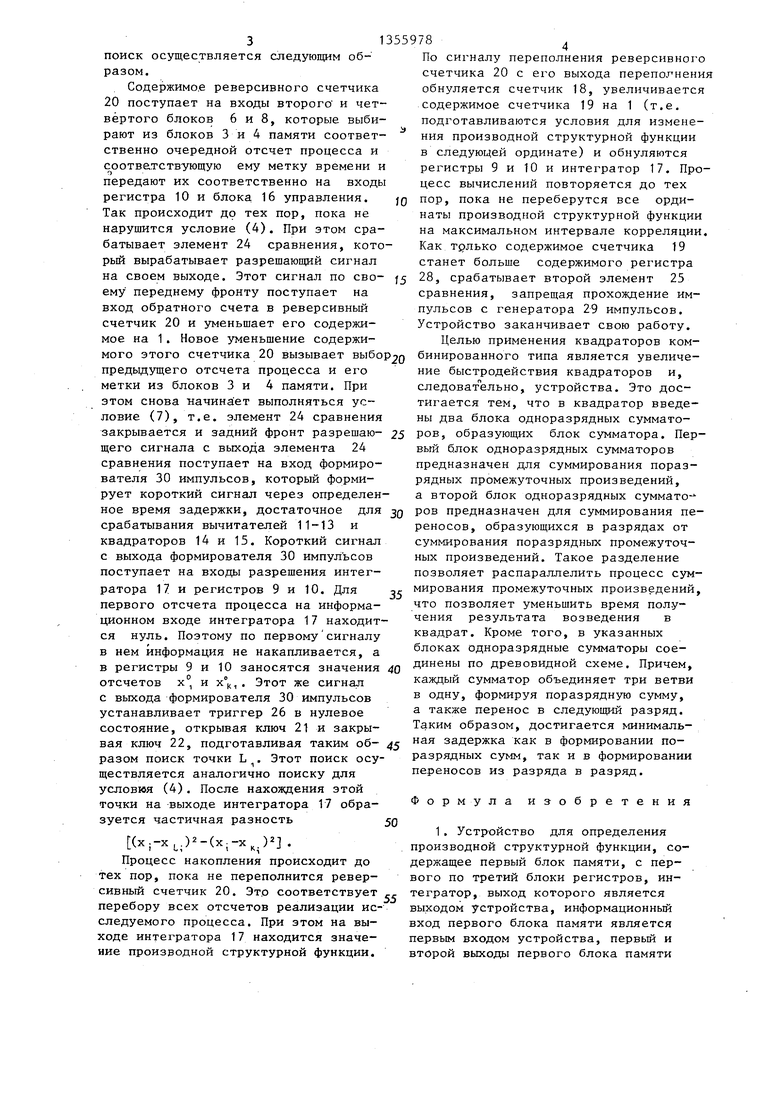

Блок управления (фиг. 2) содержит 20 соответствующий (3), и работает сле- ечетчики 18 и 19, реверсивный счет- дующим образом.

чик 20, ключи 21, 22 и 23, элементы До начала работы устройства в ре- 24 и 25 сравнения, триггер 26 сумма- гистр 28 заносится код, соответст- тор 27, регистр 28, генератор 29 им- вующий количеству определяемых орди- пульсов, формирователь 30 импульсов. 25 нат производной структурной функции.

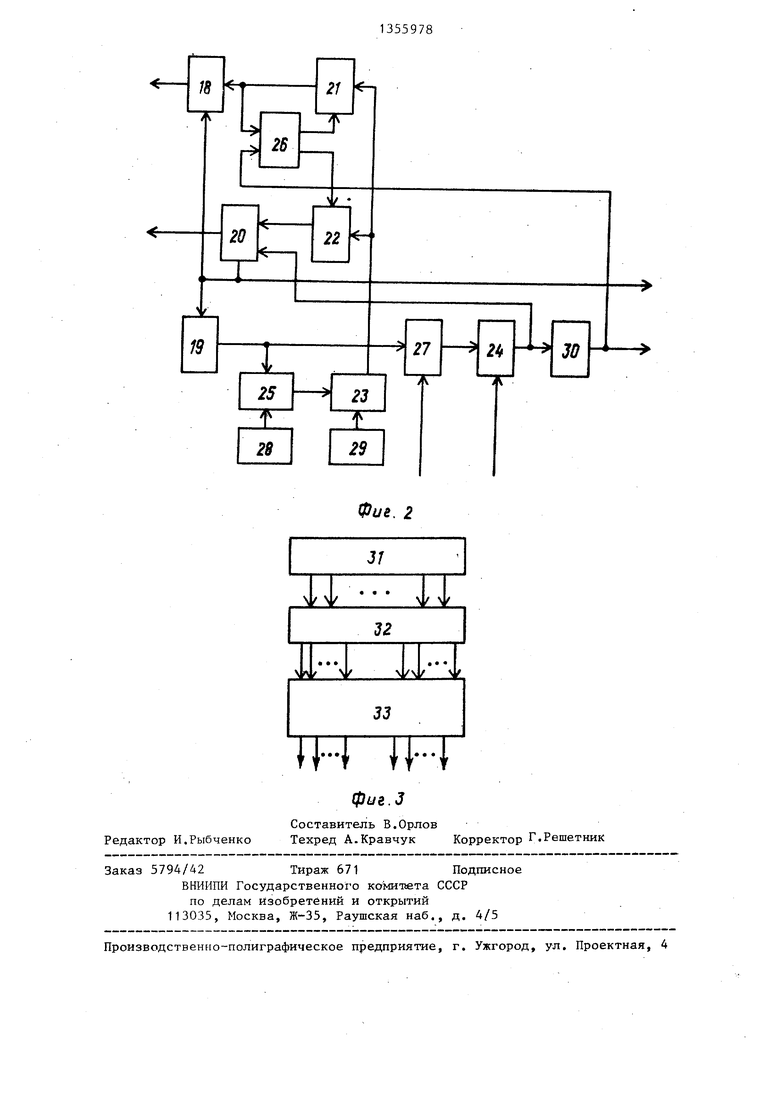

Квадратор (фиг. 3) содержит входной регистр 31, блок 32 перемножителей и блок 33 сумматоров.

Пусть исследуемый процесс на интервале Т представлен неравноотстоящими отсчетами х ., соответствующими отсчетам времени t.. На каждом адаптивном интервале дискретизации исследуемый процесс аппро симируется полиномами нулевого порядка.

Структурная функция второго пот.е. максимальному интервалу корреляции.После этого срабатывает элемент 25 сравнения и разрешающим сигналом открывается ключ 23, в результате че30 го импульсы с генератора 29 импульсов начинают проходить на входы ключей 21 и 22. Причем ключ 22 закрыт запрещающим сигналом триггера 26, а ключ 21 открыт разрешающим сигналом с выхода

35 того же триггера 26, поскольку последний находится перед началом ра боты в нулевом состоянии.

рядка:

т,

C,()T i x(t)-x(t-bt)Jt, (1)

где Т , Т - -D .

Первая производная структурной функции:

Cx(«+ ; )-Cx( O

Первый импульс с генератора 26 импульсов увеличивает содержимое

40 счетчиков 18 на 1 и перебрасывает трИ1 гер 26 в единичное состояние, запирая ключ 21 и открывая ключ 22.

С( г)11т

J

(2)

45

Предпололсив, что за сколько угодно малое время л подынтегральная функция не изменяет своего значения5мож- но получить:

N-1

50

+2-К.Л Х| л N-I

1У (х - Т 4- i,

1

ТТ

с;( г)11т 21 .+

-2.х.-х,.гЛ )

ч-2х.х,-2х..х

Т .

irl

lJ-1

llt(x,-x,.) -(x,-x,.)

Адрес с выхода счетчика 18 поступает на входы первого и третьего блоков 5 и 7, которые выбирают из блоков 3 и 4 памяти соответственно первый отсчет х° процесса и первую метку времени Причем отсчет процесса поступает на вход регистра 9, а метка времени поступает на вход сумматора 27 и после суммирования с содержимым счетчика 19 поступает на вход элемента 24 сравнения. Второй импульс с генератора 29 импульсов через открытые Ю1ЮЧИ 23 и 22 увеличивает содержимое счетчика 20 на 1. С этого момента начинается поиск точки К, удовлетворяющий условию (4). Этот

55

Моменты времени К, и L. определяются из условий:

Ч, t.t

К; ,4l

+ Jf t

(,(

(4)

Полученное выралсение (3) является оценкой производной структурной функ- ции при аппроксимации исследуемого процесса полиномами нулевого Порядка. Причем для определения этой производной не требуется знание отсчетов са. мой структурой функции. Оно находится непосредственно по отсчетам само-

ся непосредственно по отсчетам само-

го исследуемого, процесса, который в частном случае может быть дискрети- зирован равномерно.

Устройство реализует алгоритм.

соответствующий (3), и работает сле- дующим образом.

.е. максимальному интервалу корреяции.После этого срабатывает элемент 25 сравнения и разрешающим сигналом открывается ключ 23, в результате чего импульсы с генератора 29 импульсов начинают проходить на входы ключей 21 и 22. Причем ключ 22 закрыт запрещающим сигналом триггера 26, а ключ 21 открыт разрешающим сигналом с выхода

того же триггера 26, поскольку последний находится перед началом ра боты в нулевом состоянии.

Первый импульс с генератора 26 импульсов увеличивает содержимое

счетчиков 18 на 1 и перебрасывает трИ1 гер 26 в единичное состояние, запирая ключ 21 и открывая ключ 22.

поиск осуществляется следующим образом.

Содержимое реверсивного счетчика 20 поступает на входы второго и четвёртого блоков 6 и 8, которые выбирают из блоков 3 и 4 памяти соответственно очередной отсчет процесса и соответствующую ему метку времени и передают их соответственно на входы регистра 10 и блока 16 управления. Так происходит до тех пор, пока не нарушится условие (4). При этом срабатывает элемент 24 сравнения, который вырабатывает разрешающий сигнал на своем выходе. Этот сигнал по своему переднему фронту поступает на вход обратного счета в реверсивный счетчик 20 и уменьшает его содержимое на 1. Новое уменьшение содержимого этого счетчика 20 вызывает выбор20 бинированного типа является увеличепредьщущего отсчета процесса и его метки из блоков 3 и 4 памяти. При этом снова начина:ет выполняться условие (7), т.е. элемент 24 сравнения

закрывается и задний фронт разрешаю- 25 РОВ, образующих блок сумматора. Перщего сигнала с выхода элемента 24 сравнения поступает на вход формирователя 30 импульсов, который формирует короткий сигнал через определенное время задержки, достаточное для зо срабатывания вычитатепей 11-13 и квадраторов 14 и 15. Короткий сигнал с выхода формирователя 30 импул ьсов поступает на входы разрешения интегратора 17 и регистров 9 и 10. Для первого отсчета процесса на информационном входе интегратора 17 находится нуль. Поэтому по первому сигналу в нем информация не накапливается, а в регистры 9 и 10 заносятся значения отсчетов х, и х°к, . Этот же сигнал с выхода формирователя 30 импульсов устанавливает триггер 26 в нулевое состояние, открывая ключ 21 и закры35

40

вый блок одноразрядных сумматоров предназначен для суммирования пораз рядных промежуточных произведений, а второй блок одноразрядных суммато ров предназначен для суммирования п реносов, образующихся в разрядах от суммирования поразрядных промежуточ ных произведений. Такое разделение позволяет распараллелить процесс су мирования промежуточных произведени что позволяет уменьшить время получения результата возведения в квадрат. Кроме того, в указанных блоках одноразрядные сумматоры соединены по древовидной схеме. Причем каждый сумматор объединяет три ветв в одну, формируя поразрядную сумму, а также перенос в следующгй разряд. Таким образом, достигается минимальвая ключ 22, подготавливая таким об- 45 задержка как в формировании по- разом поиск точки L . Этот поиск осуществляется аналогично поиску для условия (4). После нахождения этой точки на выходе интегратора 17 образуется частичная разность50

(Х,-Х,.)-(Х;-Х,.).

Процесс накопления происходит до тех пор, пока не переполнится реверсивный счетчик 20. Это соответствует перебору всех отсчетов реализации не- следуемого процесса. При этом на выходе интегратора 17 находится значение производной структурной функции.

55

разрядных сумм, так и в формировании переносов из разряда в разряд.

Формула изобретения

1. Устройство для определения производной структурной функции, содержащее первый блок памяти, с первого по третий блоки регистров, интегратор, выход которого является выходом устройства, информационный вход первого блока памяти является первьЕм входом устройства, первый и второй выходы первого блока памяти

По сигналу переполнения реверсивног о счетчика 20 с его выхода перепот нения обнуляется счетчик 18, увеличивается содержимое счетчика 19 на 1 (т.е. подготавливаются условия для изменения производной структурной функции в следуюцей ординате) и обнуляются регистры 9 и 10 и интегратор 17. Процесс вычислений повторяется до тех

пор, пока не переберутся все ординаты производной структурной функции на максимальном интервале корреляции. Как трлько содержимое счетчика 19 станет больше содержимого регистра

28, срабатывает второй элемент 25 сравнения, запрещая прохождение импульсов с генератора 29 импульсов. Устройство заканчивает свою работу. Целью применения квадраторов комние быстродействия квадраторов и, следовательно, устройства. Это достигается тем, что в квадратор введены два блока одноразрядных сумматоо

5

0

вый блок одноразрядных сумматоров предназначен для суммирования поразрядных промежуточных произведений, а второй блок одноразрядных суммато- ров предназначен для суммирования переносов, образующихся в разрядах от суммирования поразрядных промежуточных произведений. Такое разделение позволяет распараллелить процесс суммирования промежуточных произведений, что позволяет уменьшить время получения результата возведения в квадрат. Кроме того, в указанных блоках одноразрядные сумматоры соединены по древовидной схеме. Причем, каждый сумматор объединяет три ветви в одну, формируя поразрядную сумму, а также перенос в следующгй разряд. Таким образом, достигается минималь45 задержка как в формировании по- 50

5

разрядных сумм, так и в формировании переносов из разряда в разряд.

Формула изобретения

1. Устройство для определения производной структурной функции, содержащее первый блок памяти, с первого по третий блоки регистров, интегратор, выход которого является выходом устройства, информационный вход первого блока памяти является первьЕм входом устройства, первый и второй выходы первого блока памяти

соединены с первыми информационными входами соответственно первого и вто- рбго блоков регистров, первые выходы которых соединены с соответствующими адресными входами первого блока памя- ти, отличающееся тем, что, с целью повышения быстродействия, в него введены второй блок памяти, четвертый блок регистров, два регистра, три вычитателя, два квад- ратора и блок управления, блок управления содержит первый и второй счетчики, реверсивный счетчик, три ключа, два элемента сравнения, триг . гер, сумматор, регистр, генератор импульсов, формирователь импульсов, в блоке управления выход первого кцюча соединен со счетным входом первого счетчика и входом установки в 1 триггера, вход установки в О, прямой и инверсный выходы которого соединены соответственно с выходом формирователя импульсов, yпpaвJГIЯющи- ми входами второго и первого ключей, выход регистра соединен с первым вхо дом первого элемента сравнения, второй вход и выход Больше каждого соединены соответственно с выходом второг о счетчика и управляющим входом третьего ключа, информационный вход которого соединен с выходом генератора импульсов, а выход соединен с информационными входами первого и второго ключей, выход которого соединен с суммирующим входом реверсив- ного счетчика5 вычитающий вход которого соединен с выходом второго элемента сравнения и входом формирователя импульсов, вьгход переполнения реверсивного счетчика соединен с BXO дами установки в О первого и второго счетчиков, первый вход и выход сумматора соединены соответственно с выходом второго счетчика и первым входом второго элемента сравнения, информационный вход второго блока памяти является вторым входом устройства, первый и второй выходы второго блока памяти соединены с первыми информационными входами соответственно третьего и четвертого блоков регистров, первые выходы третьего и четвертого блоков регистров соединены соответственно с первыми и вторыми адресными входами второго блока памяти, вторые выходы с первого по четвертый блоков регистров соединены соответственно с информационным входом первого регистра, с информационным входом второго регистра и входом вычитаемого первого вычитателя, вторым входом сумматора блока управления, вторым входом второго элемента сравнения блока управления выход первого регистра соединен с входом уменьшаемого первого вычитателя и входом вычитаемого второго вычитателя, вход уменьшаемого которого соединен с выходом второго ре- гистра, выходы первого и второго вы- читателей соединены соответственно с входами одноименных квадраторов, выходы первого и второго квадраторов, соединены соответственно с входами уменьшаемого и вычитаемого третьего вычитателя, выход которого соединен с информационным входом интегратора, вход разрешения записи которого соединен с входами разрешения записи первого и второго регистров и выходом формирователя импульсов блока управления, входы з становки в О первого и второго регистров и интеграторы соединены с выходом переполнения реверсивного счетчика, вторые входы первого и третьего блоков регистров соединены с выходом первого счетчика блока управления.

2. Устройство по п. 1, о т Л и - чающееся тем, что кйадратор содержит входной регистр, блок перемножителей и блок сумматоров, разрядные входы входного регистра являются входом квадратора, разрядные выходы входного регистра соединены с соответствующими: входа И блока перемножителей., выходы -которого соединены с входами блока сумматоров, выходы которого являются выходом квадратора.

i с

26

21 i

20

22

19

25

27

2

JO

23

л

28

rif ir

ir l tf

Редактор И.Рыбченко

фиг.З

Составитель В.Орлов

Техред А.Кравчук Корректор Г.Решетник

Заказ 5794/42 Тираж 671Подписное

ВНИИПИ Государственного коми-лета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения производной корреляционной функции | 1985 |

|

SU1305713A1 |

| Устройство для вычисления структурной и интервальной функций | 1984 |

|

SU1166135A1 |

| Устройство для вычисления производной взаимоструктурной функции | 1984 |

|

SU1288715A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Устройство для измерения отношения сигнала к помехе в телевизионном канале | 1985 |

|

SU1292206A1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Коррелятор | 1984 |

|

SU1173419A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Устройство для измерения защищенности сигналов от помех | 1989 |

|

SU1658399A1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

Изобретение относится к вычислительной технике и предназначено для исследования стационарных случайных процессов, представленных неравноотстоящими отсчетами. Целью изобретения является увеличение быстро.действия. Устройство содержит блоки 1, 2 записи, блоки 3, 4 памяти, блоки 5-8 регистров, регистры 9, 10, вы- читатели 11-13, квадраторы 14, 15 и блок 16 управления. Повышение быстродействия достигается тем, что квадратор содержит регистр, блок перемножителей, первый блок одноразрядных сумматоров, соединенных по древовидной схеме для суммирования промежуточных произведений разрядов результата, второй блок одноразрядных сумматоров, соединенных по древовидной схеме для суммирования поразрядных переносов, многоразрядный сумматор со сквозным переносом для формирования результата, образующие блок сумматоров. Оценка производной структурной функции основана на аппроксимации исследуемого процесса полиномами нулевого порядка. 1- з.п. ф-лы. 3 ил. ш ел 00 ел ел QD 00

| Цифровой коррелятор | 1982 |

|

SU1072057A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-30—Публикация

1986-01-15—Подача