Изобретение относится к технике связи и может быть использовано в системах телеуправления и сбора информации для .избирательного подстанции с главной станцрш.

Цель изобретения - повышение пропускной способности cиcтe Jы путем уменьшения времени переприема.

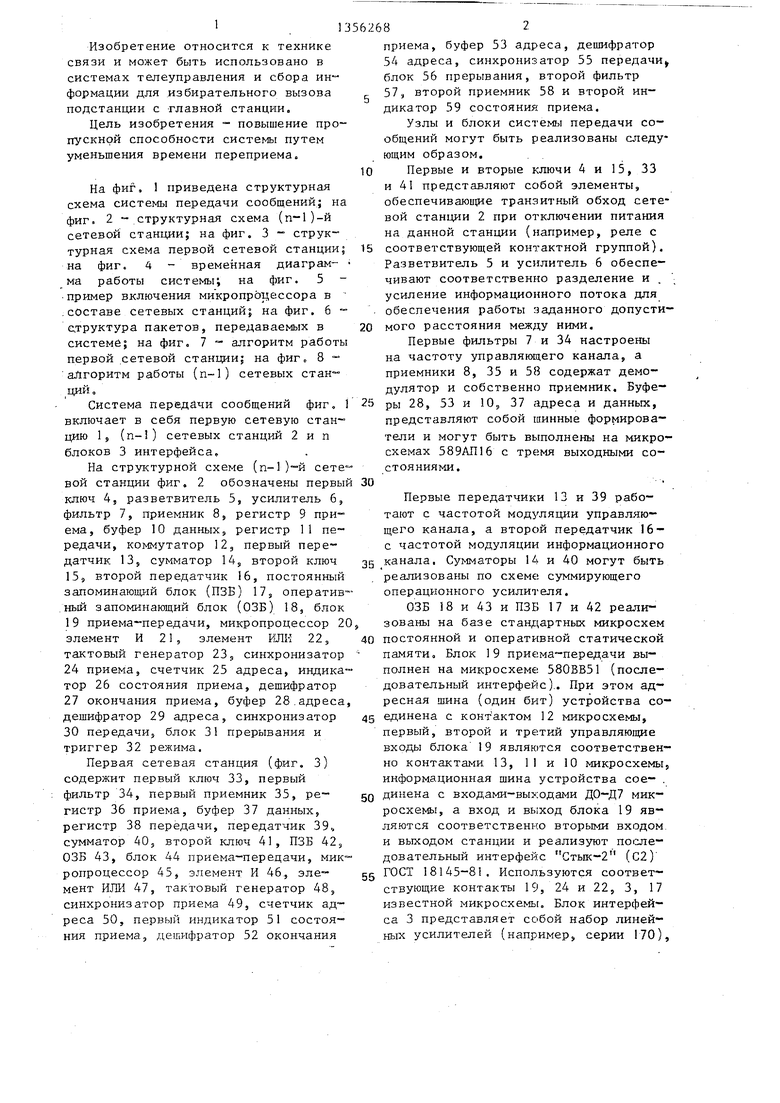

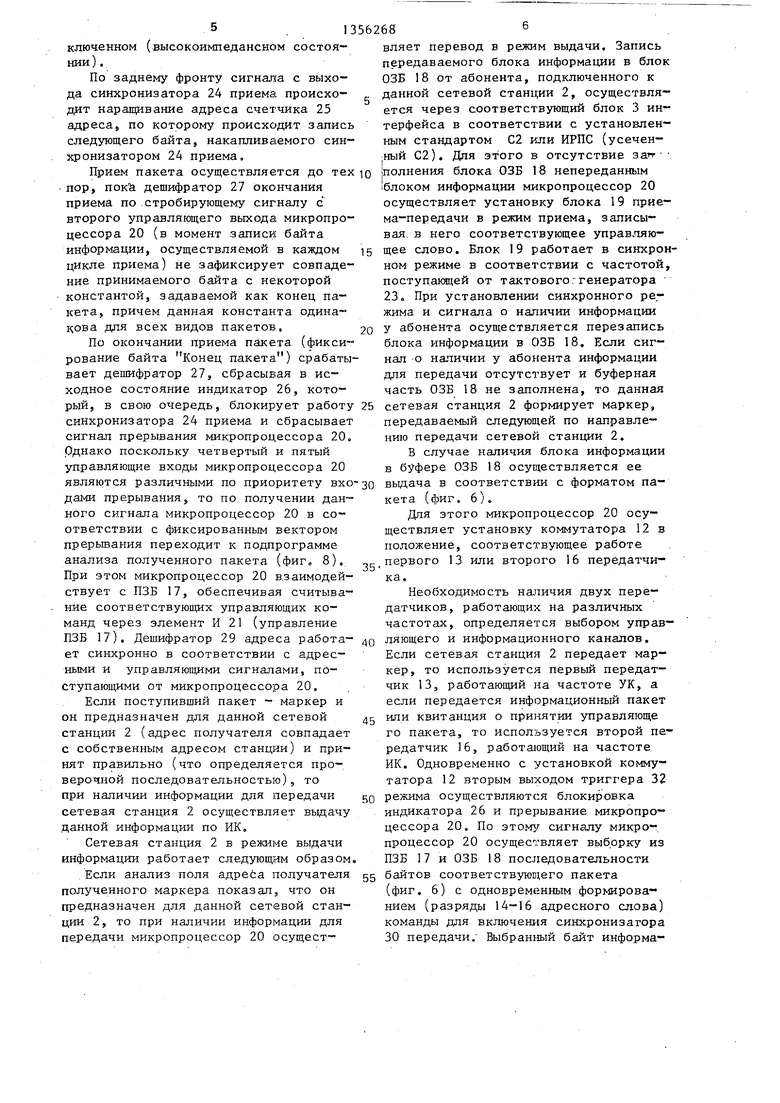

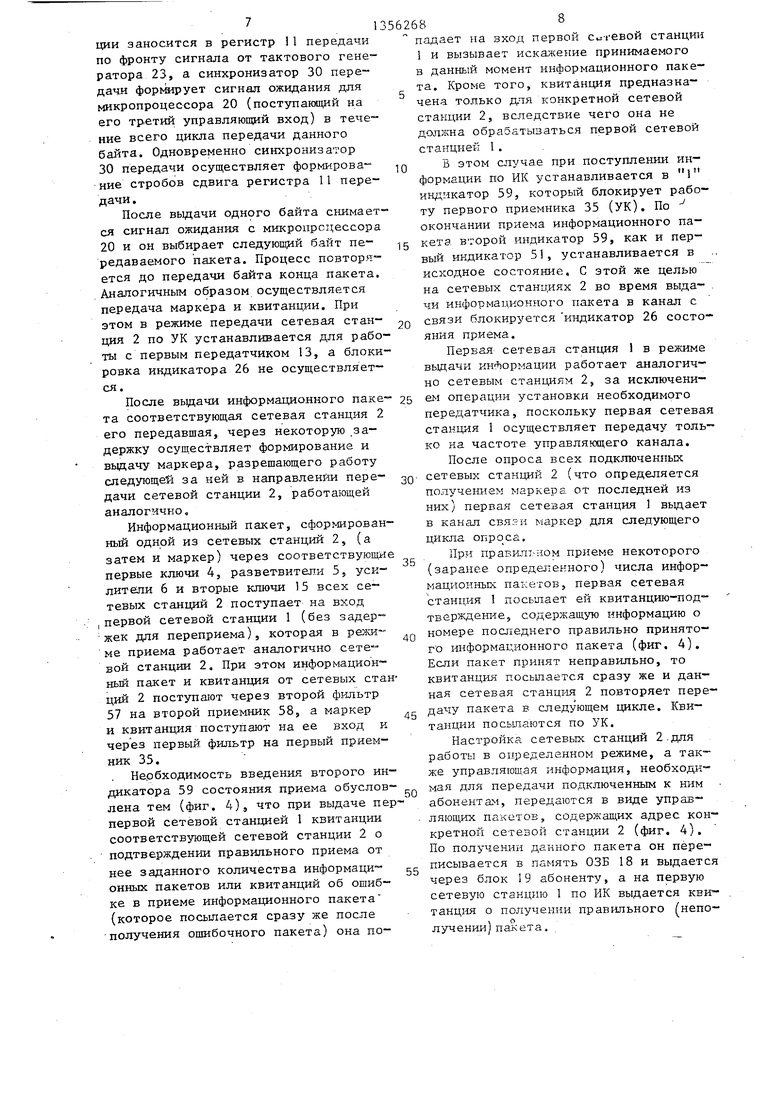

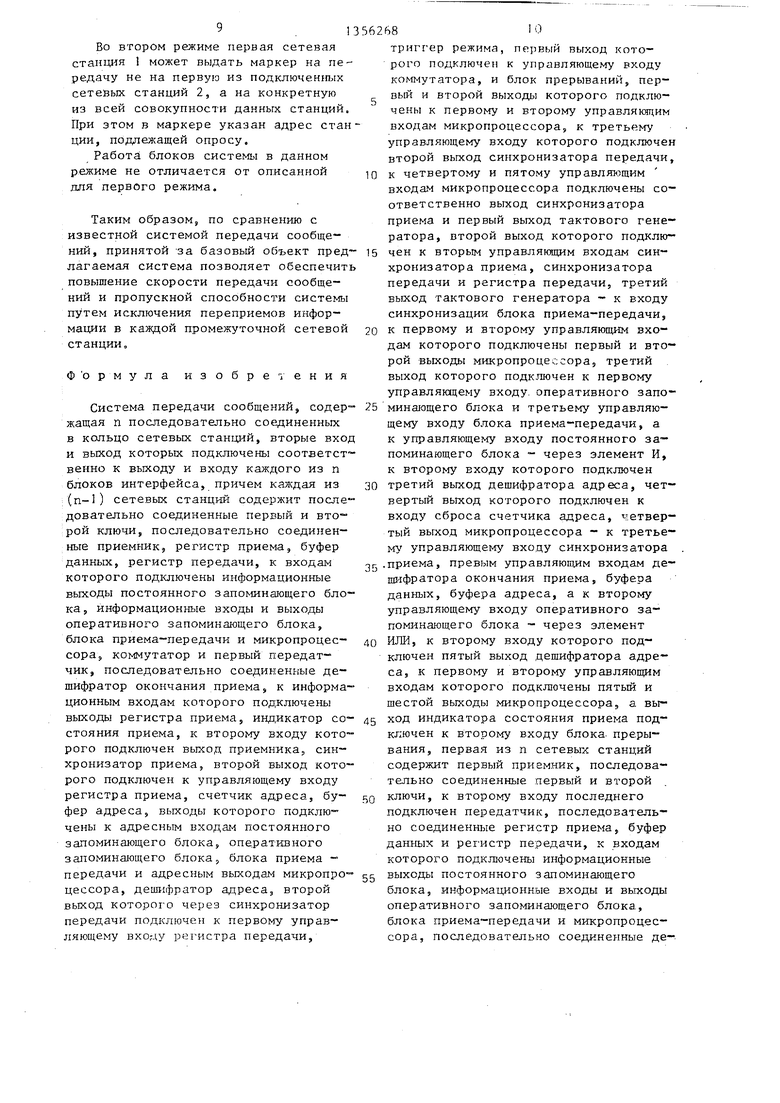

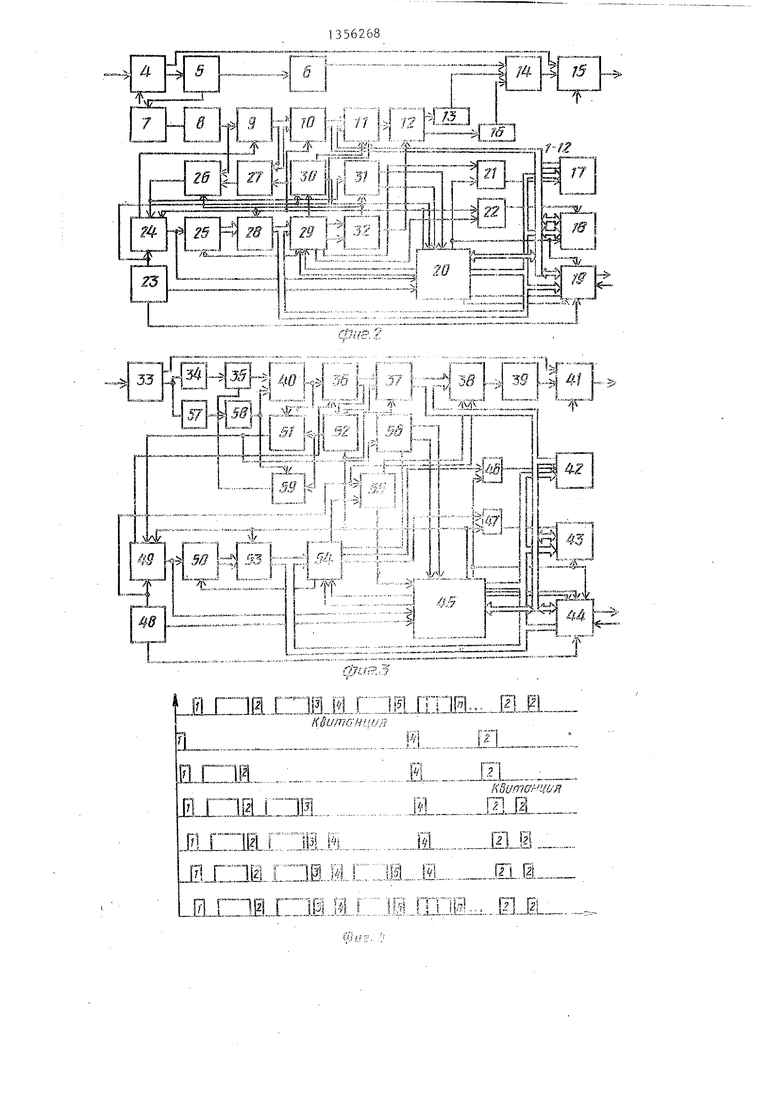

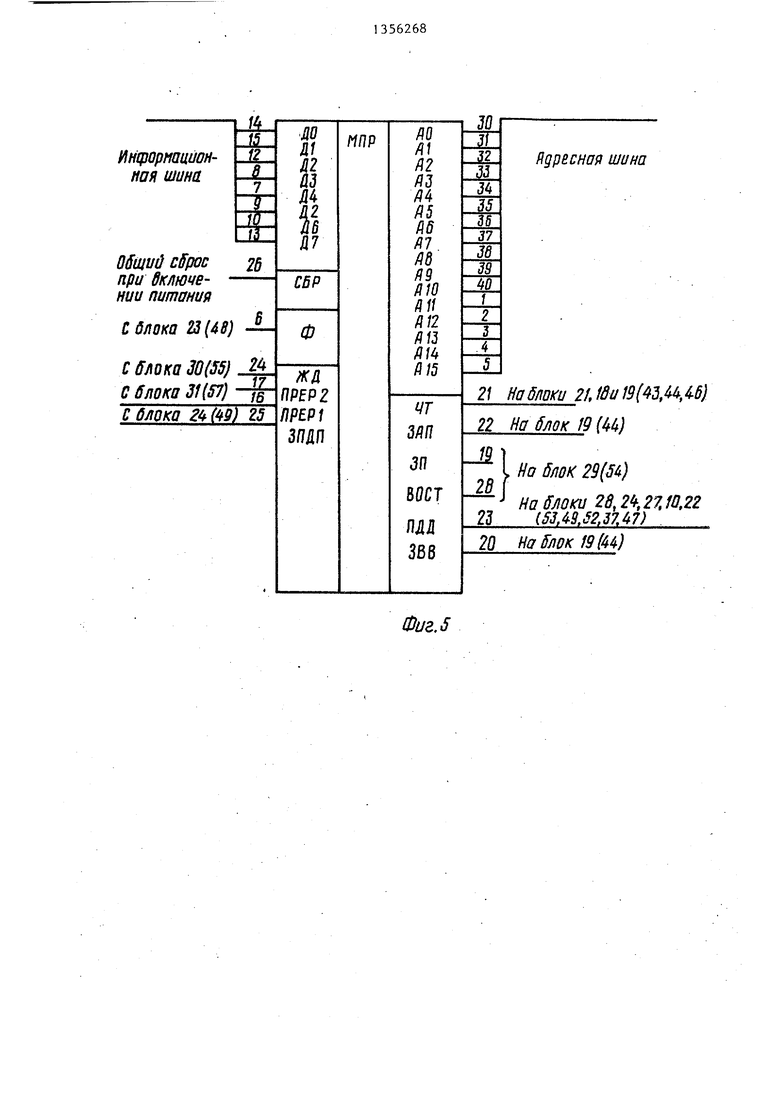

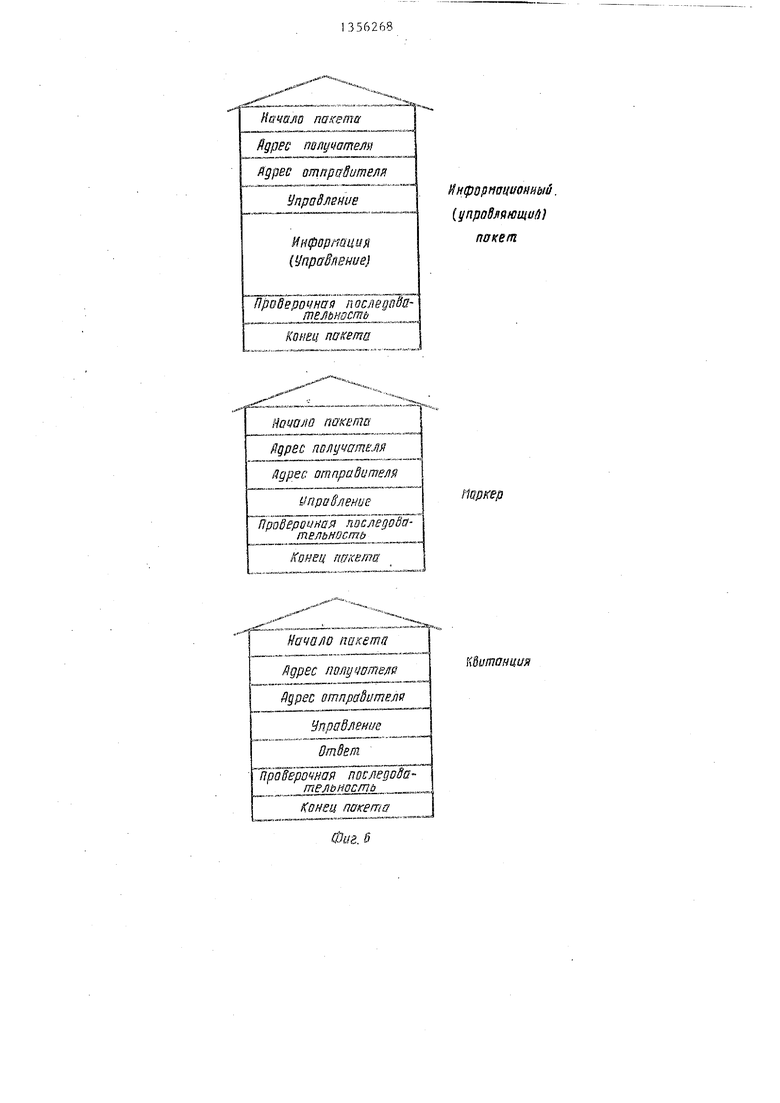

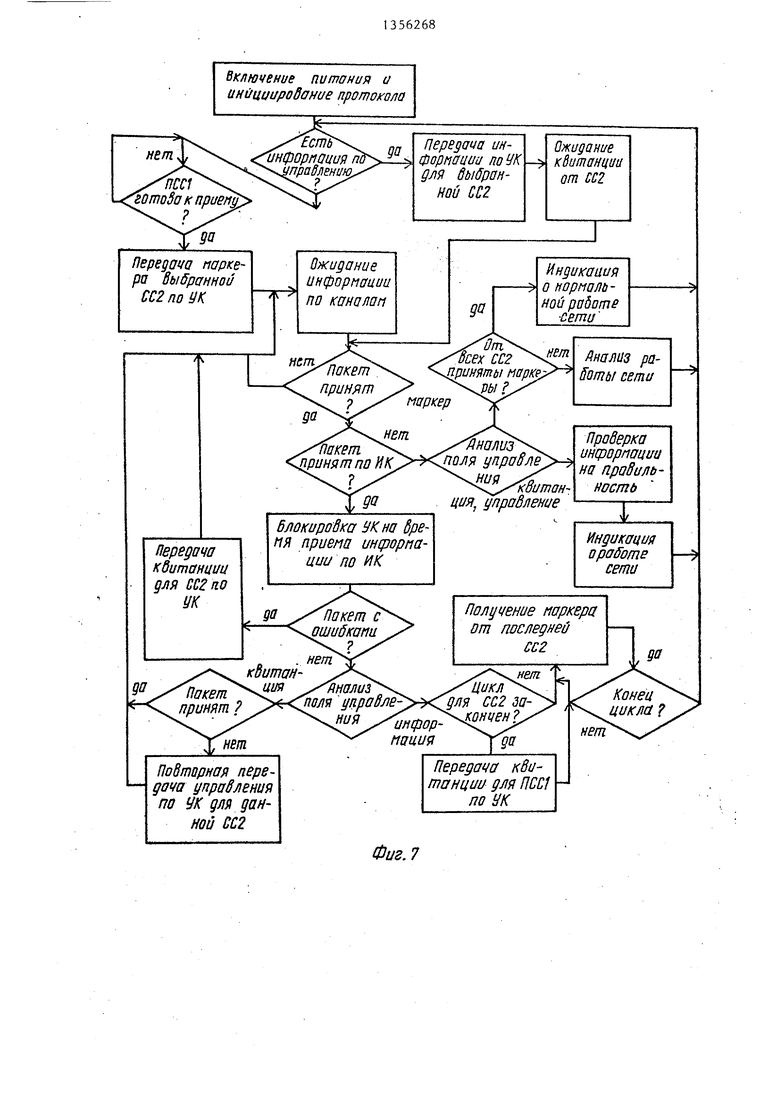

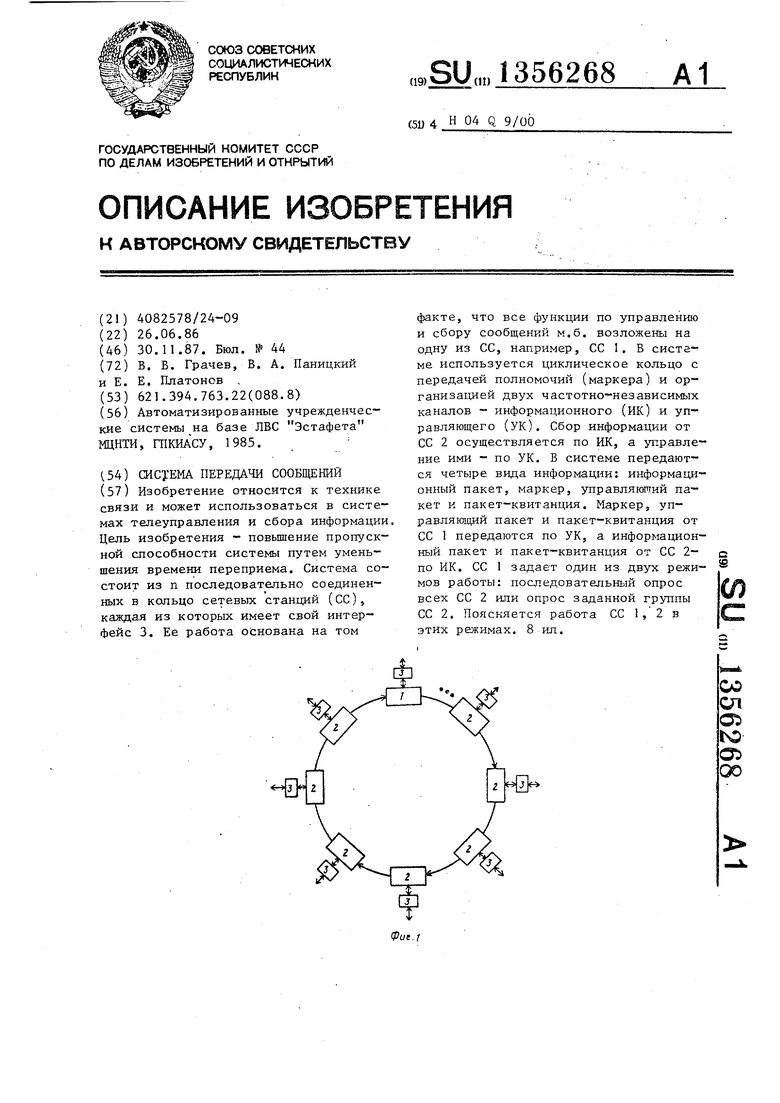

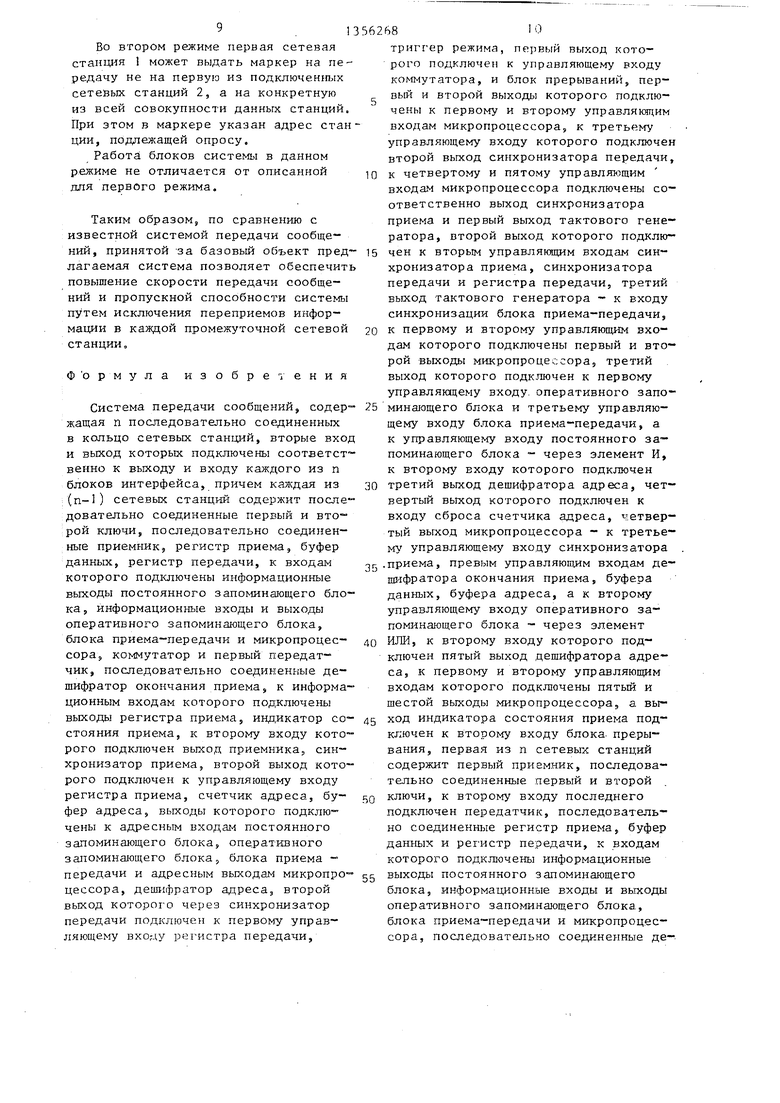

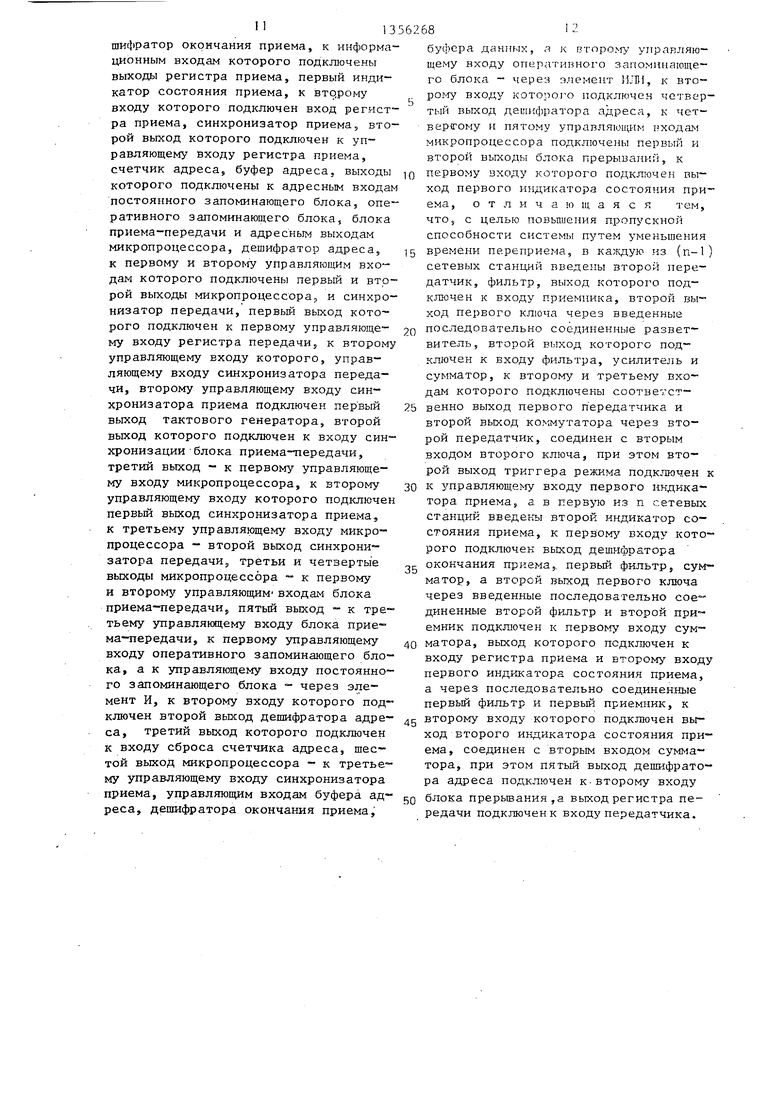

На фиг. 1 приведена структурная схема системы передачи сообщений; на фиг. 2 структурная схема (п-1)-й сетевой станции; на фиг. 3 - структурная схема первой сетевой станции; на фиг. 4 - временная диаграм- ма работы системы; на фиг. 5 пример включения микропрои,ессора в .составе сетевых станций; на фиг. 6 структура пакетов, передаваемых в системе; на фиг. 7 - алгоритм работы первой сетевой станции; на фиг„ 8 - алгоритм работы (п-1) сетевых станций.

Система передачи сообщений фиг, 1 включает в себя первую сетевую стан цию 1, (п-) сетевых станций 2 и п блоков 3 интерфейса.

На структурной схеме (п-1)-и сете вой станции фиг. 2 обозначены первый ключ 4, разветвитель 5, усилитель 6, фильтр 7, приемник 8, регистр 9 приема, буфер 10 данных, регистр 11 передачи, коммутатор 12, первый передатчик 13, сумматор 14, второй ключ 15s второй передатчик 16, постоянный запоминающий блок (ПЗБ) 17, оператив- ;ный запоминающий блок (ОЗБ) 18, блок 19 приема-передачи, микропроцессор 20 элемент И 21, элемент ИЛИ 22, тактовый генератор 235 синхронизатор 24 приема, счетчик 25 адреса, индика™ тор 26 состояния приема, дешифратор 27 окончания приема, буфер 28.адреса дешифратор 29 адреса, синхронизатор 30 передачи, блок 31 прерывания и триггер 32 режима.

Первая сетевая станция (фиг. 3) содержит первый ключ 33, первый фильтр 34, первый приемник 35, регистр 36 приема, буфер 37 данных, регистр 38 передачи, передатчик 39, сумматор 40, второй ключ 41, ПЗБ 42j ОЗБ 43, блок 44 приема-передачи, микропроцессор 45, элемент И 46, эле мент ИШ1 47, тактовый генератор 48, синхронизатор приема 49, счетчик адреса 50, первый индикатор 51 состояния приема, дешифратор 52 окончания

приема, буфер 53 адреса, дешифратор 54 адреса, синхронизатор 55 передачи блок 56 прерывания, второй фильтр 57, второй приемник 58 и второй индикатор 59 состояния приема.

Узлы и блоки системы передачи сообщений могут быть реализованы следующим образом.

0 Первые и вторые ключи 4 и 15, 33 и 4 представляют собой элементы, обеспечиваюи1ие транзитный обход сетевой станции 2 при отключении питания на данной станции (например, реле с

5 соответствующей контактной группой). Разветвитель 5 и усилитель 6 обеспечивают соответственно разделение и . ; усиление информационного потока для . обеспечения работы заданного допусти0 мого расстояния между ними.

Первые фильтры 7 и 34 настроены на частоту управляющего канала, а приемники 8, 33 и 58 содержат демодулятор и собственно приемник. Буфе5 ры 28, 53 и 10, 37 адреса и данных, представляют собой шинные формирователи и могут быть выполнены на микросхемах 589АП16 с тремя выходными состояниями.

0

Первые передатчики 13 и 39 работают с частотой модуляции управляющего канала, а второй передатчик 16- с частотой модуляции информационного

2 канала. Сумматоры 14 и 40 могут быть реализованы по схеме суммирующего операционного усилителя.

ОЗБ 18 и 43 и ПЗБ 17 и 42 реали- зованы на базе стандартных микросхем

0 постоянной и оперативной статической памяти. Блок 19 приема передачи выполнен на микросхеме 580ВВ51 (последовательный интерфейс).. При этом адресная шина (один бит) устройства со5 единена с конт актом 12 микросхемы, первый, второй и третий управляю:чие входы блока 19 являются соответственно контактами 13, II и 10 микросхемы, информационная шина устройства сое- .

Q динена с входами-выходами ДО-Д7 микросхемы, а вход и выход блока 19 являются соответственно вторыми входом, и выходом станции и реализуют поише- довательный интерфейс Стык-2 (С2)

g ГОСТ 18145-81. Используются соответствующие контакты 19, 24 и 22, 3, 17 известной микросхемы. Блок интерфейса 3 представляет собой набор линейных усилителей (например, серии 170),

включенных в соответствующие входные и вькодные цепи. Микропроцессоры 20 и 45 реализованы на используемой в прототипе специализированной микросхеме И 880Д (один из вариантов мик ропроцессора Z 80). Пример включения блоков 20 и 45 в составе станций 1 и 2 (реализация функциональных связей) приведен на фиг. 5.

Алгоритмы работы микропроцессоров 20 и 45 при включении в составе первой сетевой станции.1 и (п-1)-й сетевой станции 2 приведены на фиг. 7 и 8 соответственно.

Работа системы передачи сообщений основана на том, что при применении локальных сетей в большинстве случаев не требуется передача больших объ™ емов информации между различными станциями, а все функции по управлению и сбору сообщений могут быть возложены на одну из них.

В системе используется циклическое

кольцо с передачей полномочий (марке- 25 рывание микропроцессора 20 через

ра) и организацией двух частотно-независимых каналов в одной физической среде (кабель, волновод) - информационный канал (ИК) и управляющий канал (УК); Система обеспечивает сбор информации от сетевых станций 2 по ИК и управление ими по УК.

В системе передаются четыре вида сообщений (фиг. 6): информационный пакет, маркер, управляющий пакет и пакет-квитанция. При этом структура информационного и управляющего пакетов идентична, она различается лишь видом информации, содержащейся в нем.

блок 31 прерывания и разрешает работу синхронизатора 24 приема, осуществляющего формирование стробов сдвига для регистра 9 приема по сигналам 30 синхрочастоты от тактового генератора 23. После формирования байта информации (подсчет 8 импульсов тактовой частоты) синхронизатор 24 приема выдает соответств тощий сигнал на второй управляющий вход микропроцессора 20; обе спечивающий перевод в высоко- импедансное состояние его информационных и адресных шин. При достижении данного состояния микропроцессор

Маркер, управляющий пакет и пакет- 40 20 выдает сигнал подтверждения переквитанция от первой сетевой станции 1 передаются по УК, а информационный пакет и пакет-квитанция от сетевой станции 2 - по ИК.

Начало работы инициируется включе нием питания. При этом правом на занятие среды передачи обладает только первая сетевая станция 1, которая в зависимости от требуемой обстановки

задает один из двух возможных режимов gg яния счетчика 25 адреса управляющим |работЬ1 системы.

В первом режиме опрашиваются последовательно все сетевые станции 2, во втором режиме - только заданная группа сетевых станций 2 (или одна |Станция). Задание режима работы сетевой станции 2 обеспечивается передачей ей соответствующего управляющего пакета, принимаемого по УК.

сигналом через элемент ИЛИ 22. ОЗБ 18 при этом находится в режиме записи в отсутствие сигнала чтения с чет вертого управляющего выхода микропро 55 цессора 20, а дешифратор 29 адреса не работает, поскольку его адресные входы соединены только с адресными выходами микропроцессора 20, находящимися в данный момент времени в от-

56268

Рассмотрим работу системы в первом режиме. Первая сетевая станция 1 передает маркер (фиг. 6) первой из подключенных к ней по направлению передачи сетевых станций 2 (фиг. 4). Сетевая станция при приеме маркера (ftaK и при приеме управляющего пакета) работает следующим образом

ТО (фиг. 2 и 8).

Через первый ключ 4 последовательность маркера поступает на разветви- тель 5, служащий для согласования и разделения потоков. Далее маркерная

15 последовательность поступает соответственно на усилитель 6, обеспечивающий компенсацию затухания сигнала в ключах и разветвителе 5, через сумматор 14 и второй ключ 15 на вход, а

20 тагаке через фильтр 7 на вход приемника 8. При приеме первого бита маркерной последовательности устанавливается в 1 индикатор 26 состояния приема. Данный сигнал формирует преблок 31 прерывания и разрешает работу синхронизатора 24 приема, осуществляющего формирование стробов сдвига для регистра 9 приема по сигналам 0 синхрочастоты от тактового генератора 23. После формирования байта информации (подсчет 8 импульсов тактовой частоты) синхронизатор 24 приема выдает соответств тощий сигнал на второй управляющий вход микропроцессора 20; обе спечивающий перевод в высоко- импедансное состояние его информационных и адресных шин. При достижении данного состояния микропроцессор

вода своих адресных и информационных шин в высокоимпедансное состояние. Данный сигнал сбрасывает (по заднему фронту) синхронизатор 24 приема и разблокирует выходы буферов 10 и 28 данных и адреса. При этом принятый байт информации записывается с информационной шины в соответствующую ячейку памяти ОЗБ 18 по адресу состо-

яния счетчика 25 адреса управляющим

сигналом через элемент ИЛИ 22. ОЗБ 18 при этом находится в режиме записи в отсутствие сигнала чтения с четвертого управляющего выхода микропро- цессора 20, а дешифратор 29 адреса не работает, поскольку его адресные входы соединены только с адресными выходами микропроцессора 20, находящимися в данный момент времени в от-

ключенном (высокоимпедансном состоянии ).

По заднему фронту сигналса с выхо да синхронизатора 24 приема происхо- наращивание адреса счетчика 25 адреса, по которому происходит запись следующего байта, накапливаемого синхронизатором 24 приема.

Прием пакета осуществляется до тех ю волнения блока ОЗБ 18 непереданным

. пор, пок дешифратор 27 окончания приема по стробирующему сигналу с второго управляющего выхода микропроцессора 20 (в момент записи байта информации, осуществляемой в каждом цикле приема) не зафиксирует совпадение принимаемого байта с некоторой константой, задаваемой как конец пакета, причем данная константа одина кова для всех видов пакетов,

По окончании приема пакета (фиксирование байта Конец пакета) срабатывает дешифратор 27, сбрасывая в исходное состояние индикатор 26, который, в свою очередь, блокирует работу синхронизатора 24 приема и сбрасывает сигнал прерывания микропроцессора 20. Однако поскольку четвертый и пятый управляющие входы микропроцессора 20 являются различными по приоритету вхо дами прерывания, то по получении дан™ ного сигнала микропроцессор 20 в соответствии с фиксированным вектором прерьшания переходит к подпрограмме анализа полученного пакета (фиг, 8). При этом микропроцессор 20 взаимодействует с ПЗБ 17, обеспечивая считывание соответствующих управляющих команд через элемент И 21 (управление ПЗБ 17). Дешифратор 29 адреса работает синхронно в соответствии с адресными и управляющими сигналами, поступающими от микропроцессора 20.

Если поступивший пакет - Маркер и он предназначен для данной сетевой станции 2 (адрес получателя совпадает с собственным адресом станции) и принят правильно (что определяется проверочной последовательностью), то при наличии информации для передачи сетевая станция 2 осуществляет вьщачу данной информации по ИК.

Сетевая станция 2 в режиме выдачи информации работает следующим образом

Если анализ поля адреса получателя полученного маркера показал, что он предназначен для данной сетевой станции 2, то при наличии информации для передачи микропроцессор 20 осущест-

вляет перевод в режим выдачи. Запись передаваемого блока информации в блок ОЗБ 18 от абонента, подключенного к данной сетевой станции 2, осуществляется через соответствующий блок 3 интерфейса в соответствии с установленным стандартом С2 или ИРПС (усеченный С2). Для этого в отсутствие sai

0

5 о

5

0

5

0

5

1блоком информации микропроцессор 20 осуществляет установку блока 19 приема-передачи в режим приема, записывая, в него соответствующее управ.гшю- щее слово. Блок 19 работает в синхронном режиме в соответствии с частотой, поступающей от тактовогог генератора 23 о При установлении синхронного ре.- жима и сигнала о наличии информации у абонента осуществляется перезапись блока информации в ОЗБ 18. Если сигнал о наличии у абонента информации для передачи отсутствует и буферная часть ОЗБ 18 не заполнена, то данная сетевая станция 2 формирует маркер, передаваемый следующей по направлению передачи сетевой станции 2.

В случае наличия блока информации в буфере ОЗБ 18 осуществляется ее выдача в соответствии с форматом пакета (фиг. 6).

Для этого микропроцессор 20 осуществляет установку коммутатора 12 в положение, соответствующее работе первого 13 или второго 16 передатчика.

Необходимость наличия двух передатчиков, работающих на различных частотах, определяется выбором управляющего и информационного каналов. Если сетевая станция 2 передает маркер, то используется первый передатчик 13, работающий на частоте УК, а если передается информационный пакет или квитанция о принятии управляюще го пакета, то используется второй передатчик 16, работающий на частоте ИК. Одновременно с установкой коммутатора 12 вторым выходом триггера 32 режима осуществляются блокировка индикатора 26 и прерывание микропро- цессора 20. По этому сигналу микро-. процессор 20 осуществляет выборку из ПЗБ 17 и ОЗБ 18 последовательности байтов соответствующего пакета (фиг. 6) с одновременным формирова нием (разряды 14-16 адресного слова) команды для включения синхронизатора 30 передачи/ Выбранный байт информации заносится в регистр 11 передачи по фронту сигнала от тактового генератора 23, а синхронизатор 30 передачи форьвфует сигнал ожидания для микропроцессора 20 (поступаняций на его третий управляющий вход) в течение всего цикла передачи данного байта. Одновременно синхронизатор 30 передачи осуществляет формирование стробов сдвига регистра 11 передачи.

После вьщачи одного байта снимается сигнал ожидания с микропроцессора 20 и он выбирает следующий байт передаваемого пакета. Процесс повторяется до передачи байта конца пакета. Аналогичным образом осуществляется передача маркера и квитанции. При этом в режиме передачи сетевая станция 2 по УК устанавливается для работы с первым передатчиком 13, а блокировка индикатора 26 не осуществляется.

После выдачи информационного пакета соответствующая сетевая станция 2 его передавшая, через некоторую .задержку осуществляет формирование и выдачу маркера, разрешающего работу следующей за ней в направлении передачи сетевой станции 2, работающей аналогично,

Информационный пакет, сформированный одной из сетевых станций 2, (а затем и маркер) через соответствующие первые ключи 4, разветвители 5, усилители 6 и вторые ключи 15 всех сетевых станций 2 поступает на вход первой сетевой станции 1 (без задер ек дпя переприема), которая в релда- е приема работает аналогично сетевой станции 2 о При этом информационный ПсЖет и квитанция от сетевых станций 2 поступают через второй фильтр 57 на второй приемник 58, а маркер и квитанция поступают на ее вход и через первый фильтр на первый приемник 35.

Необходимость введения второго индикатора 59 состояния приема обусловлена тем (фиг. 4), что при выдаче пер- первой сетевой станцией 1 квитанции соответствующей сетевой станции 2 о подтверждении правильного приема от нее заданного количества информационных пакетов или квитанций об ошибке в приеме информационного пакета (которое посылается сразу же после получения ошибочного пакета) она по-

6268

падает па вход первой с -севой станции 1 и вызывает искажение принимаемого в данный момент информационного пакета. Кроме того, квитанция предназначена только Д.ПЯ конкретной сетевой станции 2, вследствие чего она не долхсна обрабатываться первой сетевой станцией 1.

Q В этом случае при поступлении информации по ИК устанавливается в 1 индикатор 59, который блокирует работу первого приемника 35 (УК). По окончании приема информационного па5 кета второй индикатор 59, как и первый индикатор 5, устанавливается в исходное состояние, С этой же целью на сетевых станциях 2 во время выда- . чи информационного пакета в канал с

0 связи блокируется индикатор 26 состояния приема.

Первая сетевая станция 1 в режиме вьщачи ин Ъормации работает аналогично сетевым станциям 2, за исключени-

25 ем операции установки необходимого передатчика, поскольку первая сетевая станция 1 осуществляет передачу только на частоте управляющего канала. После опроса всех подключенных

30 сетевых станций 2 (что определяется полу- 1ением маркера от последней из них) первая сетевая станция I выдает в канал связи маркер для следующего цикла onpqca.

При правилт-ном приеме некоторого заранее определенного) числа инфор- мационьак пакетов, первая сетевая станция 1 посылает ей квитанцию-под- твержде ше, содержащую информацию о

Q номере последнего правильно принятого информационного пакета (фиг. 4), Если пакет принят неправильно, то квитанция посьтается сразу же и данная сетевая станция 2 повторяет переjc дачу пакета в следующем цикле. Квитанции посылаются по УК.

Настройка сетевых станций 2.для работы в определенном режиме, а также управляющая информация, необходи Q мая для передачи подключенным к ним абонентам, передаются в виде управ- . ляющих пакетов, содержащих адрес конкретной сетевой станции 2 (фиг. 4). По получении данного пакета он пере- писывается в память ОЗБ 18 и выдается через блок 19 абоненту, а на первую сетевую станцию 1 по ИК выдается квитанция о получении правильного (непо-

«о

лучении)пакета.

35

9,

Во втором режиме первая сетевая cTaiiu iH 1 может выдать маркер на передачу не на первую из подключенных сетевых станций 2, а на конкретную из всей совокупности данных станций. При этом в маркере указан адрес станции, подлежащей опросу.

Работа блоков системы в данном режиме не отличается от описанной для первого режима.

Таким образом, по сравнению с известной системой передачи сообщений, принятой -за базовый объект пред лагаемая система позволяет обеспечить повышение скорости передачи сообщений и пропускной способности системы путем исключения переприемов информации в каждой промежуточной сетевой станциио

ф ормула изобретения

Система передачи сообщений, содержащая п последовательно соединенных в кольцо сетевых стангдий, вторые вход и выход которых подключены соответст- венно к выходу и входу каждого из п блоков интерфейса, причем каждая из (n-l) сетевых станций содержит после довательно соединенные первый и второй ключи, последовательно соединенные приемник, регистр приема, буфер данных, регистр передачи, к входам которого подключены информационные выходы постоянного запоминающего блока 5 информационные входы и выходы оперативного запоминающего блока, блока приема-передачи и микропроцессора, коммутатор и первый передатчик, последовательно соединенные дешифратор окончания приема, к информационным входам которого подключены выходы регистра приема, индикатор состояния приема, к второму входу которого подключен выход приемника, синхронизатор приема, второй выход которого подключен к управляющему входу регистра приема, счетчик адреса, буфер адреса, выходы которого подключены к адресным входа- постоянного запоминающего блока, оперативного запоминающего блока, блока приема - передачи и адресным выходам микропроцессора, дешифратор адреса, второй выход которого через синхронизатор передачи подключен к первому управляющему вхо;ду регистра передачи.

5

626810

триггер режима, первый выход которого подключен к управляющему входу коммутатора, и блок прерываний, первый и второй выходы которого подключены к первому и второму управляющим входам микропроцессора, к третьему управляющему входу которого подключен второй выход синхронизатора передачи,

0 к четвертому и пятому управляющим

входам микропроцессора подключены соответственно выход синхронизатора приема и первый выход тактового генератора, второй выход которого подклю-

5 чен к вторым управляющим входам синхронизатора приема, синхронизатора передачи и регистра передачи, третий вьгход тактового генератора - к входу синхронизации блока приема-передачи,

0 к первому и второму управляющим входам которого подключены первый и второй выходы микропроцессора, третий выход которого подключен к первому управлякщему входу, оперативного запо5 минающего блока и третьему управляющему входу блока приема-передачи, а к управляющему входу постоянного запоминающего блока - через элемент И, к второму входу которого подключен

0 третий выход дешифратора адреса, четвертый выход которого подключен к входу сброса счетчика адреса, четвертый вьгход микропроцессора - к третьему управляющему входу синхронизатора

5-приема, превым управляющим входам дешифратора окончания приема, буфера данных, буфера адреса, а к второму управляющему входу оперативного запоминающего блока - через элемент

0 ИЛИ, к второму входу которого подключен пятый выход дешифратора адреса, к первому и второму управляющим входам которого подключены пятый и шестой выходы микропроцессора, а вы-

5 ход индикатора состояния приема под- кх;ючен к второму входу блока, прерывания, первая из п сетевых станций содержит первый приемник, последовательно соединенные первый и второй

0 ключи, к второму входу последнего подключен передатчик, последовательно соединенные регистр приема, буфер данных и регистр передачи, к входам которого подключены информационные

5 выходы постоянного запоминающего

блока, информационные входы и выходы оперативного запоминающего блока, блока приема-передачи и микропроцессора, последовательно соединенные де-

шифратор окончания приема, к информационным входам которого подключены выходы регистра приема, первый индикатор состояния приема, к второму входу которого подключен вход регистра приема, синхронизатор приема, второй выход которого подключен к управляющему входу регистра приема, счетчик адреса, буфер адреса, выходы которого подключены к адресным входам постоянного запоминающего блока, оперативного запоминающего блока, блока приема-передачи и адресным выходам микропроцессора, дешифратор адреса, к первому и BTOpobfy управляющим входам которого подключены первый и второй выходы микропроцессора, и синхронизатор передачи, первый выход которого подключен к первому управляюще-

му входу регистра передачи, к второму управляющему входу которого, управляющему входу синхронизатора передачи, второму управляющему входу синхронизатора приема подключен первый выход тактового генератора, второй выход которого подключен к входу синхронизации блока приема-передачи, третий выход - к первому управляющему входу микропроцессора, к второму управляющему входу которого подключен первьш выход синхронизатора приема, к третьему управляющему входу микропроцессора - второй выход синхронизатора передачИэ третьи и четвертые вькоды микропроцессора - к первому и второму управляющим входам блока приема-передачи, пятый выход - к третьему управляющему входу блока приема-передачи, к первому з правляющему входу оперативного запоминающего блока, а к управляющему входу постоянного запоминающего блока - через элемент И, к второму входу которого под-

ключей второй выход дешифратора адре- д второму входу которого подключен вы-

са, третий выход которого подключен к входу сброса счетчика адреса, щес- той выход микропроцессора - к третьему управляющему входу синхронизатора

ход второго индикатора состояния приема, соединен с вторым входом сумматора, при этом пятый вьпход дешифратора адреса подключен к-второму входу

приема, управляющим входам буфера ад- Q блока прерывания,а выход регистра пе- реса, дешифратора окончания приема, редачи подключен к входу передатчика.

бусЬера данных, я к (зторому управляющему входу оперативного запоминающего блока - через элемент liJUl, к вто- входу которого подключен четвертый выход дешифратора адреса, к четвертому и пятому управляющим входам микропроцессора подключены первый и второй выходы блока прерываний, к первому входу которого подключен выход первого индикатора состояния приема, о т л и ч а 10 щ а я с я тем, что5 с целью повышения пропускной способности системы путем уменьшения времени переприема, в ка;кдую .из (п-1) сетевых станций введены второй передатчик, фильтр, выход которого подключен к входу приемника, второй выход первого ключа через введенные последовательно соединенные развет- витель, второй выход которого подключен к входу фильтра, усилитель и сумматор, к второму и TpeTbeNry входам которого подключены соответст-

венно выход первого п ередатчика и второй выход коммутатора через второй передатчик, соединен с вторым входом второго ключа, при этом второй выход триггера режима подключен к

к управляюще гу входу первого индикатора приема, а в первую из п сетевых станций введены второй индикатор состояния приема, к первому входу которого подключен выход дешифратора

окончания приема,, первый фильтр, сумматор, а второй выход первого ключа через введенные последовательно соединенные второй фильтр и второй при емник подключен к первому входу сум-

матора, выход которого подключен к входу регистра приема и второму входу первого индикатора состояния приема, а через последовательно соединенные первый фильтр и первьм приемник, к

ход второго индикатора состояния приема, соединен с вторым входом сумматора, при этом пятый вьпход дешифратора адреса подключен к-второму входу

,-.V

L

9 У Vi:4

I1„„„™ „ fff

L:™5ii i: ±..;:.:,.. .„.,.,..

lU

„ГЖ

;:

4.rh. 56 :57 L-: З/Ц I f

fi/7 ., Sf-sf «-.,,-,. ,7« |-,-.,2 .A ...„

,-..„,.,1,..,

lt SE rr:-: :-E;

, W r......-i---i:r- -1li

i :::-:,:::;:::;;z:l ,/.5

L.:

::::::::...

.ИЛИИc::is i,..ni:iM.kLJL-.

Ндитанция

., „.,,J1L

Квитанция

LJZIllU:: -, JIL.,.,МЖ.„.

.Mjz:a,.i::jiia.

JBXniCIHIJI......i.,J11..1,-..

.1Г111х:ж,.ж.1:111ЛГ1|.....

Фиа.

Начало пакета Кдрес попдцателц figpec отправителя Упрвблгние

Инфорпация

ПроВвро1-1ная последпВв- ,jn MHocm

КОНЕЦ пакета

Напало пакета flgpec попдчаткм Ядрес отправители

Управление

Проверочная тследода

Конец ппквгпа

(рйрн1}ционншй. (упраЗлающи) пакет

Поркер

| название | год | авторы | номер документа |

|---|---|---|---|

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

| Кольцевая пакетная сеть передачи информации | 1987 |

|

SU1555888A1 |

| Устройство для передачи информации с обратной связью | 1986 |

|

SU1322356A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Сетевой контроллер | 1988 |

|

SU1564641A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

| Кольцевая пакетная сеть | 1988 |

|

SU1660192A1 |

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

Изобретение относится к технике связи и может использоваться в системах телеуправления и сбора информации. Цель изобретения - повьшение пропускной способности системы путем уменьшения времени переприема. Система состоит из п последовательно соединенных в кольцо сетевых станций (СС),, каждая из которых имеет свой интерфейс 3. Ее работа основана на том факте, что все функции по управлению и сбору сообщений м.б. возложены на одну из СС, например, СС 1. Б системе используется циклическое кольцо с передачей полномочий (маркера) и организацией двух частотно-независимых каналов - информационного (ИК) и управляющего (УК). Сбор информации от СС 2 осуществляется по ИК, а управление ими - по УК. В системе передаются четыре вида информации: информационный пакет, маркер, управляющий пакет и пакет-квитанция. Маркер, управляющий пакет и пакет-квитанция от СС 1 передаются по УК, а информационный пакет и пакет-квитанция от СС 2- по ИК. СС I задает один из двух режимов работы: последовательный опрос всех СС 2 или опрос заданной группы СС 2. Поясняется работа СС 1, 2 в этих режимах. 8 ил. СлР СП О) ю а: оо

Начало пакетз йдрес nongi meflu figpec отпра&итЕла

Управление OmSem

пдитсгиция

проКёрочная последоЗа- г1емьностд

Конец пакета

Включение питания и инИцциробание протопопа

Передала парке- ра Выбранной СС2поУК

ндикааия

о Hoptianbиой работе

сети

Анализ ра- 5йты сета

Т нализ поля упробле

. битан- ция управление

блокировка УК на 8ре- пя приема ин(popнации по и К.

Побторная передача управления по УК для данной СС2

Инда/сациа

opaffome

сети

да

uepegat a кбитанции для ПСС1

по УК

Фиг. 7

питание и unuituupoBoHi s протокот

IIIZIIII3ZIZIIIIII

Ожидание иифорпации

по УК

л шг

. fiUKem -ч., принят f

- пакепг - ОЛЯ данной ; Jc2t/- тт.

йнтаишт поШдт ПШ

.- mrfffl - f- /

},- 1Ш. l. „

J t - - /J/ /s i-iK .jiff.Ksma

. ,j j uBumHdf - х- ,dtf-- ,& yf msHHiML f

,..- , -.инфорг/аци Я wem ---. ,,-Гши тгмсвоего ааркер

Передача LO-apop- паиаи по дпя

ncci

.„i r;inzy :i; iii; i., I „,, J Иер(ор /а -юркет ---J

fw УК gfH следд- L ...

«й гй | ,

S ПоВтор редаиа Взиног па

.

,

,, Принап

- Конец - ii tf/aff пикк - В Ч

г-, правильн

-

I Шшдоние кдитанции

Й5/71 Kfjiirnaif

,/|//Я

Редактор А„ Огар 5815/57

Составитель Л, Тимошина

Техред Л.Сердюхова Корректор С. Черни

Т Ир аж 636П од пи с н о е

ВНИИПИ Государственного комитета СССР

по далам изобретений и открытий 1130355 Москва, Ж-ЗЗ, Раушская наб., Д.

Производствекно-т олиграфическое предприятие; г З жгород, угь Проектная, 4

nepegava

кдатанииа

поМК g/is

пса

I „,, ---J

своего ааркеро.

™-

S ПоВторнт пе- редаиа заВрико- Взиного икета па ик

- HSfn

,, Принапг

г-, правильно

-

| Автоматизированные учрежденческие системы на базе ЛВС Эстафета ЩНТИ, ГПКИАСУ, 1985 | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-11-30—Публикация

1986-06-26—Подача