СП

О Ј О5 Јь

315

Изобретение относится к вычислительной технике, а именно обмену информацией между станциями (абонентами) локальной управляющей вычислительной сети, и может быть использовано в АСУ технологическими агрега тами и процессами.

Цель изобретения - повышение скорости передачи информации и расширение протокольных функций контроллера о

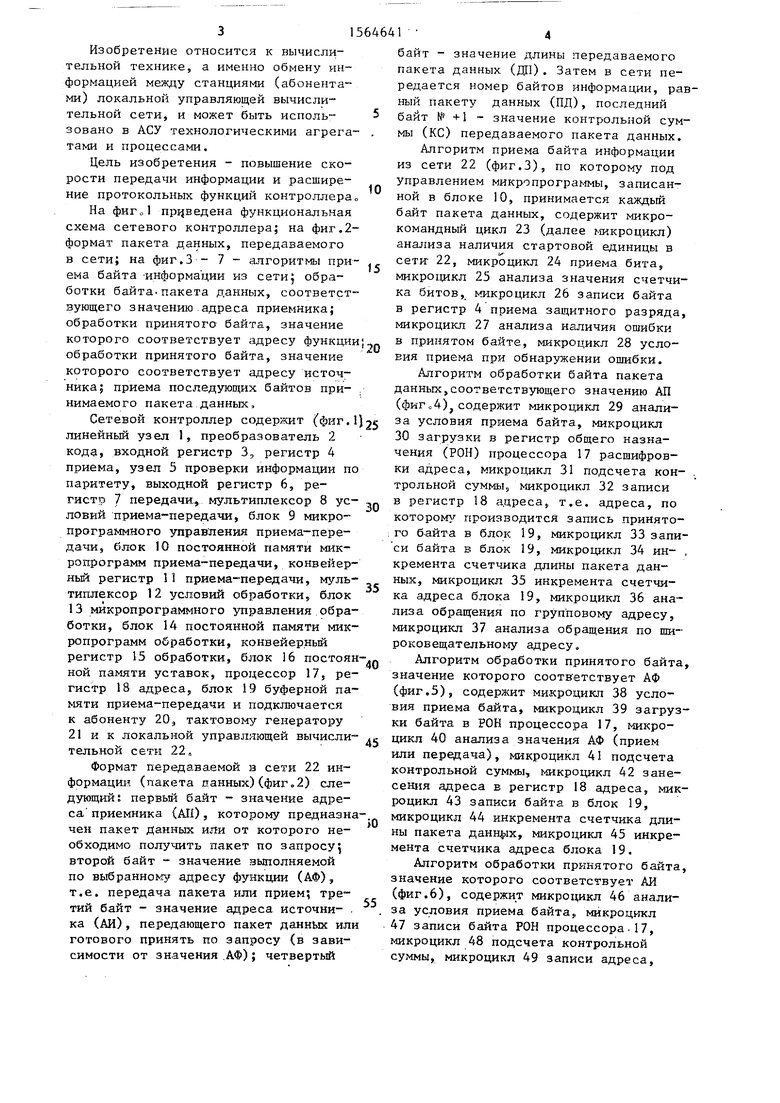

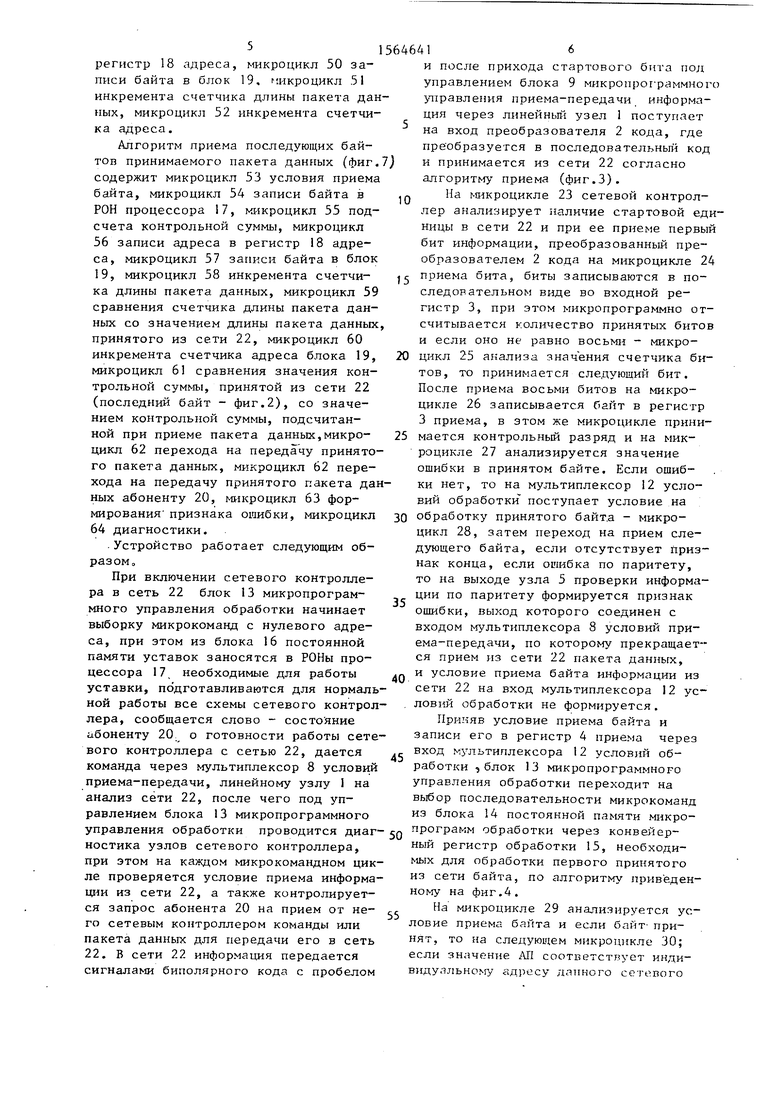

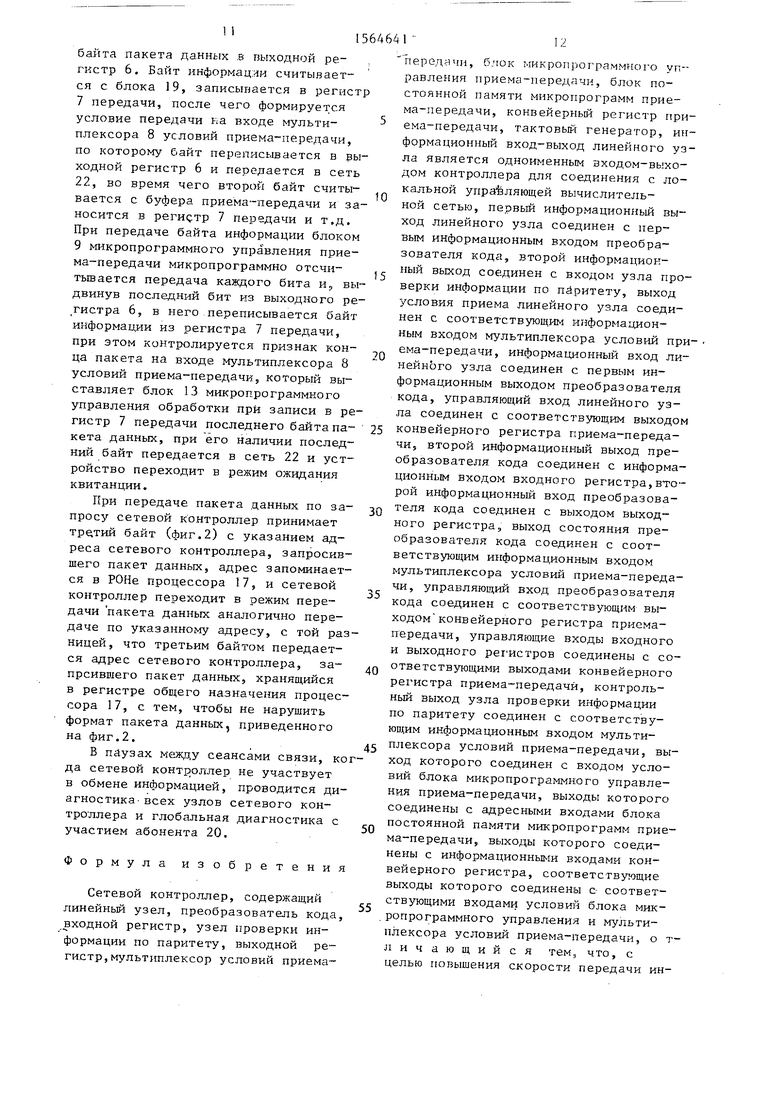

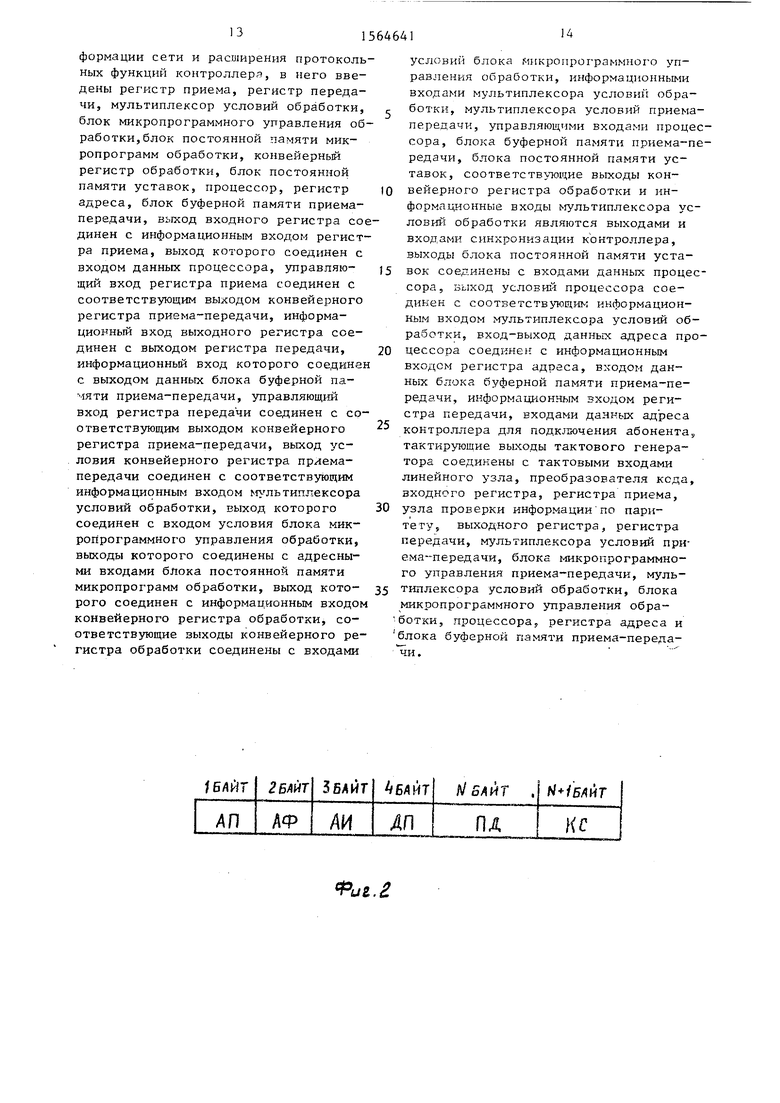

На фиг приведена функциональная схема сетевого контроллера; на фиг. 2- формат пакета данных, передаваемого в сети; на фиг.З - 7 - .алгоритмы приема байта информации из сети} обработки байта.пакета данных, соответствующего значению адреса приемника; обработки принятого байта, значение

байт - значение длины передаваемого пакета данных (ДП). Затем в сети передается номер байтов информации, равный пакету данных (ПД), последний байт № +1 - значение контрольной суммы (КС) передаваемого пакета данных.

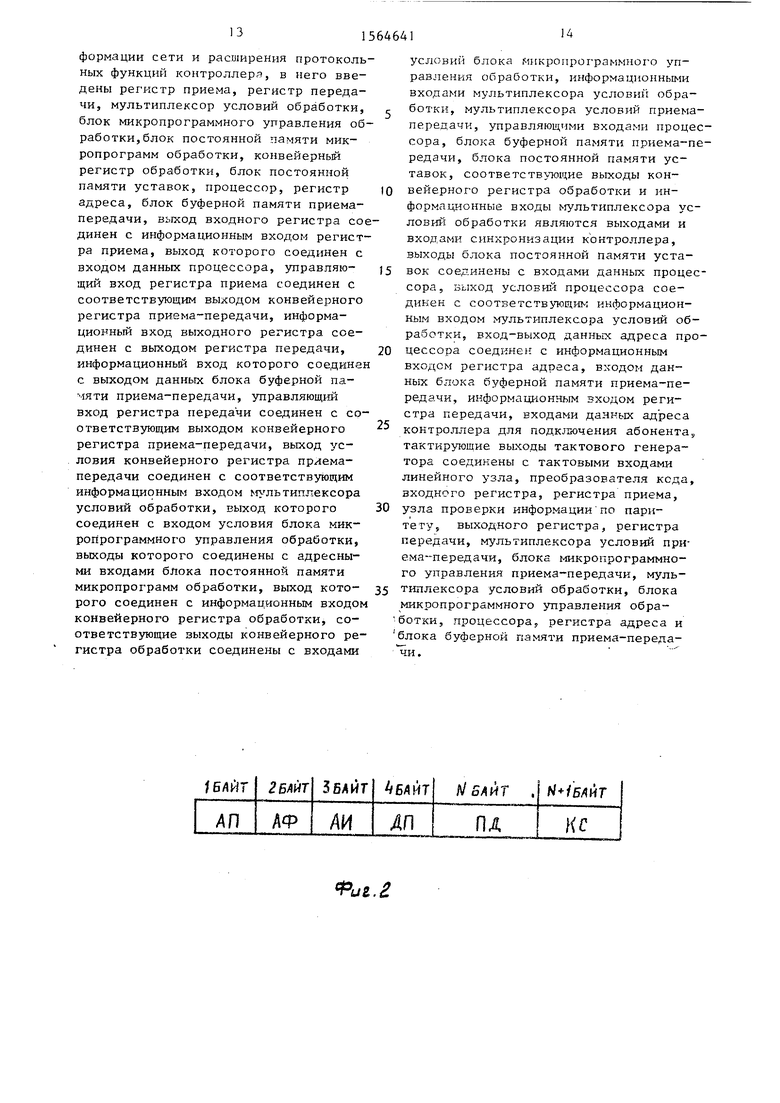

Алгоритм приема байта информации из сети 22 (фиг.З), по которому под управлением микропрограммы, записанной в блоке 10, принимается каждый байт пакета данных, содержит микрокомандный цикл 23 (далее микроцикл) анализа наличия стартовой единицы в сети 22, микроцикл 24 приема бита, микроцикл 25 анализа значения счетчика битов, микроцикл 26 записи байта в регистр 4 приема защитного разряда, микроцикл 27 анализа наличия ошибки

| название | год | авторы | номер документа |

|---|---|---|---|

| Контроллер станции локальной сети | 1988 |

|

SU1647590A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ И ДОСТУПА К КАНАЛУ ДЛЯ ЛОКАЛЬНОЙ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 1992 |

|

RU2060539C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ КОМПОНЕНТ ПРОГРАММ И СХЕМА УПРАВЛЕНИЯ ПАМЯТЬЮ ДЛЯ ТРАНСПОРТНОГО ПРОЦЕССОРА | 1995 |

|

RU2145728C1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| СИСТЕМА И СПОСОБ ПОДДЕРЖАНИЯ ВРЕМЕННОЙ СИНХРОНИЗАЦИИ В СЕТИ ЦИФРОВОГО ВИДЕО | 1998 |

|

RU2222116C2 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

Изобретение относится к вычислительной технике, а именно обмену информацией между станциями (абонентами) локальной управляющей вычислительной сети, и может быть использовано в АСУ технологическими агрегатами и процессами. Целью изобретения является повышение скорости передачи информации и расширение протокольных функций контроллера. Сетевой контролер содержит линейный узел 1, преобразователь кода 2, входной регистр 3, регистр приема 4, узел 5 проверки информации по паритету, выходной регистр 6, регистр передачи 7, мультиплексор 9 условий приемопередачи, блок 10 постоянной памяти микропрограмм приемопередачи, конвейерный регистр 11 приемопередачи, мультиплексор 12 условия обработки, блок 13 микропрограммного управления обработки, блок 14 постоянной памяти микропрограмм обработки, конвейерный регистр 15 обработки, блок 16 постоянной памяти уставок, процессор 17, регистр 18 адреса, блок 19 буферной памяти приемопередачи и подключается к абоненту 20, тактовому генератору 21 и к локальной управляющей вычислительной сети 22. 7 ил.

которого соответствует адресу функции;.,- в принятом байте, микроцикл 28 усло- обработки принятого байта, значение вия приема при обнаружении ошибки, которого соответствует адресу источ- Алгоритм обработки байта пакета ника; приема последующих байтов принимаемого пакета данных,

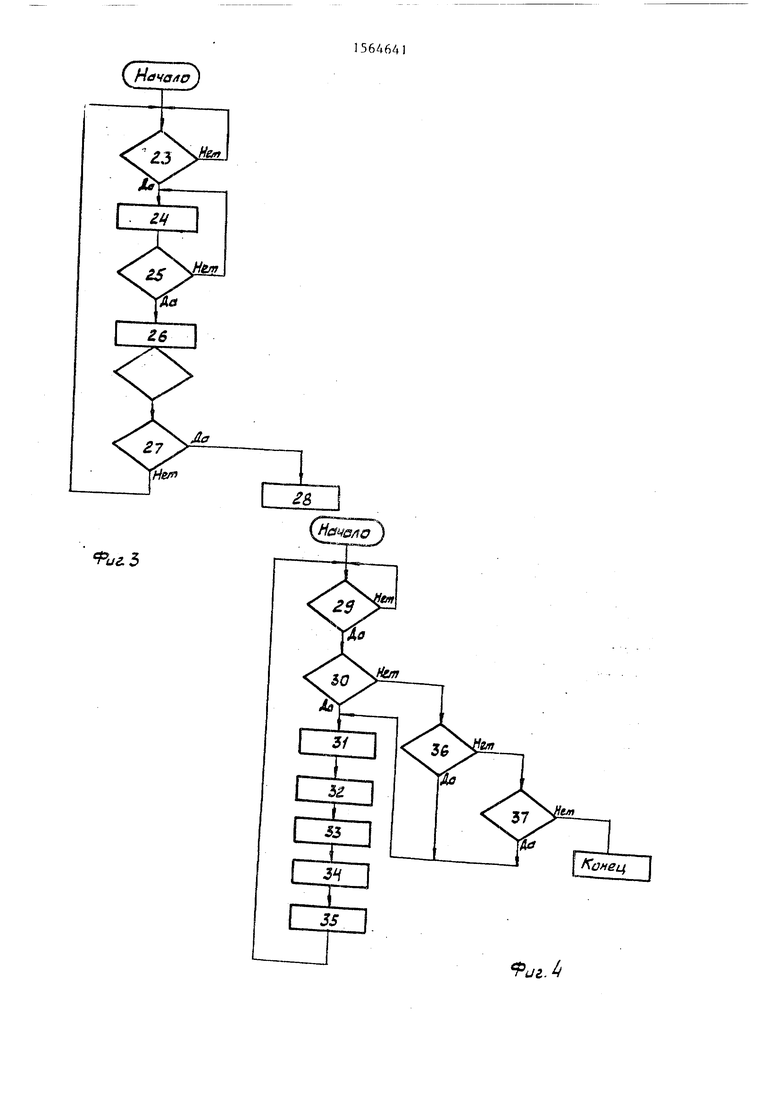

данных,соответствующего значению АЛ (фиго4)содержит микроцикл 29 аналиданных,соответствующего значению АЛ (фиго4)содержит микроцикл 29 анал

Сетевой контроллер содержит (фиг.1)25 за условия приема байта, микроцикл

30

линейный узел 1, преобразователь 2 кода, входной регистр Зэ регистр 4 приема, узел 5 проверки информации по паритету, выходной регистр 6, ре- гистп 7 передачи., мультиплексор 8 условий приема-передачи, блок 9 микропрограммного управления приема-передачи,, блок 10 постоянной памяти микропрограмм приема-передачи, конвейерный регистр i приема-передачи, мультиплексор 12 условий обработки, блок 13 микропрограммного управления обработки, блок 14 постоянной памяти микропрограмм обработки, конвейерный регистр 15 обработки, блок 16 постоян-,- ной памяти уставок, процессор 17, регистр 18 адреса, блок 19 буферной памяти приема-передачи и подключается к абоненту 20, тактовому генератору

35

30 загрузки в регистр общего назначения (РОН) процессора 17 расшифро ки адреса, микроцикл 31 подсчета ко трольной суммы5 микроцикл 32 записи в регистр 18 адреса, т.е. адреса, п котором - производится запись принят го байта в блок 19, микроцикл 33 за си байта в блок 19, микроцикл 34 ин кремента счетчика длины пакета данных, микроцикл 35 инкремента счетчи ка адреса блока 19, микроцикл 36 ан лиза обращения по групповому адресу микроцикл 37 анализа обращения по ш роковещательному адресу.

Алгоритм обработки принятого бай значение которого соответствует АФ (фиг.З), содержит микроцикл 38 усло вия приема байта, микроцикл 39 загр ки байта в РОН процессора 17, микро

21 и к локальной управляющей вычисли- цикл 40 анализа значения АФ (прием

тельной сети 22

Формат передаваемой в сети 22 информации (пакета данных)(фиг,2) следующий i первый байт - значение адреса приемника (ATI), которому преднаэна-.

Ю

или передача), микроцикл 41 подсчет контрольной суммы, микроцикл 42 зан сения адреса в регистр 18 адреса, м роцикл 43 записи байта в блок 19, микроцикл 44 инкремента счетчика дл ны пакета данных, микроцикл 45 инкр мента счетчика адреса блока 19.

чен пакет данных или от которого необходимо получить пакет по запросуj второй байт - значение выполняемой по выбранному адресу функции (АФ), т.е. передача пакета или прием; третий байт - значение адреса источника (АИ), передающего пакет данных или готового принять по запросу (в зависимости от значения АФ); четвертый

в принятом байте, микроцикл 28 усло- вия приема при обнаружении ошибки, Алгоритм обработки байта пакета

данных,соответствующего значению АЛ (фиго4)содержит микроцикл 29 анализа условия приема байта, микроцикл

за условия приема байта, микроцикл

30 загрузки в регистр общего назначения (РОН) процессора 17 расшифровки адреса, микроцикл 31 подсчета контрольной суммы5 микроцикл 32 записи в регистр 18 адреса, т.е. адреса, по котором - производится запись принятого байта в блок 19, микроцикл 33 записи байта в блок 19, микроцикл 34 ин- . кремента счетчика длины пакета данных, микроцикл 35 инкремента счетчика адреса блока 19, микроцикл 36 анализа обращения по групповому адресу, микроцикл 37 анализа обращения по широковещательному адресу.

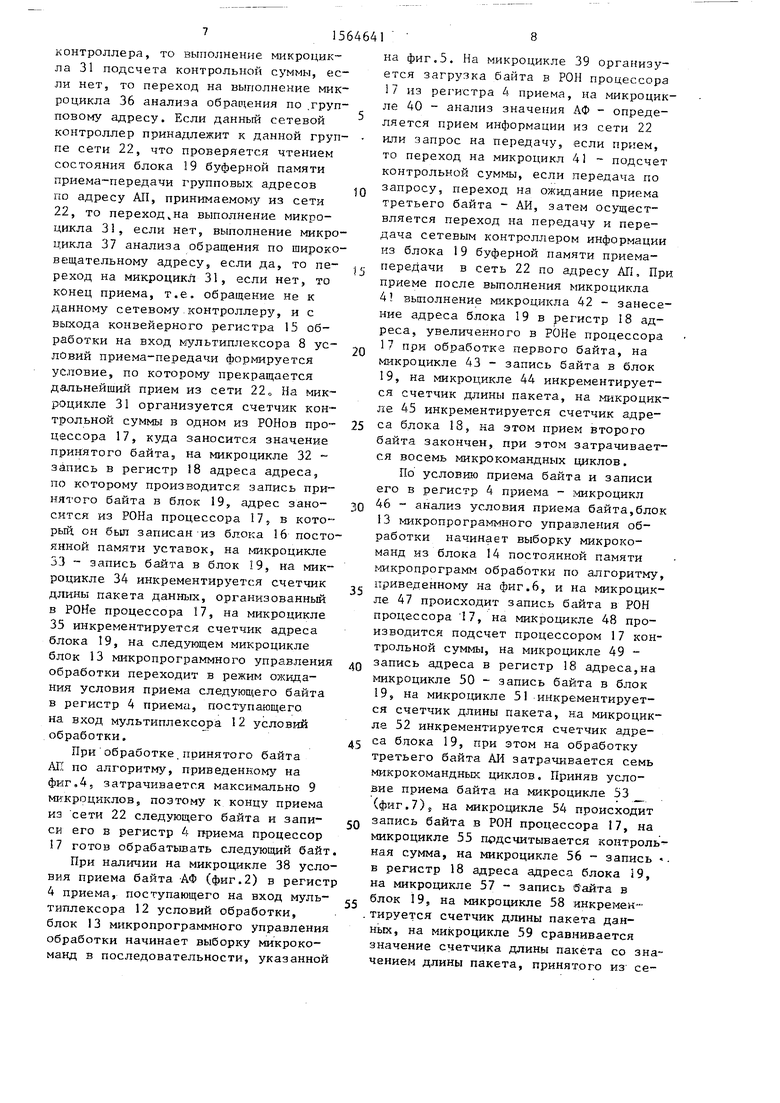

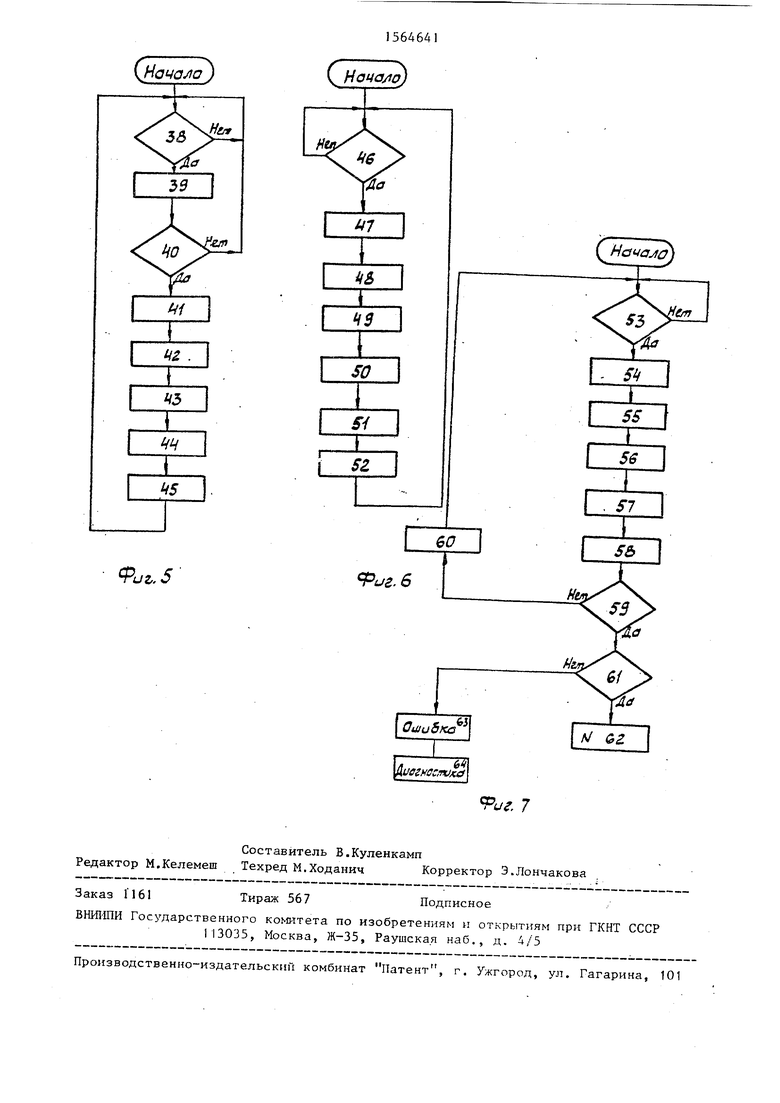

Алгоритм обработки принятого байта, значение которого соответствует АФ (фиг.З), содержит микроцикл 38 условия приема байта, микроцикл 39 загрузки байта в РОН процессора 17, микроцикл 40 анализа значения АФ (прием

или передача), микроцикл 41 подсчета контрольной суммы, микроцикл 42 занесения адреса в регистр 18 адреса, микроцикл 43 записи байта в блок 19, микроцикл 44 инкремента счетчика длины пакета данных, микроцикл 45 инкремента счетчика адреса блока 19.

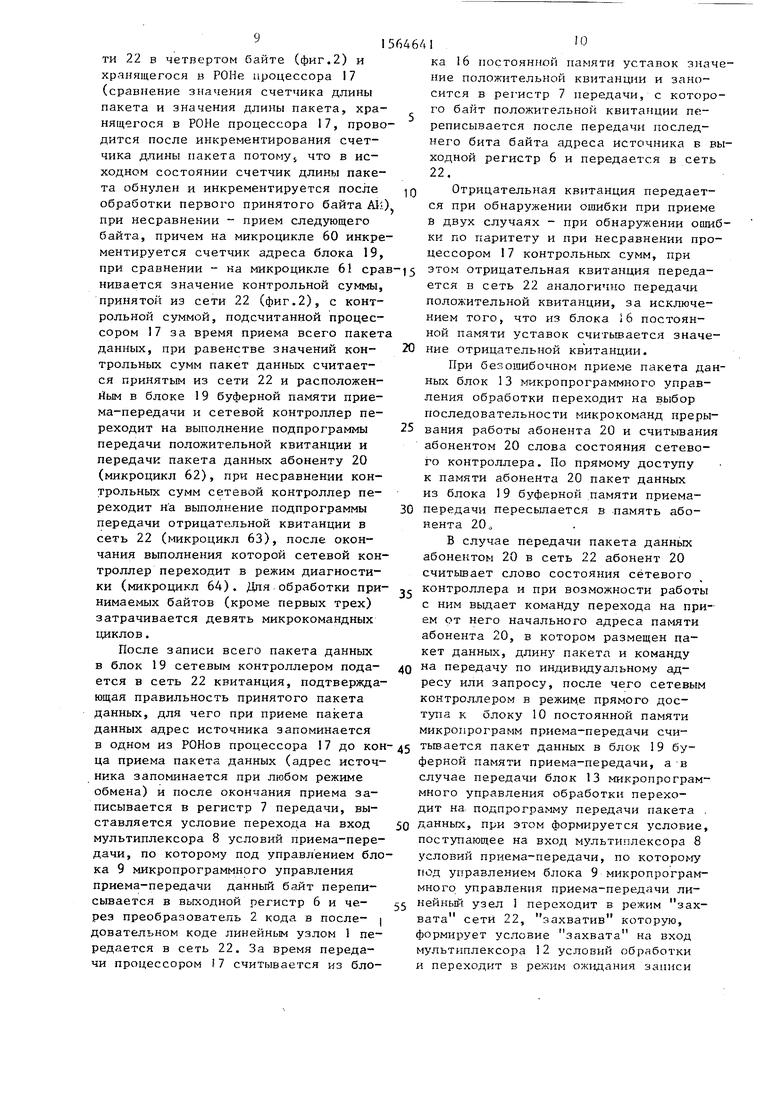

Алгоритм обработки принятого байта, значение которого соответствует АИ (фиг.6), содержит микроцикл 46 анализа условия приема байта, микроцикл 47 записи байта РОН процессора.17, микроцикл 48 подсчета контрольной суммы, микроцикл 49 записи адреса,

регистр 18 адреса, микроцикл 50 записи байта в блок 19, микроцикл 51 инкремента счетчика длины пакета данных, микроцикл 52 инкремента счетчика адреса.

Алгоритм приема последующих байтов принимаемого пакета данных (фиг. содержит микроцикл 53 условия приема байта, микроцикл 54 записи байта в РОН процессора 17, микроцикл 55 подсчета контрольной суммы, микроцикл 56 записи адреса в регистр 18 адреса, микроцикл 57 записи байта в блок 19, микроцикл 58 инкремента счетчика длины пакета данных, микроцикл 59 сравнения счетчика длины пакета данных со значением длины пакета данных принятого из сети 22, микроцикл 60 инкремента счетчика адреса блока 19, микроцикл 61 сравнения значения контрольной суммы, принятой из сети 22 (последний байт - фиг.2), со значением контрольной суммы, подсчитанной при приеме пакета данных,микроцикл 62 перехода на передачу принятого пакета данных, микроцикл 62 перехода на передачу принятого пакета данных абоненту 20, микроцикл 63 формирования признака ошибки, микроцикл 64 диагностики.

Устройство работает следующим образом

При включении сетевого контроллера в сеть 22 блок 13 микропрограммного управления обработки начинает выборку микрокоманд с нулевого адреса, при этом из блока 16 постоянной

На микроцикле 23 сетевой контроллер анализирует наличие стартовой ед ницы в сети 22 и при ее приеме первы бит информации, преобразованный преобразователем 2 кода на микроцикле 2 .с приема бита, биты записываются в последовательном виде во входной регистр 3, при этом микропрограммно от считывается количество принятых бито и если оно не равно восьми - микроцикл 25 анализа значения счетчика би тов, то принимается следующий бит. После приема восьми битов на микроцикле 26 записывается байт в регистр 3 приема, в этом же микроцнкле принимается контрольный разряд и на микроцикле 27 анализируется значение ошибки в принятом байте. Если ошибки нет, то на мультиплексор 12 условий обработки поступает условие на обработку принятого байта - микроцикл 28, затем переход на прием следующего байта, если отсутствует признак конца, если ошибка по паритету, то на выходе узла 5 проверки информации по паритету формируется признак ошибки, выход которого соединен с входом мультиплексора 8 условий приема-передачи, по которому прекращается прием из сети 22 пакета данных, и условие приема байта информации из сети 22 на вход мультиплексора 12 условий обработки не формируется.

Приняв условие приема байта и записи его в регистр 4 приема через вход мультиплексора 12 условий об40

памяти уставок заносятся в РОНы процессора 17, необходимые для работы уставки, подготавливаются для нормальной работы все схемы сетевого контроллера, сообщается слово - состояние абоненту 20 о готовности работы сетевого контроллера с сетью 22, дается дс команда через мультиплексор 8 условий работки , блок 13 микропрограммного

управления обработки переходит на выбор последовательности микрокоманд из блока 14 постоянной памяти микроуправления обработки проводится диаг- 50 пР°гРакм обработки через конвейер- ностика узлов сетевого контроллера, ный регистр обработки 15, необходи- при этом на каждом микрокомандном цик- №1Х Для обработки первого принятого ле проверяется условие приема информа- из сети байта, по алгоритму приведен- ции из сети 22, а также контролирует- ному на фиг.4. ся запрос абонента 20 на прием от не- -,приема-передачи, линейному узлу I на анализ сети 22, после чего под управлением блока 13 микропрограммного

На микроцикле 29 анализируется условие приема байта и если байт принят, то на следующем микроцнкле 30; если значение АЛ соответствует индивидуальному адресу данного сетевого

го сетевым контроллером команды или пакета данных для передачи его в сеть 22. В сети 22 информация передается сигналами биполярного кода с пробелом

10

20

и после прихода стартового бита под управлением блока 9 микропрограммного управления приема-передачи информация через линейный узел 1 поступает на вход преобразователя 2 кода, где преобразуется в последовательный код и принимается из сети 22 согласно алгоритму приема (фиг.З).

На микроцикле 23 сетевой контроллер анализирует наличие стартовой единицы в сети 22 и при ее приеме первый бит информации, преобразованный преобразователем 2 кода на микроцикле 24 .с приема бита, биты записываются в последовательном виде во входной регистр 3, при этом микропрограммно отсчитывается количество принятых битов и если оно не равно восьми - микроцикл 25 анализа значения счетчика битов, то принимается следующий бит. После приема восьми битов на микроцикле 26 записывается байт в регистр 3 приема, в этом же микроцнкле принимается контрольный разряд и на микроцикле 27 анализируется значение ошибки в принятом байте. Если ошибки нет, то на мультиплексор 12 условий обработки поступает условие на обработку принятого байта - микроцикл 28, затем переход на прием следующего байта, если отсутствует признак конца, если ошибка по паритету, то на выходе узла 5 проверки информации по паритету формируется признак ошибки, выход которого соединен с входом мультиплексора 8 условий приема-передачи, по которому прекращается прием из сети 22 пакета данных, и условие приема байта информации из сети 22 на вход мультиплексора 12 условий обработки не формируется.

Приняв условие приема байта и записи его в регистр 4 приема через вход мультиплексора 12 условий об5

0

5

0

с работки , блок 13 микропрограммного

управления обработки переходит на выбор последовательности микрокоманд из блока 14 постоянной памяти микропР°гРакм обработки через конвейер- ный регистр обработки 15, необходи- №1Х Для обработки первого принятого из сети байта, по алгоритму приведен- ному на фиг.4.

На микроцикле 29 анализируется условие приема байта и если байт принят, то на следующем микроцнкле 30; если значение АЛ соответствует индивидуальному адресу данного сетевого

контроллера, то выполнение микроцикла 31 подсчета контрольной суммы, если нет, то переход на выполнение микроцикла 36 анализа обращения по групповому адресу. Если данный сетевой контроллер принадлежит к данной группе сети 22, что проверяется чтением состояния блока 19 буферной памяти приема-передачи групповых адресов по адресу All, принимаемому из сети 22, то переход,.на выполнение микроцикла 3, если нет, выполнение микроцикла 37 анализа обращения по широковещательному адресу, если да, то переход на микроцикл 31, если нет, то конец приема, т.е. обращение не к данному сетевому контроллеру, и с выхода конвейерного регистра 15 обработки на вход мультиплексора 8 ус- лОвий приема-передачи формируется условие, по которому прекращается дальнейший прием из сети 22„ На мик рецикле 31 организуется счетчик контрольной суммы в одном из РОНов процессора 17, куда заносится значение принятого байта,, на микроцикле 32 запись в регистр 18 адреса адреса, по которому производится запись принятого байта в блок 19, адрес заносится из РОНа процессора 17, в который, он был записан из блока 16 постоянной памяти уставок, на микроцикле 33 - запись байта в блок 19, на микроцикле 34 инкрементируется счетчик длины пакета данных, организованный в РОНе процессора 17, на микроцикле 35 инкрементируется счетчик адреса блока 19, на следующем микроцикле блок 13 микропрограммного управления обработки переходит в режим ожидания условия приема следующего байта в регистр 4 приема, поступающего на вход мультиплексора 12 условий обработки.

При обработке.принятого байта АЛ по алгоритму, приведеньому на фиг.45 затрачивается максимально 9 микроциклов, поэтому к концу приема из сети 22 следующего байта и записи его в регистр 4 приема процессор 17 готов обрабатывать следующий байт При наличии на микроцикле 38 условия приема байта АФ (фиг.2) в регист 4 приема, поступающего на вход мультиплексора 12 условий обработки, блок 13 микропрограммного управления обработки начинает выборку микрокоманд в последовательности, указанной

0

5

0

5

0

5

50

5

на фиг.5. На микроцикле 39 организуется загрузка байта в РОН процессора 17 из регистра 4 приема, на микроцикле 40 - анализ значения АФ - определяется прием информации из сети 22 или запрос на передачу, если прием, то переход на микроцикл 41 - подсчет контрольной суммы, если передача по запросу, переход на ожидание приема третьего байта - АИ, затем осуществляется переход на передачу и передача сетевым контроллером информации из блока 19 буферной памяти приема- передачи в сеть 22 по адресу АЛ, При приеме после выполнения микроцикла 4 выполнение микроцикла 42 - занесение адреса блока 19 в регистр 18 адреса, увеличенного в РОНе процессора 17 при обработке первого байта, на микроцикле 43 - запись байта в блок 19, на микроцикле 44 инкрементируется счетчик длины пакета, на микроцикле 45 инкрементируется счетчик адреса блока 18, ка этом прием второго байга закончен, при этом затрачивается восемь микрокомандных циклов.

По условию приема байта и записи его в регистр 4 приема - чикроцикл 46 - анализ условия приема байта,блок 13 микропрограммного управления обработки начинает выборку микрокоманд из блока 14 постоянной памяти микропрограмм обработки по алгоритму, приведенному на фиг.6, и на микроцикле 47 происходит запись байта в РОН процессора 17, на микроцикле 48 производится подсчет процессором 17 контрольной суммы, на микроцикле 49 - запись адреса в регистр 18 адреса,на микроцикле 50 - запись байта в блок 19, на микроцикле 51 инкрементируется счетчик длины пакета, на микроцикле 52 инкрементируется счетчик адреса блока 19, при этом на обработку третьего байта АИ затрачивается семь микрокомандных циклов. Приняв условие приема байта на микроцикле 53

(фиг.7), на микроцикле 54 происходит запись байта в РОН процессора 17, на микроцикле 55 подсчитывается контрольная сумма, на микроцикле 56 - запись « в регистр 18 адреса адреса блока 19, на микроцикле 57 - запись байта в блок 19, на микроцикле 58 инкремек™ . тируется счетчик длины пакета данных, на микроцикле 59 сравнивается значение счетчика длины пакета со значением длины пакета, принятого из сети 22 в четвертом байте (фиг.2) и хранящегося в РОНе процессора 17 (сравнение значения счетчика длины пакета и значения длины пакета, хранящегося в РОНе процессора 17, проводится после инкрементирования счетчика длины пакета потому4 что в исходном состоянии счетчик длины пакета обнулен и инкрементируется после обработки первого принятого байта АИ), при несравнении прием следующего байта, причем на микроцикле 60 инкрементируется счетчик адреса блока 19,

при сравнении - на микроцикле 61 срав- 5 этом отрицательная квитанция переда- нивается значение контрольной суммы, ется в сеть 22 аналогично передачи принятой из сети 22 (фиг.2), с конт- положительной квитанции, за исключе- рольной суммой, подсчитанной процессором 17 за время приема всего пакета

нием того, что из блока 16 постоянной памяти уставок считывается значеданных, при равенстве значений контрольных сумм пакет данных считается принятым из сети 22 и расположен- йым в блоке 19 буферной памяти приема-передачи и сетевой контроллер переходит на выполнение подпрограммы передачи положительной квитанции и передачи пакета данных абоненту 20 (микроцикл 62), при несравнении контрольных сумм сетевой контроллер переходит н а выполнение подпрограммы передачи отрицательной квитанции в сеть 22 (микроцикл 63), после окончания выполнения которой сетевой контроллер переходит в режим диагностики (микроцикл 64). Для обработки принимаемых байтов (кроме первых трех) затрачивается девять микрокомандных циклов.

После записи всего пакета данных в блок 19 сетевым контроллером подается в сеть 22 квитанция, подтверждающая правильность принятого пакета данных, для чего при приеме пакета данных адрес источника запоминается

в одном из РОНов процессора 17 до кон-45 тывается пакет данных в блок 19 бу- ца приема пакета данных (адрес источ- ферной памяти приема-передачи, а в

ника запоминается при любом режиме обмена) и после окончания приема записывается в регистр 7 передачи, выставляется условие перехода на вход мультиплексора 8 условий приема-передачи, по которому под управлением блока 9 микропрограммного управления приема-передачи данный байт переписывается в выходной регистр 6 и через преобразователь 2 кода в после- | довательном коде линейным узлом 1 передается в сеть 22. За время передачи процессором 7 считывается из бло

464I10

ка 16 постоянной памяти уставок значение положительной квитанции и заносится в регистр 7 передачи, с которого байт положительной квитанции переписывается после передачи последнего бита байта адреса источника в выходной регистр 6 и передается в сеть 22.

IQ Отрицательная квитанция передается при обнаружении ошибки при приеме в двух случаях - при обнаружении ошибки по паритету и при несравнении процессором 17 контрольных сумм, при

этом отрицательная квитанция переда- ется в сеть 22 аналогично передачи положительной квитанции, за исключе-

нием того, что из блока 16 постоянной памяти уставок считывается значе

ние отрицательной квитанции.

При безошибочном приеме пакета данных блок 13 микропрограммного управления обработки переходит на выбор последовательности микрокоманд прерывания работы абонента 20 и считывания абонентом 20 слова состояния сетевого контроллера. По прямому доступу к памяти абонента 20 пакет данных из блока 19 буферной памяти приемапередачи пересылается в память абонента 20 „

В случае передачи пакета данных абонентом 20 в сеть 22 абонент 20 считывает слово состояния сетевого

контроллера и при возможности работы с ним выдает команду перехода на прием от него начального адреса памяти абонента 20, в котором размещен пакет данных, длину пакета и команду

на передачу по индивидуальному адресу или запросу, после чего сетевым контроллером в режиме прямого доступа к блоку 10 постоянной памяти микропрограмм приема-передачи счислучае передачи блок 13 микропрограммного управления обработки переходит на подпрограмму передачи пакета .

данных, при этом формируется условие, поступающее на вход мультиплексора 8 условий приема-передачи, по которому под управлением блока 9 микропрограммного управления приема-передачи линейный узел 1 переходит в режим зах захватив которую,

вата сети 22, формирует условие захвата на вход мультиплексора 12 условий обработки и переходит в режим ожидания записи

байта пакета данных в выходной регистр 6. Байт информац-ш считывается с блока 19, записьшается в регистр 7 передачи, после чего формируется условие передачи ьа входе мультиплексора 8 условий приема-передачи, по которому байт переписывается в выходной регистр 6 и передается в сеть 22, во время чего второй байт считывается с буфера приема-передачи и заносится в регистр 7 передачи и т.д. При передаче байта информации блоком 9 микропрограммного управления приема-передачи микропрограммно отсчитывается пересдача каждого бита и, выдвинув последний бит из выходного регистра 6, в него переписывается байт информации из регистра 7 передачи, при этом контролируется признак конца пакета на входе мультиплексора 8 условий приема-передачи, который выставляет блок 13 микропрограммного управления обработки при записи в регистр 7 передачи последнего байта пакета данных, при его наличии последний байт передается в сеть 22 и устройство переходит в режим ожидания квитанции.

При передаче пакета данных по запросу сетевой контроллер принимает тре/гий байт (фиг.2) с указанием адреса сетевого контроллера, запросившего пакет данных, адрес запоминается в РОНе процессора 7, и сетевой контроллер переходит в режим передачи пакета данных аналогично передаче по указанному адресу, с той разницей, что третьим байтом передается адрес сетевого контроллера, за- прсившего пакет данных, хранящийся в регистре общего назначения процессора 17, с тем, чтобы не нарушить формат пакета данных, приведенного на фиг.2.

В паузах между сеансами связи, кода сетевой контроллер не участвует в обмене информацией, проводится диагностика всех узлов сетевого контроллера и глобальная диагностика с участием абонента 20.

Формула изобретения

Сетевой контроллер, содержащий линейный узел, преобразователь кода, входной регистр, узел проверки информации по паритету, выходной регистр, мультиплексор условий приема

0

5

0

5

0

5

0

5

передачи, бтюк микропрограммного управления приема-передачи, блок постоянной памяти микропрограмм приема-передачи, конвейерный регистр приема-передачи, тактовый генератор, информационный вход-выход линейного узла является одноименным входом-выходом контроллера для соединения с локальной управляющей вычислительной сетью, первый информационный выход линейного узла соединен с первым информационным входом преобразователя кода, второй информационный выход соединен с входом узла проверки информации по паритету, выход условия приема линейного узла соединен с соответствующим информационным входом мультиплексора условий приема-передачи, информационный вход линейного узла соединен с первым информационным выходом преобразователя кода, управляющий вход линейного узла соединен с соответствующим выходом конвейерного регистра приема-передачи, второй информационный выход преобразователя кода соединен с информационным входом входного регистра,второй информационный вход преобразователя кода соединен с выходом выходного регистра, выход состояния преобразователя кода соединен с соответствующим информационным входом мультиплексора условий приема-передачи, управляющий вход преобразователя кода соединен с соответствующим выходом конвейерного регистра приема- передачи, управляющие входы входного и выходного регистров соединены с соответствующими выходами конвейерного регистра приема-передачи, контрольный выход узла проверки информации по паритету соединен с соответствующим информационным входом мультиплексора условий приема-передачи, выход которого соединен с входом условий блока микропрограммного управления приема-передачи, выходы которого соединены с адресными входами блока постоянной памяти микропрограмм приема-передачи, выходы которого соединены с информационными входами конвейерного регистра, соответствующие выходы которого соединены с соответствующими входами условий блока микропрограммного управления и мультиплексора условий приема-передачи, о т- личающийся тем, что, с целью повышения скорости передачи информации сети и расширения протокольных функций контроллера, в него введены регистр приема, регистр передачи, мультиплексор условий обработки, блок микропрограммного управления обработки, блок постоянной памяти микропрограмм обработки, конвейерный регистр обработки, блок постоянной памяти уставок, процессор, регистр адреса, блок буферной памяти приема- передачи, выход входного регистра соединен с информационным входом регистра приема, выход которого соединен с входом данных процессора, управляющий вход регистра приема соединен с соответствующим выходом конвейерного регистра приема-передачи, информационный вход выходного регистра соединен с выходом регистра передачи, информационный вход которого соединен с выходом данных блока буферной памяти приема-передачи, управляющий вход регистра передачи соединен с соответствующим выходом конвейерного регистра приема-передачи, выход условия конвейерного регистра приема- передачи соединен с соответствующим информационным входом мультиплексора условий обработки, выход которого соединен с входом условия блока микропрограммного управления обработки, выходы которого соединены с адресными входами блока постоянной памяти микропрограмм обработки, выход которого соединен с информационным входом конвейерного регистра обработки, соответствующие выходы конвейерного регистра обработки соединены с входами

Фиг. 2

условий блока микропрограммного управления обработки, информационными входами мультиплексора условий обработки, мультиплексора условий приема- передачи, управляющими входами процессора, блока буферной памяти приема-передачи, блока постоянной памяти уставок, соответствующие выходы конвейерного регистра обработки и информационные входы мультиплексора условий обработки являются выходами и входами синхронизации контроллера, выходы блока постоянной памяти уставок соединены с входами данных процессора, выход условий процессора соединен с соответствующим информационным входом мультиплексора условий обработки, вход-выход данных адреса процессора соединен с информационным входом регистра адреса, входом данных блока буферной памяти приема-передачи, информационным входом регистра передачи, входами данных адреса контроллера для подключения абонента, тактирующие выходы тактового генератора соединены с тактовыми входами линейного узла, преобразователя кода, входного регистра, регистра приема,

0 узла проверки информации по паритету, выходного регистра, регистра передачи, мультиплексора условий приема-передачи, блока микропрограммного управления приема-передачи, муль5 типлексора условий обработки, блока

микропрограммного управления обра- ботки, процессора, регистра адреса и блока буферной памяти приема-передачи.

0

5

Риг 5

Фиг. 4

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1990-05-15—Публикация

1988-02-29—Подача