М и п

М m М

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| Устройство для сопряжения процессоров в мультипроцессорной системе | 1984 |

|

SU1188747A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1442998A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

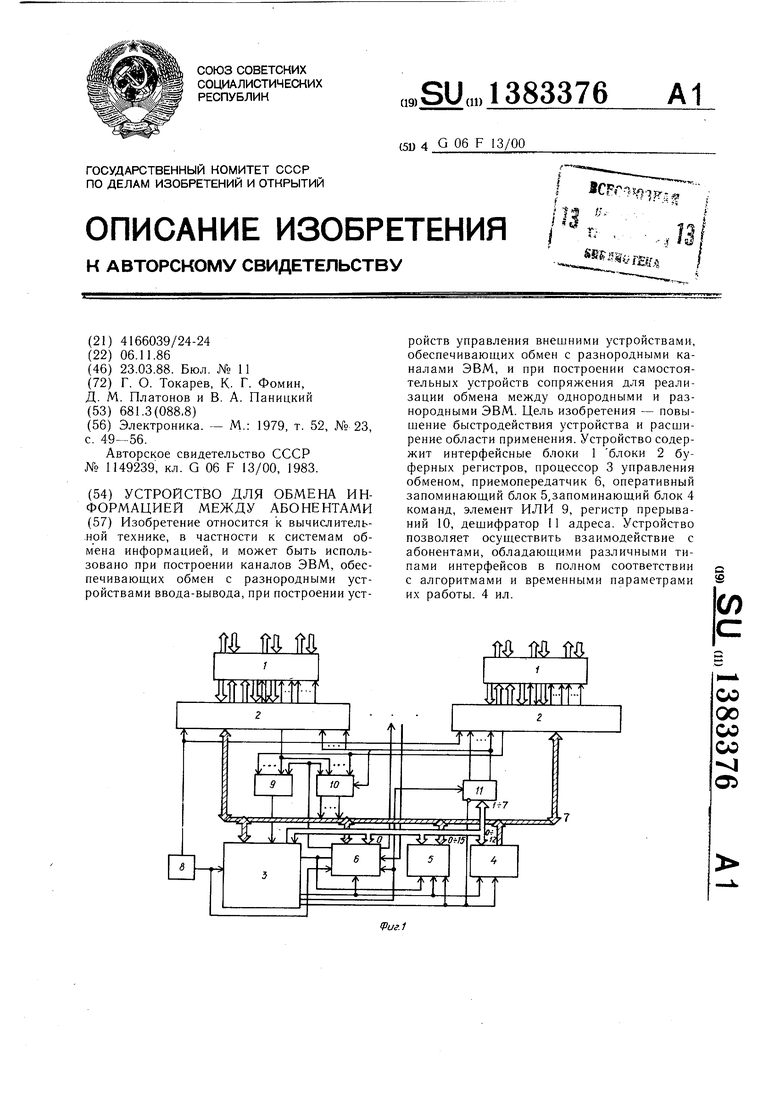

Изобретение относится к вычислитель- ,ной технике, в частности к системам обмена информацией, и может быть использовано при построении каналов ЭВМ, обеспечивающих обмен с разнородными устройствами ввода-вывода, при построении устройств управления внешними устройствами, обеспечивающих обмен с разнородными каналами ЭВМ, и при построении самостоятельных устройств сопряжения для реализации обмена между однородными и разнородными ЭВМ. Цель изобретения - повы- щение быстродействия устройства и расширение области применения. Устройство содержит интерфейсные блоки 1 блоки 2 буферных регистров, процессор 3 управления обменом, приемопередатчик 6, оперативный запоминающий блок 5,запоминающий блок 4 команд, элемент ИЛИ 9, регистр прерываний 10, дешифратор 11 адреса. Устройство позволяет осуществить взаимодействие с абонентами, обладающими различными типами интерфейсов в полном соответствии с алгоритмами и временными параметрами их работы. 4 ил. (О (Л

со 00 со со

С5

Изобретение относится к вычислительной технике, в частности к системам обмена информацией, и может быть использовано при построении каналов ЭВМ, обеспечивающих обмен с разнородными устройствами ввода-вывода, при построении устройств управления внешними устройствами (устройствами ввода-вывода), обеспечивающих обмен с разнородными каналами ЭВМ, и при построении самостоятельных устройств сопряжения для обеспечения обмена между разнородными ЭВМ и (или) разнородными устройствами ввода-вывода.

Цель изобретения - повышение быстродействия устройства и расширение области применения за счет универсальной реали- зации практически всех типов используемых машинных интерфейсов.

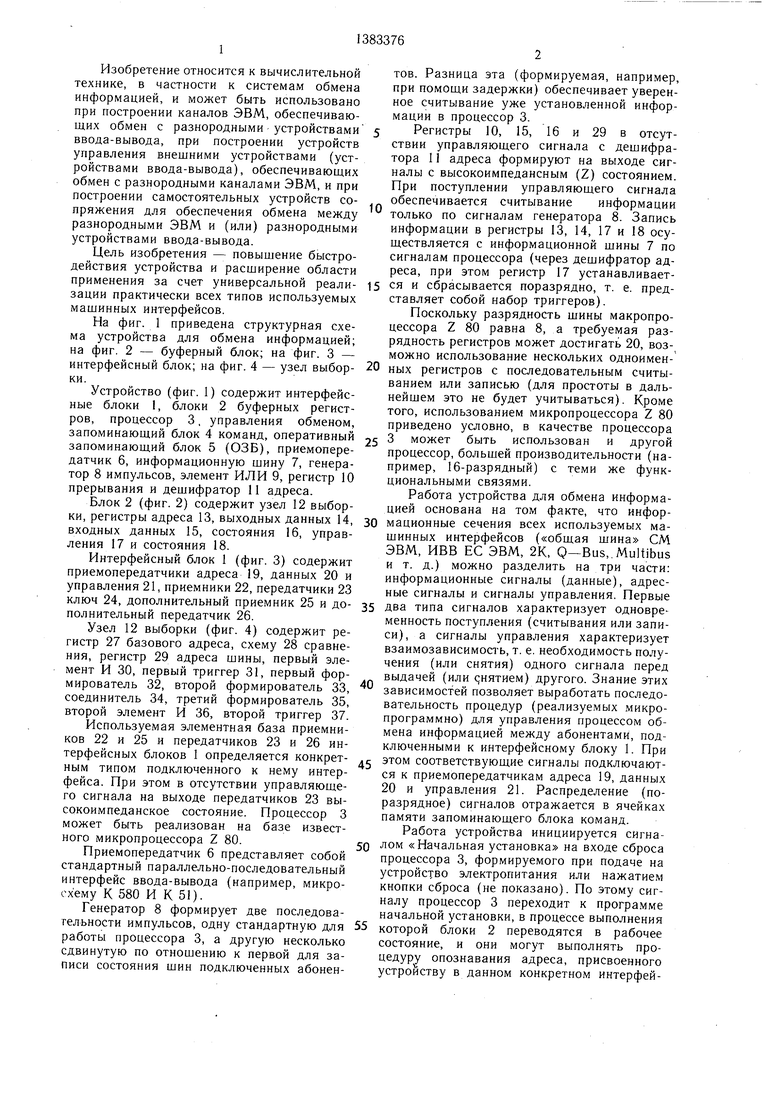

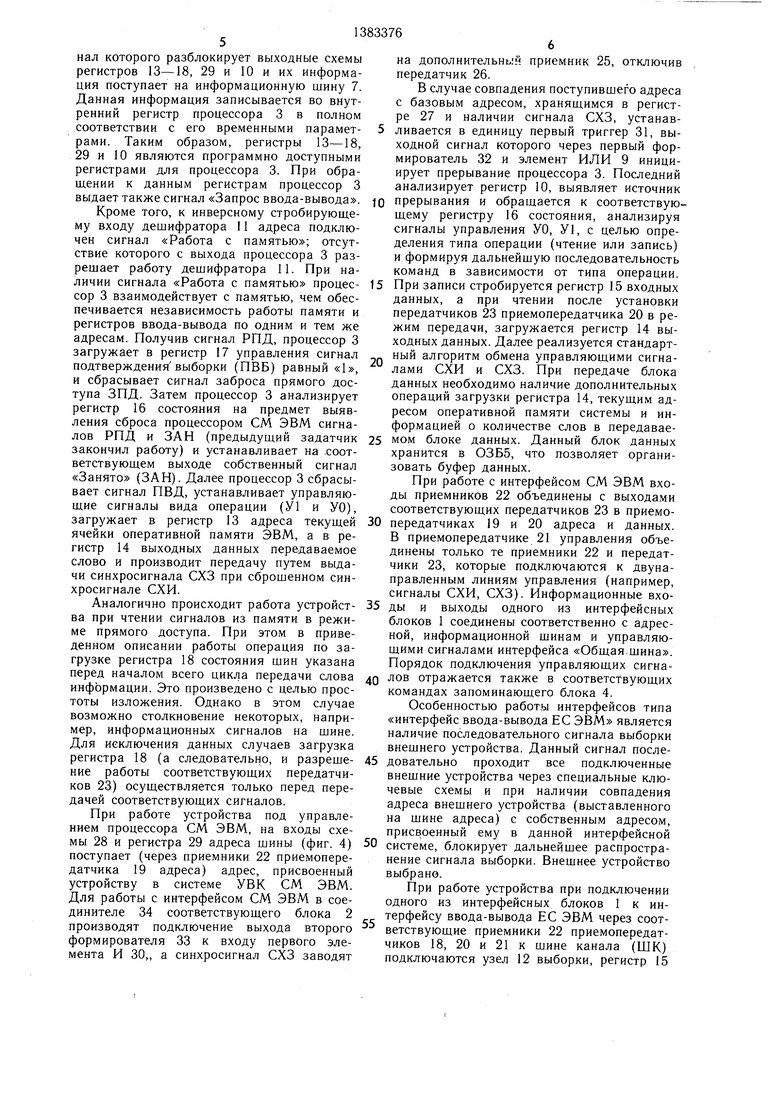

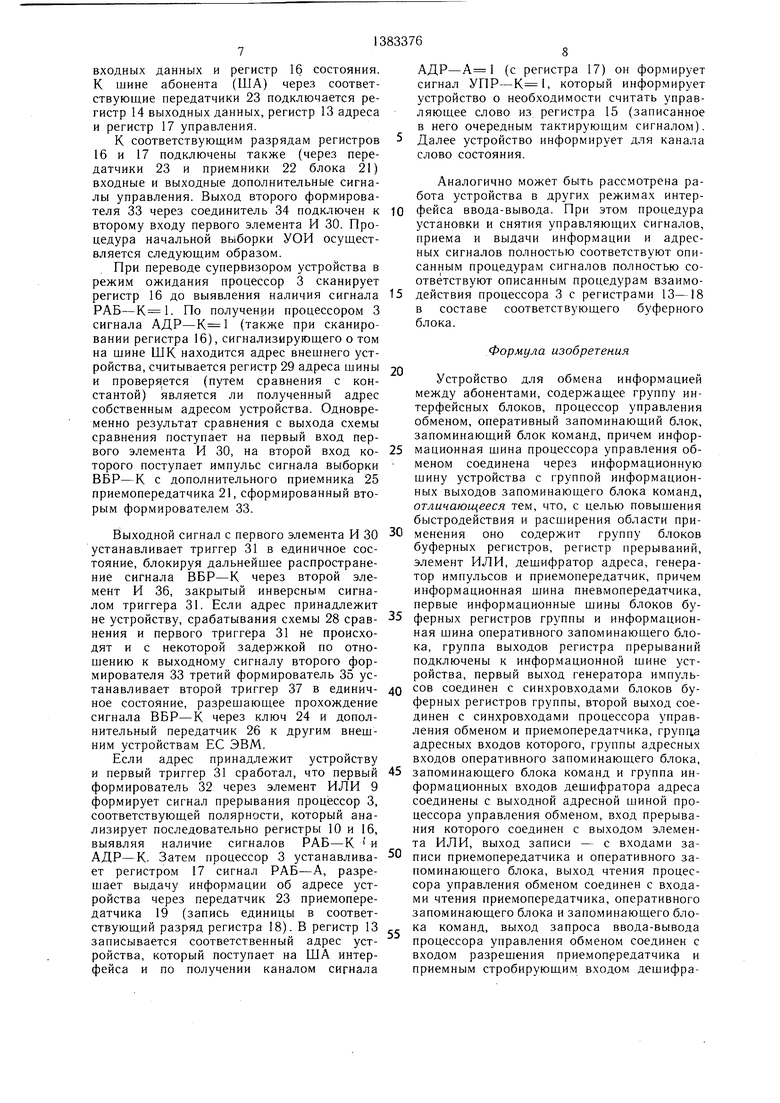

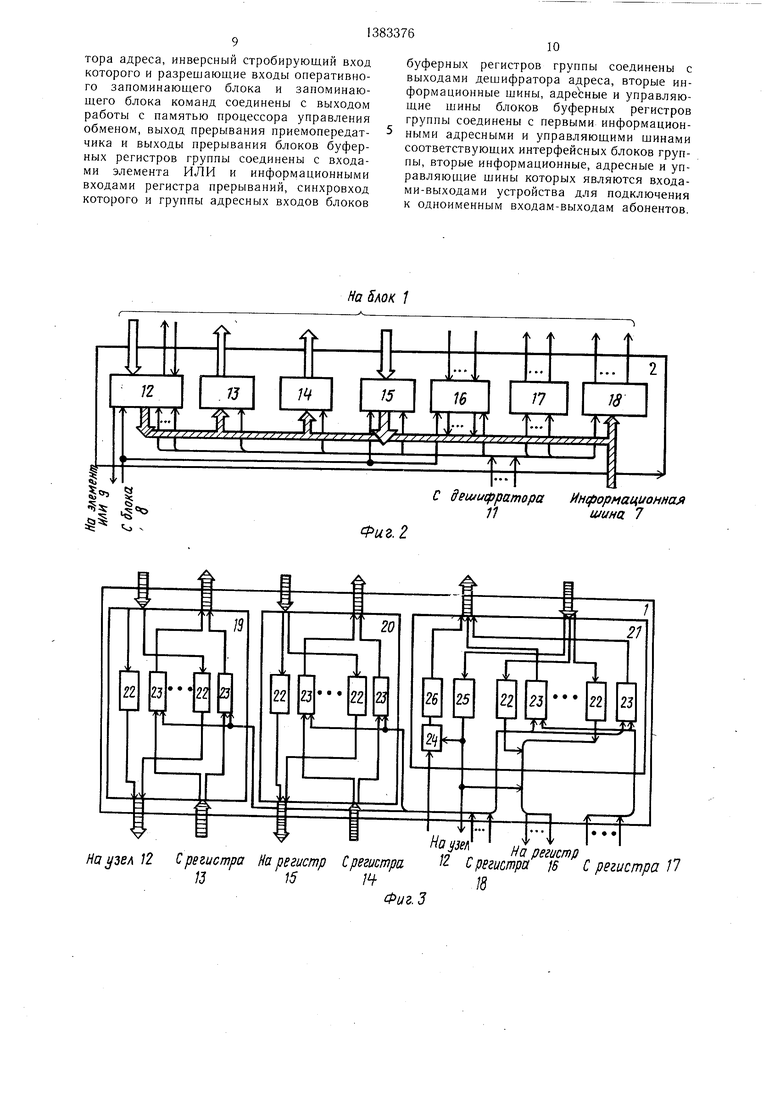

На фиг. 1 приведена структурная схема устройства для обмена информацией; на фиг. 2 - буферный блок; на фиг. 3 - интерфейсный блок; на фиг. 4 - узел выбор- ки.

Устройство (фиг. 1) содержит интерфейсные блоки 1, блоки 2 буферных регистров, процессор 3, управления обменом, запоминающий блок 4 команд, оперативный запоминающий блок 5 (ОЗБ), приемопередатчик 6, информационную шину 7, генератор 8 импульсов, элемент ИЛИ 9, регистр 10 прерывания и дешифратор 11 адреса.

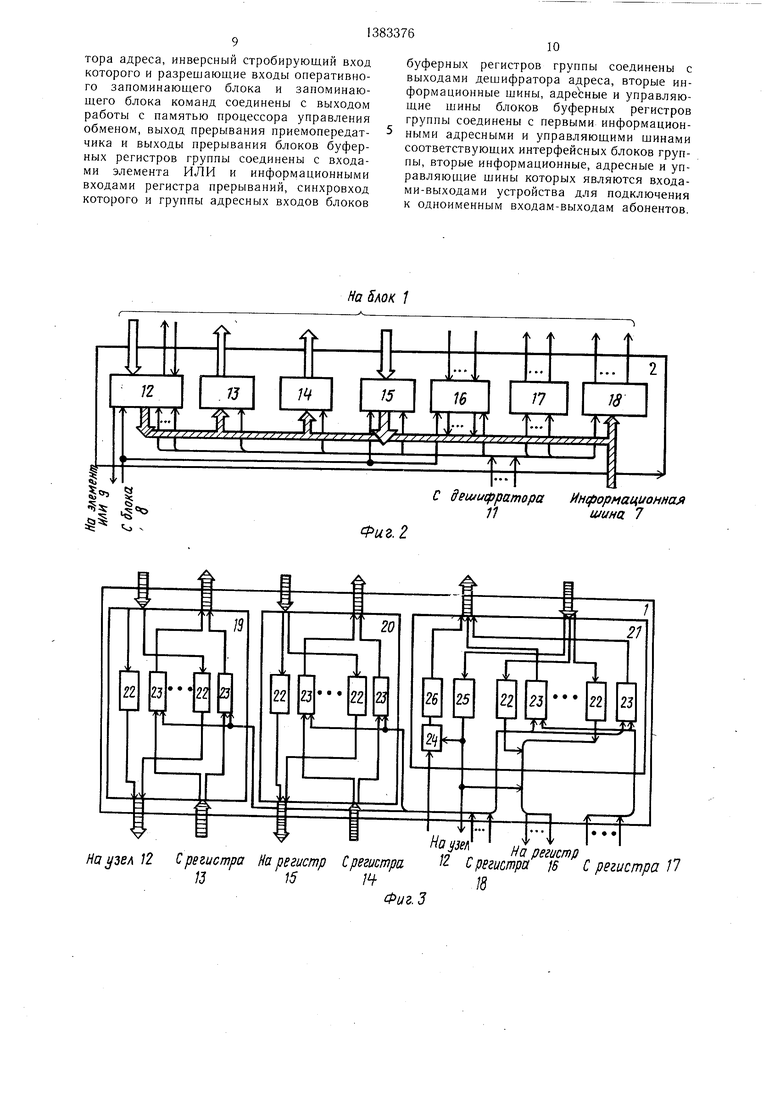

Блок 2 (фиг. 2) содержит узел 12 выборки, регистры адреса 13, выходных данных 14, входных данных 15, состояния 16, управления 17 и состояния 18.

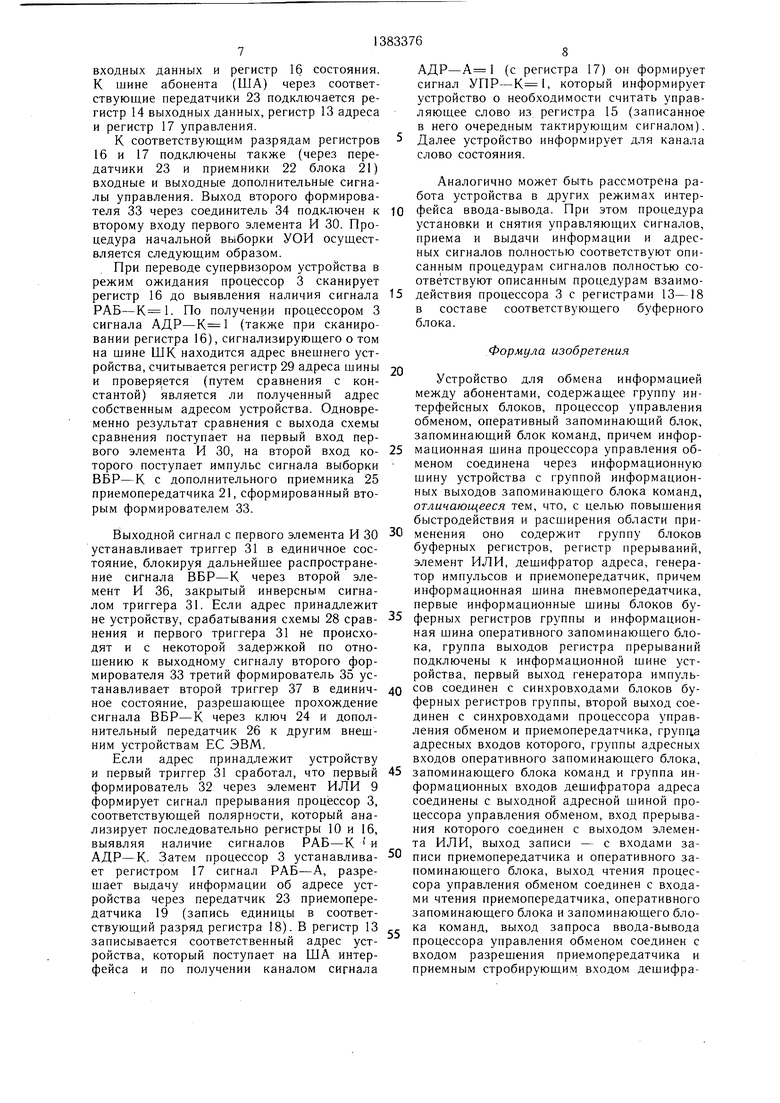

Интерфейсный блок 1 (фиг. 3) содержит приемопередатчики адреса 19, данных 20 и управления 21, приемники 22, передатчики 23 ключ 24, дополнительный приемник 25 и до- полнительный передатчик 26.

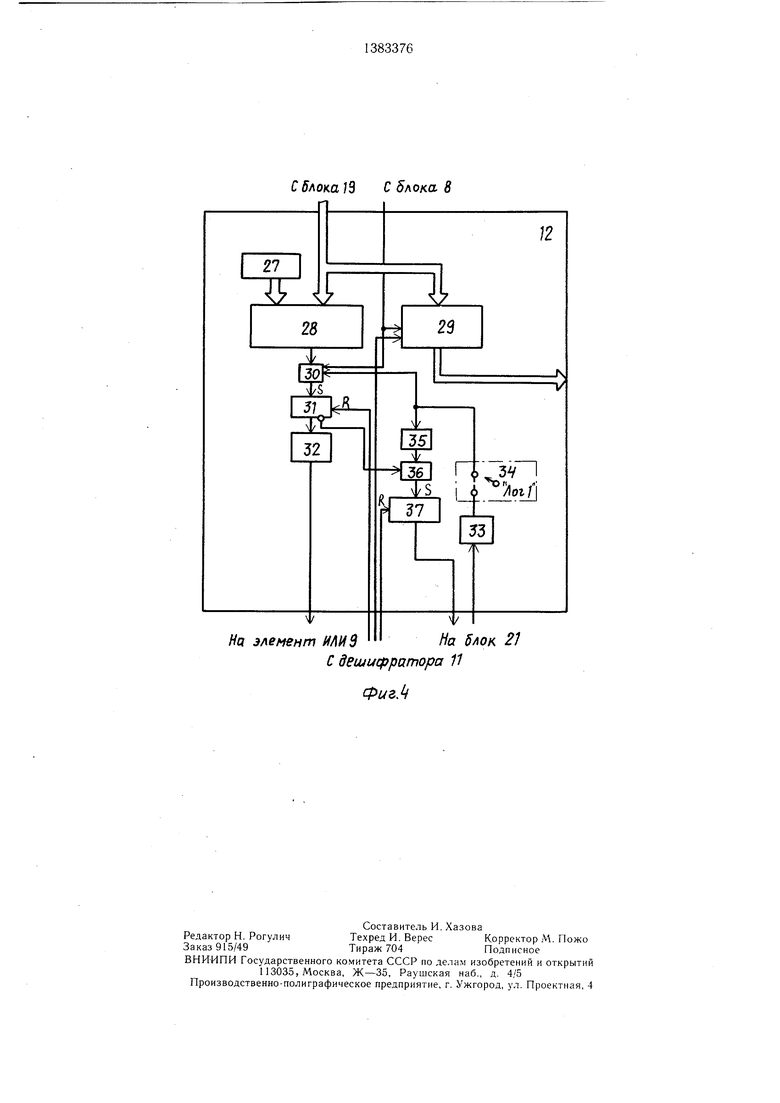

Узел 12 выборки (фиг. 4) содержит регистр 27 базового адреса, схему 28 сравнения, регистр 29 адреса шины, первый элемент И 30, первый триггер 31, первый формирователь 32, второй формирователь 33, соединитель 34, третий формирователь 35, второй элемент И 36, второй триггер 37.

Используемая элементная база приемников 22 и 25 и передатчиков 23 и 26 интерфейсных блоков 1 определяется конкрет- ным типом подключенного к нему интерфейса. При этом в отсутствии управляющего сигнала на выходе передатчиков 23 вы- сокоимпеданское состояние. Процессор 3 может быть реализован на базе известного микропроцессора Z 80.

Приемопередатчик 6 представляет собой стандартный параллельно-последовательный интерфейс ввода-вывода (например, микросхему К 580 И К 51).

Генератор 8 формирует две последовательности импульсов, одну стандартную для работы процессора 3, а другую несколько сдвинутую по отношению к первой для записи состояния шин подключенных абонен0

0

5

о

тов. Разница эта (формируемая, например, при помощи задержки) обеспечивает уверенное считывание уже установленной информации в процессор 3.

Регистры 10, 15, 16 и 29 в отсутствии управляющего сигнала с дещифра- тора 11 адреса формируют на выходе сигналы с высокоимпедансным (Z) состоянием. При поступлении управляющего сигнала обеспечивается считывание информации только по сигналам генератора 8. Запись информации в регистры 13, 14, 17 и 18 осуществляется с информационной шины 7 по сигналам процессора (через дешифратор адреса, при этом регистр 17 устанавливается и сбрасывается поразрядно, т. е. представляет собой набор триггеров).

Поскольку разрядность шины макропроцессора Z 80 равна 8, а требуемая разрядность регистров может достигать 20, возможно использование нескольких одноименных регистров с последовательным считыванием или записью (для простоты в дальнейшем это не будет учитываться). Кроме того, использованием микропроцессора Z 80 приведено условно, в качестве процессора 3 может быть использован и другой процессор, большей производительности (например, 16-разрядный) с теми же функциональными связями.

Работа устройства для обмена информацией основана на том факте, что информационные сечения всех используемых машинных интерфейсов («общая шина СМ ЭВМ, ИВВ ЕС ЭВМ, 2К, Q-Bus,.Multibus и т. д.) можно разделить на три части: информационные сигналы (данные), адресные сигналы и сигналы управления. Первые два типа сигналов характеризует одновременность поступления (считывания или записи), а сигналы управления характеризует взаимозависимость, т. е. необходимость получения (или снятия) одного сигнала перед выдачей (или нятием) другого. Знание этих зависимостей позволяет выработать последовательность процедур (реализуемых микропрограммно) для управления процессом обмена информацией между абонентами, подключенными к интерфейсному блоку 1. При этом соответствующие сигналы подключаются к приемопередатчикам адреса 19, данных 20 и управления 21. Распределение (поразрядное) сигналов отражается в ячейках памяти запоминающего блока команд.

Работа устройства инициируется сигналом «Начальная установка на входе сброса процессора 3, формируемого при подаче на устройство электропитания или нажатием кнопки сброса (не показано). По этому сигналу процессор 3 переходит к программе начальной установки, в процессе выполнения которой блоки 2 переводятся в рабочее состояние, и они могут выполнять процедуру опознавания адреса, присвоенного устройству в данном конкретном интерфейсе, а приемопередатчик 6 устанавливается в режим приема информации от абонента.

Дальнейшая работа устройства определяется управляющей программой-супервизором, хранящейся в. запоминабщем блоке 4 и требующей для своего функционирования некоторого объема ОЗБ5.

При опознавании адреса устройства одним из блоков 2 формируется сигнал прерывания процессора 3, отработка которого осуществляется супервизором. При поступлении информационного слова на вход приемопередатчика 6 последний формирует на своем выходе также сигнал прерывания.

Рассмотрим работу наиболее характерных интерфейсов типа «Общая щина

Обработка прерывания осуществляется в 15 СМ ЭВМ и интерфейс ввода-вывода ЕС ЭВМ, каждом случае стандартно. При поступле-работающих в двух режимах: в первом рении импульса прерывания с элемента ИЛИ 9жиме осуществляется передача под управданный сигнал записывается также в ре-лением устройства в режиме прямого достугистр 10, а процессор после выполненияпа, во втором режиме - передача слова

соответствующего цикла обращается в стан-информации под управлением процессора

дартную ячейку запоминающего блока 4, 20 СМ ЭВМ.

Устройство в первом режиме работает

следующим образом.

При передаче супервизором команды на

передачу слова информации в намять СМ

тывания дещифратора 11 адреса и анали- 25 ЭВМ в режиме прямого доступа устройство зирует его. При соответствии каждого раз-обеспечивает захват щины, для чего загруряда регистра 10 определенному блоку 2 и первого разряда приемопередатчику 6 процессор 3 однозначно определяет источник прерывания. Супервизор осуществляет обгде хранится начальная команда подпрограммы обработки прерывания. Процессор 3 считывает содержимое регистра 10 путем выдачи соответствующего адреса и срабажает в регистр 16 управления единичный сигнал запроса (ЗПД 1).

Регистр 16 представляет собой набор триггеров, установочные и сбросовые входы

щее управление работой устройства путем ЗО которого подключены к соответствующим выходам дещифратора 11 адреса. Аналогично разрешается работа соответствующих передатчиков 23 приемопередатчика 21 управления, на управляющие входы которых поступают разрещающие сигналы с регистинициирования выполнения процедур, реализованных в виде программ процессора по установлению соединения с абонентами, передачи информации между абонентами и устройством, разъединению с абонентом.

ходам дещифратора 11 адреса. Аналогично разрешается работа соответствующих передатчиков 23 приемопередатчика 21 управления, на управляющие входы которых поступают разрещающие сигналы с регистУказанные процедуры для каждого кон- 35 Р 18 состояния щин. Данные сигналы кретного типа интерфейса регламентируются устанавливаются только на тех разрядах стандартами.регистра 18, которые обеспечивают разреОбщая стратегия, включающая в себя щение выдачи информации с регистра 14 такие элементы, как выбор направлениявыходных данных, регистра 13 адреса и сигпередачи, объем передаваемых блоков ин- налов управления, участвующих в данном реформации, приоритетность абонентов и т. д., J жиме. Все остальные передатчики 23 закры- реализуемая супервизором, определяется конкретным применением устройства в системах сбора и обработки информации. Блоки 2 предназначены для реализации интерфейты, и на их выходах устанавливается высокоимпеданское состояние, не препятствующее нормальному обмену сигналами на соответствующих двунаправленных тинах сов с передачей данных в параллельном коде, .г интерфейса. Приемопередатчик 6 предназначен для реализации интерфейсов с последовательной передачей данных. Принципиально приемопередатчиков 6 может быть несколько (аналогично как и блоков 2), при этом соответствующие управляющие сигналы являют- о пает через соответствующий приемник 22 ся общими для всех приемопередатчиков 6,приемопередатчика 2 на вход регистра 16

за исключением сигнала адреса, который может быть получен с отдельного выхода дещифратора 11, и отдельного выхода прерывания процессора, заведенного на соотПолучив сигнал ЗПД, процессор СМ ЭВМ производит арбитраж поступивщих запросов и при положительном ответе выдает сигнал разрешения (РПД). Данный сигнал постусостояния. Процессор 3 после выдачи ЗПД постоянно анализирует регистр 16 состояния до получения сигнала РПД. Для этого процессор 3 (как и при любом другом обветствующие входы элементов ИЛИ 9 и ре- 55 ращении к регистрам 13-18, 10 и 29 форгистра 10.

В соответствующих регистрах 27 базового адреса записывается (например, с помощью

мирует на щине адреса код адреса соответствующего регистра, который дешифрируется дещифратором 11 адреса, выходной сигкнопок или другими наборными элементами) код, присвоенный устройству в данном типе интерфейсной системы абонента.

Запись информации в регистры 29, 15 г и 16 осуществляется но сигналам генератора 8. Это позволяет постоянно отслеживать состояние щин адреса, данны.х и управления соответствующего интерфейса и путе.м считывания и дальнейщего анализа информации в установленные моменты времени 0 производить либо прием, либо выдачу сигналов с установленной временной последовательностью.

Рассмотрим работу наиболее характерных интерфейсов типа «Общая щина

5 СМ ЭВМ и интерфейс ввода-вывода ЕС ЭВМ, работающих в двух режимах: в первом ре ЭВМ в режиме прямого доступа устройство обеспечивает захват щины, для чего загружает в регистр 16 управления единичный сигнал запроса (ЗПД 1).

Регистр 16 представляет собой набор триггеров, установочные и сбросовые входы

которого подключены к соответствующим выходам дещифратора 11 адреса. Аналогично разрешается работа соответствующих передатчиков 23 приемопередатчика 21 управления, на управляющие входы которых поступают разрещающие сигналы с регистР 18 состояния щин. Данные сигналы устанавливаются только на тех разрядах регистра 18, которые обеспечивают разреты, и на их выходах устанавливается высокоимпеданское состояние, не препятствующее нормальному обмену сигналами на соответствующих двунаправленных тинах интерфейса. пает через соответствующий приемник 22 приемопередатчика 2 на вход регистра 16

Получив сигнал ЗПД, процессор СМ ЭВМ производит арбитраж поступивщих запросов и при положительном ответе выдает сигнал разрешения (РПД). Данный сигнал постуты, и на их выходах устанавливается высокоимпеданское состояние, не препятствующее нормальному обмену сигналами на соответствующих двунаправленных тинах интерфейса. пает через соответствующий приемник 22 приемопередатчика 2 на вход регистра 16

состояния. Процессор 3 после выдачи ЗПД постоянно анализирует регистр 16 состояния до получения сигнала РПД. Для этого процессор 3 (как и при любом другом об ращении к регистрам 13-18, 10 и 29 формирует на щине адреса код адреса соответствующего регистра, который дешифрируется дещифратором 11 адреса, выходной сиг1383376

56

нал которого разблокирует выходные схемына дополнительный приемник 25, отключив

регистров 13-18, 29 и 10 и их информа-передатчик 26.

ция поступает на информационную шину 7.В случае совпадения поступившего адреса

Данная информация записывается во внут-с базовым адресом, хранящимся в регистренний регистр процессора 3 в полномре 27 и наличии сигнала СХЗ, устанавсоответствии с его временными парамет-5 ливается в единицу первый триггер 31, вырами. Таким образом, регистры 13-18,ходней сигнал которого через первый фор29 и 10 являются программно доступнымимирователь 32 и элемент ИЛИ 9 иницирегистрами для процессора 3. При обра-ирует прерывание процессора 3. Последний

щении к данным регистрам процессор 3анализирует регистр 10, выявляет источник

выдает также сигнал «Запрос ввода-вывода,ю прерывания и обращается к соответствуюКроме того, к инверсному стробирующе-щему регистру 16 состояния, анализируя му входу дешифратора 11 адреса подклю-сигналы управления УО, У1, с целью опре- чен сигнал «Работа с памятью ; отсут-деления типа операции (чтение или запись) ствие которого с выхода процессора 3 раз-и формируя дальнейшую последовательность решает работу дещифратора 11. При на-команд в зависимости от типа операции, личии сигнала «Работа с памятью процес-15 При записи стробируется регистр 15 входных сор 3 взаимодействует с памятью, чем обес-данных, а при чтении после установки печивается независимость работы памяти ипередатчиков 23 приемопередатчика 20 в ре- регистров ввода-вывода по одним и тем жежим передачи, загружается регистр 14 вы- адресам. Получив сигнал РПД, процессор 3ходных данных. Далее реализуется стандарт- загружает в регистр 17 управления сигналный алгоритм обмена управляющими сигна- подтверждения выборки (ПВБ) равный «1,лами СХИ и СХЗ. При передаче блока и сбрасывает сигнал заброса прямого дос-данных необходимо наличие дополнительных тупа ЗПД. Затем процессор 3 анализируетопераций загрузки регистра 14, текущим ад- регистр 16 состояния на предмет выяв-ресом оперативной памяти системы и ин- ления сброса процессором СМ ЭВМ сигна-формацией о количестве слов в передавае- лов РПД и ЗАН (предыдущий задатчик25 мом блоке данных. Данный блок данных закончил работу) и устанавливает на .соот-хранится в ОЗБ5, что позволяет органи- ветствующем выходе собственный сигналзовать буфер данных.

«Занято (ЗАН). Далее процессор 3 сбрасы-При работе с интерфейсом СМ ЭВМ вховает сигнал ПВД, устанавливает управляю-ды приемников 22 объединены с выходами

щие сигналы вида операции (У1 и УО),соответствующих передатчиков 23 в приемозагружает в регистр 13 адреса текущей30 передатчиках 19 и 20 адреса и данных,

ячейки оперативной памяти ЭВМ, а в ре-В приемопередатчике 21 управления объегистр 14 выходных данных передаваемоединены только те приемники 22 и передатслово и производит передачу путем выда-чики 23, которые подключаются к двуначи синхросигнала СХЗ при сброшенном син-правленным линиям управления (например,

хросигнале СХИ.сигналы СХИ, СХЗ). Информационные вхоАналогично происходит работа устройст-35 ды и выходы одного из интерфейсных

ва при чтении сигналов из памяти в режи-блоков 1 соединены соответственно с адресме прямого доступа. При этом в призе-ной, информационной шинам и управляюденном описании работы операция по за-щими сигналами интерфейса «Общая-шина.

грузке регистра 18 состояния шин указанаПорядок подключения управляющих сигнаперед началом всего цикла передачи слова Q лов отражается также в соответствующих

информации. Это произведено с целью прос-командах запоминающего блока 4.

тоты изложения. Однако в этом случаеОсобенностью работы интерфейсов типа

возможно столкновение некоторых, напри-«интерфейс ввода-вывода ЕС ЭВМ является

мер, информационных сигналов на шине.наличие последовательного сигнала выборки

Для исключения данных случаев загрузкавнешнего устройства. Данный сигнал послерегистра 18 (а следовательно, и разреше-45 довательно проходит все подключенные

ние работы соответствующих передатчи-внещние устройства через специальные клюков 23) осуществляется только перед пере-чевые схемы и при наличии совпадения

дачей соответствующих сигналов.адреса внещнего устройства (выставленного

При работе устройства под управле-на щине адреса) с собственным адресом,

нием процессора СМ ЭВМ, на входы схе-присвоенный ему в данной интерфейсной

мы 28 и регистра 29 адреса шины (фиг. 4)50 системе, блокирует дальнейшее распрострапоступает (через приемники 22 приемопере-нение сигнала выборки. Внешнее устройство

датчика 19 адреса) адрес, присвоенныйвыбрано.

устройству в системе УВК СМ ЭВМ.При работе устройства при подключении

Для работы с интерфейсом СМ ЭВМ в сое-одного из интерфейсных блоков 1 к индинителе 34 соответствующего блока 2терфейсу ввода-вывода ЕС ЭВМ через соотпроизводят подключение выхода второго ветствующие приемники 22 приемопередатформирователя 33 к входу первого эле-чиков 18, 20 и 21 к шине канала (ШК)

мента И 30,, а синхросигнал СХЗ заводятподключаются узел 12 выборки, регистр 15

входных данных и регистр 16 состояния. К шине абонента (ША) через соответствующие передатчики 23 подключается регистр 14 выходных данных, регистр 13 адреса и регистр 17 управления.

К соответствующим разрядам регистров 16 и 17 подключены также (через передатчики 23 и приемники 22 блока 21) входные и выходные дополнительные сигналы управления. Выход второго формирователя 33 через соединитель 34 подключен к второму входу первого элемента И 30. Процедура начальной выборки УОИ осуществляется следующим образом.

При переводе супервизором устройства в режим ожидания процессор 3 сканирует регистр 16 до выявления наличия сигнала РАБ-К 1. По получении процессором 3 сигнала АДР-К 1 (также при сканировании регистра 16), сигнализирующего о том на щине П1К находится адрес внещнего устройства, считывается регистр 29 адреса шины и проверяется (путем сравнения с константой) является ли полученный адрес собственным адресом устройства. Одновременно результат сравнения с выхода схемы сравнения поступает на первый вход первого элемента И 30, на второй вход ко- торого поступает импульс сигнала выборки ВБР-К с дополнительного приемника 25 приемопередатчика 21, сформированный вторым формирователем 33.

Выходной сигнал с первого элемента И 30 устанавливает триггер 31 в единичное состояние, блокируя дальнейшее распространение сигнала ВБР-К через второй элемент И 36, закрытый инверсным сигналом триггера 31. Если адрес принадлежит

30

Устройство для обмена информацией между абонентами, содержащее группу интерфейсных блоков, процессор управления обменом, оперативный запоминающий блок, запоминающий блок команд, причем информационная щина процессора управления обменом соединена через информационную щину устройства с группой информационных выходов запоминающего блока команд, отличающееся тем, что, с целью повышения быстродействия и расщирения области применения оно содержит группу блоков буферных регистров, регистр прерываний, элемент ИЛИ, дещифратор адреса, генератор импульсов и приемопередатчик, причем информационная шина пневмопередатчика, первые информационные щины блоков буне устройству, срабатывания схемы 28 срав- 5 ферных регистров группы и информацион40

нения и первого триггера 31 не происходят и с некоторой задержкой по отношению к выходному сигналу второго формирователя 33 третий формирователь 35 устанавливает второй триггер 37 в единичное состояние, разрешающее прохождение сигнала ВБР-К через ключ 24 и дополнительный передатчик 26 к другим внешним устройствам ЕС ЭВМ.

Если адрес принадлежит устройству и первый триггер 31 сработал, что первый 45 формирователь 32 через элемент ИЛИ 9 формирует сигнал прерывания процессор 3, соответствующей полярности, который анализирует последовательно регистры 10 и 16, выявляя наличие сигналов РАБ-К и АДР-К. Затем процессор 3 устанавливает регистром 17 сигнал РАБ-А, разрешает выдачу информации об адресе устройства через передатчик 23 приемопередатчика 19 (запись единицы в соответствующий разряд регистра 18). В регистр 13 записывается соответственный адрес устройства, который поступает на ША интерфейса и по получении каналом сигнала

50

55

ная шина оперативного запоминающего блока, группа выходов регистра прерываний подключены к информационной щине устройства, первый выход генератора импульсов соединен с синхровходами блоков буферных регистров группы, второй выход соединен с синхровходами процессора управления обменом и приемопередатчика, группа адресных входов которого, группы адресных входов оперативного запоминающего блока, запоминающего блока команд и группа информационных входов дешифратора адреса соединены с выходной адресной шиной процессора управления обменом, вход прерывания которого соединен с выходом элемента ИЛИ, выход записи - с входами записи приемопередатчика и оперативного запоминающего блока, выход чтения процессора управления обменом соединен с входами чтения приемопередатчика, оперативного запоминающего блока и запоминающего блока команд, выход запроса ввода-вывода процессора управления обменом соединен с входом разрешения приемопередатчика и приемным стробирующим входом дешифра5ю

5 0 5

0

АДР-А 1 (с регистра 17) он формирует сигнал УПР-К 1, который информирует устройство о необходимости считать управляющее слово из регистра 15 (записанное в него очередным тактирующим сигналом). Далее устройство информирует для канала слово состояния.

Аналогично может быть рассмотрена работа устройства в других режимах интерфейса ввода-вывода. При этом процедура установки и снятия управляющих сигналов, приема и выдачи информации и адресных сигналов полностью соответствуют описанным процедурам сигналов полностью соответствуют описанным процедурам взаимодействия процессора 3 с регистрами 13-18 в составе соответствующего буферного блока.

Формула изобретения

Устройство для обмена информацией между абонентами, содержащее группу интерфейсных блоков, процессор управления обменом, оперативный запоминающий блок, запоминающий блок команд, причем информационная щина процессора управления обменом соединена через информационную щину устройства с группой информационных выходов запоминающего блока команд, отличающееся тем, что, с целью повышения быстродействия и расщирения области применения оно содержит группу блоков буферных регистров, регистр прерываний, элемент ИЛИ, дещифратор адреса, генератор импульсов и приемопередатчик, причем информационная шина пневмопередатчика, первые информационные щины блоков бу5 ферных регистров группы и информацион0

5

0

5

ная шина оперативного запоминающего блока, группа выходов регистра прерываний подключены к информационной щине устройства, первый выход генератора импульсов соединен с синхровходами блоков буферных регистров группы, второй выход соединен с синхровходами процессора управления обменом и приемопередатчика, группа адресных входов которого, группы адресных входов оперативного запоминающего блока, запоминающего блока команд и группа информационных входов дешифратора адреса соединены с выходной адресной шиной процессора управления обменом, вход прерывания которого соединен с выходом элемента ИЛИ, выход записи - с входами записи приемопередатчика и оперативного запоминающего блока, выход чтения процессора управления обменом соединен с входами чтения приемопередатчика, оперативного запоминающего блока и запоминающего блока команд, выход запроса ввода-вывода процессора управления обменом соединен с входом разрешения приемопередатчика и приемным стробирующим входом дешифратора адреса, инверсный стробирующий вход которого и разрешающие входы оперативного запоминающего блока и запоминающего блока команд соединены с выходом работы с памятью процессора управления обменом, выход прерывания приемопередатчика и выходы прерывания блоков буферных регистров группы соединены с входами элемента ИЛИ и информационными входами регистра прерываний, синхровход которого и группы адресных входов блоков

12

:1.ЖГ...1ш.:.ЖГ,.ШЖ,.,7ЕГ,л

17Тм

1 I

И S .

ат Ни регистр На ц je л 12 С ре систра На регистр С регистра С регистра /5 С регистра 1 / ;j 514-/5

Фиг. 3

буферных регистров группы соединены с выходами дешифратора адреса, вторые информационные щины, и управляющие шины блоков буферных регистров группы соединены с первыми информационными адресными и управляющими шинами соответствующих интерфейсных блоков группы, вторые информационные, адресные и управляющие шины которых являются входами-выходами устройства для подключения к одноименным входам-выходам абонентов.

На 5мк 1

Л

15

/7

,.,7ЕГ,л

17Тм

с дешисрратора Информационная 77шина 7

Фиг. 2

С блока ;9 С блока 8

С deaiuif ротора 11 ФигМ

| Электроника | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-23—Публикация

1986-11-06—Подача