Изобретение относится к цифровой вычислительной технике, в частности, к устройствам специализированного назначения для решения уравнений, и может быть использовано в различных областях народного хозяйства в системах автоматизированного управления.

Цель изобретения - расширение области применения за счет извлечения корня квадратного из комплексных чисел при непрерывном изменении подкоренного выражения.

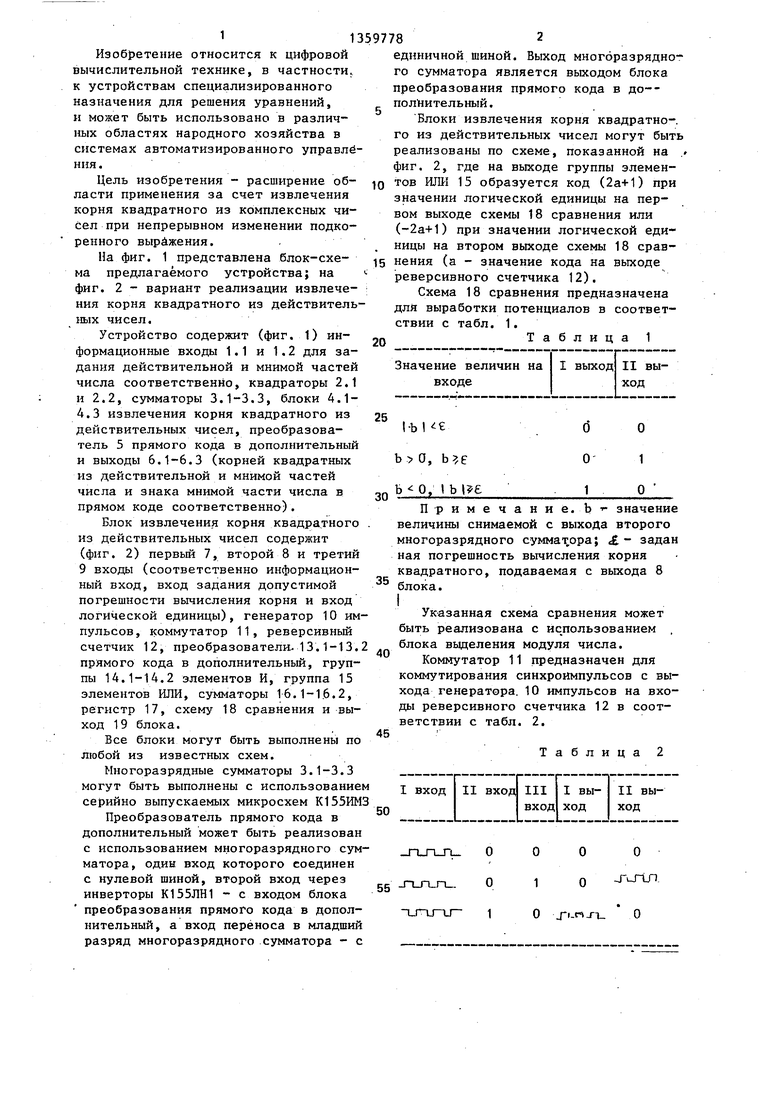

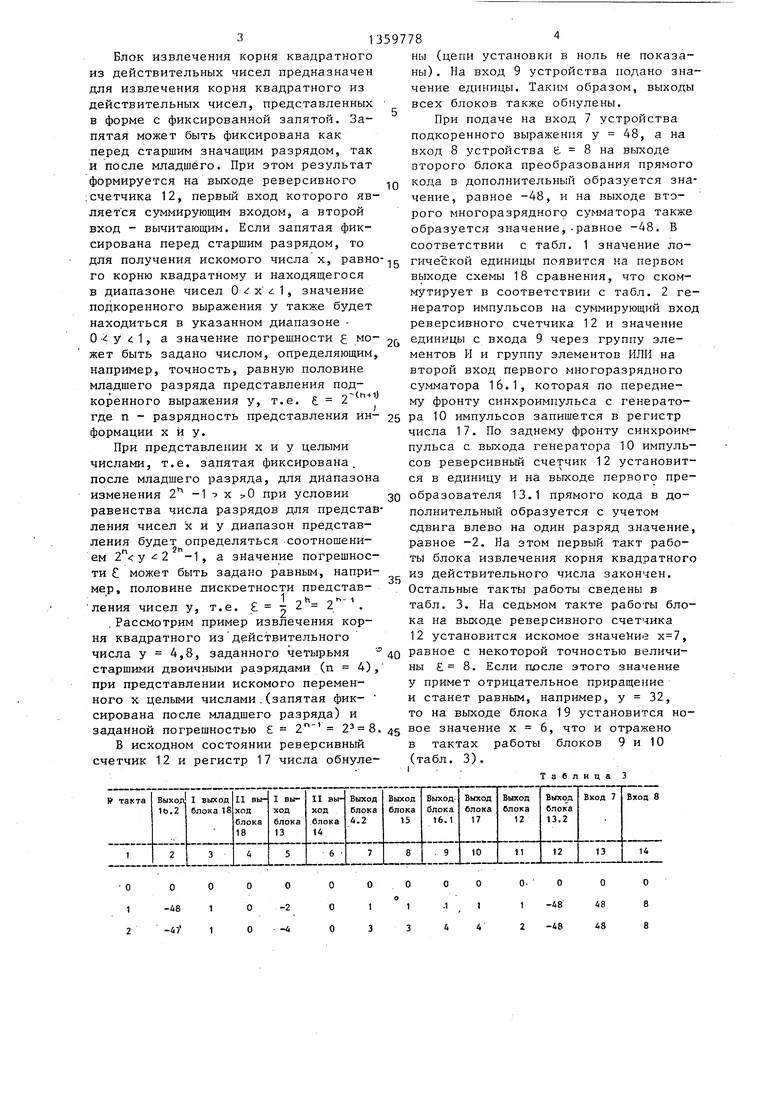

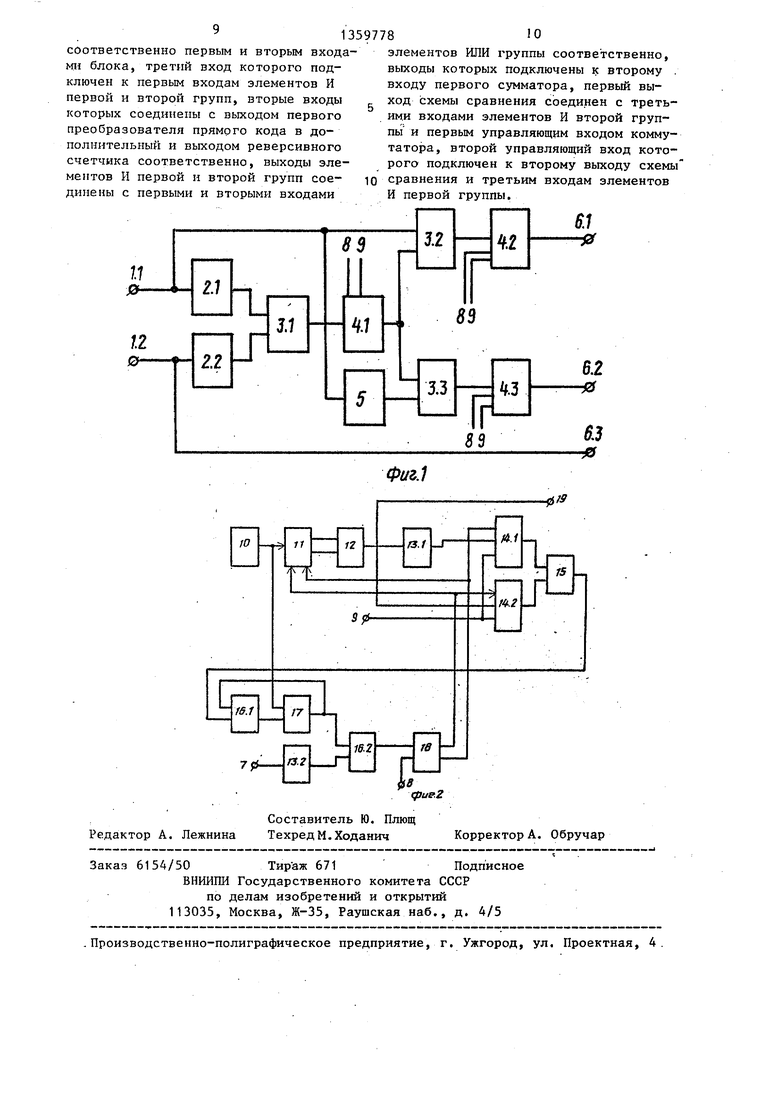

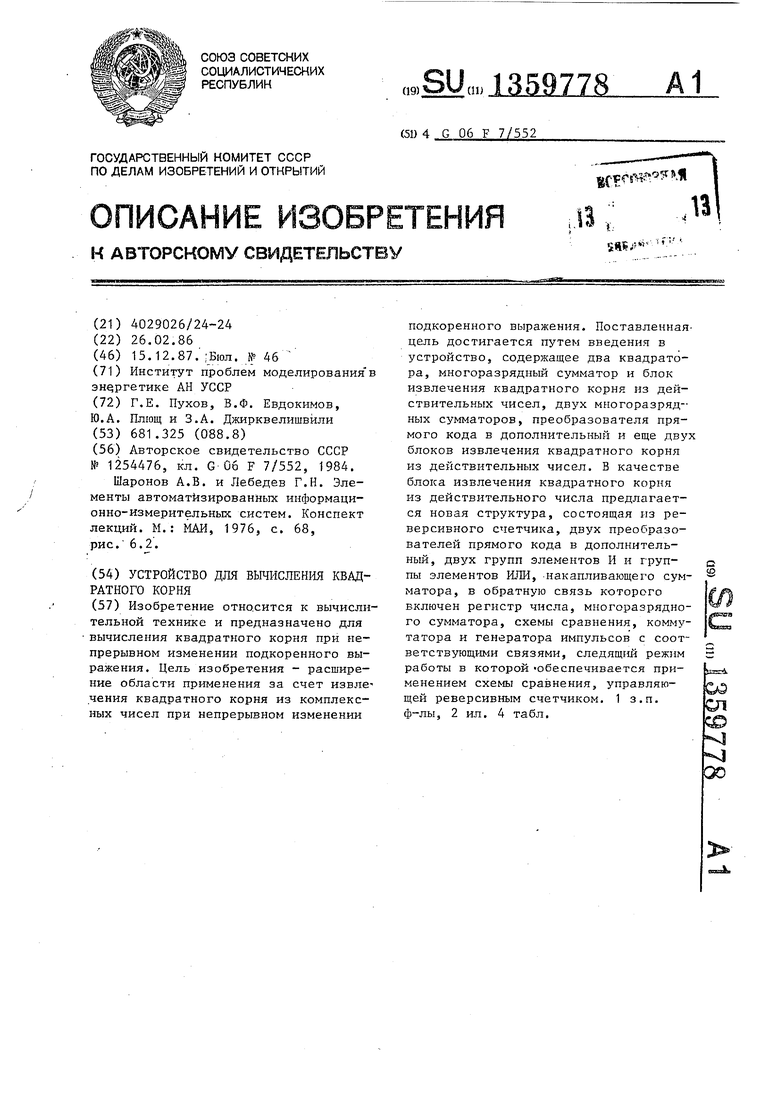

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - вариант реализации иэвлече- ния корня квадратного из действительных чисел.

Устройство содержит (фиг. 1) информационные входы 1.1 и 1.2 для задания действительной и мнимой частей числа соответственно, квадраторы 2.1 и 2.2, сумматоры 3.1-3.3, блоки 4.1- 4.3 извлечения корня квадратного из действительных чисел, преобразователь 5 прямого кода в дополнительный и выходы 6.1-6.3 (корней квадратных из действительной и мнимой частей числа и знака мнимой части числа в прямом коде соответственно).

Блок извлечения корня квадратного из действительных чисел содержит (фиг. 2) первый 7, второй 8 и третий 9 входы (соответственно информационный вход, вход задания допустимой погрешности вычисления корня и вход логической единицы), генератор 10 импульсов, коммутатор 11, реверсивный счетчик 12, преобразователя. 13.1-13. прямого кода в дополнительный, группы 14.1-14.2 элементов И, группа 15 элементов ИЛИ, сумматоры 16.1-1.6.2, регистр 17, схему 18 сравнения и выход 19 блока.

Все блоки могут быть выполнены по любой из известных схем.

Многоразрядные сумматоры 3.1-3.3 могут быть выполнены с использование серийно выпускаемых микросхем К155ИМ

Преобразователь прямого кода в дополнительный может быть реализован с использованием многоразрядного сумматора, один вход которого соединен с нулевой шиной, второй вход через инверторы К155ЛН1 - с входом блока преобразования прямого кода в дополнительный, а вход переноса в младший разряд многоразрядного сумматора - с

единичной шиной. Выход многоразрядного сумматора является выходом блока преобразования прямого кода в до-- пол1нительный.

Блоки извлечения корня квадратно-, го из действительных чисел могут быть реализованы по схеме, показанной на . фиг. 2, где на выходе группы элементов ИЛИ 15 образуется код (2а+1) при значении логической единицы на первом выходе схемы 18 сравнения или (-2а+1) при значении логической единицы на втором выходе схемы 18 сравнения (а - значение кода на выходе реверсивного счетчика 12).

Схема 18 сравнения предназначена для выработки потенциалов в соответствии с табл. 1.

Таблица 1

Примечание. значение величины снимаемой с выхода второго многоразрядного суммат ора; ,- задан ная погрешность вычисления корня квадратного, подаваемая с выхода 8 блока.

I

Указанная схема сравнения может

быть реализована с ис пользованием , блока вьщеления модуля числа.

Коммутатор 11 предназначен для коммутирования синхроимпульсов с выхода генератора. 10 импульсов на входы реверсивного счетчика 12 в соответствии с табл. 2.

Таблица 2

Блок извлечения корня квадратного из действительных чисел предназначен для извлечения корня квадратного из действительных чисел, представленных в форме с фиксированной запятой. Запятая может быть фиксирована как перед старшим значащим разрядом, так и после младшего. При этом результат формируется на выходе реверсивного ;счетчика 12, первый вход которого является суммирующим входом, а второй вход - вычитающим. Если запятая фиксирована перед старшим разрядом, то

для получения искомого числа х, равно- g гической единицы появится на первом го корню квадратному и находящегося выходе схемы 18 сравнения, что ском- в диапазоне, чисел Оv х -i 1, значение подкоренного выражения у также будет

мутирует в соответствии с табл. 2 генератор импульсов на суммирующий вход реверсивного счетчика 12 и значение О - у i 1, а значение погрещности мо- 2ь единицы с входа 9 через группу зле- жет быть задано числом, определяющим, ментов И и группу элементов ИЛИ на например, точность, равную половине второй вход первого многоразрядного младшего разряда представления под- сумматора 16.1, которая по передне- коренного выражения у, т.е. 2 му фронту синхроимпульса с генерато- где п - разрядность представления ин- 25 Ра 10 импульсов запишется в регистр формации X и у.числа 17. По заднему фронту синхроимПри представлении х и у целыми пульса с выхода генератора 10 импуль- числами, т.е. запятая фиксирована. сов реверсивный счетчик 12 установит- после младшего разряда, для диапазона ся в единицу и на выходе первого пре- изменения 2 -1 х 0 при условии дц образователя 13.1 прямого кода в до- равенства числа разрядов для представ- полнительный образуется с учетом ления чисел х и у диапазон представнаходиться в указанном диапазоне

сдвига влево на один разряд значение, равное -2. На этом первый такт работы блока извлечения корня квадратного ти может быть задано равным, напри- из действительного числа закончен.

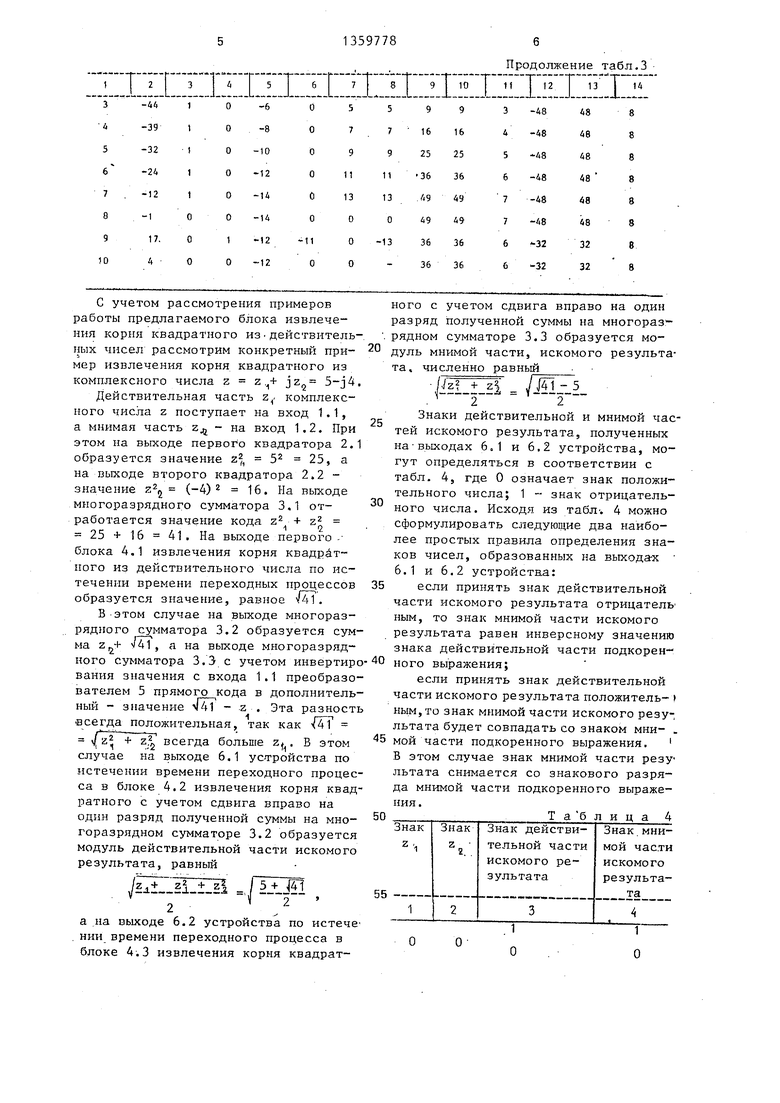

Остальные такты работы сведены в табл. 3. На седьмом такте работы бло.Рассмотрим пример извлечения кор- ка на выходе реверсивного счетчика ня квадратного из действительного 12 установится искомое значение , числа у 4,8, заданного четырьмя 40 Равное с некоторой точностью величиления будет определяться -соотношением 2 у i 2 -1, а значение погрешносмер, половине пискоетности представ 1 о h о ления чисел у, т.е. -г «i

старшими двоичными разрядами (п 4), при представлении искомого переменного X целыми числами , (запятая фик- сирована после младшего разряда) и заданной погрешностью .

В исходном состоянии реверсивный счетчик 12 и регистр 17 числа обнуле45

ны 8. Если дрсле этого значение у примет отрицательное приращение и станет равным, например, у 32, то на выходе блока 19 установится новое значение х 6, что и отражено в тактах работы блоков 9 и 10

(табл. 3). I . ,

вы (цепи установки в ноль не показаны) . На вход 9 устройства подано значение единицы. Таким образом, выходы всех блоков также обнулены.

При подаче на вход 7 устройства подкоренного выражения у 48, а на вход 8 устройства е 8 на выходе второго блока преобразования прямого кода в дополнительный образуется значение, равное -48, и на выходе второго многоразрядного сумматора также образуется значение,-равное -48. В соответствии с табл. 1 значение ло5

ны 8. Если дрсле этого значение у примет отрицательное приращение и станет равным, например, у 32, то на выходе блока 19 установится новое значение х 6, что и отражено в тактах работы блоков 9 и 10

(табл. 3). I . ,

Таблица 3

С учетом рассмотрения примеров работы предлагаемого блока извлечения корня квадратного издействительных чисел рассмотрим конкретный пример извлечения корня квадратного из комплексного числа z z ,+ jz 5-j4,

Действительная часть z. комплексного числа Z поступает на вход 1.1, а мнимая часть z - на вход 1.2. При этом на выходе первого квадратора 2.1 образуется значение z 5 25, а на выходе второго квадратора 2.2 - значение z (-4) 16. На выходе многоразрядного сумматора 3,1 отработается значение кода z + z| 25 + 16 41. На выходе первого-- блока 4,1 извлечения корня квадрАт- ного из действительного числа по истечении времени переходных процессов образуется значение, равное v41.

В-этом случае на выходе многоразрядного мматора 3,2 образуется сум- а на выходе многоразряд20

25

30

35

,+ /41.

ного с учетом сдвига вправо на один разряд полученной суммы на многоразрядном сумматоре 3.3 образуется модуль мнимой части, искомого результата, численно равньгй

Uz + z| „,---

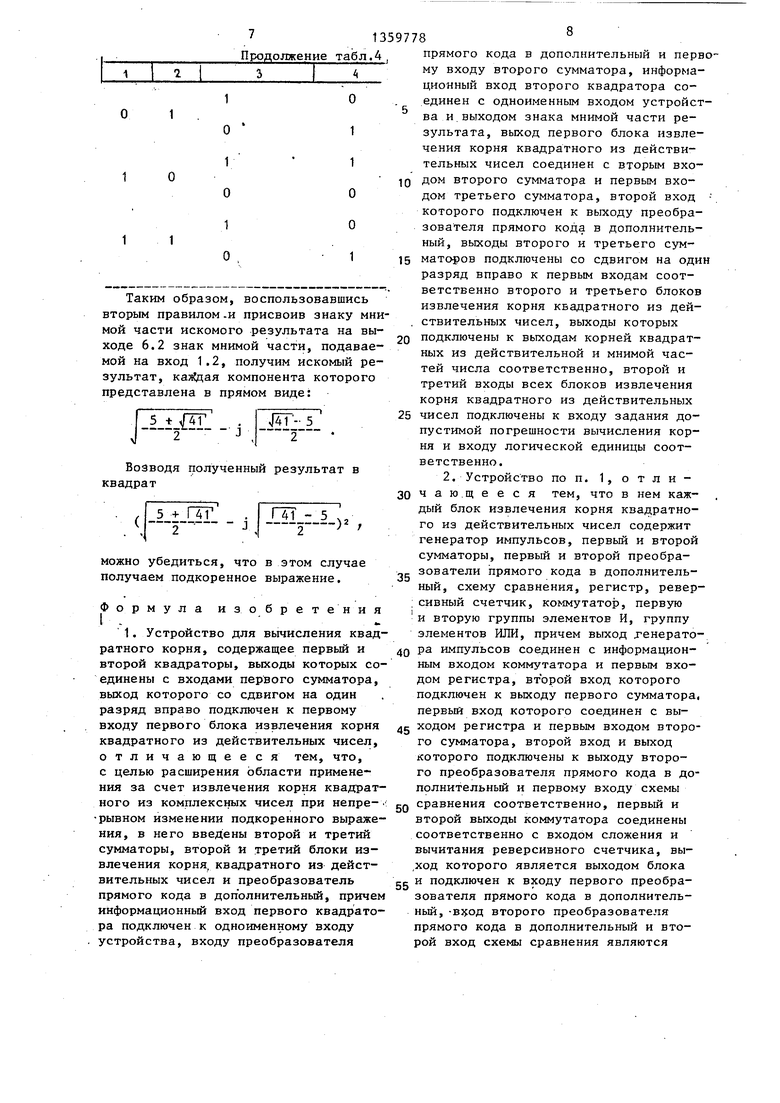

Знаки действительной и мнимой частей искомого результата, полученных на выходах 6.1 и 6,2 устройства, могут определяться в соответствии с табл. 4, где О означает знак положительного числа; 1 - знак отрицательного числа. Исходя из табл-. 4 можно сформулировать следующие два наиболее простых правила определения знаков чисел, образованных на выхода-х 6,1 и 6,2 устройстна:

если принять знак действительной части искомого результата отрицатель ным, то знак мнимой части искомого результата равен инверсному значению знака действительной части подкорен-

ма z

ного сумматора 3.3 с учетом инвертиро-40 цого выражения;

вания значения с входа 1,1 преобразо- если принять знак действительной

части искомого результата положитель- ным, то знак мнимой части искомого результата будет совпадать со знаком мни- . IS мой части подкоренного выражения. В этом случае знак мнимой части резу льтата снимается со знакового разряда мнимой части подкоренного выражения, 50Т а б л и ц а 4

вателем 5 прямого кода в дополнительный - значение 41 - z . Эта разность всегда положительная, так как (41 (z всегда больше z, В этом случае на выходе 6,1 устройства по

истечении времени переходного процесса в блоке 4.2 извлечения корня квадратного с учетом сдвига вправо на один разряд полученной суммы на многоразрядном сумматоре 3,2 образуется модуль действительной части искомого результата, равньш

- Гзт: „ - „ ,

а на выходе 6,2 устройства по истече НИИ времени переходного процесса в блоке 4.3 извлечения корня квадрат55

0

5

0

35

ного с учетом сдвига вправо на один разряд полученной суммы на многоразрядном сумматоре 3.3 образуется модуль мнимой части, искомого результата, численно равньгй

Uz + z| „,---

Знаки действительной и мнимой частей искомого результата, полученных на выходах 6.1 и 6,2 устройства, могут определяться в соответствии с табл. 4, где О означает знак положительного числа; 1 - знак отрицательного числа. Исходя из табл-. 4 можно сформулировать следующие два наиболее простых правила определения знаков чисел, образованных на выхода-х 6,1 и 6,2 устройстна:

если принять знак действительной части искомого результата отрицатель ным, то знак мнимой части искомого результата равен инверсному значению знака действительной части подкорен-

Таким образом, воспользовавшись вторым правилом.и присвоив знаку мнимой части искомого результата на выходе 6.2 знак мнимой части, подаваемой на вход 1.2, получим искомый результат, компонента которого представлена в прямом виде:

Возводя полученный результат в квадрат

+

Т

тг

- J

ГТТ - 5

)

можно убедиться, что в этом случае получаем подкоренное выражение.

Формула изобретения

1. Устройство для вычисления квадратного корня, содержащее первый и второй квадраторы, выходы которых соединены с входами первого сумматора, выход которого со сдвигом на один разряд вправо подключен к первому входу первого блока извлечения корня квадратного из действительных чисел, отличающее с я тем, что, с целью расширения области применения за счет извлечения корня квадратного из комплексных чисел при непре- : рывном изменении подкоренного выражения, в него введены второй и третий сумматоры, второй и третий блоки извлечения корня, квадратного из действительных чисел и преобразователь прямого кода в дополнительный, причем информационный вход первого квадратора подключен к одноименному входу устройства, входу преобразователя

прямого кода в дополнительный и первому входу второго сумматора, информационный вход второго квадратора соединен с одноименным входом устройства и. выходом знака мнимой части результата, выход первого блока извлечения корня квадратного из действительных чисел соединен с вторым входом второго сумматора и первым входом третьего сумматора, второй вход - которого подключен к выходу преобразователя прямого кода в дополнительный, выходы второго и третьего сум5

0

5

0

маторов подключены со сдвигом на один разряд вправо к первым входам соответственно второго и третьего блоков извлечения корня квадратного из действительных чисел, выходы которых подключены к выходам корней квадратных из действительной и мнимой частей числа соответственно, второй и третий входы всех блоков извлечения корня квадратного из действительных чисел подключены к входу задания допустимой погрешности вычисления корня и входу логической единицы соответственно.

2. Устройство по п. 1, отличаю.щееся тем, что в нем каждый блок извлечения корня квадратного из действительных чисел содержит генератор импульсов, первый и второй сумматоры, первый и второй преобразователи прямого кода в дополнительный, схему сравнения, регистр, реверсивный счетчик, коммутатор, первую и вторую группы элементов И, группу элементов ИЛИ, причем выход тенерато0 ра импульсов соединен с информационным входом коммутатора и первым входом регистра, вт орой вход которого подключен к выходу первого сумматора, первый вход которого соединен с выg ходом регистра и первым входом второго сумматора, второй вход и выход которого подключены к выходу второго преобразователя прямого кода в дополнительный и первому входу схемы сравнения соответственно, первый и второй выходы коммутатора соединены соответственно с входом сложения и вычитания реверсивного счетчика, выход которого является выходом блока и подключен к входу первого преобра5

0

5

зователя прямого кода в дополнительный, -вход второго преобразователя прямого кода в дополнительный и второй вход схемы сравнения являются

соответственно первым и вторым входами блока, третий вход которого подключен к первым входам элементов И первой и второй групп, вторые входы которых соединены с вькодом первого преобразователя прямого кода в дополнительный и выходом реверсивного счетчика соответственно, выходы элементов И первой и второй групп соединены с первыми и вторыми входами

83

П .1

TJ

j.t

Редактор А. Лежнина

Составитель Ю. Плющ Техред М. Ходанич

Заказ 6154/50 Тир аж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

элементов ИЛИ группы соответственно, выходы которых подключены к второму . входу первого сумматора, первый выход схемы сравнения соединен с третьими входами элементов И второй группы и первьм управляющим входом коммутатора, второй управляющий вход которого подключен к второму выходу схемы сравнения и третьим входам элементов И первой группы.

- ч,г

р

6.1 -0

Ц,1

83

Фиг.1

Корректор А. Обручар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ | 1984 |

|

SU1166102A1 |

| Устройство для вычисления квадратного корня | 1988 |

|

SU1494004A1 |

| Измеритель параметров амплитудномодулированных сигналов | 1978 |

|

SU752195A1 |

| Устройство для извлечения квадратного корня | 1980 |

|

SU942005A1 |

| Цифровой измеритель показателей качества электрической энергии трехфазной сети | 1988 |

|

SU1633368A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ГАРМОНИКИ НАПРЯЖЕНИЯ | 1990 |

|

RU2030753C1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Устройство для измерения симметричных составляющих напряжений трехфазной сети | 1989 |

|

SU1725166A1 |

Изобретение относится к вычислительной технике и предназначено для вычисления квадратного корня при непрерывном изменении подкоренного выражения. Цель изобретения - расширение области применения за счет извле- чения квадратного корня из комплексных чисел при непрерывном изменении подкоренного выражения. Поставленная- цель достигается путем введения в устройство, содержащее два квадратора, многоразрядный сумматор и блок извлечения квадратного корня из действительных чисел, двух многоразрядных сумматоров, преобразователя прямого кода в дополнительный и еще двух блоков извлечения квадратного корня из действительных чисел. В качестве блока извлечения квадратного корня из действительного числа предлагается новая структура, состоящая из реверсивного счетчика, двух преобразователей прямого кода в дополнительный, двух групп элементов И и группы элементов ИЛИ, -накапливающего сумматора, в обратную связь которого включен регистр числа, многоразрядного сумматора, схемы сравнения, коммутатора и генератора импульсов с соответствующими связями, следящий режим работы в которой -обеспечивается применением схемы сравнения, управляющей реверсивным счетчиком. 1 з.п. ф-лы, 2 ил. 4 табл. с to Ol --vl 00

| Устройство для вычисления квадратного корня | 1984 |

|

SU1254476A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шаронов А.В | |||

| и Лебедев Г.И | |||

| Элементы автоматизированных информационно-измерительных систем | |||

| Конспект лекций | |||

| М.: МАИ, 1976, с | |||

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-15—Публикация

1986-02-26—Подача