регистра и входом схемы сравнения с нулем, прямой выход которой соеди нен с первым управляющим входом пятого коммутатора и заправляющим входом блока извлечения квадратного корня, выходы разрядов которого сое динены с вторыми входами соответств ющих элементов И второй группы, выходы которых соединены с информационным- входом реверсивного счетчика, выход которого соединен с первы и BTdpbiM информационными входами шестого коммутатора и вторым и трет информационньми входами второго ком мутатора, выход которого соединен с вторым информационным входом сумматора-вычитателя, инверсный выход схемы сравнения с нулем соединен с вторым управляющим входом пятого .коммутатора и первым управляющим входом шестого коммутатора, выход которого является выходом устройств 2. Устройство по п. 1, отличающееся тем,что блок анализа содержит триггер, два элемента .задержки и с первого по пятьй эле,менты-И, прямой и инверсный выходы триггера соединены с первыми входа02t-m соответственно первого и второго элементов И, вторые входы которых соединены с выходами соотве.:ственно первого и второго элементов задержки, инверсные выходы первого и пторого элементов И соединены с первыми входами соответственно третьего и четвертого элементов И, первый и второй входы пятого элемента И соединены с прямыми выходами соответственно первого и второго элементов И, вход установки в О триггера соединен с инверсным выходом схемы сравнения, вторым входом четвертого элемента И и входом первого элемента задержки, вход установки в 1 триггера соединен с прямым выходом схемы, сравнения, вторым входом.третьего элемента И, входом второго элемента задержки, управляющим входом сумматора-вычитателя и входом разрешения блока синхронизации, вход останова которого соединен с выходом пятого элемента И и вторым управляющим входом шестого коммутатора, выходы третьего и четвертого элементов И соединены с входами соответственно суммирования и вычитания реверсивного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1983 |

|

SU1140117A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1015380A1 |

| Устройство для вычисления функции arctg y/x | 2017 |

|

RU2642385C1 |

| Вычислительное устройство | 1986 |

|

SU1325468A1 |

| Устройство для вычисления квадратного корня | 1988 |

|

SU1501051A1 |

| Устройство для извлечения квадратного корня | 1982 |

|

SU1129608A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1151957A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

1. УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ Z -4 хЧ .содержащее первый и второй коммутаторы, сумматор, первый регистр и схему сравнения, отличающееся тем, что, с целью повышения быстродействия, в него введены с третьего по шестой коммутаторы, первый и второй квадраторы, второй регистр, с первой по четвертую группы элементов И, схема сравнения с нулем, блок извлечения квадратного корня, реверсивньй счетчик, блок анализа и блок синхронизации, причем сумматор выполнен в виде сумматора-вьиитателя, первые информационные входы первого и второго коммутаторов сое динены соответственно с входом первого аргумента устройства и выходом ;первого квадратора, вход которого соединен с входом второго аргумента устройства, вход пуска которого подключен к входу пуска блока синхронизации, первьй выход которого соединен с первыми управляющими входами с первого по третий коммутаторов и первыми входами элементов И первой и второй групп, второй выход блока синхронизации соединен с вторыми управляющими входами первого и второго коммутаторов и первым управляющим входом четвертого коммутатора, третий выход блока синхронизации соединен с первыми входами элементов И третьей и четвертой групп, четвертьм выход блока синхронизации соединен с третьим управляющим входом второго коммутатора и вторыми управляющими входами третьего и четвертого коммутаторов, выход первого коммутатора через второй квад-, ратор соединен с первым информационным входом третьего коммутатора, выход которого соединен с первым ин(Л формационным входом сумматора-вычитателя, выходы разрядов которого соединены с вторыми входами соответствующих элементов И первой группы и первым и вторьм информационными . входами четвертого коммутатора, выход которого соединен с информационным входом второго регистра, выходы ф разрядов которого соединены с вторым О) информационным вхрдом третьего коммутатора и вторыми входами соответствующих элементов И третьей N5 группы, выходы которых соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами элементов И четвертой группы, вторые входы эле- . ментов И которой соединены с выходами младших разрядов первого регистра и первым информационным входом пятого коммутатора, второй информационный вход которого соединен с выходами старших разрядов первого

Изобретение относится к вычислительной технике и может быть использовано в системах обработки в реальном времени, где требуется опреде-лить расстояние по заданным координатам на плоскости или в пространстве либо амплитуды комплексных сигналов, например, в цифровых спект роанализаторах.

Известно устройство, обеспечивающее, определение величины корня квадратного из квадратов двух величин D

Однако это устройство имеет малую точность.

Наиболее близким по технической сущности к предложенному является устройство извлечения квадратного корня из суммы квадратов, содержащее два блока элементов И-ИПИ, два компаратора, регистр сдвига на один

разряд вправо, блок памяти, два умножителя, сумматор Г21,

Недостатками известного устройства являются невысокое быстроДействие и наличие относительной погрешности в пределах 0,8-1,4%.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в устройство для вычисления функции 2 Тх%у,содержащее первый и второй коммутаторы, сумматор, первьй регистр и схему сравнения, дополнительно введены с третьего по

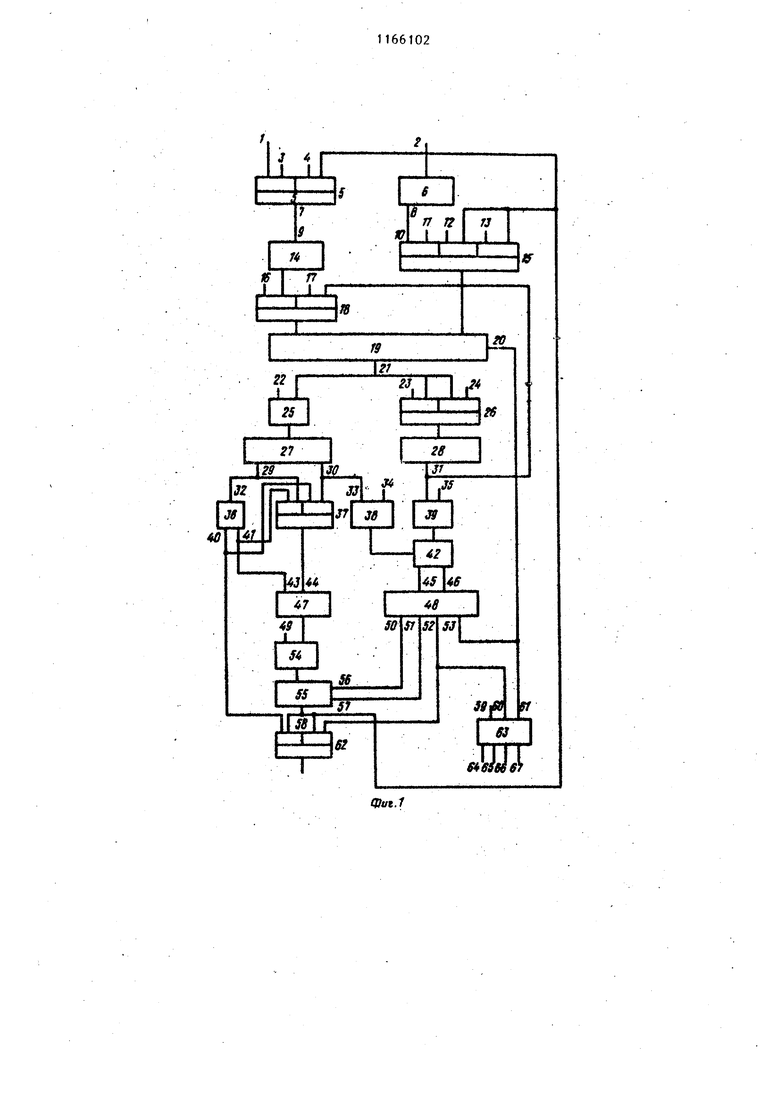

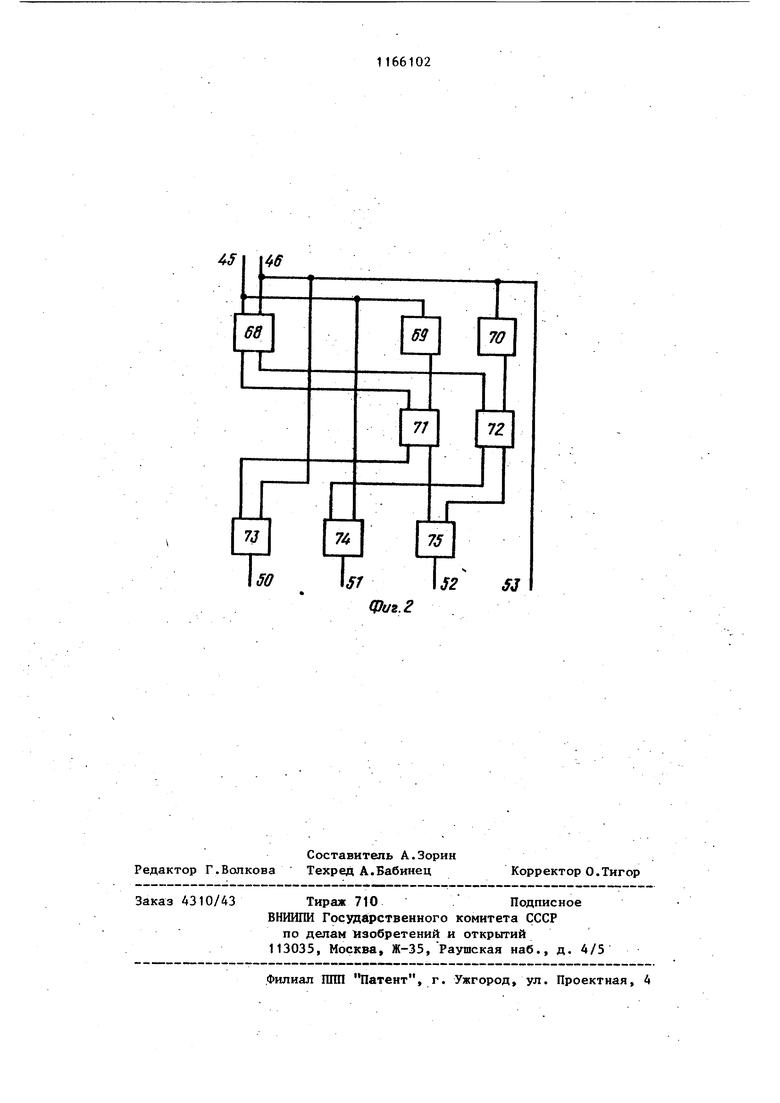

шестой коммутаторы, первьА и второй квадраторы, второй регистр, с первой по четвертую группы элементов И, схема сравнения с нулем, блок извлечения квадратного корня, реверсивный счетчик, блок анализа и блок синхронизации, причем сумматор выполней в виде сумматора-вычитателя, первые информационные входы первого и второго коммутаторов соединены соответственно с входом первого арг мента устройства и выходом первого квадратора, вход которого соединен с входом второго аргумента устройст ва, вход уска которого подключен к входу пуска блока синхронизации, первый вых-од которого соединен с первыми управляющими входами с первого по третий коммутаторов и первы ми входами элементов И первой и вто рой групп, второй выход блока синхронизации соединен с вторыми управляющими входами первого и второг коммутаторов и первым управляющим входом четвертого коммутатора, третий выход блока синхронизации соединен с первыми входами элементов И третьей и четвертой групп, четверты вькод блока синхронизации соединен с третьим управляющим входом второг коммутатора и вторыми управляющими входами третьего и четвертого коммутаторов, выход первого коммутатора через второй квадратор соединен с первым информационным входом третьего коммутатора, выход которого соединен с первым информационным входом сумматора-вычитателя, выходы разрядов которого соединены с вторыми входами соответствующих элементов И первой группы и первым и вторы информационными входами четвертого коммутатора, выход которого- соединен с информационным входом второго регистраj выходы разрядов которого соединены с вторым информационным входом третьего коммутатора и вторыми входами соответствующих элемен- . тов И третьей группы, вькоды которых соединены с первой группой входо схемы сравнения, вторая группа входов которой соединена с вькодами элементов И четвертой группы, вторые входы соответствую1щх элементов И/ которой соединены с выходами младших разрядов первого регистра и первым информационным входом пятого коммутатора, второй информационный вход которого соединен с выходами старших разрядов первого регистра и входом схемы сранения с нулем, прямой выход которой соединен с первым управляющим входом пятого ком .мутатора и управляющим входом блока извлечения квадратного корня, выходы разрядов которого соединены с вторыми входами соответствующих элементов И второй группы, выходы которых соединены с информационным входом реверсивного счетчика, выход которого . соединен с первым и вторым информационными входами шестого коммутатора и вторым и третьим информационными входами второго коммутатора, выход которого соединен с вторым информационным входом сумматора-вычитателя, инверсньй выход схемы сравнения с нулем соединения с вторым управляющим входом пятого коммутатора и первым управляющим входом шестого коммутатора, выход которого является выходом устройства. Кроме того, блок анализа содержит триггер, два элемента задержки и с первого по пятый элементы И, прямой и инверсный выходы триггера соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых соединены с выходами соответственно первого и второго элементов задержки, инверс.ные выходы первого и второго элементов И соединены с первыми входами соответственно третьего и четвертого элементов И, первый и второй входы пятого элемента И соединены с прямыми выходами соответственно первого и второго элементов И, вход установки в О триггера соединен с инверсным выходом схемы сравнения, вторым входом четвертого элемента И и входом первого элемента задержки, вход установки в 1 триггера соединен с прямым выходом схемы сравнения, вторым входом третьего элемента И, входом второго элемента задержки, управляющим входом сумматоравычитателя и входом разрешения блока синхронизации, вход останова которого соединен с выходом пятого элемента И и вторым управляющим входом шестого коммутатора, выходы третьего и четвертого элементов И соединены с входами соответственно суммирования и вычитания реверсивного счетчика. На фиг. 1 дана блок-схема устройства на фиг. 2 - вариант конструкции блока анализа. Устройство содержит входы 1 и 2 аргумента, входы 3 и 4 управления коммутатора 5, квадратор 6, выходы 7 коммутатора и 8 квадратора, входы 9 5 квадратора,входы 10-13 коммутатора квадратор 14, коммутатор 15, входы 16 и 17 коммутатора 18, сумматорвычитатель 19,. вход 20 з Фавления, выход 21 сумматора-вычитателя, входы 22-2 группы элементов И 25 и коммутатора 26, регистры 27 и 28, выходы 29-31 регистров, входы 32-35 схемы 36 сравнения с нулем, коммутатор 37, группу-элементов И 38 .и 39, выходы 40 и 41 схемы сравнени с нулем, схему 42 сравнения, входы 43-46 блока 47 извлечения квадратного корня и блока 48 анализа, вход 49. группы элементов И, выходы 50-53 блока анализа, группу элементов И 54, реверсивный счетчик 55 с входами 56 и 57 и выходом 58, входы .блока 59-61 синхронизации, коммутатор 62, блок 63 с выходами 64-67. Блок анализа содержит триггер 68 элементы 69 и 70 задержки, элементы И 71-75. Выходы блока 63.синхронизащи имеют следующую логику подключения: 64-3, 11, 16, 22, 49 65-4, 12, З; 66-34, 35; 67-13, 17, 24. Работа устройства основана на следующем алгоритме. Пусть 2 И . разрядность подкоренного выражения Предлагается извлекать корень табличным путем только из h старших разрядов подкоренного выражения и затем при необходимости корректи ровать результат либо извлекать табличным путем корень из П млад ших разрядов, если старшие разряды равны 0. Коррекция разрядов основывается на следующем: существует интервал В, , BjJ значений подкоренного вь1ражения, в пределах которого в СИЛУ ограничений (П -разрядные значения аргументов), значение корня является одним и тем же с точностью до младшего разряда аргументов и определяется i . (1) el Л г-гЧг, если Z - приближенное значение кор ня из И старших разрядов подкоренного вьгражения и Z -квадрат этого значения, тона основе выражений. (1) возможно определить границы достоверности Z и если исходное 026 подкоренное значение находится в этом интервале е,, то процесс вычисления заканчивается, в противном случае существует связь между найденными границами неверного, приближения ,, 7 границами точного результата В ,62 связь между границами определяется 62-6, z,zH (i) , «I n В,&,2Г z; %,z (3 l -г;, z;., , преобразовывая вьфажения (2) и (3) учитьшая, что все значения границ содержат одинаковые п старших разрядов и их численные значения можно рассматривать только в пределах И мпадших разрядов Bin мл 2 мл г-т- -т-% /;6,пмл &,пмп г-т; + 21 t . г t Анализ выражений (4) и (5) показывает, что можно оперировать только с (fj -1) старшими разрядами fj мпадших разрядов значений границ, что позволит значительно сократить разрядность регистрового и дополнительного оборудования, если 4 подкоренное значение и 2 62 , найденного в соответствии с вьфажением (1), то на основании (4) начинается последовательный процесс суммиройания 2 со значением приближенного % , увеличенного на единицу, причем в каждом цикле приближенное значение увеличивается на единицу. Точным значением корня будет последнее наращиваемое значение z , когда сумма превысит или станет равной подкоренному значению; если 2 Oj ; и Z « 6, J то коррекция результата отличается тем, что из С, происходит вычитание значения 2, уменьшенного на единицу, причем в каждом цикле значение уменьшается на единицу до тех пор, пока г €

71

не станет больше или равно разности Число циклов зависит от величины старших ц разрядов и является максмальным, когда она равна 1. Поэтому целесообразно первое приближение брать в середине интервала возможных значений, что уменьшит число лагов. Методом времяструктурной оптимизации устройства является варьирование числом старших разрядов из 2 п , на основе которых определяется первое приближение, результата

В качестве примера рассмотрим работу устройства при ц 11 (разрядность аргументов). Аргументы, с приходом сигнала разрешения на вход 59 .блока 63 поступают на входы 1 и 2 устройства, а на входы 3 и It - сигнал с выхода 64. В результате первый аргумент с выхода 7 коммутатора 5 поступает на вход 9 квадратора 14, а квадрат второго аргумента с выхода 8 квадратора 6 на входы 10 коммутатора 15. Квадратор 14 возводит в квадрат первый аргумент и по управляющему входу 16 коммутатора 18 коммутирует данное значение на сумматор-вычитатель 19, куда поступает также квадрат второго аргумента с выхода коммутатора 15. Сумматор-вычитатель, установленный по входу 20 на суммирование, производит суммирование и значение суммы поступает на элементы И 25, а с его выхода записывается в первьй регистр 27. Пусть там находится число 3969, двоичный код которого 0000000000111110000001. Анализ 11 старших разрядов с первого выхода 29 по входу 32 схемы 36 определяет наличие О и 1 на инверсном 40 и прямом 41 его выходах. Поэтому значение 11 старших разрядов поступает через коммутатор 37 на информационный вход-44 блока 47. На управляющем входе 43 логическая единица и поэтому на выходе 47 получаем приближенное значение корня, которое возможно придетсй корректировать. Это значение по управляющему входу 49 через блок 54

28

поступает на вход реверсивного счетчика 55, а с его выхода - на входы коммутаторов 5 и 15. С приходом второго управляющего сигнала с выхода 65 на управляющие входы 4, 12 и 23 в регистр 28 через коммутатор 26 поступает значение верхней границы интервала в соответствии с выражением (1). Для данного значения интервал точных значений корня меняется от 46 до 63. Пусть, . первое приближение равно середине этого интервала, т.е. 55. Значение 10 старших разрядов 11 младujHx разрядов верхней границы для Z- 55,8 1000000100, а значение 10 старших разрядов 11 младших подкоренного вьфажения 1111000000. Эти значения с подачей третьего управляющего сигнала с выхода 66 на входы 34 и 35 поступают через элемент 38 и 39 на схему 42 сравнения .

. Управляющие сигналы с выходов 50 и 53 соответственно увеличивают содержимое счетчика 55 на единицу и устанавливают сумматор-вычитатель на суммирование. С приходом управляющего, сигнала с выхода 67 на входы 13, 17 и 24 начинается процесс наращивания значения верхней границы в соответствии с выражением (4), а с приходом управляющего сигнала с выхода 66 ее сравнение с содержимым регистра 27. Такая поочередная подача управляющих сигналов с выходов 67 и 66 продолжается до тех, пока Z4 2 Это наступит, когда содержимое счетчика 55 станет равным 63, так как содержимое регистров 27 и 28 станет равным между собой. Логический сигнал с выхода 52 блокирует работу блока 63 и разрешает вьщачу содержимого 55 по информационным входам коммутатора 62 на выход устройства.

Таким образом, быстродействие предлагаемого устройства возросло в 1,6 раза и обеспечена точность результата в пределах разрядной сетки аргументов.

50

S3

Фиг.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для извлечения квадратного корня из суммы квадратов двух величин | 1976 |

|

SU624238A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1980 |

|

SU943718A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-07—Публикация

1984-01-16—Подача