Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах специализированных цифровых вычислительных машин для извлечения корня квадратного из большого массива многоразрядных чисел. Известно устройство, построенное на конвейерном принципе и выполненно из однотипных блоков, каждый из кото рых содержит два регистра, схему фор мирования п + 1 старших разрядов, два триггера и элемент И tH, Это устройство предназначено для одновременного выполнения арифмётических операций над множеством чисел, но не предназначено для выполне ния извлечения квадратного корня из одного массива многоразрядных чисел. Наиболее близким к предлагаемому является устройство, содержащее п однотипных решающих блоков, каждый из которых содержит регистр остатка, сумматор-вычитатель, первые входы которого подключены к первой группе выходов регистра остатка, регистр результата, причем вторая группа выходов регистра остатка предыдущего блока соединена с первой группой входов регистра остатков последующего блока, выходы регистра результата предыдущего блока соединены с соответствующими входами регистра результата последующего блока 2. Известное устройство обладает недостаточно высоким быстродействием и производительностью при обработке массива многоразрядных чисел. Быстродействие его определяется скоростью одного такта обработки, которое равно V 2Ч,,„+ 2tM, где tp - время суммирования на сумматоре; время анализа знака сумматора на схеме; - время срабатывания тригг ра переполнения; t - время прохождения информации через элементы И. Выполнение операции извлечения квадратного корня в два полутакта замедляет процесс вычислений и усложняет схему. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что устройство для извлечения квадратного корня, содержащее и однотипных решающих блоков, каждый из которых содержит регистр остатка, riepsap группа выходов которого прдключена к первой группе входов сумматора- ычитателя, вторая групп выходов регистра остатка подключена к соответствующим входам первой группы остатка (i + 1)-го где I 1,п) блока, регистр проме жуточного результата, входы двух ст ших разрядов которого подключены со ответственно к входам логической единицы и нуля устройства, выходы р гистра промежуточного результата iблока, кроме первого, соединены с соответствующими входами регистра промежуточного результата (i + 1)-г блока со сдвигом на один разряд вле во п-ый решающий блок содержит такж регистр конечного результата, входы которого соединены с соответствующи выходами регистра промежуточного ре зультата, дополнительно содержит в каждом решающем блоке, кроме п-го, (Г + 1) (где i - номер решающего бл ка элементов И-ИЛИ, причем выходы регистра промежуточного результата соединены со второй группой входов сумматора-вычитателя, -знаковые раз ряды которого соединены с управляющими входами элементов И-ИЛИ, инверсный выход знакового разряда сумматора-вычитателя, кроме п-го, соединен с информационным входом регистра промежуточного результата (i + 1) -го блока, инверсный выход сумматора-вычитателя| п-го блока подключен к старшему разряду регист ра конечного результата, выходы сум матора-вычислителя соединены с первой группой информационных входов элементов И-ИЛИ, вторая группа инфо

мационных входов которых соединена с первой группой выходов регистра остатка (п - 1)-го блока, выходы

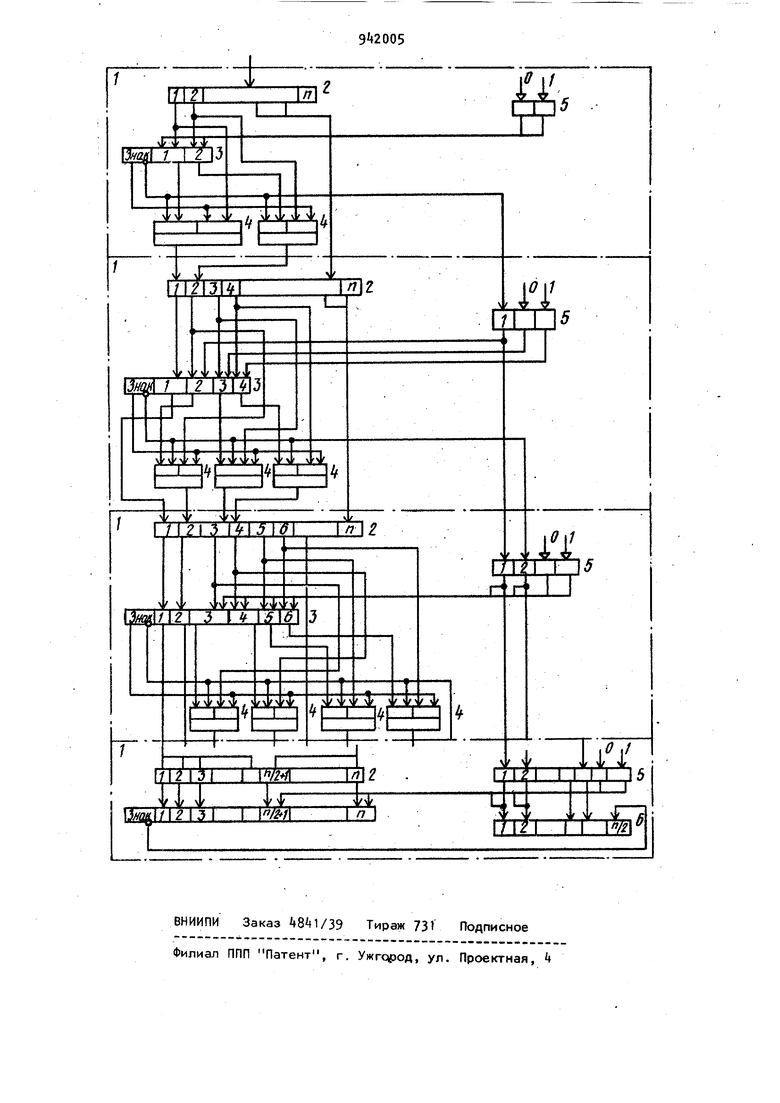

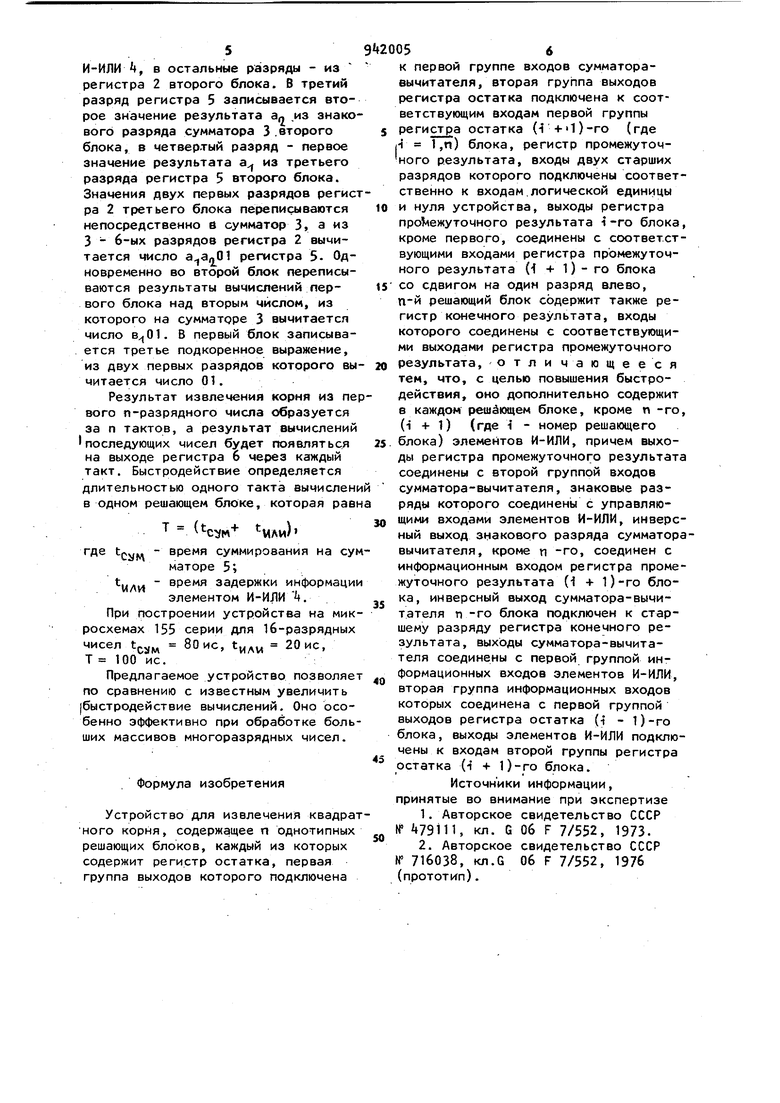

следующие значения: в 1-й разряд |ИЗ сумматора 3 второго блока, во 2 - 4-ые разряды - из элементов 54 элементов И-ИЛИ подключены к входам второй группы регистра остатка (п + 1)-го блока. На чертеже представлена функциональная схема устройства. Устройство содержит п однотипных решающих блоков 1, каждый из которь(х включает регистр 2 остатка, сумматор- вычитатель 3, элементы И-ИЛИ 1, регистр 5 промежуточного результата, регистр 6 конечного результата. В устройстве производится извлечение квадратного корня из п-разрядных чисел за п тактов, В Первом такте в регистр 2 первого решающего блока 1 записывается первое подкоренное выражение. Из двух старших разрядов регистра 2 вычитается число 01 регистра 5 в сумматоре 3. Если частичный остаток сумматора 3 положителен (знак суммы равен нулю), разряд результата равен единице и информация с выходов сумматора 3 проходит через первую группу информационных входов элементов И-ИЛИ 4. Если остаток сумматора 3 отрицателен, разряд результата равен нулю и на вторую группу информационных входов элементов И-ИЛИ поступает значение подкоренного выражения, т.е. происходит восстановление остатка. Во втором такте производится запись значений двух разрядов в регистр 2 через элемент И-ИЛИ k первого блока 1 и запись значений остальных разрядов регистра 2 первого блока в регистр 2 второго блока, а также запись первого значения результата в регистр 5 из знакового разряда сумматора 3. Значение 1-го разряда регистра 2 второго блока поступает непосредственно в 1-й разряд сумматора 3, а из. содержимого 2 - 4-ых разрядов регистра 2 вычитается число регистра 5, где а - первое значение результата вычислений, результат вычитания поступает на элемент И-ИЛИ k. Одновременно в первом решающем блоке 1 в регистр 2 поступает второе подкоренное выражение, из двух первых разрядов которого вычитается число 01 регистра 5, а результат вычитания поступает на элемент И-ИЛИ А. В третьем такте в регистр 2 третьgj-g решающего блока записываются И-ИЛИ , в остальные разряды - из регистра 2 второго блока. В третий разряд регистра 5 записывается второе значение результата а ,из знако вого разряда сумматора 3 .второго блока, в четвертый разряд - первое значение результата а из третьего разряда регистра 5 второго блока. Значения двух первых разрядов регис ра 2 третьего блока переписываются непосредственно в сумматор 3, э из 3 - 6-ых разрядов регистра 2 вычитается число регистра 5. Одновременно во второй блок переписываются результаты вычислений первого блока над вторым числом, из которого на сумматоре 3 вычитается число . В первый блок записывается третье подкоренное выражение, из двух первых разрядов которого вы читается число 01. Результат извлечения корня из пе вого п-разрядного числа образуется за п тактов, а результат вычислений последующих чисел будет появляться на выходе регистра 6 через каждый такт. Быстродействие определяется длительностью одного такта вычислен в одном решающем блоке, которая рав Ч Чли) где tj4j,M - время суммирования на су маторе 5; или Р задержки информаци элементом И-ИЛИ . При построении устройства на мик росхемах 155 серии для 16-разрядных чисел 80 ис, 20 ис, Т 100 ис. Предлагаемое устройство позволяе по сравнению с известным увеличить быстродействие вычислений. Оно особенно эффективно при обработке боль ших массивов многоразрядных чисел. , Формула изобретения Устройство для извлечения квадра ного корНя, содержащее п однотипных решающих блоков, каждый из которых содержит регистр остатка, первая группа выходов которого подключена к первой группе входов сумматоравычитателя, вторая группа выходов регистра остатка подключена к соответствующим входам первой группы регистра остатка (i 4-1)-го (где /i 1,п) блока, регистр промежуточного результата, входы двух старших разрядов которого подключены соответственно к входам,логической единицы и нуля устройства, выходы регистра про Межуточного результата i-го блока, кроме первого, соединены с соответствующими входами регистра промежуточного результата (i + 1) - го блока со сдвигом на один разряд влево, П-й решающий блок содержит также регистр конечного результата, входы которого соединены с соответствующими выходами регистра промежуточного результата, отличающееся тем, что, с целью повышения быстродействия, оно дополнительно содержит в каждом решающем блоке, кроме п -го, (i +1) (где 1 - номер решающего блока) элементов И-ИЛИ, причем выходы регистра промежуточного результата соединены с второй группой входов сумматора-вычитателя, знаковые разряды которого соединены с управляющими входами элементов И-ИЛИ, инверсный выход знакового разряда сумматоравычитателя, кроме п -го, соединен с информационным входом регистра промежуточного результата (1 -f 1) -го блока, инверсный выход сумматора-вычитателя п -го блока подключен к старшему разряду регистра конечного результата, выходы сумматора-вычитателя соединены с первой группой информационных входов элементов И-ИЛИ, вторая группа информационных входов которых соединена с первой группой выходов регистра остатка (i - 1)-го блока, выходы элементов И-ИЛИ подключены к входам второй группы регистра остатка (i + 1)-го блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР W i 79l11, кл. G Об F 7/552, 1973. 2.Авторское свидетельство СССР If 716038, кл.а Об F 7/552, 1976 (прототип).

z±

ПЗ

ИШ

. . j. IJvaflfl 7 IYl3

ajzoos

I/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1976 |

|

SU716038A1 |

| Арифметическое устройство | 1981 |

|

SU993252A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1015380A1 |

| Арифметическое устройство | 1976 |

|

SU703804A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1571581A1 |

| Устройство для вычисления координат | 1978 |

|

SU752350A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

/ Li LJ LJL I |Vf I

Ш

Ш2

Щш

Дг

/ r

Шм| ; {21

d

J

3

tO

1

f

jm2.

.U|g

a

Л

a:

ЬЫ

yf

T

ТШ

Щ

i

Ф k if .

f 31 J }4 иш Шдй1/1г13Г т Ш

7|/

л

J5

1/

n

rrnj

E

w .jj/j. I I I II fN I

Авторы

Даты

1982-07-07—Публикация

1980-08-04—Подача