(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для побитовой обработки чисел,представленных в форме с плавающей запятой | 1980 |

|

SU938284A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для нормализации чисел | 1980 |

|

SU862139A1 |

| Арифметическое устройство для обработки комплексных чисел | 1984 |

|

SU1223249A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| Цифровой спектроанализатор | 1982 |

|

SU1092518A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

Изобретение относится к вычислительной технике и может быть использовано для выполнения операций умножения, деления и извлечения квадратного корня- с плавающей запятой. По основному авт.св. № 703804 известно арифметическое устройство, содержащее п последовательно соедине ных однотипных блоков, причем каждый блок содержит два регистра, комбинационный сумматор и триггер, выходы первого регистра каждого блока соеди нены с первой группой входов комбинационного сумматора того ж блока, выход i-ro разряда (,....,п-1) комбинационного сумматора {К-1)-го блока (К«2;...,п) соединен с входом (i+l)-ro разряда первого регистра К-го блока, выход i-ro разряда второ го регистра (К-1)-го блока подключен к входу i-го разряда второго регистра К-го блока, входы первого и. второго регистров первого блока соединены с первой и второй группами входов устройства. ( Каждый блок, устройства содержит третий регистр, узел анализа переполнения комбинационного сумматора, первый и второй коммутаторы, входы узла анализа переполнения комбинационного сумматора каждого блока соединены с выходами знакового разряда комбинационного сумматора, а выход подключен к входу триггера и первому входу первого коммутатора, выход триггера подключен к входу п-го разряда третьего регистра и первому входу каждого разряда второго коммутатора, второй вход которого соединен с выходом первого разряда третьего регистра, третий и четвертый входы соединены с прямым и инверсным выходами соответствующего разряда второго регистра, выходы второго коммутатора соединены с второй групТ1ОЙ входов комбинационного сумматора, второй вход первого коммутатора К-го блока соединен с выходом К-го разряда второго регистра (К-1)-го блока, второй вход первого коммутатора первого блока соединен с входом устройства, первый, второй и третий управляющие входы первого коммутатора соединены соответственно с управляющей шиной умножения и деления, управляющей шиной извлечения корня и тактовой ишной устройства, выход г-го разряда третьего регистра (,....,n) (К-1 )-Го блока .соединен с входом (I -1)-го разряда третьего регистра К-го блока.

входы третьего реристра первого блока соединены с третьей группой входов устройства,первый, второй и третий управляющие входы второго коммутатора соединены соответственно с yпpaвляющи lИ шинами умножения, деления и извлечения корня устройства, выход первого коммутатора т-го блока

(,п) соединен с входом т-го

разряда второго регистра того же блока; первый.коммутатор каждого блока устройства содержит элемент И-ИЛИ, первая группа входов которого соединена с вторым и первым управляющим входами коммутатора, а вторая группа входов - с первым и вторым и третьим управляющими входами коммутатора, второй коммутатор каждого К-го (К-1......,п) блока устройства

содержит п элементов И-ИЛИ (по одному .в каждом разряде), причем первая группа входов каждого элемента И-ИЛИ соединена с первым управляющим, вторым и третьим входами ком.мутатора, вторая группа входов соединена с вторым управляющим, первым и четвертым входами коммутатора, первый и второй входы третьей группы входов первого - п-го элементов И-ИЛИ соединены с третьим управляющим и первым входами коммутатора, третий вход третьей группы входов (К-1)-го элемента И-ИЛИ соединен с четвертым входом коммутатора, а третьи входы третьей группы входов .остальных элементов И-ИЛИ соединены с третьими входами коммутатора ClJ ,

Однако известное арифметическое устройство предназначено только для обработки операндов в коде с фиксированной запятой и не может выполнять операции в коде с плавающей запятой .

Цель изобрет ения - расширение функциональных возможностей основного изобретения за счет обработки массивов чисел, представленных в коде с плавающей запятой.

Поставленная цель достигается тем, что устройство дополнительно содержит блок предварительной обработки , блок Обработки порядков, блок памяти, коммутатор и блок нормализации, причем входы блока предварительной обработки являются входами .устройства, первый, второй и третий выходы блока предварительной обработки подключены к входам соответственно первого, второго и третьего регистров первого блока устройства, четвертый и пятый выходы блока предварительной обработки подключены соответственно к первому и второму входам блока обработки порядков, выход которого подключен к входу блока памяти, выходы сумматора, второго и третьего регистров.последнего блока устройства соединены с информационными входами коммутатора, управляющие.

входы которого соединены с управляющими шинами, умножения, извлечения корня и деления устройства, выходы блока памяти и коммутатора соединены соответственно с первым и вторым входами нормализации.

Кроме того, блок предварительной обработки содержит первый преобразователь прямого кода в обратный и первый регистр, соединенные последовательно, второй регистр, второй преЬбразователь прямого кода в обратный

третий регистр, узел определения четности порядка, элемент ИЛИ, сумматор, узел анёьлиза переполнения, сдвиговый регистр, коммутатор, входы блока соединены с входами первого преобразователя прямого кода в обратный, второго регистра, второго преобразователя прямого кода в обраный и сдвигового регистра соответственно, выход второго преобразователя прямого кода в обратный подключён к входу третьего регистра, выходы знакового разряда и п-го информационного, разрядов которого подключены к входам узла определения четности порядка, управляющий вход которого соединен с управлякщей шиной извлечения корня устройства, а выход подключен к первому входу элемента ИЛИ, второй вход которого соедине с управляющей шиной деления устройства, входы разрядов сумматора соединены с выходами разрядов третьего регистра, выход элемента ИЛИ соединен с вторым входом младшего разряда сумматора и управляющим входом сдвиговог регистра, выход которого соединен с входом коммутатора, первый выход коммутатора, выход второго регистра, выход сумматора и выход первого регистра подключены к выходам блока, выходы знаковых разрядов сумматора .

подключены к входу узла анализа переполнения, управляющие входы коммутатора соединены с управляющими шинами деления, извлечения корня и умножения устройства..

При этом блок обработки порядков содержит первый регистр, кс 1мутатор, второй регистр, сумматор, .узел анализа переполнения, узел сдвига, преобразователь прямого ..кода в обратный причем входы блока .соединены с входами второго и первого регистров соответственно, прямой и инверсный выходы первого регистра соединены с информационными входами коммутатора, управлякядие входы которого подключены . к управляющим шинам умножения и

.деления, устройства, выходы коммутатора и второго регистра соединены с

входами сумматора, выход которого. соединен с входом узла сдвига, выход которого подключен к входу преобраг зователя п| ямога кода в обратный, выход которого является выходом блок выходы знаковых разрядов сумматора

подключены к входам узла анализа переполнения, управляющие входы узла сдвига соединены с управляющими шинг1ми деления, умножения и извлечения корня устройства.

Кроме того, блок нормализации содержит регистр, сдвиговый регистр, дешифратор и сумматор, выход которог соединен с входом регистра, выход сдвигового регистра соединен с входом дешифратора, причем первые входы сумматора и сдвигового регистра соединены с входами блока, вторые их входы соединены с выходом дешифратора, выходы регистров являются выходами блока.

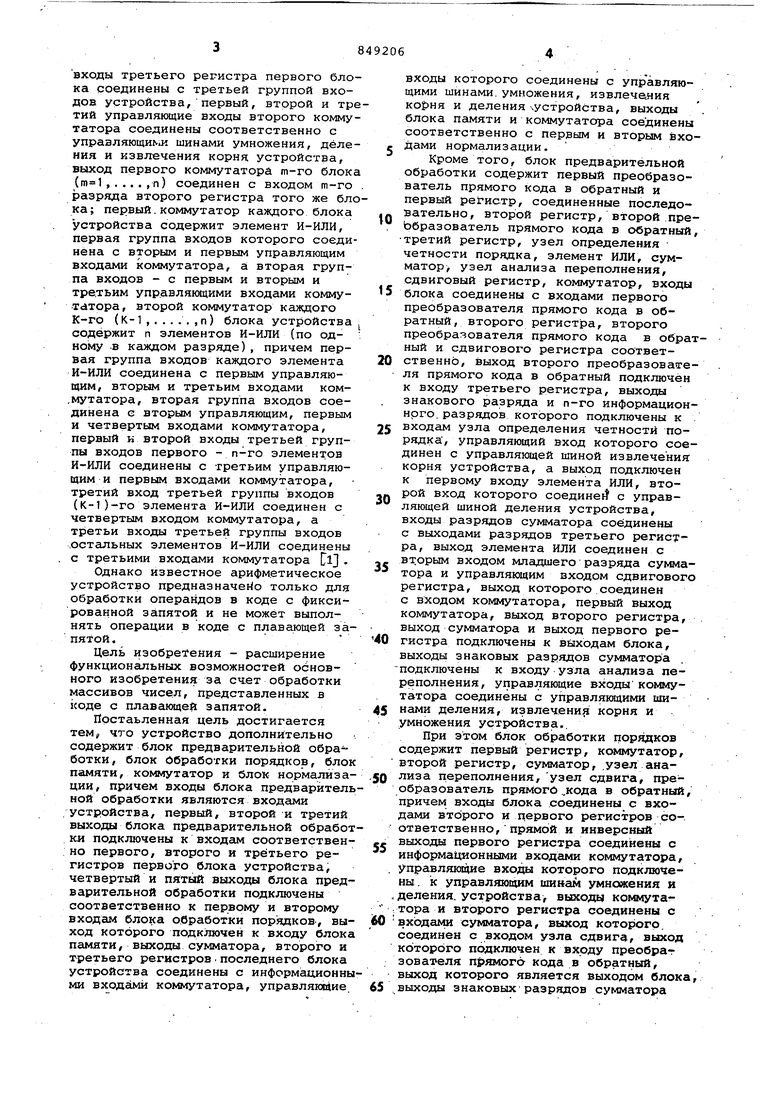

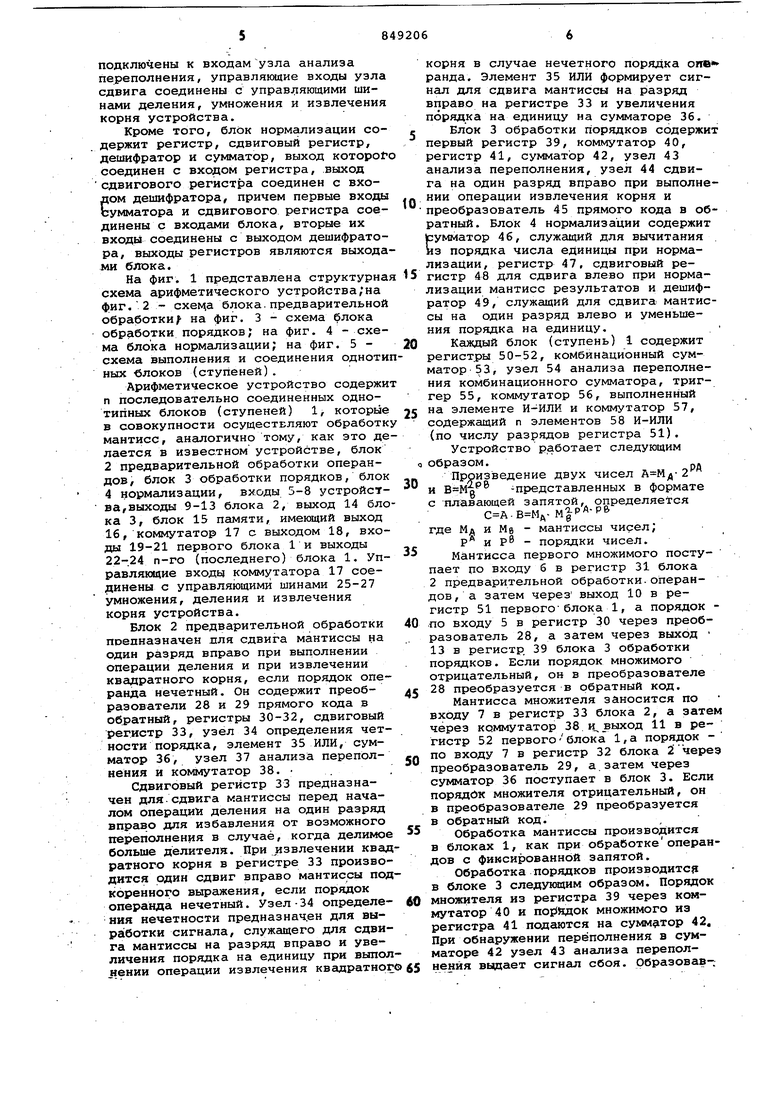

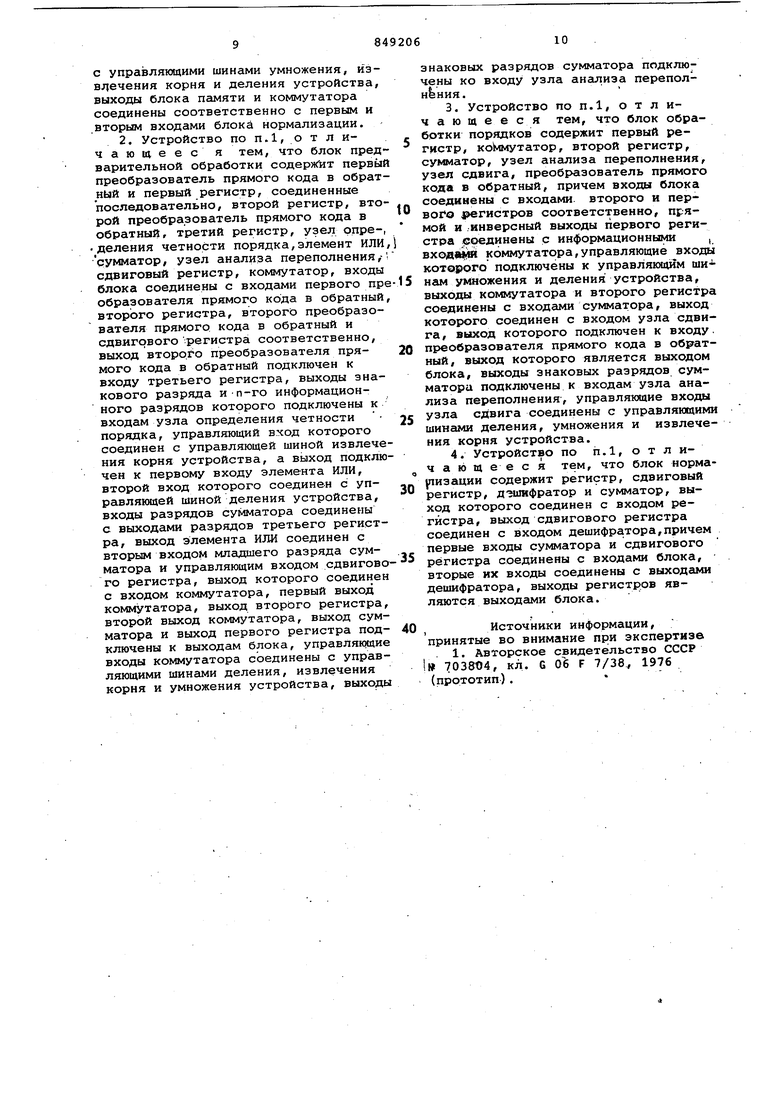

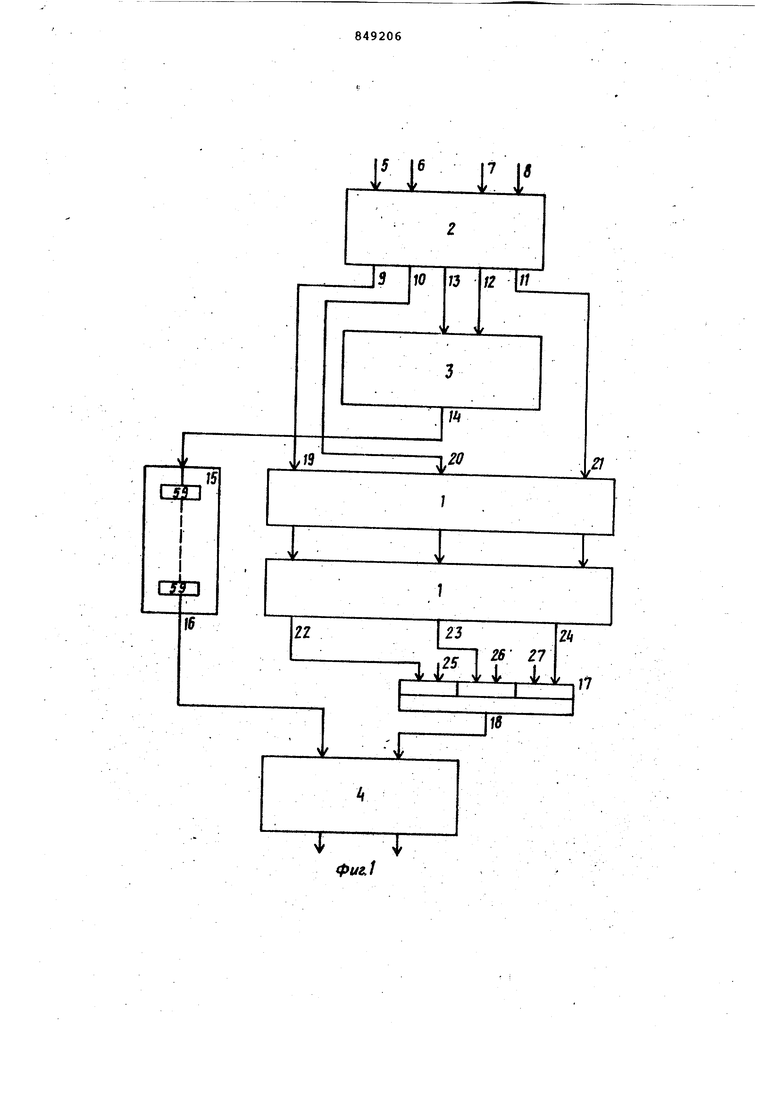

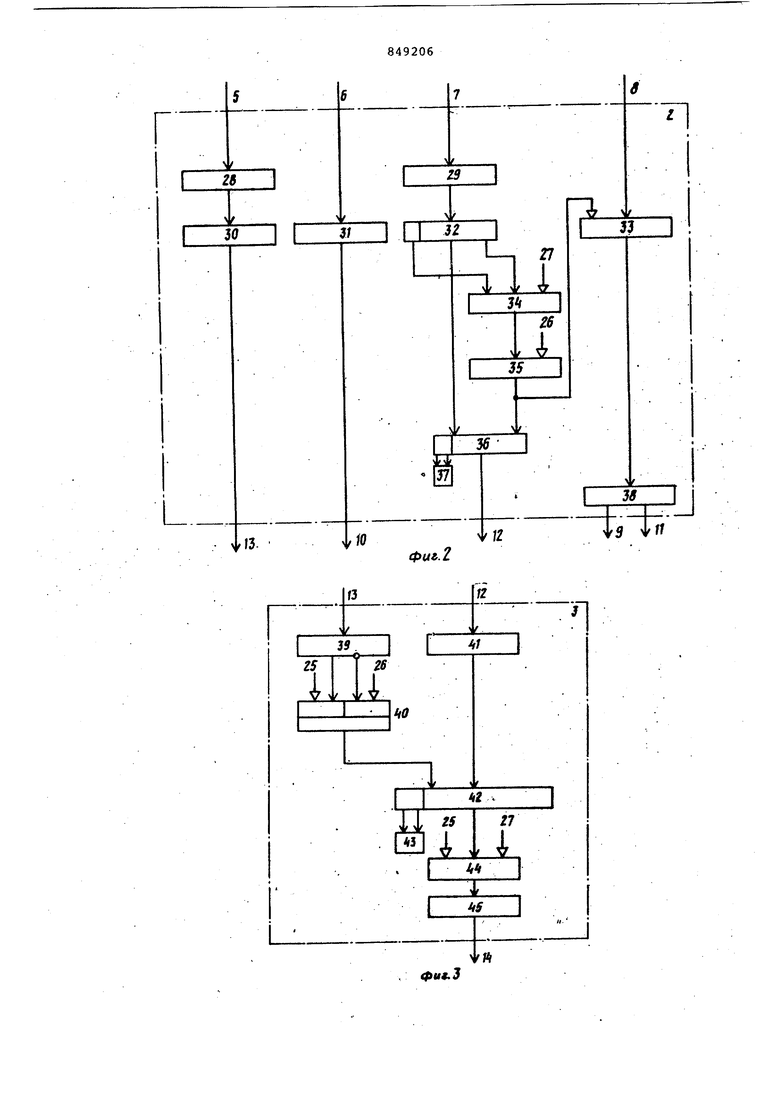

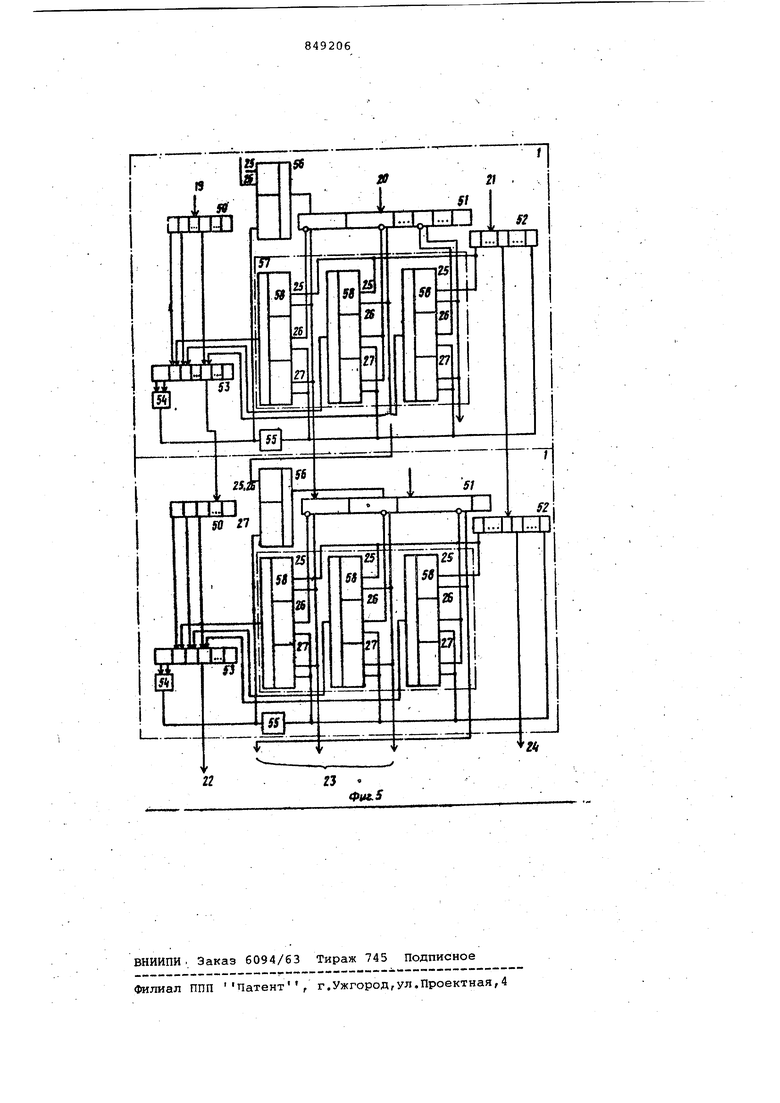

На фиг. 1 представлена структурна схема арифметического устройства;на фиг.2 - схеца блока.предварительной обработки на фиг. 3 - схема лока обработки порядков; на фиг. 4 - схема блока нормсшизации; на фиг. 5 схема выполнения и соединения однотиных блоков (ступеней).

Арифметическое устройство содержи п последовательно соединенных однотипных блоков (ступеней) 1, которые в совокупности осуществляют обработк мантисс, аналогично тому, как это делается в известном устройстве, блок 2 предварительной обработки операндов, блок 3 обработки порядков, блок 4 нормализации, входы 5-8 устройства,выходы 9-13 блока 2, выход 14 блока 3, блок 15 Пс1мяти, имеющий выход 16, коммутатор 17 с выходом 18, входы 19-21 первого блока 1 и выходы 22-.24 п-го (последнего) блока 1. Управляющие входы коммутатора 17 соединены с управляющими шинами 25-27 умножения, деления и извлечения корня устройства.

Блок 2 предварительной обработки поепнаэначен пля сдвига мантиссы на один разряд вправо при выполнении операции деления и при извлечении квадратного корня, если порядок операнда нечетный. Он содержит преобразователи 28 и 29 прямого кода в обратный, регистры 30-32, сдвиговый регистр 33, узел 34 определения четности порядка, элемент 35 ИЛИ, сумматор 36, узел 37 анализа переполнения и коммутатор 38.

Сдвиговый регистр 33 предназначен для.сдвига мантиссы перед началом операций деления на один разряд вправо для избавления от возможного переполнения в случае, когда делимое больше делителя. При .извлечении квадратного корня в регистре 33 производится один сдвиг вправо мантиссы подкоренного вьфажения, если порядок операнда нечетный. Узел-34 определения нечетности предназначен для выработки сигнала, служащего для сдвига мантиссы на разряд вправо и увеличения порядка на единицу при выполнении операции извлечения квадратного

корня в случае нечетного порядка оив ранда. Элемент 35 ИЛИ формирует сигнал для сдвига мантиссы на разряд вправо на регистре 33 и увеличения порядка на единицу на сумматоре 36.

Блок 3 обработки порядков содержи первый регистр 39, коммутатор 40, регистр 41, сумматор 42, узел 43 анализа переполнения, узел 44 сдвига на один разряд вправо при выполнении операции извлечения корня и преобразователь 45 прямого кода в обратный. Блок 4 нормализации содержит (сумматор 46, служащий для вычитания из порядка числа единицы при нормализации, регистр 47, сдвиговый регистр 48 для сдвига влево при нормализации мантисс результатов и дешифратор 49, служащий для сдвига мантиссы на один разряд влево и уменьшения порядка на единицу.

Каждый блок (ступень) 1 содержит регистры 50-52, комбинационный сумматор 53, узел 54 анализа переполнения комбинационного сумматора, триггер 55, коммутатор 56, выполненный на элементе И-ИЛИ и коммутатор 57, содержащий п элементов 58 И-ИЛИ (по числу разрядов регистра 51).

Устройство работает следующим образом.

Произведение двух чисел и -представленных в формате с плавающей запятой, определяется

.В МД-MlP -P где Мд и MB - мантиссы чисел; Р и рв - порядки чисел.

Мантисса первого множимого поступает по входу 6 в регистр 31 блока 2 предварительной обработки.операндов, а затем через выход 10 в регистр 51 первогоблока 1, а порядок по входу 5 в регистр 30 через преобразователь 28, а затем через выход 13 в регистр 39 блока 3 обработки порядков. Если порядок множимого отрицательный, он в преобразователе 28 преобразуется в обратный код.

Мантисса множителя заносится по входу 7 в регистр 33 блока 2, а зате через коммутатор 38 невыход 11 в регистр 52 первого - блока 1, а порядок по входу 7 в регистр 32 блока 2 чере преобразователь 29, а,затем через сумматор 36 поступает в блок 3. Если порядок множителя отрицательный, он в преобразователе 29 преобразуется в обратный код.

Обработка мантиссы производ ится в блоках 1, как при обработкеоперандов с фиксированной запятой.

Обработка порядков производите в блоке 3 следующим образом. Порядок множителя из регистра 39 через коммутатор 40 и поЕ(ЗДок множимого из регистра 41 подаются на 42. При обнаружении переполнения в сумматоре 42 узел 43 анализа переполнения вьвдает сигнал сбоя. Образовав-; шийся на сумматоре 42 порядок произ ведения передается через узел сдвига 44 и преобразователь 45 по выходу 14 на регистры 59 блокаХЗ памяти. В блоке 15, содержащем п последовательно соединенных регистров 59, значения порядков-переписываются из регистра в регистр синхронно обработке мантисс в блоках 1. В случае отрицательного знака по рядок представлен в обратном коде ив преобразователе 45 инвертируетс образуя прямой код. Из блока 15 порядок произведения передается по вы ходу 16 в блок 4 нормализации. Если нужно произвести нормализацию мантиссы в регистре 48, дешифратор нормализации 49 выдает сигнал, служа щий для сдвига мантиссы на один разряд влево. Также это.т сигнал поступает на сумматор 46, в котором произ водится вычитание единицы из порядка произведения. Полученный порядок пос тупает на выход через регистр 47. Знак произведения образуется пода чей знака мантиссы множимого из реги стра 31 и знака мантиссы множителя из регистра 33 блока 2 предварительной обработки на элемент сложения по модулю два (не показан). Знак произведения последовательно передается по регистрам и сумматорам блоков 1. Деление выполняется следующим образом С - - В М Мантисса первого дел.ителя заносится по входу 6 в регистр 31 блока 2, а порядок - по входу 5 в регистр 30через преобразователь 28. Через выход 10 мантисса первого делителя передается в первый блок 1. Мантисса первого делимого по входу 8 заносится в регистр 33, а по рядок - по входу 7 в регистр 33 через преобразователь 29. Элемент 35 ИЛИ вырабатывает управляющий сигнал с помощью которого в регистре 33 осу ществляется предварительный сдвиг мантиссы делимого вправо для предотвращения возможности переполнения. Этот же сигнал поступает на сумматор 36, в котором производится корректировка порядка. С сумматора 36 скорректированный порядок поступает по выходу 12 в регистр 41 блока 3, а мантисса с регистра 33 через коммутатор 38 по выходу 9 поступает в регистр 50 первого блока 1. Порядок делимого из регистра 41, а порядок делителя из регистра 39 через комму татор 40 подаются на сумматор 42 блока 3. Дальше порядок образуется так же, как и-при. умножении. Знак частного образуется подачей знака мантиссы делимого из perjjcTpa 31и делителя из регистра 33 блока 2 на элемент сложения по модулю два. Знак частного последовательно передается по регистра и сумматорам блоков 1. Извлечение квадратного корня выполняется следующим образом: С 7 2 Перед началом операции проверяется знак подкоренного выражения и, если он отрицательный, формируется сигнал сбоя.. . Мантисса подкоренного выражения поступает по входу 8 на регистр 33 блока 2, а порядок - по входу 7 на регистр 32 через преобразователь 29. Узел 34 анализирует знаковый млад- щий разряд порядка и в случае нечетного порядка вьщает управляющий сиг- нал, котор|Ый проходит через элемент 35 ИЛИи поступает на регистр-33, сдвигая подкоренное выражение на один разряд вправо, а также поступает на сумматор 36, в котором производится дрбавление единицы к порядку.. Дальше с регистра 33 подкоренное выражение через коммутатор 38 по выходу 9 поступает на регистр 50 первого блока, а порядок - с сумматора 36 по выходу 12 в регистр 32 блока 3. Деление по рядка на два производится;в узле 44 сдвига, который производит сдвиг на один разряд, вправо. Изобретение позволя.ет расширить функциональные возможности устройства и использовать его при обработке больших массивов многоразрядных чисел в коде с плавающей запятой. Формула изобретения 1. Арифметическое устройство по авт.св. № 703804, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет возмож ности обработки массивов чисел с плавающей запятой, оно дополнительно содержит блок предварительной обработки, блок обработки порядков,.блок памяти, коммутатор и блок нормализации, причем входы блока предварительной обработки являются входами устройства, первый, второй и третий выходы блока предварительной обработки подключены входам соответственно первого, второго и третьего р регистров первого блока устройства, четвертый и пятый выходы блока предварительной обработки-подключены соответственно к первому и второму уходам блока обработки порядков, выход которого подключен -к входу блока памяти, выходы сумматора, второго и третьего регистров последнего блока устройства соединены с информационными входами коммутатора, управляквдие входы которого соединены

с управляющими шинами умножения, извлечения корня и деления устройства, выходы блока памяти и коммутатора соединены соответственно с первым и вторым входами блока нормализации. 2. Устройство по п.1, о т л ичающеес я тем, что блок предварительной обработки содержит первый преобразователь прямого кода в обратный и первый регистр, соединенные последовательно, второй регистр, второй преобразователь прямого кода в обратный, третий регистр, узел рпре-, деления четности порядка,элемент ИЛИ сумматор, узел анализа переполнения,сдвиговый регистр, коммутатор, входы блока соединены с входами первого пре образователя прямого кода в обратный второго регистра, второго преобразователя прямого, кода в обратный и сдвиговогорегистра соответственно, выход второго преобразователя прямого кода в обратный подключен к входу третьего регистра, выходы знакового разряда и-п-го информационного разрядов которого подключены к входам узла определения четности порядка, управляющий вход которого соединен с управляющей шиной извлечения корня устройства, а выход подключен к первому входу элемента ИЛИ, второй вход которого соединен с управляющей шиной деления устройства, входы разрядов сумматора соединены с выходами разрядов третьего регистра, выход элемента ИЛИ соединен с вторым входом младшего разряда сумматора и управляющим входом сдвигового регистра, выход которого соединен с входом коммутатора, первый выход коммутатора, выход второго регистра, второй выход коммутатора, выход сумматора и выход первого регистра подключены к выходам блока, управляющие входы коммутатора соединены с управляющими шинами деления, извлечения корня и умножения устройства, выходы

знаковых разрядов сумматора подключены ко входу узла анализа переполнения.

5 шинами деления, умножения и извлечения корня устройства.

0 регистр, дешифратор и сумматор, выход которого соединен с входом регистра, выход сдвигового регистра соединен с входом дешифратора,причем первые входы сумматора и сдвигового

5 регистра соединены с входами блока, вторые их входы соединены с выход 1ми дешифратора, выходы регистров являются выходс1ми блока.

0

Источники информации, принятые во внимание при экспертизе

. 1. Авторское свидетельство СССР I 7038t)4, кд. G 06 F 7/38, 1976 (прототип).

JS

00 IT

22

ТТ

4r Фw. J

//

w

/2

/3

.-

.

t

23

2lt

26 27 t25

J/ V .

J7

i

-ng

rz

w г I

1 33 I

171 I I

..Jzqp-qzrU

g ФГГ

1Z

фи9.3

22

23

Авторы

Даты

1981-07-23—Публикация

1979-07-06—Подача