1

Изобретение относится к ускори тельной технике и может быть использовано для стабилизации ит тегрально интенсивности выведенных пучков,

При отборе ускоренных частиц из сш1хротрона в экспериментальный канал основным требованием, пред1зяяля емым к выводимому пучку, является стабильность величины выведенной ин тенсивности при равномерном потоке частиц в некотором интервале времен ut. Так как радиальное распределени плотности ускоренного пучка неоднородно и сам пучок имеет малые прост ранствеиные размеры, то к устройст ваМ, ответственным за отбор частиц, предъявляются жесткие требования

Работа выводных устройств по оп ределенной программе, учитывающей плотность распределения частиц в пучке, не решает полностью проблемы получения стабильного во времени потока частиц.

Цепью изобретения является увеличение количества выведенных частиц снижение радиационного облучения об .рудования.

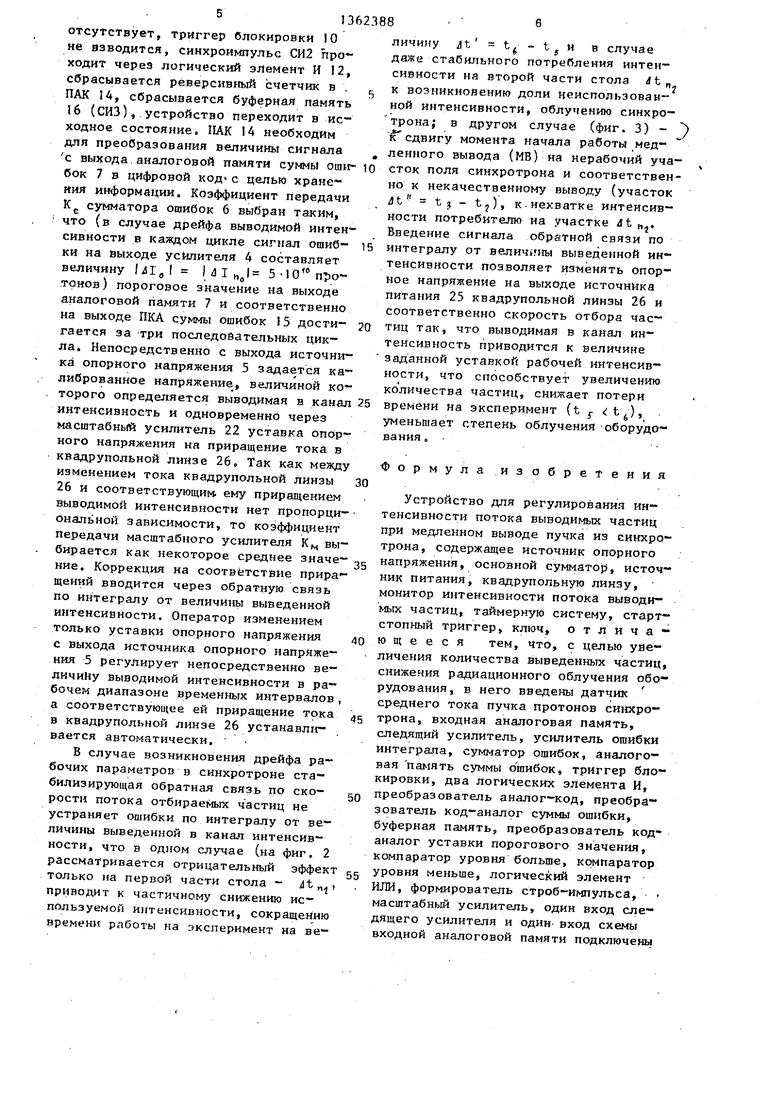

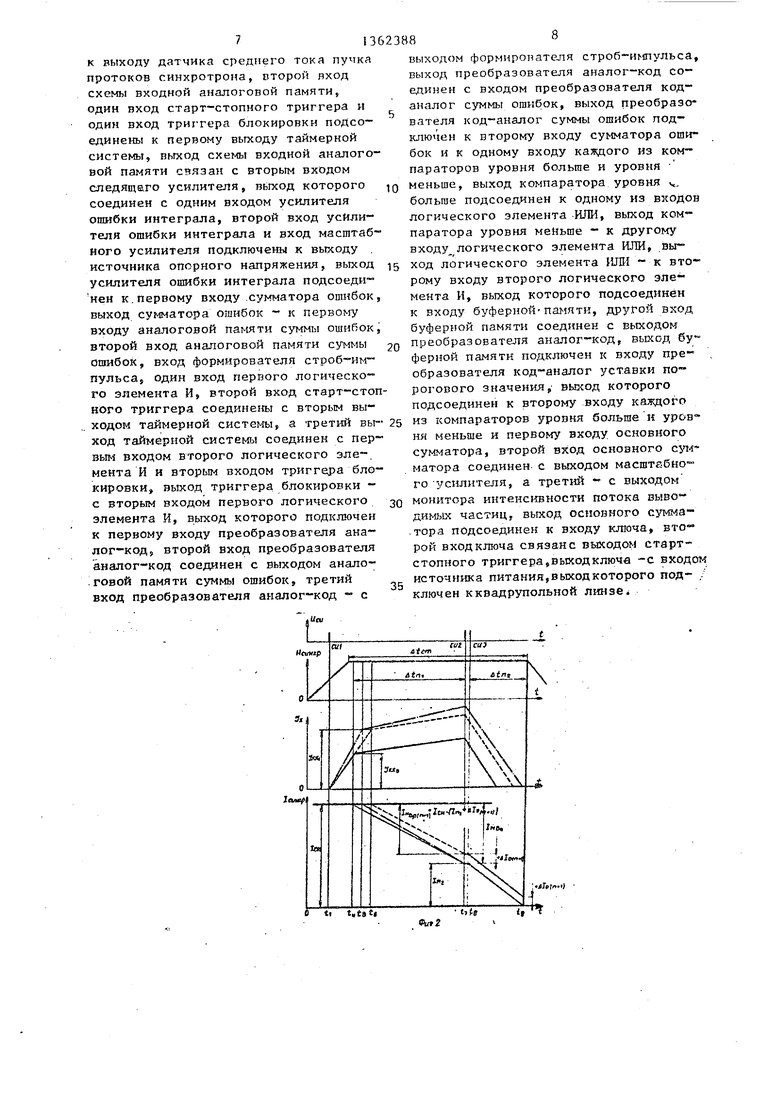

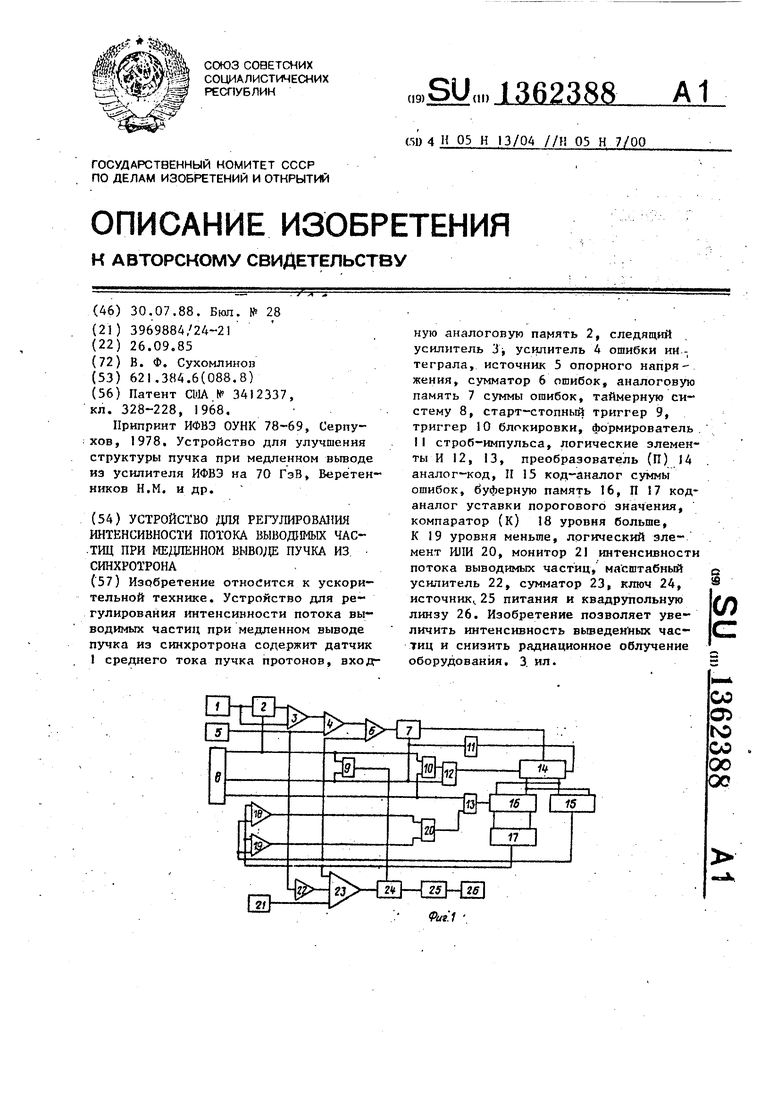

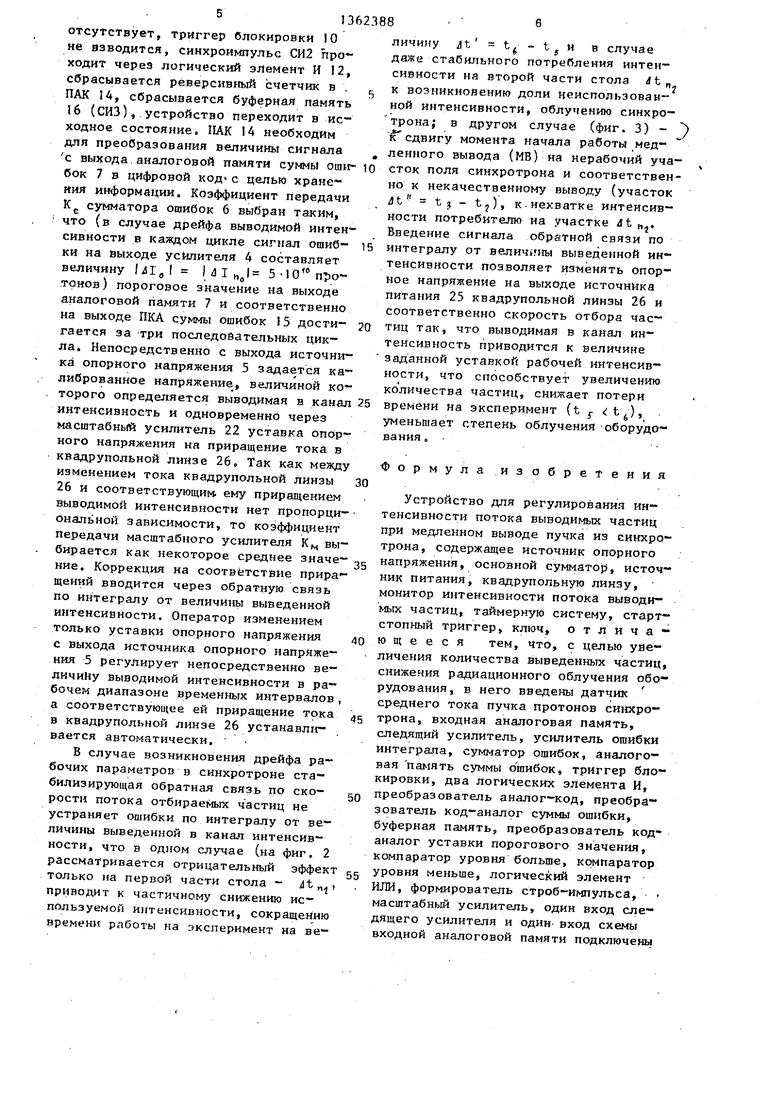

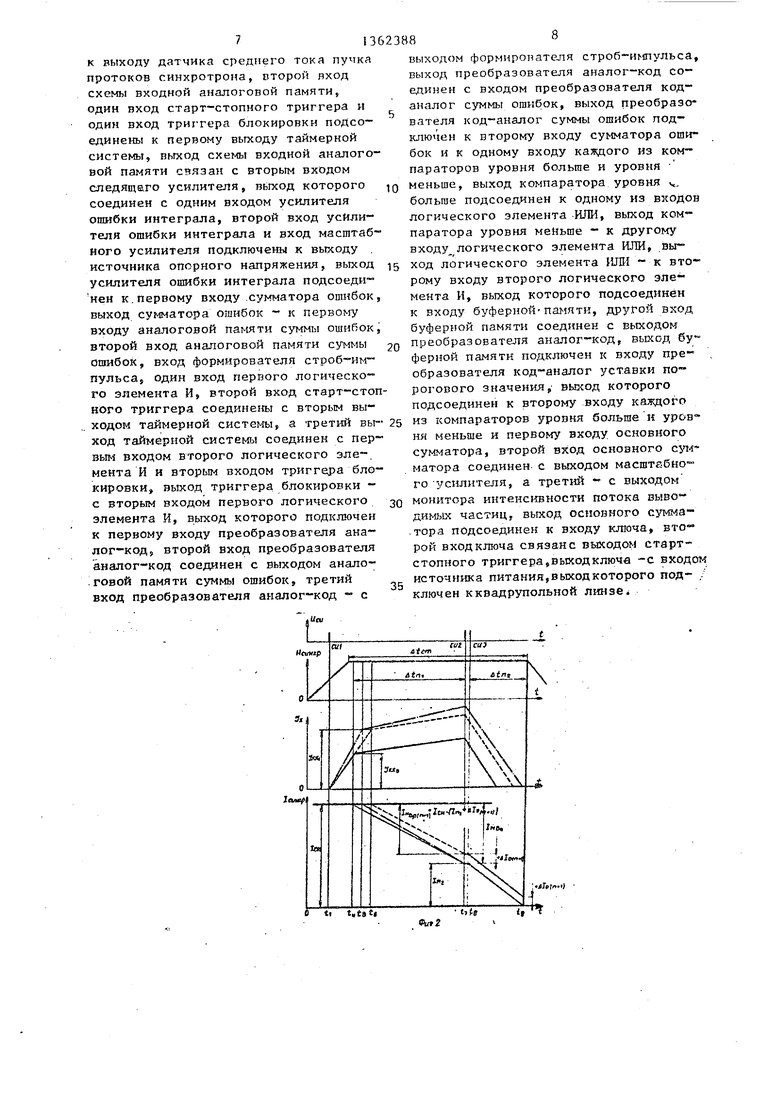

Ни фиг. 1 представлена блок-схем предлагаемого устройства; на фиг. 2 и 3 диaгpa ы, поясняюпще положи- тельный эффект, достигаемый .в резул тате введения предлагаемого устройства. .

Устройство содержит датчик среднего тока пучка протонов синхро трона, входную аналоговую память 2, которая соединена со следящим усилителем 3, выход которого соединен с входом усилителя 4 ошибки интеграла источник опорного напряжения 5, cyr-j матор ошибок 6, включенный на входе аналоговой памяти суммы ошибок 7,

таймерную систему 8, старт-стопный триггер 9, триггер блокировки Ю, формирователь строб-импульса 11 логические элементы И 12 и 13, преобразователь аналог-код (ПАК) 14,.преобразователь код-аналог (ПКА) суммы ошибок 15, буферную память 16, ПКА уставки порогового значения .17, компараторы уровня больше I8 и уровня меньше 19, логический элемент ИЛИ 20, монитор 21 интенсивности потока выводимых частиц, масштабный усилитель 22, соединенный с основным сумматором 23, на выходе которого расположен ключ 2А, источник питания 25, квадру- польную линзу 26, последовательно

Г

0 | й1

0

5

соедииемную с источником питания 25 и ключом 24„

Устройство работает следующим о,б разом.

В момент, определяемый синхроимпульсом (си) (момент t, , фиг. 2 и 3), с выхода таймерной системы 8 до начала вывода частиц в канал сигнал начальной интенсивности в ускорителе с выхода датчика .в виде сигнала напряжения запоминается во входной аналоговой памяти 2, вводится триггер блокировки lOj, взводится старт-стопный триггер 9, замыкается ключ 24, Опорное напряжение с выхода источника опорного напряжения 5 через масштабный усилитель 22, основной сумма- тор 23 и ключ 24 поступает на вход источника питания 25 и определяет начальную скорость нарастания тока 1 в квадрупольной линзе 26 (начальный участок I , f{t) от момента

А,

стёрта ti до момента t4 сплотная ли ния, фиг, 2 и 3), С момента появления частиц в канапе (момент t ХУ VXTI) скорость нарастания тока квадруполь- ной линзы определяется разностью на- пряжения с выхода масштабного уси.гш- теля 22 и напряжения сигнала с выхода монитора обратной саязи 21, С приходом синхроимпульса СИ2 с выхода таймерной системы 8 сигнал ошибки

I с выхода усилителя 4 ошибки интеграла проходит через сумматор оши- , бок 6 с коэффициентом передачи К в аналоговой памяти суммы ошибок 7 за поминается величина I, сбрасыва ется старт-стопный триггер 9, размыкается ключ 24, отбор частиц в канал прекращается. Далее управляюпи1м г.троб-импульсом с выхода формирова теля П величина К,|Лр I преобразуется в ПАК 14 в цифровой код, обратно 5 преобразуется в аналоговую величину Кц |л1р f на выходе ПКА суммы ошибок 15 и поступает на второй вход сумматора ошибок 6 и на один вход каяэдого из компараторов уровня больше 18 и уровня меньше 19, Если величина К UIд i на выходе ПКА суммы ошибок 15 меньше величины порогового значения |Л1„ 1,-т.е. Kj4I,U М1п„1 О в следующем цикле по логическому, состо- янию компараторов уровня больше 18 и уровня меньше 19 с выхода логического элемента ИЛИ 20 поступает запрет на прохождение синхроимпульса СИЗ с выхода таймерной системы 8 через ло5

0

0

5

гический элемент 13 на управляющий вход буфер)ной памяти 16. С выхода ИКЛ уставки порогового значения 1 7

исходная величина IЛ сохраняется, ляется сигналом, корректирую1цим скорость изменения тока квадрупольной линзы 26. Тогда к началу {п+2)-го цикла (СИ1) уставка на выходе основ™ ного с умматора 23 1св() ; ТдДЛЯ случая на фиг, 2 или

релейный регулятор не включается, от цикла к циклу значение уставки на вы ходе основного сумматора 23 определя ется 1 j I мвв К„. Если за п по- следовательных циклов сумма ошибок в- 10 аналоговой памяти 7 равна нулю или

К,1

nt I

к..- к. 5Z aio для

меньше

(41-1 , т.е. Kj 4lJ

(п.1 ) мв

к..- к. 5Z aio для

м

ы

iil

(dln, ТО регулятор работает как и в предыдущем случае. Если вызванное дрейфом параметров синхротрона на (п+1)-м цикле изменяется радиальное положение пучка, то при неизменной уставке опорного напряжения на входе источника питания 25 квадрупольной линзы 26 максимальный начальный ток Iххв достигает значений

I VV I

15

случая на фиг. 3. В результате в (п+2)-м цикле смещается момент начала

20

появления пучка в канале (штрих-пунктирная линия, момент tj на фиг. 2 или t3 на фиг 3), изменяется интенсивность потока выводимых частиц, но поток частиц в канале остается равномерным, величина сигнала ошибки с выхода усилителя А уменьшается l4Ij,j,(j| , „ -г) I/ ) Тогда выведенная в канал

интенсивность 1д,вр(). сн - (г

и о . ок Ifl ) случа я иа фиг 2 стабилизирующей обратной связи по

тенсивности потока выводимых частиц с монитора 2 i, к недопустимому сдвигу момента начала отбора частиц, появлению частицы неиспользованной интенсивности, облучению оборудования 30

I xXj УХо

Это приводит, при достаточно хорошей

И 1л,вр( си

- (Iij - lo(n-fj; ) для случая на фиг. 3 приближается к

величине, заданной уставкой интенсив ности выхода источника опорного напряжения 5. Если к концу (п+2)-го

цикла величина суммы ошибок К.151 л1

(момент t, /II о - 11о() штриховая линия, фиг. 2) или сдвигу начала работы медленного вывода на нерабочую (нарастающую) часть поля синхро-

цикла величина суммы ошибок К.151 л1

с выхода ПКА суммы ошибок 15 больше

величины суммы ошибок вы

трона и нехватке интен сивности следу 35 хода ПКА уставки порогового значения ющему потребителю (момент tj ai, , „ предыдущего цикла на величину

- -lo(n-n) штриховая линия, фиг. 3),

тогда сумма ошибок в аналоговой памя t т.е. о ти выходе ПКА суммы ошибок 15 hisj, то,в сл едующем циклГ устройКс| -llol 141„ I , а интенсив- ство работает как и в предыдущем. В in. . результате происходит очередной шаг

ность, выведенная в канал медленного приближения. Если ка е-м шаге приб хлижения К J2l 41с| - K.lH 4 IB I

in . i45 Bluing} t TO уставка : опорного напряжения иа выходе основного суммато ра 23 сохраняется и в следующем циквывода, 1м8р(|1.г сп - (I пг + Io() фиг. 2) или 1мвр п 157 ICK- dnj- ) (фиг. 3). В результате изменяется логическое состояине с

выхода компаратора уровня больше 18

(или уровня меньше 19), и с выхода

логического элемеита ИЛИ 20 .поступа-

ет разрешение на прохождение сиихро- 50

импульса СИЗ от таймерной системы 8

через логический элемеит И 13 иа уп

равляющий вход буферной памяти 16.

Запомиенньй в буферной памяти 16 и

преобразованньм,в аналоговую величи- 55 гул ятор бтключается. Триггер блоки IkM + l к - IMB, . k-f

+ К XI -dlo а интенсивиость, выве ч. .

денная в канал, определяется с точностью до величины 1мвр 1с«- ± ° Релейньй рену сигнал К I z Л1 д с выхода ПКА i уставки порогового значения 17 поступает иа п ервый вход основного сумма-

.ровки 10 каждый раз в конце цикла сбрасывается СИЗ. Когда вывода частиц в канале нет, стартовый импульс СИ1

тора 23 и на второй вход каждого и. компараторов уровня больше 18 и уровня меньше 19 и в следующем цикле яв

ляется сигналом, корректирую1цим скорость изменения тока квадрупольной линзы 26. Тогда к началу {п+2)-го цикла (СИ1) уставка на выходе основ™ ного с умматора 23 1св() ; ТдДЛЯ случая на фиг, 2 или

К,1

(п.1 ) мв

nt I

к..- к. 5Z aio для

м

iil

5

случая на фиг. 3. В результате в (п+2)-м цикле смещается момент начала

появления пучка в канале (штрих-пунктирная линия, момент tj на фиг. 2 или t3 на фиг 3), изменяется интенсивность потока выводимых частиц, но поток частиц в канале остается равномерным, величина сигнала ошибки с выхода усилителя А уменьшается l4Ij,j,(j| ) Тогда выведенная в канал

20

Ifl ) случа я иа фиг 2

И 1л,вр( си

- (Iij - lo(n-fj; ) для случая на фиг. 3 приближается к

величине, заданной уставкой интенсив ности выхода источника опорного напряжения 5. Если к концу (п+2)-го

цикла величина суммы ошибок К.151 л1

с выхода ПКА суммы ошибок 15 больше

гул ятор бтключается. Триггер блоки IkM + l к - IMB, . k-f

+ К XI -dlo а интенсивиость, выве ч. .

денная в канал, определяется с точностью до величины 1мвр 1с«- ± ° Релейньй ре.ровки 10 каждый раз в конце цикла сбрасывается СИЗ. Когда вывода частиц в канале нет, стартовый импульс СИ1

5136

отсутствует, триггер блокировки 10 не взводится, синхрои {пульс СИ2 про ходит через логический элемент И 12, сбрасывается реверсивный счетчик в . ПАК 14, сбрасывается буферная память 16 (сиз), устройство переходит в исходное состояние. IIAK 14 необходим для преобразования величины сигнала

с выхода.аналоговой памяти суммы оши- ю сток поля синхротрона и соответственбок 7 в цифровой КОД с целью хранения информации. Коэффициент передачи Kj. сумматора ошибок 6 выбран таким, что (в случае дрейфа выводимой интенсивности в каждом цикле сигнал ошибки на выходе ус шитепя 4 составляет величину Ulgl )/3IrtJ 5-lO протонов) пороговое значение на выходе аналоговой памяти 7 и соответственно на выходе ПКА ошибок 15 достигается за три последовательных цикла. Непосредственно с выхода источника опорного напряжения 5 задается калиброванное напряжение, величиной которого определяется выводимая в канал 25 времени на эксперимент (t j- ;t),

интенсивность и одновременно через масштабньйй усилитель 22 уставка опорного напряжения на приращение тока в квадрупольной линзе 26. Так как между изменением тока квадрупольной линзы 30 26 и соответствующим, ему приращением выводимой интенсивности нет пропорци- ональной зависимости, то коэффициент передачи масштабного усилителя К выбирается как некоторое среднее значе- од ние. Коррекция на соответствие прира - щений вводится через обратную связь по интегралу от величины выведенной интенсивности. Оператор изменением только уставки опорного напряжения с выхода источника опорного напряжения 5 регулирует непосредственно величину выводимой интенсивности в рабочем диапазоне временных интервалов , а соответствующее ей приращение тока в квадрупольной линзе 26 устанавливается автоматически.

В случае возникновения дрейфа рабочих параметров в синхротроне стабилизирующая обратная связь по скорости потока отбираемых частиц не устраняет ошибки по интегралу от величины выведенной в канал интенсивности, что в одном случае (на фиг. 2

уменьшает степень облучения оборуд вания.

Формула изобретени

Устройство для регулирования ин тенсивности потока выводимых части при медленном выводе пучка из синх трона, содержащее источник опорног напряжения, основной сумматор, ист ник питания, квадрупольную линзу, монитор интенсивности потока вывод мых частиц, таймерную систему, ста стопный триггер, ключ, о т л и ч 40 ю щ е е с я тем, что, с целью ув личения количества выведенных част снижения радиационного облучения о рудования, в него введены датчик среднего тока пучка протонов синхр трона, входная аналоговая память, следящий усилитель, усилитель ошиб интеграла, сумматор ошибок, аналог вая память суммы ошибок, триггер б кировки, два логических элемента И преобразователь аналог-код, преобр зователь код-аналог суммы ошибки, буферная память, преобразователь к аналог уставки порогового значения компаратор уровня больше, компарат

45

50

рассматривается отрицателышй эффект gg уровня меньше, логический элемент

только на первой части стола Jt

Г

приводит к частичному снижению используемой интенсивности, сокращен ию времени работы на эксперимент на веИЛИ, формирователь строб-импульса, масштабньй усилитель, один вход сл дящего усилителя и один- вход схемы входной аналоговой памяти подключе

6

личину Jt t - tj н в случае даже стабильного потребления интенсивности на второй части стола пу к возникновению доли неиспользованной интенсивности, облучению синхротрона, в другом случае (фиг. 3) - ) к сдвигу момента начала работы медленного вывода (МВ) на нерабочий учано к некачественному выводу (участок it t ) - tj), K. нехватке интенсивности потребителю на участке at (,j. Введение сигнала обратной связи по

интегралу от величины выведенной интенсивности позволяет изменять опорное напряжение на выходе источника питания 25 квадрупольной линзы 26 и соответственно скорость отбора час-

тиц так, что выводимая в канал интенсивность приводится к величине заданной уставкой рабочей интенсив- кости, что способствует увеличению количества частиц, снижает потери

0 д

уменьшает степень облучения оборудо вания.

Формула изобретения

Устройство для регулирования интенсивности потока выводимых частиц при медленном выводе пучка из синхротрона, содержащее источник опорного напряжения, основной сумматор, источник питания, квадрупольную линзу, монитор интенсивности потока выводимых частиц, таймерную систему, старт- стопный триггер, ключ, о т л и ч а - 0 ю щ е е с я тем, что, с целью увеличения количества выведенных частиц, снижения радиационного облучения обо рудования, в него введены датчик среднего тока пучка протонов синхротрона, входная аналоговая память, следящий усилитель, усилитель ошибки интеграла, сумматор ошибок, аналоговая память суммы ошибок, триггер блокировки, два логических элемента И, преобразователь аналог-код, преобразователь код-аналог суммы ошибки, буферная память, преобразователь код- аналог уставки порогового значения, компаратор уровня больше, компаратор

5

0

уровня меньше, логический элемент

ИЛИ, формирователь строб-импульса, масштабньй усилитель, один вход следящего усилителя и один- вход схемы входной аналоговой памяти подключены

к выходу датчика среднего тока пучка протоков синхротрона, второй вход схемы входной аналоговой памяти, один вход старт-стопного триггера и один вход триггера блокировки подсоединены к первому выходу таймерной системы, выход cxer-tbi входной аналоговой памяти связан с вторым входом следящего усилителя, выход которого соединен с одним входом усилителя ошибки интеграла, второй вход усилителя ошибки интеграла и вход масштабного усилителя подключены к выходу . источника опорного напряжения, выход усилителя ошибки интеграла подсоеди- нен к.первому входу .сумматора ошибок, выход сумматора ошибок к nepBONry входу аналоговой суммы ошибок, второй вход аналоговой памяти суммы ошибок, вход формирователя строб-им пульса, один вход первого логическо™ го элемента И, второй вход старт-стопного триггера соединегш с вторым вы5

10

выходом формирователя строб-импульса выход преобразователя аналог-код соединен с входом преобразователя код- аналог суммы ошибок, выход преобразо вателя код-аналог суммы ошибок подключен к второму входу сумматора ошибок и к одному входу каждого из компараторов уровня больше и уровня меньше, выход компаратора уровня ч, больше подсоединен к одному из входов логического элемента ИЛИ, выход компаратора уровня меньше - к другому входу логического элемента ИЛИ, 1зы- ход логического элемента ИЛИ к вто рому входу второго логического эле мента И, выход которого подсоединен к входу буферной-памяти, другой вход буферной памяти соединен с выходом преобразователя аналог-код, выход буферной памяти подключен к входу пре образователя код-аналог уставки по рогового значения, выход которого подсоединен к второму входу каждого

15

20

ходом таймерной системы, а третий вы- 25 з компараторов уровня больше к уров°

ход таймерной системы соединен с первым входом второго логического эле-. мента И и вторым входом триггера блокировки, выход триггера блокировки - с вторым входом первого логического элемента И, выход которого подключен к первому входу преобразователя аналог-код, второй вход преобразователя аналог-код соединен с выходом анало- говой памяти суммы ошибок третий вход преобразователя аналог-код - с

5

10

623888

выходом формирователя строб-импульса, выход преобразователя аналог-код соединен с входом преобразователя код- аналог суммы ошибок, выход преобразо вателя код-аналог суммы ошибок подключен к второму входу сумматора ошибок и к одному входу каждого из компараторов уровня больше и уровня меньше, выход компаратора уровня ч, больше подсоединен к одному из входов логического элемента ИЛИ, выход компаратора уровня меньше - к другому входу логического элемента ИЛИ, 1зы- ход логического элемента ИЛИ к вто рому входу второго логического эле мента И, выход которого подсоединен к входу буферной-памяти, другой вход буферной памяти соединен с выходом преобразователя аналог-код, выход буферной памяти подключен к входу пре образователя код-аналог уставки по рогового значения, выход которого подсоединен к второму входу каждого

15

20

ня меньше и первому входу основного сумматора, второй вход основного сумматора соединен- с выходом масштйбно- го -усилителя, а третий - с выходом монитора интенсивности потока выво димых частиц, выход основного сумма- тора подсоединен к входу ключа второй вход ключа связано выходом старт- стопного триггера,выходключа с входом источника питания,выход которого под- / ключен кквадрупольной линзе

iUeu

1а«у

О ti t,

.)

it/CAf

Нсинхр

Ici/MXp

, tiigtyttf

Фи9.3

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛАЗЕРНЫЙ ИМПУЛЬСНЫЙ ДАЛЬНОМЕР | 2014 |

|

RU2551700C1 |

| Система автоматического управления циклическими процессами | 1983 |

|

SU1124247A1 |

| Способ регулирования интенсивности пучка в циклическом ускорителе заряженных частиц | 1982 |

|

SU1072784A1 |

| Устройство для определения дефектов в прозрачных полимерных пленках | 1986 |

|

SU1385038A1 |

| Устройство для определения поперечной координаты центра тяжести сгруппированного пучка заряженных частиц | 1986 |

|

SU1457179A1 |

| Устройство для акустического каротажа скважин | 1982 |

|

SU1040447A1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Способ синхронизации устройств в накопительных электронных синхротронах источников синхротронного излучения | 2018 |

|

RU2689297C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД | 1972 |

|

SU433634A1 |

Изобретение относится к ускорительной технике. Устройство для регулирования интенсивности потока выводимых частиц при медленном выводе пучка из синхротрона содержит датчик 1 среднего тока пучка протонов, входную аналоговую память 2, следящий усилитель S, усилитель 4 ошибки ин.- теграла, источник 5 опорного напряжения, сумматор 6 ошибок, аналоговую память 7 суммы ошибок, таймерную систему 8, старт-стопный триггер 9, триггер 10 блокировки, формирователь. II строб-импульса, логические элементы И 12, 13, преобразоват€ ль (П) 14 аналог-код, П 15 код-аналог суммы ошибок, буферную память 16, П 17 код- аналог уставки порогового значения, компаратор (К) 18 уровня больше, К 19 уровня меньше, логический зле- мент ИЛИ 20, монитор 21 интенсивности потока выводимых частиц, иа сштабный усилитель 22, сумматор 23, ключ 24, источник 25 питания и квадрупольную линзу 26, Изобретение позволяет увеличить интенсивность вьгоеден ных частиц и снизить радиационное облучение оборудования, 3. ил. с S (Л со СП) tsD СО . 00 00

Составитель Н. Катиновз Редактор Т. Иванова Техред И.Дидык Корректор М. Пожо

.-.. л -J.г-тг-ш11 л1Г1 щ лл1

Заказ 3846Тираж 832 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,

| Патент CDJA № 3412337, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| и др, | |||

Авторы

Даты

1988-07-30—Публикация

1985-09-26—Подача