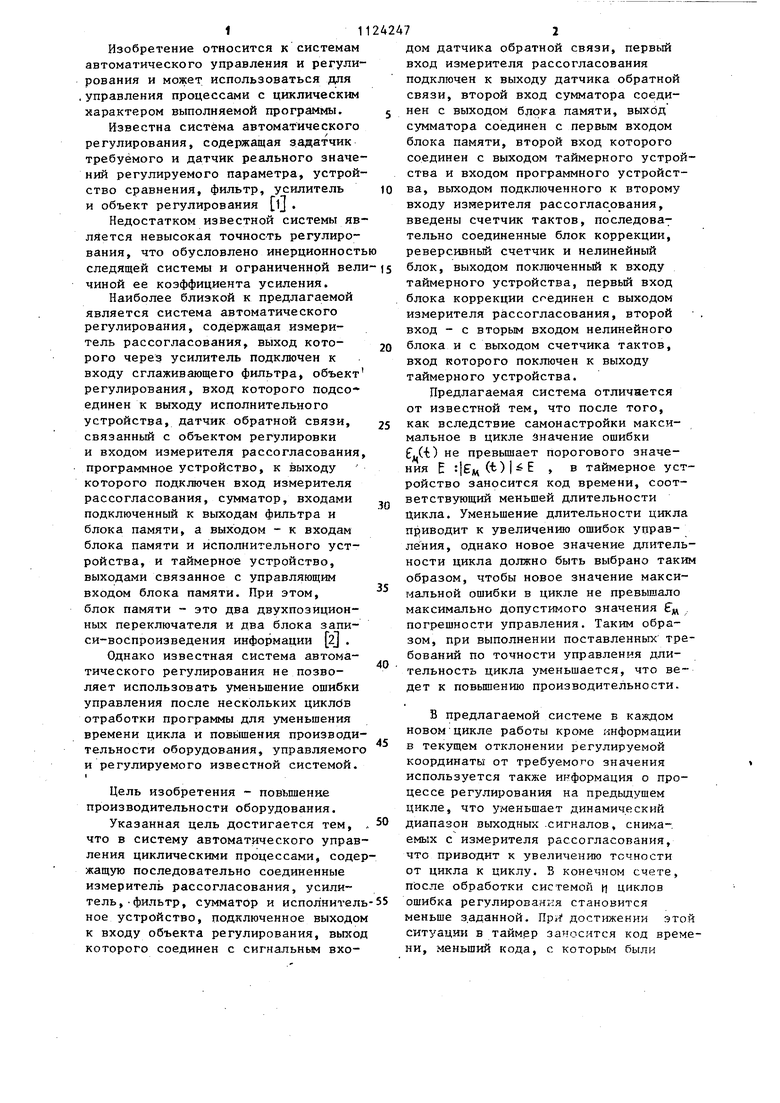

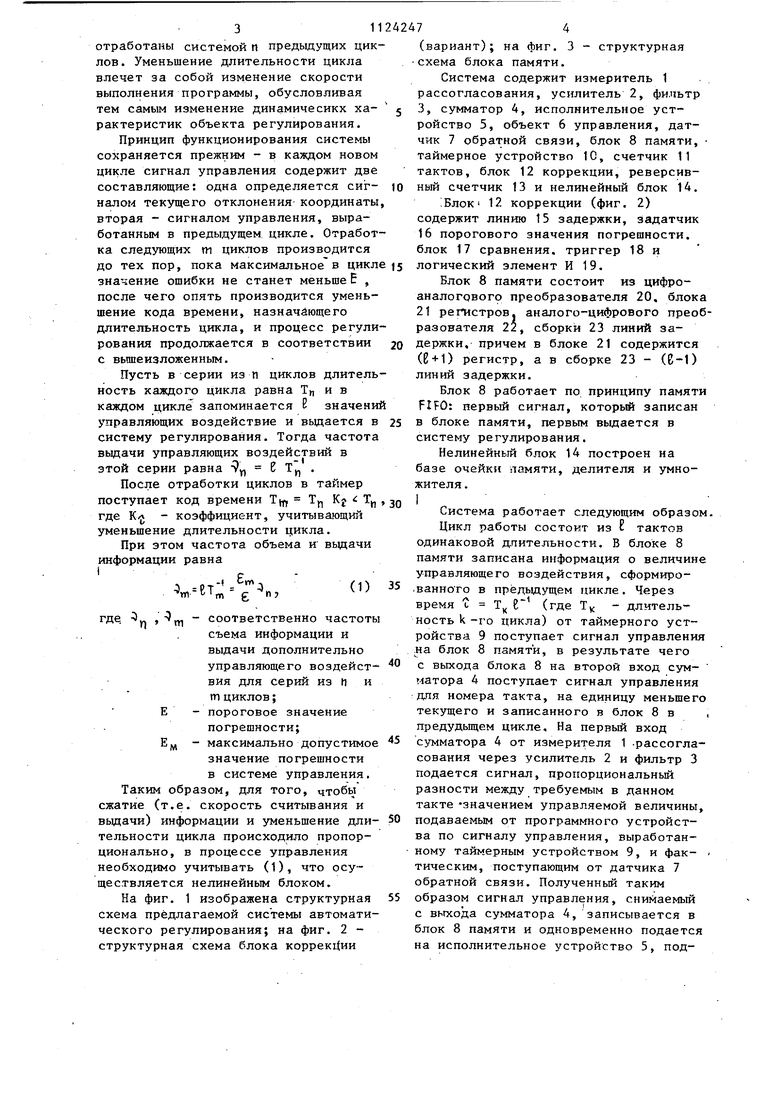

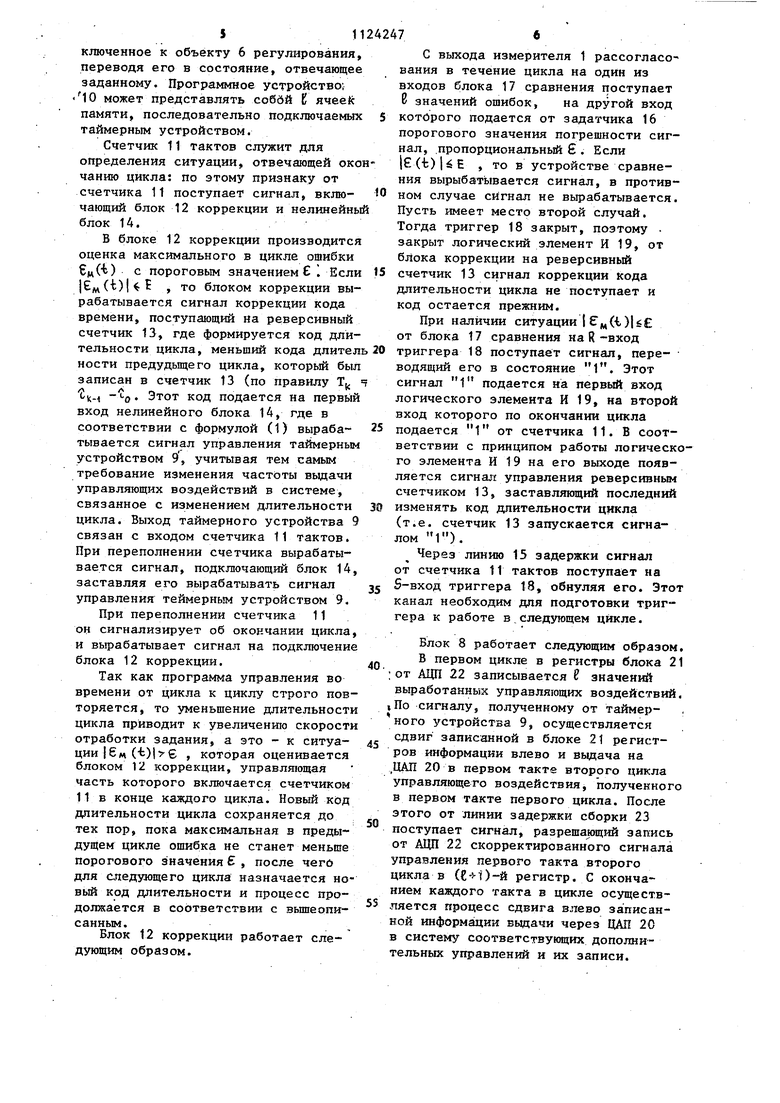

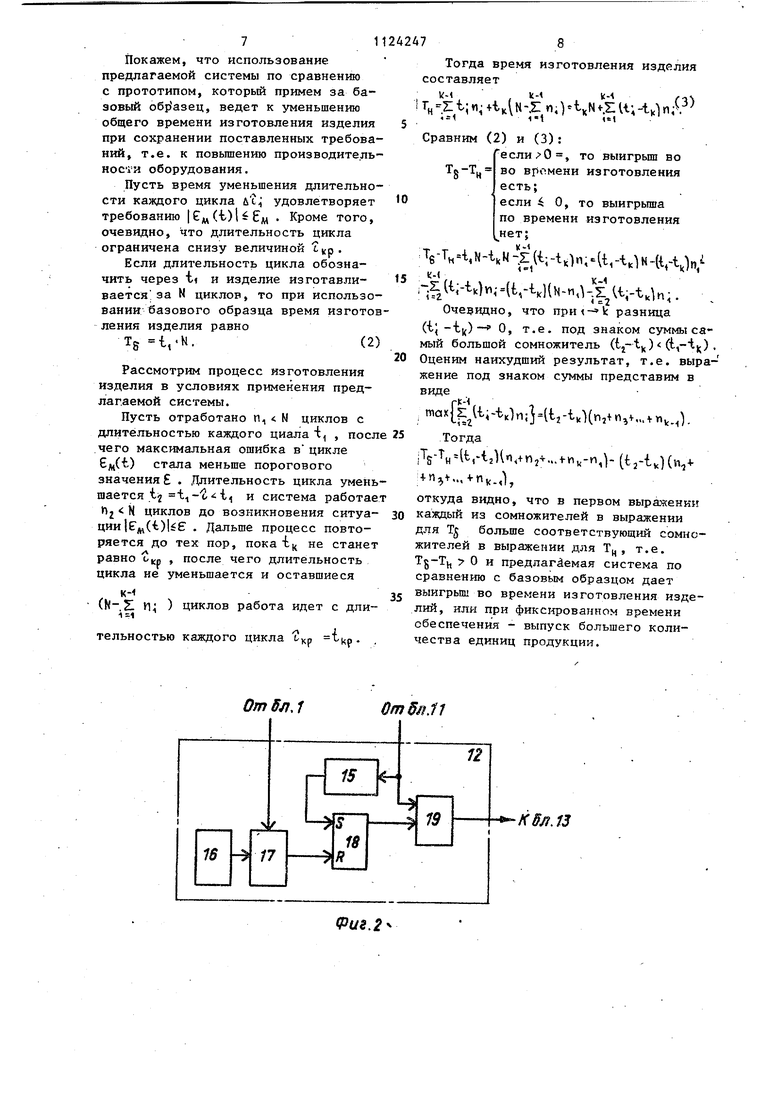

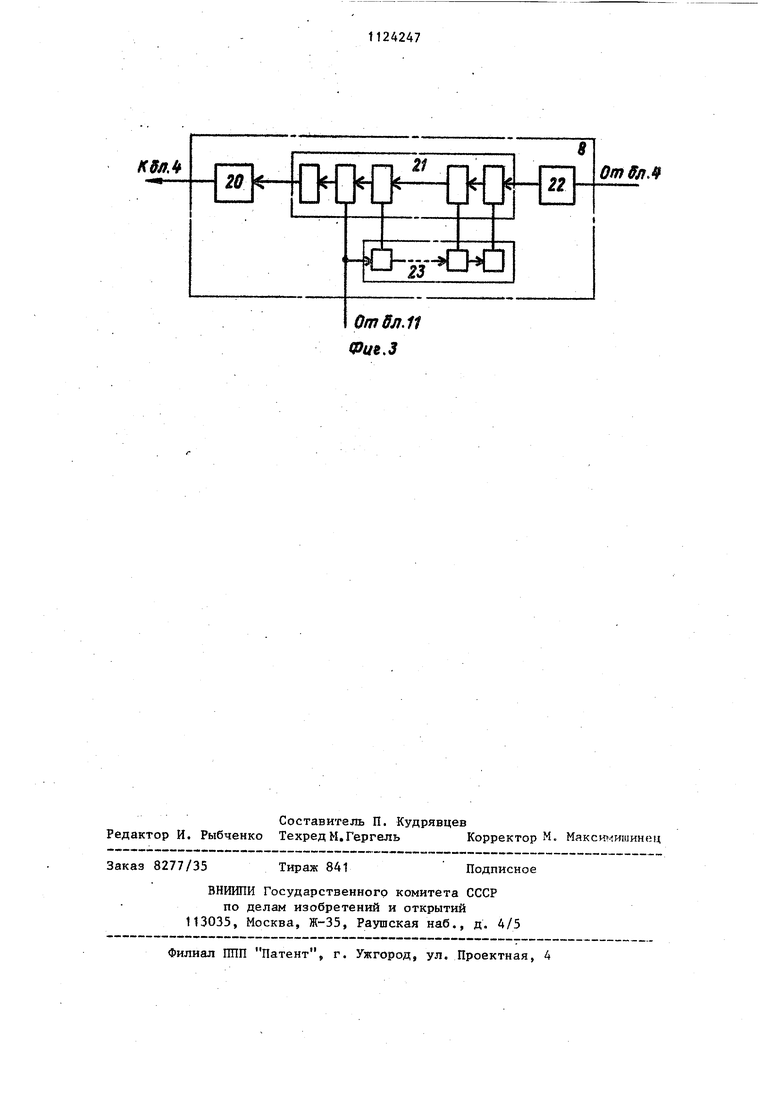

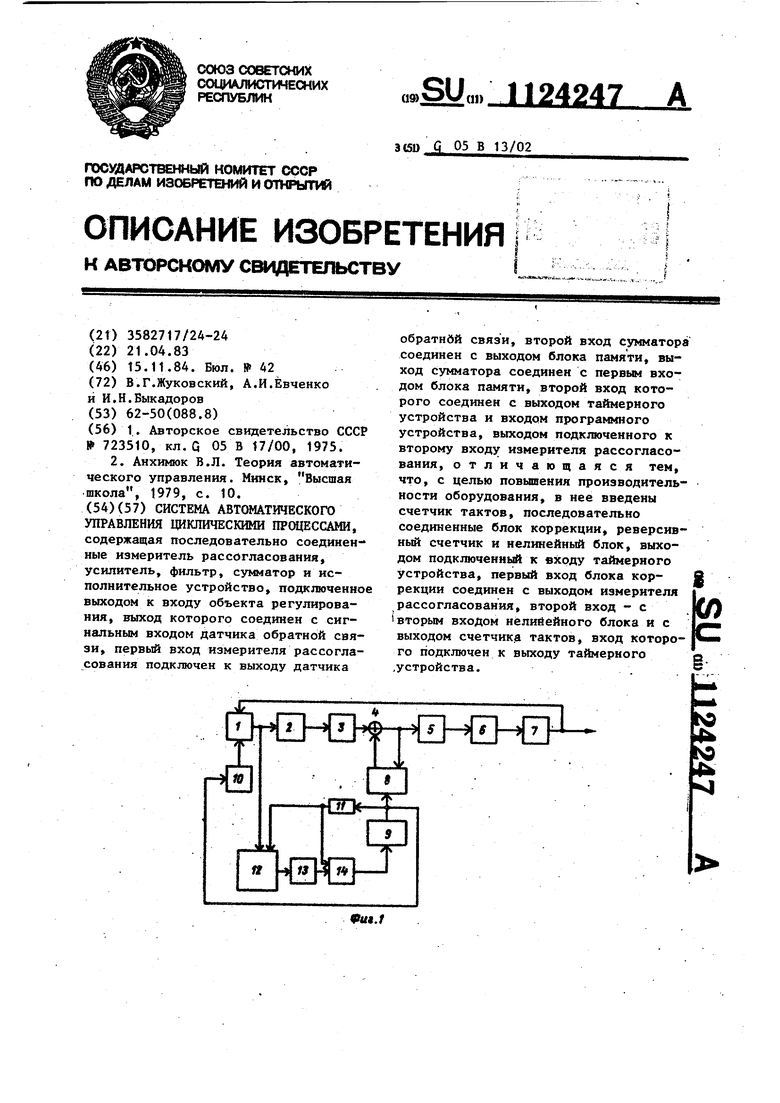

Изобретение относится к системам автоматического управления и регули рования и может использоваться для .управления процессами с циклическим характером выполняемой программы. Известна система автоматического регулирования, содержащая задатчик требуемого и датчик реального значе ний регулируемого параметра, устрой ство сравнения, фильтр, усилитель и объект регулирования lj . Недостатком известной системы яв ляется невысокая точность регулирования, что обусловлено инерционност следящей системы и ограниченной вел чиной ее коэффициента усиления. Наиболее близкой к предлагаемой является система автоматического регулирования, содержащая измеритель рассогласования, выход которого через усилитель подключен к входу сглаживающего фильтра, объект регулирования, вход которого подсоединен к выходу исполнительного устройства, датчик обратной связи, связанный с объектом регулировки и входом измерителя рассогласования программное устройство, к выходу которого подключен вход измерителя рассогласования, сумматор, входами подключенный к выходам фильтра и блока памяти, а выходом - к входам блока памяти и исполнительного устройства, и таймерное устройство, выходами связанное с управляющим входом блока памяти. При этом, блок памяти - это два двухпозиционных переключателя и два блока записи-воспроизведения информации 2j . Однако известная система автоматического регулирования не позволяет использовать уменьшение ошибки управления после нескольких циклов отработки программы для уменьшения времени цикла и повышения производи тельности оборудования, управляемог и регулируемого известной системой. Цель изобретения - повъш1ение производительности оборудования. Указанная цель достигается тем, что в систему автоматического управ ления циклическими процессами, соде жащую последовательно соединенные измеритель рассогласования, усилитель, -фильтр, сумматор и исполнител ное устройство, подключенное выходо к входу объекта регулирования, вьпсо которого соединен с сигнальным входом датчика обратной связи, первый вход измерителя рассогласования подключен к выходу датчика обратной связи, второй вход сумматора соединен с выходом блока памяти, выход сумматора соединен с первым входом блока памяти, второй вход которого соединен с выходом таймерного устройства и входом программного устройства, выходом подключенного к второму входу измерителя рассогласования, введены счетчик тактов, последовательно соединенные блок коррекции, реверсивньй счетчик и нелинейный блок, выходом поключенный к входу таймерного устройства, первый вход блока коррекции соединен с выходом измерителя рассогласования, второй вход - с вторым входом нелинейного блока и с выходом счетчика тактов, вход которого поключен к выходу таймерного устройства. Предлагаемая система отличается от известной тем, что после того, как вследствие самонастройки максимальное в цикле значение ошибки f.-Ct) не превьш1ает порогового значения Б таймерное устройство заносится код времени, соответствующий меньшей длительности цикла. Уменьшение длительности цикла приводит к увеличению ошибок управлёния, однако новое значение длительности цикла должно быть выбрано таким образом, чтобы новое значение максимальной ошибки в цикле не превышало максимально допустимого значения в погрешности управления. Таким образом, при выполнении поставленных требований по точности управления длительность цикла уменьшается, что ведет к повьшению производительности. В предлагаемой системе в каждом новомцикле работы кроме информации в текущем отклонении регулируемой координаты от требуемого значения используется также информация о процессе регулирования на предьщушем цикле, что уменьшает динамический диапазон выходных .сигналов, снимаемых с измерителя рассогласования, что приводит к увеличению тсчности от цикла к циклу. В конечном счете, после обработки системой ц циклов ошибка регулирования становится меньше заданной. При достижении этой ситуации в таймрр заносится код времени, меньший кода, с которым были отработаны системой n предыдущих цик лов. Уменьшение длительности цикла влечет за собой изменение скорости выполнения программы, обусловливая тем самым изменение динамичесикх характеристик объекта регулирования. Принцип функционирования системы сохраняется прежним - в казкдом новом цикле сигнал управления содержит две составляющие: одна определяется сигналом текущего отклонения координаты вторая - сигналом управления, выработанным в предыдущем цикле. Отработ ка следующих т циклов производится до тех пор, пока максимальное в цикл значение ошибки не станет меньше В , после чего опять производится уменьшение кода времени, назначающего длительность цикла, и процесс регули рования продолжается в соответствии с вьшеизложенным. Пусть в серии из n циклов длитель ность каждого цикла равна Тп и в каждом цикле запоминается Е значени управляющих воздействие и вьщается в систему регулирования. Тогда частота выдачи управляющих воздействий в этой серии равна 9, 6 Т . После отработки циклов в таймер Tj поступает код времени Т( Т где Kvj - коэффициент, учитывающш уменьшение длительности цикла. При этом частота объема и вьщачи информации равна .-( w , m ,т соответственно частот съема информации и выдачи дополнительно управляющего воздейст ВИЯ для серий из h и m циклов; Е - пороговое значение погрешности; Е - максимально допустимо значение погрешности в системе управления. Таким образом, для того, чтобы сжатие (т.е. скорость считывания и вьщачи) информации и уменьшение дли тельности цикла происходило пропорционально, в процессе управления необходимо учитывать (1), что осуществляется нелинейным блоком. На фиг. 1 изображена структурная схема предлагаемой системы автомати ческого регулирования; на фиг. 2 структурная схема блока коррекг ии (1) (вариант); на фиг. 3 - структурная схема блока памяти. Система содержит измеритель 1 рассогласования, усилитель 2, фи.чьтр 3, сумматор 4, исполнительное устройство 5, объект 6 управления, датчик 7 обратной связи, блок 8 памяти, таймерное устройство 1C, счетчик 11 тактов, блок 12 коррекции, реверсивНВ1Й счетчик 13 и нелинейный блок 14. :БЛОК 12 коррекции (фиг. 2) содержит линию 15 задержки, задатчик 16 порогового значения погрешности, блок 17 сравнения, триггер 18 и логический элемент И 19. Блок 8 памяти состоит из цифроаналогового преобразователя 20, блока 21 регистров, аналого-цифрового преобразователя 22, сборки 23 линий задержки, причем в блоке 21 содержится (E+l) регистр, а в сборке 23 - (В-1) линий задержки. Блок 8 работает по принципу памяти FIFO: первый сигнал, который записан в блоке памяти, первым выдается в систему регулирования. Нелинейный блок 14 построен на базе очейки памяти, делителя и умножителя. Система работает следующим образом. Цикл работы состоит из Е тактов одинаковой Д-пительности. В блоке 8 памяти записана информация о величине управляющего воздействия, сформиро.ванното в предыдущем цикле. Через время t Т (где Ту; - длительность k-го цикла) от таймерного устройства 9 поступает сигнал управления .на блок 8 памяти, в результате чего с выхода блока 8 на второй вход сум- матора 4 поступает сигнал управления для номера такта, на единицу меньшего текущего и записанного в блок 8 в , предудьш;ем цикле. На первый вход сумматора 4 от измерителя 1 -рассогласования через усилитель 2 и фильтр 3 подается сигнал, пропорциональный разности между требуемым в данном такте -значением управляемой величины, подаваемым от программного устройства по сигналу управления, выработанному таймерным устройством 9, и фак- тическим, поступающим от датчика 7 обратной связи. Полученный таким образом сигнал управления, снимаемый с выхода сумматора 4, записывается в блок 8 памяти и одновременно подается на исполнительное устройство 5, подS11ключенное к объекту 6 регулирования, переводя его в состояние, отвечающее заданному. Программное устройство; 10 может представлять собдй К ячеёй памяти, последовательно подключаемых таймерным устройством. Счетчик 11 тактов служит для определения ситуации, отвечающей око чанию цикла: по этому признаку от счетчика 11 поступает сигнал, включающий блок 12 коррекции и нелинейны блок 14. В блоке 12 коррекции производится оценка максимального в цикле ошибки SuC-t) с пороговым значением € I Если ()1 то блоком коррекции вырабатывается сигнал коррекции кода времени, поступающий на реверсивный счетчик 13, где формируется код длительности цикла, меньший кода длител ности предудьщего цикла, который был записан в счетчик 13 (по правилу Т,, Этот код подается на первый вход нелинейного блока 14, где в соответствии с формулой (1) вырабатывается сигнал управления таймерным у стройством 9, учитывая тем самым требование изменения частоты вьздачи управляющих воздействий в системе, связанное с изменением длительности цикла. Выход таймерного устройства 9 связан с входом счетчика 11 тактов. При переполнении счетчика вырабатывается сигнал, подключающий блок 14, заставляя его вырабатывать сигнал управления теймерным устройством 9, При переполнении счетчика 11 он сигнализирует об окончании цикла, и вырабатывает сигнал на подключение блока 12 коррекции. Так как программа управления во времени от цикла к циклу строго повторяется, то уменьшение длительности цикла приводит к увеличению скорости отработки задания, а это - к ситуации |6м (t) , которая оценивается блоком 12 коррекции, управляющая часть которого включается счетчиком 11 в конце каждого цикла. Новый код дпительности цикла сохраняется до тех пор, пока максимальная в преды дущем цикле ошибка не станет меньше порогового значения , после чего для следующего цикла назначается новый код длительности и процесс продолжается в соответствии с вьшеописанным., Блок 12 коррекции работает следующим образом. 7 С выхода измерителя 1 рассогласования в течение цикла на один из входов блока 17 сравнения поступает 6 значений ошибок, на другой вход которого подается от задатчика 16 порогового значения погрешности сигнал, пропорциональньй . Если |(-fc) , то в устройстве сравнения вырыбатывается сигнал, в противном случае сигнал не вырабатывается. Пусть имеет место второй случай. Тогда триггер 18 закрыт, поэтому закрыт логический элемент И 19, от блока коррекции на реверсивный счетчик 13 сигнал коррекции кода длительности цикла не поступает и код остается прежним. При наличии ситуации i &,(i)U от блока 17 сравнения наR-вход триггера 18 поступает сигнал, переводящий его в состояние 1. Этот сигнал 1 подается на первый вход логического элемента И 19, на второй вход которого по окончании цикла подается 1 от счетчика 11. В соответствии с принципом работы логического элемента И 19 на его выходе появляется сигнал управления реверсивным счетчиком 13, заставляющий последний изменять код дпительности цикла (т.е. счетчик 13 запускается сигналом 1). Через линию 15 задержки сигнал от счетчика 11 тактов поступает на S-вход триггера t8, обнуляя его. Этот канал необходим для подготовки триггера к работе в следующем цикле. Блок 8 работает следующим образом. В первом цикле в регистры блока 21 от АЦП 22 записывается 0 значениз выработанных управляющих воздействий. По сигналу, полученному от таймерного устройства 9, осуществляется сдвиг записанной в блоке 21 регистров информации влево и выдача на ЦАП 20 в первом такте второго цикла управляющего воздействия, полученного в первом такте первого цикла. После этого от линии задержки сборки 23 поступает сигнал, paзpeшajoщий запись от АЦП 22 скорректированного сигнала управления первого такта второго цикла в (-5-1)-й регистр. С окончанием каждого такта в цикле осуществляется процесс сдвига влево записанной информации выдачи через ЦАП 20 в систему соответствующих дополнительных управлений и их записи. Покажем, что использование предлагаемой системы по сравнению с прототипом, который примем за базовый образец, ведет к уменьшению общего времени изготовления изделия при сохранении поставленных требований, т.е. к повьшению производительносги оборудования. Пусть время уменьшения длительности каждого цикла ut удовлетворяет требованию Кроме того, очевидно, что длительность цикла ограничена снизу величиной t кр. Если длительность цикла обозначить через t и изделие изготавливаетсяза N циклов, то при использо- вании базового образца время изготов ления изделия равно Рассмотрим процесс изготовления изделия в условиях применения предлагаемой системы. Пусть отработано Л, N циклов с длительностью каждого циала i , посл чего максимальная ошибка в цикле ) стала меньше порогового значения . .Длительность цикла умень шается tj t и система работае hj, N циклов до возникновения ситуации1Ед4(Ь)и . Дальше процесс повторяется до тех пор, пока t не станет равно Оир , после чего длительность цикла не уменьшается и оставшиеся (N 21 И; ) циклов работа идет с длиi iтельностью каждого цикла txp kp 1 (2) 78 Тогда время изготовления изделия составляет И-f, TH.|,t;«+t N-.En,)tKN jU;-tKln/.3 Сравним (2) и (3): если 0, то выигрьш во TS-TH во времени изготовления есть; если О, то выигрьша по времени изготовления нет; :T6-T,i,N-i,H(i;-t,)n,m,-t,K-(vgn/ rZ (t;-t,)v,,-(t,-y (N-n,b|: Ct,-t,n;. j-2 Очевидно, что разница (ij-tK)- О, т.е. под знаком суммы самый большой сомножитель (tj-t) () . Оценим наихудший результат, т.е. выражение под знаком суммы представим в виде niax | trtJn;5(tj--t.)(n,in,.,...r,,.J. Тогда Ts-H lt,.ljK4,+ njV...,)-(tj-tO(.), откуда видно, что в первом выражении каждый из сомножителей в выражении для Tj больше соответствующий сомножителей в выражении для Тц, т.е. Tg-Tj, О и предлагаемая система по сравненгпо с базовым образцом дает выигрыш во времени изготовления изделий, или при фиксированном времени обеспечения - выпуск большего количества единиц продукции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регулирования интенсивности потока выводимых частиц при медленном выводе пучка из синхротрона | 1985 |

|

SU1362388A1 |

| ТЕЛЕВИЗИОННЫЙ АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1988 |

|

SU1623536A1 |

| БЕСКОНТАКТНЫЙ ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА | 2017 |

|

RU2658678C1 |

| Система адаптивного управления параметром технологического процесса | 1988 |

|

SU1620989A1 |

| Система автоматического регулирования | 1983 |

|

SU1083158A1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Цифровой измеритель температуры | 1986 |

|

SU1362952A1 |

| Устройство для регулирования массовых расходов смешиваемых продуктов | 1988 |

|

SU1695273A1 |

| Способ стабилизации толщины изоляции кабеля и устройство для его реализации | 1982 |

|

SU1302248A1 |

| Способ фазового управления асинхронным электродвигателем и устройство для его осуществления | 1978 |

|

SU928582A1 |

СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ЦИКЛИЧЕСКИМИ ПРОДЕССАМИ, содержащая последовательно соединен- ные измеритель рассогласования, усилитель, фильтр, сумматор и исполнительное устройство, подключенное выходом к входу объекта регулирования, выход которого соединен с сигнальным входом датчика обратной связи, первый вход измерителя рассогласования подключен к выходу датчика обратной связи, второй вход сумматора соединен с выходом блока памяти, выход сумматора соединен с первым входом блока памяти, второй вход которого соединен с выходом таймерного устройства и входом программного устройства, выходом подключенного к второму входу измерителя рассогласования, отличающаяся тем, что, с целью повышения производительности оборудования, в нее введены счетчик тактов, последовательно соединенные блок коррекции, реверсивный счетчик и нелинейный блок, выходом подключенный к входу таймерного устройства, первый вход блока коррекции соединен с выходом измерителя рассогласования, второй вход - с вторым входом нёлийейного блока и с выходом счетчика тактов, вход которого подключен к выходу таймерного .устройства.

От 5л, 1

(Риг.2

К§л.13

HKF 5ni-&

К5лЛ

20

OmSflA

-O-yf MJ

23

Отбл.И Фт.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Система автоматического регулирования | 1975 |

|

SU723510A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Анхимюк В.Л | |||

| Теория автоматического управления | |||

| Минск, Высшая школа, 1979, с | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1984-11-15—Публикация

1983-04-21—Подача