Изобретение относится к электросвязи и может использоваться в системах цифровой передачи звуковых сигналов.

Цель изобретения - повышение точности работы устройства.

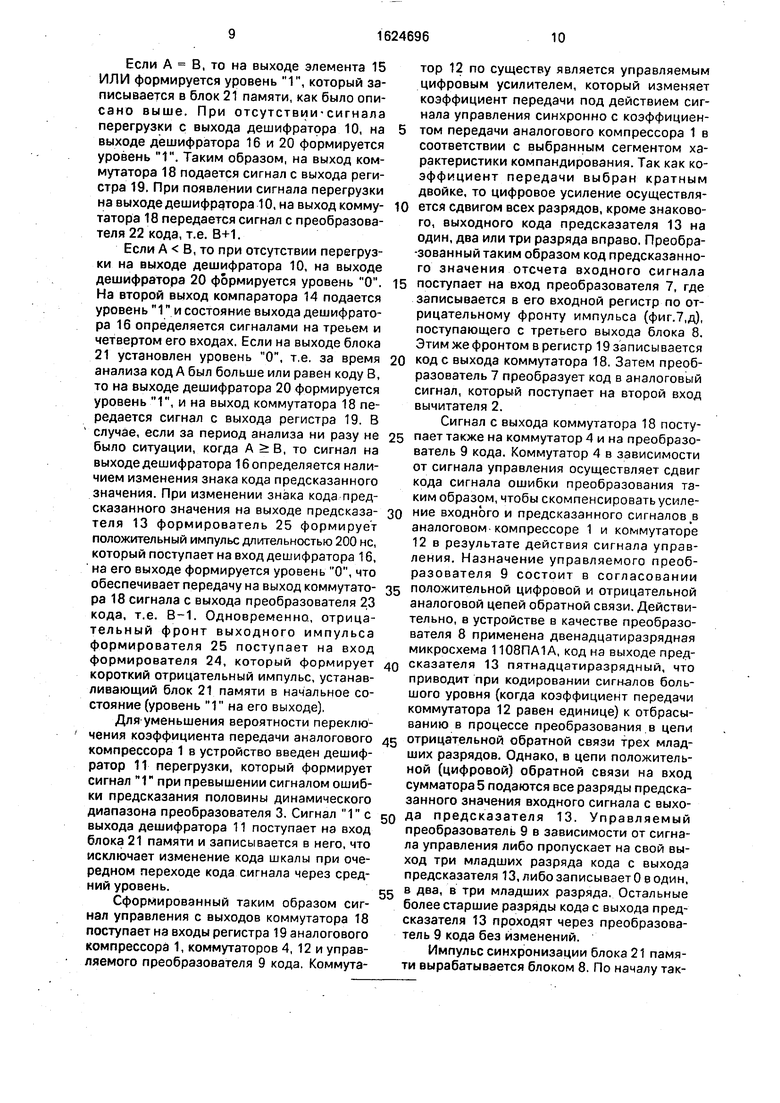

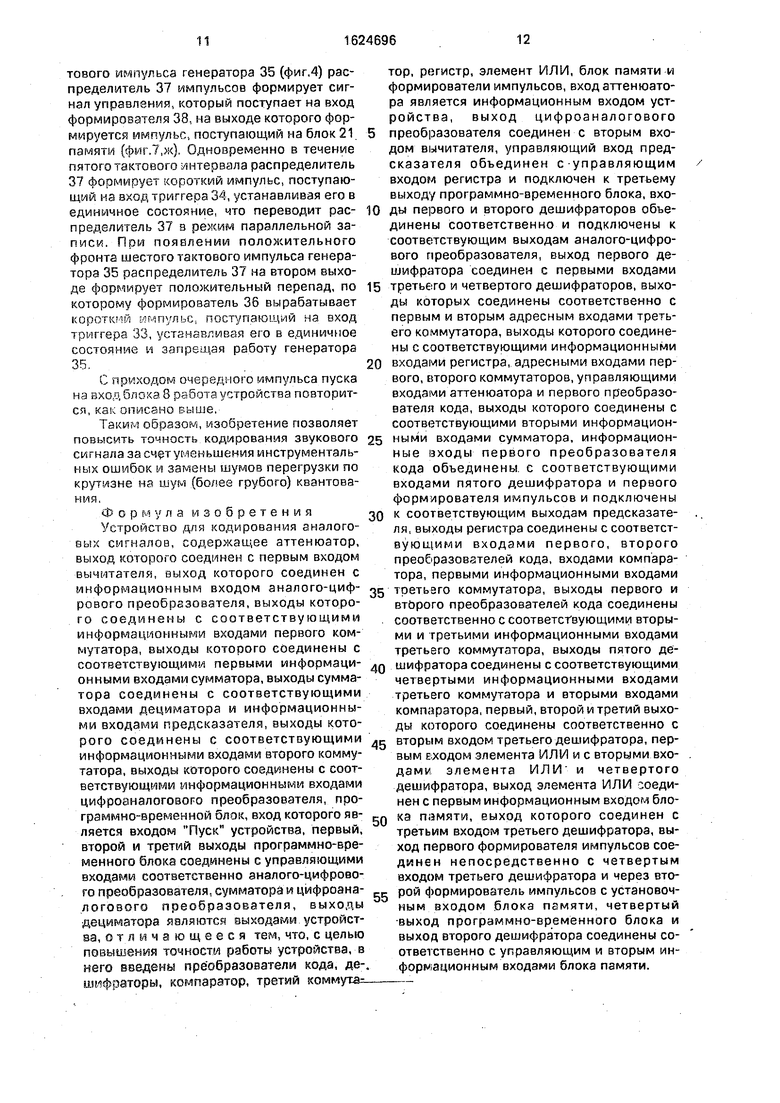

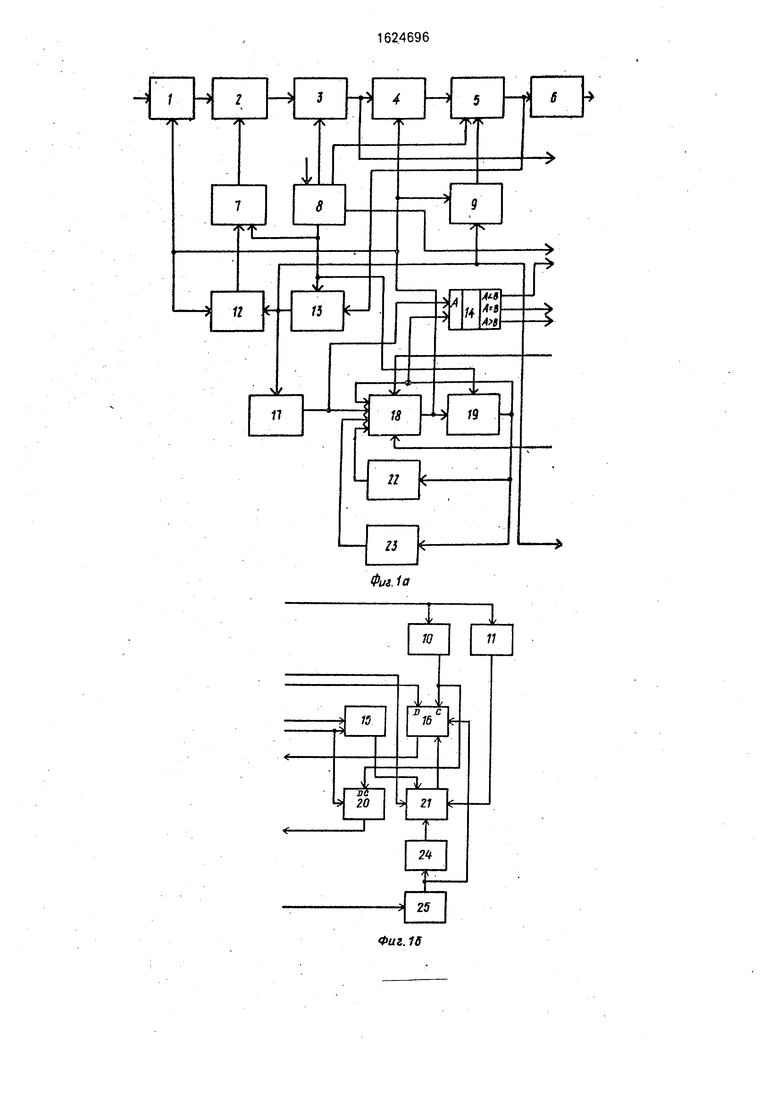

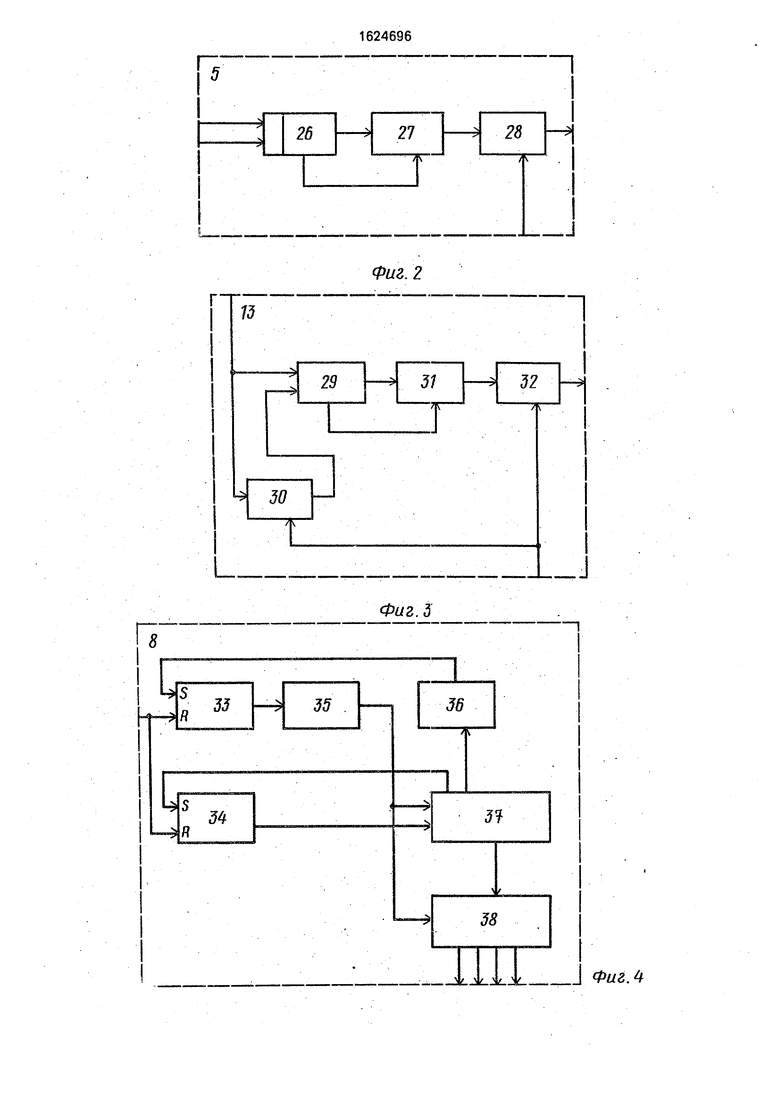

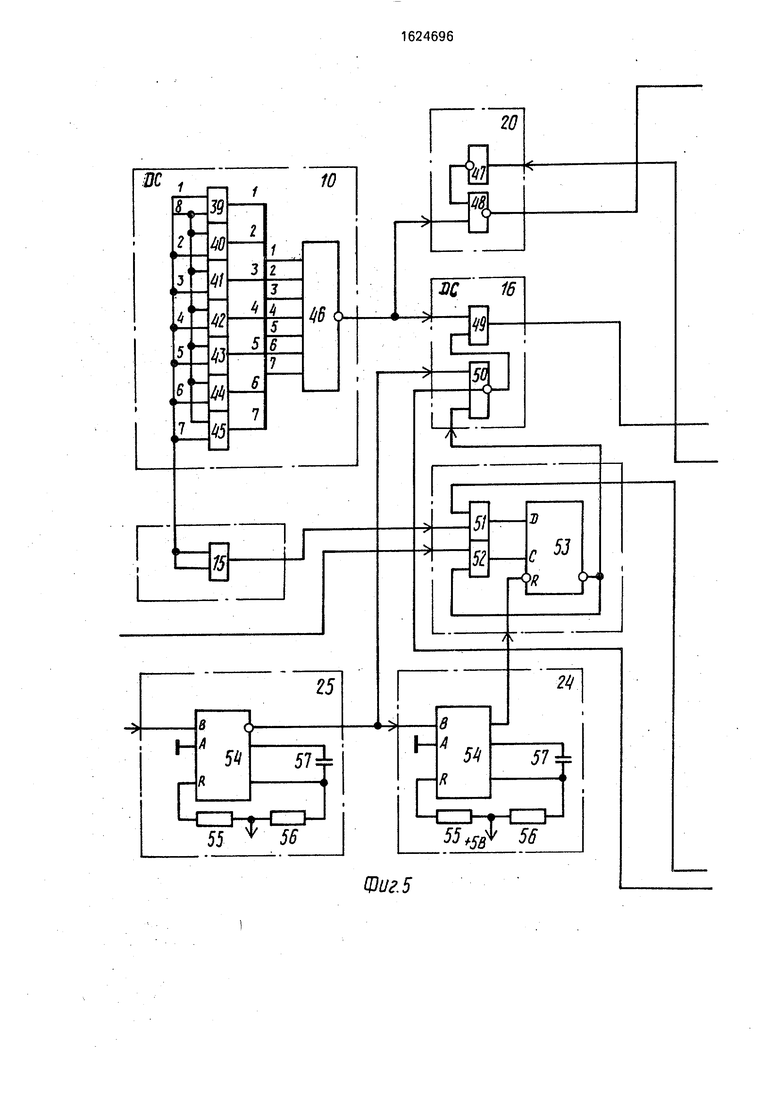

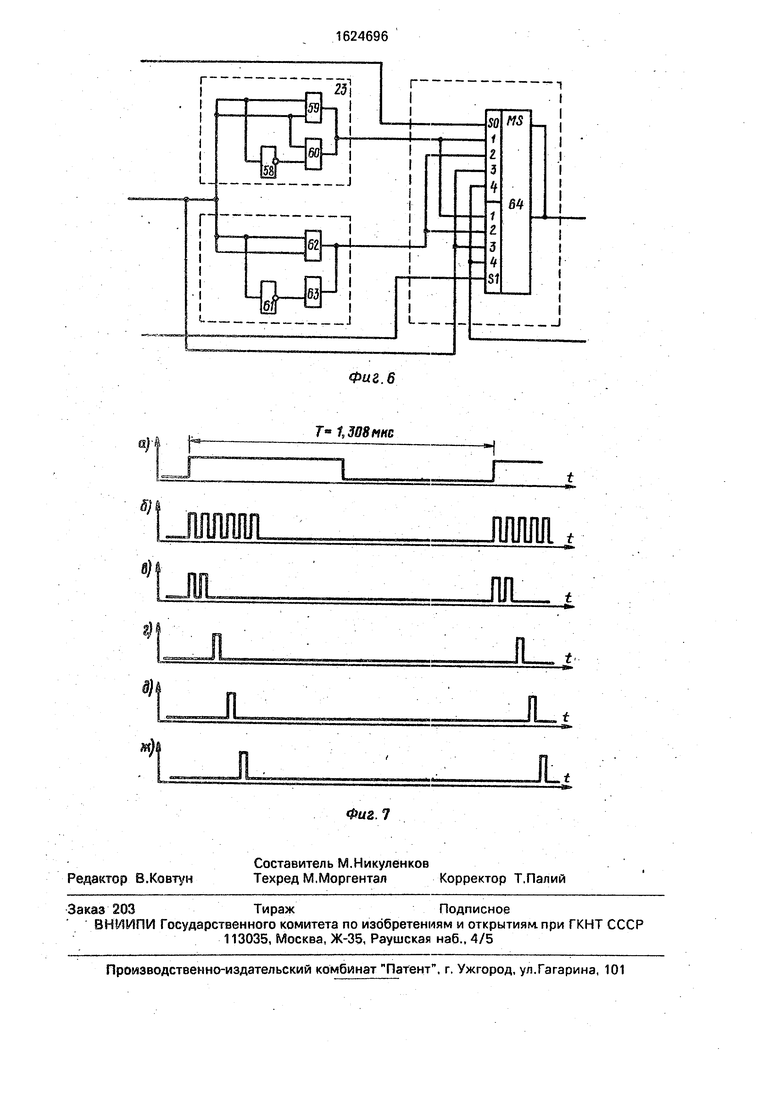

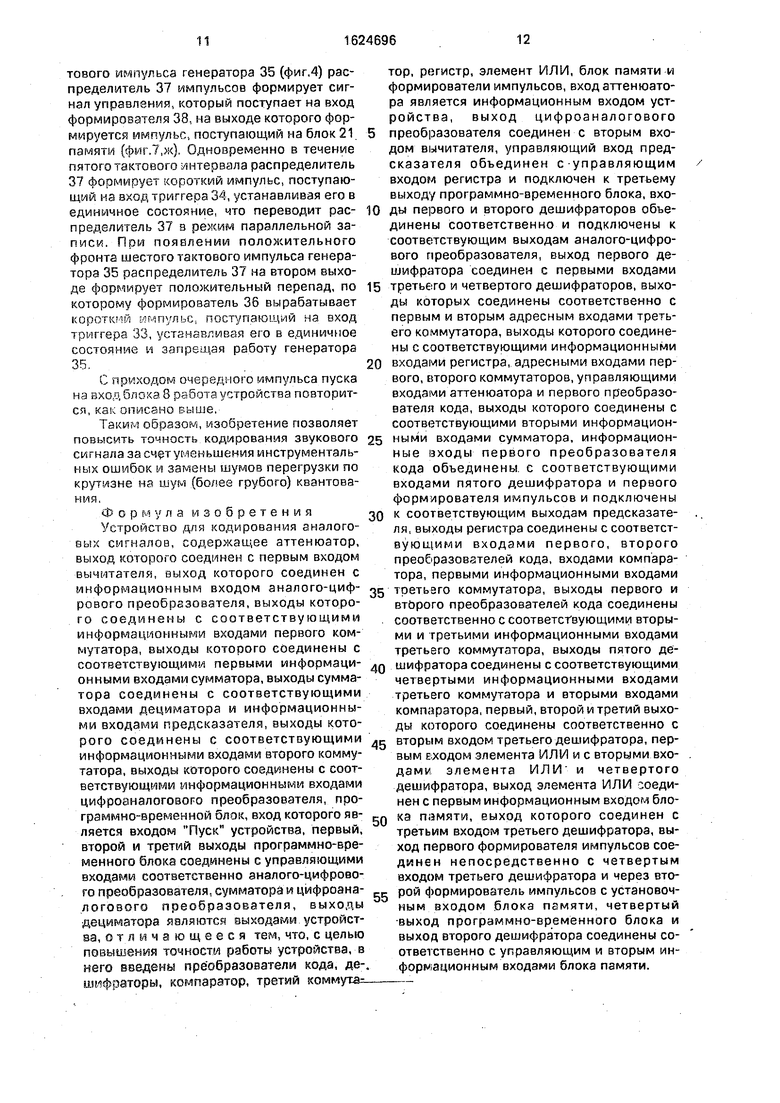

На фиг.1 представлена структурная схема устройства; на фиг.2 - функциональная схема сумматора; на фиг.З - функциональная схема предсказателя; на фиг.4 - функциональная схема программно-временного блока; на фиг.5 - функциональные схемы первого, третьего, четвертого дешифраторов, блока памяти, первого и второго формирователей импульсов; на фиг.6 - функциональные схемы первого, второго преобразователей кода третьего коммутатора; на фиг.7 - временные диаграммы, поясняющие работу устройства.

Устройство содержит (фиг.1) аттенюатор (аналоговый компрессор) 1, вычитатель

2, аналого-цифровой пареобразователь 3, первый коммутатор 4, сумматор 5, децима- тор 6, цифроаналоговый преобразователь 7, программно-временной блок 8, первый управляемый преобразователь 9 кода, первый, второй дешифраторы 10, 11, второй коммутатор 12, предсказатель 13, компаратор 14, элемент 15 ИЛИ, третий, пятый дешифраторы 16, 17, третий коммутатор 18, регистр 19, четвертый дешифратор 20, блок 21 памяти, первый, второй преобразователи 22,23 кода, второй и первый формирователи 24 и 25 импульсов.

Сумматор 5 содержит (фиг.2) элемент 26 суммирования, ограничитель 27 и регистр 28.

Предсказатель 13 содержит (фиг.З) вычитатель 29, регистр 30, ограничитель 31 и регистр 32.

Программно-временной блок 8 содержит (фиг.4) триггеры 33, 34, генератор 35 импульсов, формирователь 36 импульсов, распределитель 37 импульсов и формирователь 38 импульсов.

Первый дешифратор 10 выполнен (фиг.Б) на элементах 39-45 ИСКЛЮЧАЮЩЕЕ ИЛИ и элементе 46 И-НЕ, четвертый дешифратор 20 выполнен на элементе 47 НЕ и элементе 48 И-НЕ. Третий дешифра- тор 16 выполнен на элементе 49 И и элементе 50 И-НЕ. Блок 21 памяти выполнен на элементе 51 ИЛИ, элементе 52 И и триггере

53.Второй и первый формирователи 24 и 25 импульсов выполнены на одновибраторах

54,резисторах 55, 56 и конденсаторах 57.

Второй преобразователь 23 кода выполнен (фиг.6) на элементе 58 НЕ, элементах 59 и 60 И. Первый преобразователь 22 кода выполнен на элементе 61, элементах 62 и 63 ИЛИ.

Коммутатор 18 выполнен на мультиплексоре 64,

Аналоговый компрессор 1 содержит последовательно соединенные операци- онный усилитель 157УД2, матрицу сопротивлений, выполненную на интегральной сборке 301НРЗ, включенной в качестве делителя напряжения, аналоговый коммутатор на ключе 590КН6, и выходной буферный усилитель, собранный на операционном усилителе 544УД2. На управляющий вход аналогового компрессора 1, который подключен к управляющим входам ключа 590КН6, подается цифровой код, определя- ющий коэффициент передачи устройства по напряжению информационного входа на выход.

Вычитатель 2 собран на операционном усилителе 544УД2, Выходное напряжение вычитателя 2 определяется разностью напряжений, подаваемых на первый и второй входы.

Аналого-цифровой преобразователь 3 выполнен на микросхеме 1107ПВ2.

Коммутатор 4 выполнен на мультиплексорах 531КП12, включенных по схеме сдви- гателя кодов. На адресные входы коммутатора 4 подается управляющий код, определяющий сдвиг разрядной сетки на выходе коммутатора.

Элемент 26 суммирования собран на пяти микросхемах 531ИПЗ, включенных в режим суммирования кодов. С целью увеличения быстродействия в сумматоре исполь- зуется схема ускоренного переноса на 531ИПЧ. Ограничитель 27 (31) выполнен на мультиплексорах 531КП11, первые входы которого подключены к выходу суммы элемента 26 (вычитателя 29), а на вторые входыподаны сигналы 1. Управляющим сигналом для мультиплексора служит сигнал переноса из старшего разряда, снимаемый с элемента 26 (вычитателя 29), Регистры 28, 30,32 собраны на микросхемах 555ТМ8, Вычитатель 29 выполнен на микросхемах 531 ИПЗ со схемой ускоренного переноса 531ИПЧ.

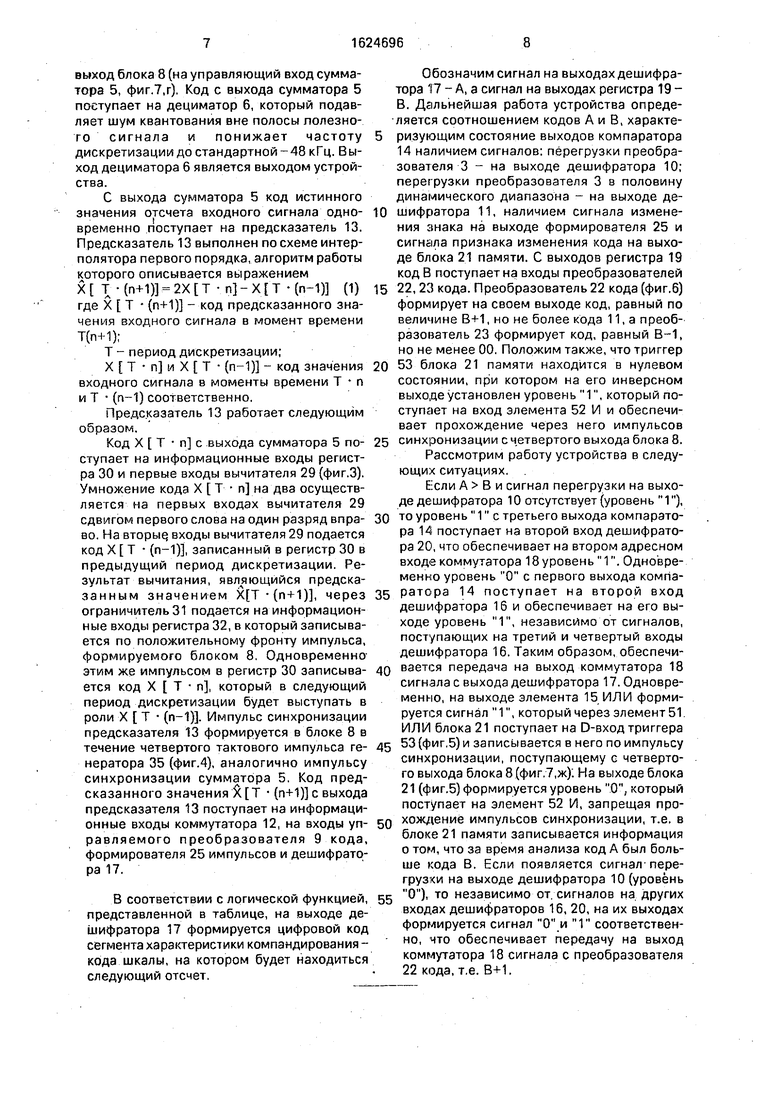

Коммутатор 12 выполнен на трех микросхемах 531ИР21. Он имеет пятнадцать информационных входов и двенадцать выходов. В зависимости от сигнала, поступающего на адресные входы, коммутатор 12 подключает либо с 2 по 12, либо с 3 по 13, либо с 4 по 14, либо с 5 по 15 входы к его выходам со 2 по 12, а первый разряд (знаковый) подключен постоянно на выход. Циф- роаналоговый преобразователь 7 состоит из преобразователя 1108ПА1, источника опорного напряжения 142ЕН2Аи выходного усилителя на ОУ 544УД2. Входной код подается через регистр, выполненный на микросхемах 555ТМ8. Дешифратор 17 кода шкалы выполнен на микросхемах 555ЛП5 и 555ЛА4. Дешифратор 17 реализует логическую функцию, представленную в таблице.

Одновибратор 54 выполнен на микросхеме 555АГЗ, триггер 53 на микросхеме 555ТМ2, коммутатор 18 - на микросхеме 555КП11.

Устройство работает следующим образом.

Аналоговый звуковой сигнал поступает на информационный вход аналогового компрессора 1, где усиливается операционным усилителем таким образом, чтобы использовалась вся шкала квантования и в то же

время клиппирование сигнала было маловероятным. Затем этот нормированный входной аналоговый сигнал поступает на усилитель (выполненный на резистивной матрице, ключе и операционном усилителе), коэффициент передачи которого задается в виде кода, посту лающего с выхода коммутатора 18, и определяется выбранным сегментом характеристики компандирования. (компрессированный сигнал с выхода аналогового компрессора 1 поступает на первый вход вычитателя 2, на второй вход которого с выхода преобразователя 3 поступает предсказанное значение входного сигнала.

Предполагается, что в начальный момент устройство находится в режиме отслеживания сигнала, т.е. соотношение между сигналами, подаваемыми на первый и второй входы вычитателя 2 не превышает динамического диапазона работы преобразователя 3, Если это условие не выполняется, то по истечении переходного процесса устройство войдет в режим отслеживания сигнала. Таким образом, на выходе вычитателя 2 формируется сигнал ошибки предсказания, равный разности предсказанного и истинного значений входных сигналов. С приходом импульсов синхронизации на управляющий вход преобразователя 3 происходит преобразование аналоговой величины сигнала ошибки предсказания в соответствующий код, В качестве преобразователя используется микросхема 1107ПВ2, которая для полного цикла преобразования требует двух импульсов. Импульсы синхронизации формируются в блоке 8 следующим образом. С приходом положительного фронта сигнала внешней синхронизации (фиг.7,а) на вход блока 8 триггеры 33, 34 (фиг.4) устанавливаются в нулевое состояние. Уровень О с выхода триггера 34 переводит распределитель 37 импульсов в режим счета, а уровень О с выхода триггера 33 запускает генератор 35, который начинает вырабатывать прямоугольные тактовые импульсы (фиг.7,6) с периодом 50 не. Тактовые импульсы поступают на входы распределителя 37 импульсов v формирователя 38. По первому и второму тактовым импульсам распределитель 37 формирует сигнал разрешения, поступающий на вход формирователя 38 и разрешает прохождение двух первых тактовых импульсов с выхода генератора 35 через формирователь 38 на первый выход блока 8 (фиг.7,в).

Таким образом, на выходе преобразователя 3 через 100 не появляется цифровой код сигнала ошибки предсказания, который

поступает на входы дешифраторов 10, 11 перегрузки коммутатора 4. Дешифратор 10 вырабатывает сигнал О в случае, когда сигнал ошибки предсказания превышает 5 динамический диапазон квантования преобразователя 3, т.е. произошла перегрузка устройства по крутизне, в остальных случаях на его выходе - 1. Дешифратор 11 формирует сигнал О в том счлучае, если код

10 сигнала ошибки предсказания превышает по абсолютной величине половину динамического диапазона преобразователя 3,с учетом знака ошибки предсказания, а в остальных случаях на его выходе - 1, Ком5 мутатор 4 в зависимости от сигнала управления, поступающего на его входы с выходов коммутатора 18, подключает выходы преобразователя 3 к первым информационным входам сумматоров 5 либо с 15 по 9.

0 либо с 14 по 8, либо с 13-по 7, либо с 12 по 6 разряды. При этом, старший знаковый разряд преобразователя 3 подается во все остальные старшие разряды сумматора 5. Так как на вторые информационные входы

5 сумматора 5 подается с выхода предсказателя 13 через управляемый преобразователь 9 код предсказанного значения входного сигнала, то на выходе элемента 26 формируется истинное значение отсчета

0 входного сигнала, которое по импульсу блока 8 записывается в регистр 28 (фиг.2). В состав сумматора 5 включен ограничитель 27. Цифровым сумматором, выполненным на микросхемах 555ИПЗ, присущ

5 следующий недостаток - при переполнении его разрядной сетки возникает ошибка ьо весь динамический диапазон. Для исключения этого недостатка выходной код элемента 26 суммирования представлен в виде

Q модифицированного кода, знаковые разряды которого и являются сигналом управления ограничителя 27. При значении знаковых разрядов 01, что соответствует переполнению разрядной сетки элемента 26

5 суммирования вниз, на выходе ограничителя 27 устанавливается минимально разрешенный код (знаковый разряд 1, все остальные 0), при комбинации 10 на выходе ограничителя 27 максимально возможное

0 число (знаковый разряд 0, все остальные 1). При всех остальных комбинациях в знаковых разрядах на выходе элемента 26 (11 или 00) ограничитель 27 передает сигнал со своих входов на выходы и далее на входы реги5 стра 28 без изменения. По третьему тактовому импульсу генератора 35 (фиг.4) распределитель 37 импульсов формирует сигнал управления, который, поступая на вход формирователя 38 импульсов, пропускает третий тактовый импульс на второй

выход блока 8 (на управляющий вход сумматора 5, фиг.Т.г), Код с выхода сумматора 5 поступает на дециматор 6, который подавляет шум квантования вне полосы полезного сигнала и понижает частоту дискретизации до стандартной - 48 кГц. В ы- ход дециматора 6 является выходом устройства.

С выхода сумматора 5 код истинного значения отсчета входного сигнала одновременно поступает на предсказатель 13. Предсказатель 13 выполнен по схеме интерполятора первого порядка, алгоритм работы которого описывается выражением Х T-(n+1) (n-1) (1) где X Т (п+1) - код предсказанного значения входного сигнала в момент времени Т(п+1);

Т - период дискретизации; X Т п и X Т (п-1) - код значения входного сигнала в моменты времени Т п и Т (п-1) соответственно.

Предсказатель 13 работает следующим образом.

Код X Т п с выхода сумматора 5 поступает на информационные входы регистра 30 и первые входы вычитателя 29 (фиг.З). Умножение кода X Т п на два осуществляется на первых входах вычитателя 29 сдвигом первого слова на один разряд вправо. На вторы§ входы вычитателя 29 подается код X Т (п-1), записанный в регистр 30 в предыдущий период дискретизации. Результат вычитания, являющийся предсказанным значением (п + 1), через ограничитель 31 подается на информационные входы регистра 32, в который записывается по положительному фронту импульса, формируемого блоком 8. Одновременна этим же импульсом в регистр 30 записывается код X Т п, который в следующий период дискретизации будет выступать в роли X Т (п-1). Импульс синхронизации предсказателя 13 формируется в блоке 8 в течение четвертого тактового импульса генератора 35 (фиг.4), аналогично импульсу синхронизации сумматора 5. Код предсказанного значения (п+1) с выхода предсказателя 13 поступает на информационные входы коммутатора 12, на входы управляемого преобразователя 9 кода, формирователя 25 импульсов и дешифратора 17.

В соответствии с логической функцией, представленной в таблице, на выходе дешифратора 17 формируется цифровой код сегмента характеристики компандирования - кода шкалы, на котором будет находиться следующий отсчет.

Обозначим сигнал на выходах дешифратора 17 - А, а сигнал на выходах регистра 19 - В. Дальнейшая работа устройства определяется соотношением кодов А и В, характеризующим состояние выходов компаратора 14 наличием сигналов: перегрузки преобразователя 3 - на выходе дешифратора 10; перегрузки преобразователя 3 в половину динамического диапазона - на выходе де0 шифратора 11, наличием сигнала изменения знака на выходе формирователя 25 и сигнала признака изменения кода на выходе блока 21 памяти. С выходов регистра 19 код В поступает на входы преобразователей

5 22, 23 кода. Преобразователь 22 кода (фиг.6) формирует на своем выходе код, равный по величине В+1, но не более кодэ 11, а преобразователь 23 формирует код, равный В-1, но не менее 00. Положим также, что триггер

0 53 блока 21 памяти находится в нулевом состоянии, при котором на его инверсном выходе установлен уровень 1, который поступает на вход элемента 52 l/l и обеспечивает прохождение через него импульсов

5 синхронизации с четвертого выхода блока 8. Рассмотрим работу устройства в следующих ситуациях.

Если А В и сигнал перегрузки на выходе дешифратора 10 отсутствует (уровень 1),

0 то уровень 1 с третьего выхода компаратора 14 поступает на второй вход дешифратора 20, что обеспечивает на втором адресном входе коммутатора 18 уровень 1. Одновременно уровень О с первого выхода компа5 ратора 14 поступает на второй вход дешифратора 16 и обеспечивает на его выходе уровень 1, независимо от сигналов, поступающих на третий и четвертый входы дешифратора 16. Таким образом, обеспечиQ вается передача на выход коммутатора 18 сигнала с выхода дешифратора 17. Одновременно, на выходе элемента 15 ИЛИ формируется сигнал 1, который через элемент 51 ИЛИ блока 21 поступает на D-вход триггера

5 53 (фиг,5) и записывается в него по импульсу синхронизации, поступающему с четвертого выхода блока 8 (фиг.7,ж). На выходе блока

21(фиг.5) формируется уровень О, который поступает на элемент 52 И, запрещая прол хождение импульсов синхронизации, т.е. в

блоке 21 памяти записывается информация о том, что за время анализа код А был больше кода В. Если появляется сигнал перегрузки на выходе дешифратора 10 (уровень 5 0)i то независимо от. сигналов на других входах дешифраторов 16, 20, на их выходах формируется сигнал О и 1 соответствен- - но, что обеспечивает передачу на выход коммутатора 18 сигнала с преобразователя

22кода, т.е. В+1.

Если А В, то на выходе элемента 15 ИЛИ формируется уровень 1, который записывается в блок 21 памяти, как было описано выше. При отсутствии-сигнала перегрузки с выхода дешифратора 10, на выходе дешифратора 16 и 20 формируется уровень 1. Таким образом, на выход коммутатора 18 подается сигнал с выхода регистра 19. При появлении сигнала перегрузки на выходе дешифратора 10, на выход коммутатора 18 передается сигнал с преобразователя 22 кода, т.е. В+1.

Если А В, то при отсутствии перегрузки на выходе дешифратора 10, на выходе дешифратора 20 формируется уровень О. На второй выход компаратора 14 подается уровень 1 и состояние выхода дешифратора 16 определяется сигналами на треьем и четвертом его входах. Если на выходе блока 21 установлен уровень О, т.е. за время анализа код А был больше или равен коду В, то на выходе дешифратора 20 формируется уровень 1, и на выход коммутатора 18 передается сигнал с выхода регистра 19. В случае, если за период анализа ни разу не было ситуации, когда А В, то сигнал на выходе дешифратора 16 определяется наличием изменения знака кода предсказанного значения. При изменении знака кода предсказанного значения на выходе предсказателя 13 формирователь 25 формирует положительный импульс длительностью 200 не, который поступает на вход дешифратора 16, на его выходе формируется уровень О, что обеспечивает передачу на выход коммутатора 18 сигнала с выхода преобразователя 23 кода, т.е. В-1. Одновременно, отрицательный фронт выходного импульса формирователя 25 поступает на вход формирователя 24, который формирует короткий отрицательный импульс, устанавливающий блок 21 памяти в начальное состояние (уровень 1 на его выходе).

Для уменьшения вероятности переклю- чения коэффициента передачи аналогового компрессора 1 в устройство введен дешифратор 11 перегрузки, который формирует сигнал 1 при превышении сигналом ошибки предсказания половины динамического диапазона преобразователя 3. Сигнал 1 с выхода дешифратора 11 поступает на вход блока 21 памяти и записывается в него, что исключает изменение кода шкалы при очередном переходе кода сигнала через средний уровень.

Сформированный таким образом сигнал управления с выходов коммутатора 18 поступает на входы регистра 19 аналогового компрессора 1, коммутаторов 4, 12 и управляемого преобразователя 9 кода. Коммутатор 12 по существу является управляемым цифровым усилителем, который изменяет коэффициент передачи под действием сигнала управления синхронно с коэффициен- 5 том передачи аналогового компрессора 1 в соответствии с выбранным сегментом характеристики компандирования. Так как коэффициент передачи выбран кратным двойке, то цифровое усиление осуществля0 ется сдвигом всех разрядов, кроме знакового, выходного кода предсказателя 13 на один, два или три разряда вправо. Преобразованный таким образом код предсказанного значения отсчета входного сигнала

5 поступает на вход преобразователя 7, где записывается в его входной регистр по отрицательному фронту импульса (фиг.7,д), поступающего с третьего выхода блока 8. Этим же фронтом в регистр 19 записывается

0 коде выхода коммутатора 18, Затем преобразователь 7 преобразует код в аналоговый сигнал, который поступает на второй вход вычитателя 2.

Сигнал с выхода коммутатора 18 посту5 пает также на коммутатор 4 и на преобразователь 9 кода. Коммутатор 4 в зависимости от сигнала управления осуществляет сдвиг кода сигнала ошибки преобразования таким образом, чтобы скомпенсировать усиле0 ние входного и предсказанного сигналов .в аналоговом компрессоре 1 и коммутаторе 12 в результате действия сигнала управления. Назначение управляемого преобразователя 9 состоит в согласовании

5 положительной цифровой и отрицательной аналоговой цепей обратной связи. Действительно, в устройстве в качестве преобразователя 8 применена двенадцатиразрядная микросхема 1108ПА1А, код на выходе пред0 сказателя 13 пятнадцатиразрядный, что приводит при кодировании сигналов большого уровня (когда коэффициент передачи коммутатора 12 равен единице) к отбрасыванию в процессе преобразования в цепи

5 отрицательной обратной связи трех младших разрядов. Однако, в цепи положительной (цифровой) обратной связи на вход сумматора 5 подаются все разряды предсказанного значения входного сигнала с выхоQ да предсказателя 13. Управляемый преобразователь 9 в зависимости от сигнала управления либо пропускает на свой выход три младших разряда кода с выхода предсказателя 13, либо записывает 0 в один,

е в два, в три младших разряда. Остальные более старшие разряды кода с выхода предсказателя 13 проходят через преобразователь 9 кода без изменений.

Импульс синхронизации блока 21 памяти вырабатывается блоком 8. По началу тактового импульса генератора 35 (фиг,4) распределитель 37 импульсов формирует сигнал управления, который поступает на вход формирователя 38, на выходе которого формируется импульс, поступающий на блок 21 памяти (фиг.7,ж). Одновременно в течение пятого тактового интервала распределитель 37 формирует короткий импульс, поступающий на вход триггера 34, устанавливая его в единичное состояние, что переводит распределитель 37 а режим параллельной записи. Пои появлении положительного фронта шестого тактового импульса генератора 35 распределитель 37 на втором выходе формирует положительный перепад, по которому формирователь 36 вырабатывает короткий тпульс поступающий на вход триггера 33, устанавливая его в единичное состояние и запрещая работу генератора 3

С приходом очередного импульса пуска на вхоп блока 8 работа устройства повторится, как описано выше.

Таким обоазом, изобретение позволяет повысить точность кодирования звукового сигнала за счет уменьшения инструментальных ошибок и замены шумов перегрузки по крутизне на шум (более грубого) квантования,

Формула изобретения Устройство для кодирования аналоговых сигналов, содержащее аттенюатор, выход которого соединен с первым входом вычитателя, выход которого соединен с информационным входом аналого-цифрового преобразователя, выходы которого соединены с соответствующими информационными входами первого коммутатора, выходы которого соединены с соответствующими первыми информационными входами сумматора, выходы сумматора соединены с соответствующими входами дециматора и информационными входами предсказателя, выходы которого соединены с соответствующими информационными входами второго коммутатора, выходы которого соединены с соответствующими информационными входами цифроаналогового преобразователя, программно-временной блок, вход которого является входом Пуск устройства, первый, второй м третий выходы программно-временного блока соединены с управляющими входами соответственно аналого-цифрового преобразователя, сумматора и цифроана- логового преобразователя, выходы дециматора являются выходами устройства, отличающееся тем, что, с целью повышения точности работы устройства, в него введены преобразователи кода, де-, шифраторы, компаратор, третий коммута.

тор, регистр, элемент ИЛИ, блок памяти и формирователи импульсов, вход аттенюатора является информационным входом устройства, выход цифроаналогового

преобразователя соединен с вторым входом вычитателя, управляющий вход предсказателя объединен с управляющим входом регистра и подключен к третьему выходу программно-временного блока, вхо0 ды первого и второго дешифраторов объединены соответственно и подключены к соответствующим выходам аналого-цифрового преобразователя, выход первого дешифратора соединен с первыми входами

5 третьего и четвертого дешифраторов, выходы которых соединены соответственно с первым и вторым адресным входами третьего коммутатора, выходы которого соединены с соответствующими информационными

0 входами регистра, адресными входами первого, второго коммутаторов, управляющими входами аттенюатора и первого преобразователя кода, выходы которого соединены с соответствующими вторыми информацион5 ными входами сумматора, информационные входы первого преобразователя кода объединены с соответствующими входами пятого дешифратора и первого формирователя импульсов и подключены

0 к соответствующим выходам предсказателя, выходы регистра соединены с соответствующими входами первого, второго преобразователей кода, входами компаратора, первыми информационными входами

5 тоетьвго коммутатора, выходы первого и второго преобразователей кода соединены соответственно с соответствующими вторыми и третьими информационными входами третьего коммутатора, выходы пятого де0 шифратора соединены с соответствующими четвертыми информационными входами третьего коммутатора и вторыми входами компаратора, первый, второй и третий выходы которого соединены соответственно с

5 вторым входом третьего дешифратора, первым ЕХОДОМ элемента ИЛИ и с вторыми входами элемента ИЛИ и четвертого дешифратора, выход элемента ИЛИ соединен с первым информационным входом бло0 ка п.эмяти, выход которого соединен с третьим входом третьего дешифратора, выход первого формирователя импульсов сое- динен непосредственно с четвертым входом третьего дешифратора и через вто5 рой формирователь импульсов с установочным входом блока памяти, четвертый выход программно-временного блока и выход второго дешифратора соединены соответственно с управляющим и вторым информационным входами блока памяти.

Фиг. 16

27

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования аналоговых сигналов | 1985 |

|

SU1316091A1 |

| Преобразователь перемещения в код | 1989 |

|

SU1656682A1 |

| Устройство для автоматической проверки преобразователя угол-код | 1987 |

|

SU1441478A1 |

| Цифровой термометр | 1989 |

|

SU1732182A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1988 |

|

SU1647901A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 1991 |

|

RU2074514C1 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| Система передачи телевизионного сигнала | 1984 |

|

SU1252974A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

Изобретение относится к электросвязи и может использоваться в системах цифровой передачи звуковых сигналов. Устройство производит преобразование аналогового (звукового) сигнала в цифровой сигнал. Изобретение позволяет повысить точность кодирования звукового сигнала за счет уменьшения инструментальных ошибок и замены шумов перегрузки по крутизне на шум (более грубого) квантования. Устройство содержит аттенюатор (аналоговый компрессор), вычитатель, аналого-цифровой преобразователь, коммутаторы, сумматор, Дециматор, цифроаналоговый преобразователь, программы о-сременной блок, преобразователи кода, дешифраторы, предсказатель, компаратор, элемент ИЛИ, регистр, блок памяти и формирователи импульсов. 7 ил., 1 табл.

13

29

/V

Фиг. 2

П

I

Фиг.д

Фи&Л

ri

969frZ9l

S MQ)

Т 1,308 мнс

Фиг.6

ж

Л.

JLt

JL

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1984 |

|

SU1197085A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для кодирования аналоговых сигналов | 1985 |

|

SU1316091A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-30—Публикация

1989-01-09—Подача