Изобретение относится к вычислительной технике и может быть использовано для сопряжения электронных вычислительных машин (ЭВМ), имеющих общесистемный ин.- терфейс типа «Общая шина (ОШ) с периферийным устройством, имеющим интерфейс ЕС ЭВМ.

Цель изобретения - повышение достоверности передаваемой информации и расширение номенклатуры сопрягаемых устройств.

В данном устройстве осуществляется сопряжение вычислительной машины с интерфейсом «ОШ СМ-4 с печатающим устройством ЕС-7040.

Устройство для сопряжения подключаетходов регистра 2, шину 29 группы информационных выходов регистра 3, шину 30 группы информационных выходов шифратора 4, шину 31 информационного выхода формиг рователя 5, шину 32 группы управляющих входов мультиплексора 1, шины 33 первого и 34 второго синхррвыходов узла 10, шину 35 группы информационных входов регистра 6, шину 36 первой группы информационных входов регистра 8, шину 37 второй груп 0 пы информационных входов регистра 8, шину 38 группы выходов регистра 8, шину 39 разрешающего входа узла 9, шину 40 группы разрешающих входов узла 9, шину 41 группы выходов узла 9, шину 42 группы

ся к СМ-4 через контроллер БЭ810-0,2 М, 15 информационных входов регистра 18, шину БЭ812-012 М (3.043.016-01 ТО), который 43 группы информационных входов регистра 17, шину 44 группы информационных выходов регистра 12, шину 45 группы информационных выходов регистра 13, шину 46 группы выходов дешифратора 14, шину 47

не входит в состав изобретения и предназначен для подсоединения печатающего устройства СМ6304.01.

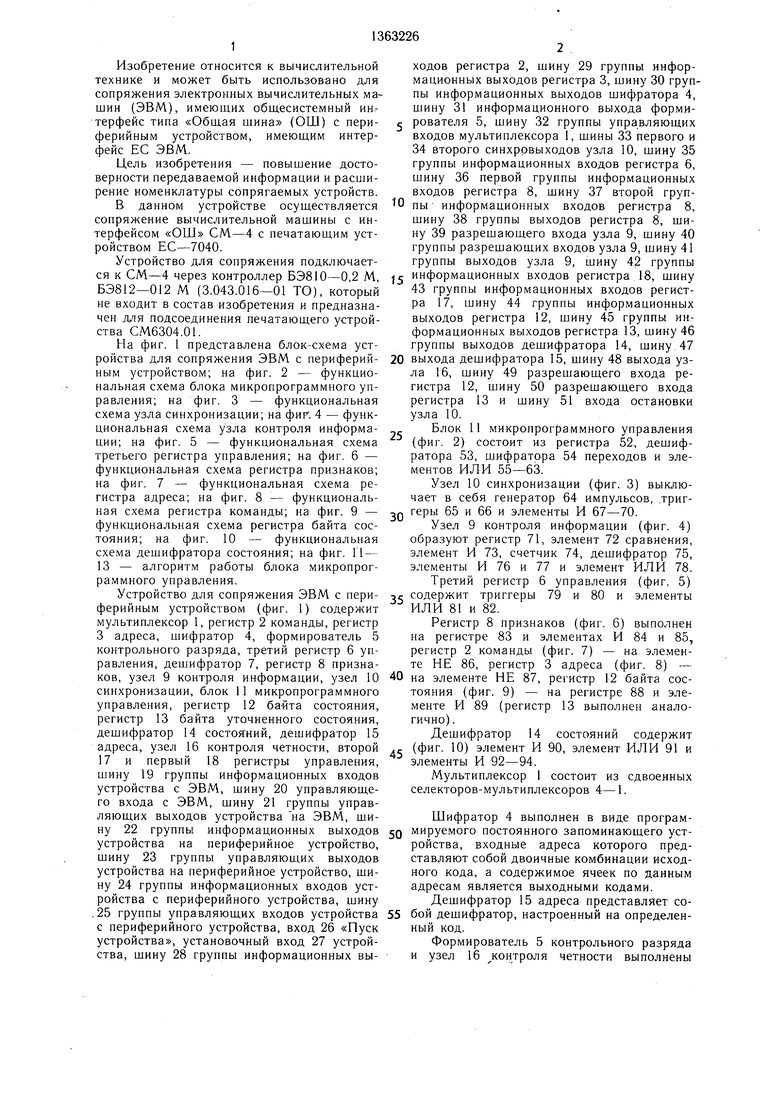

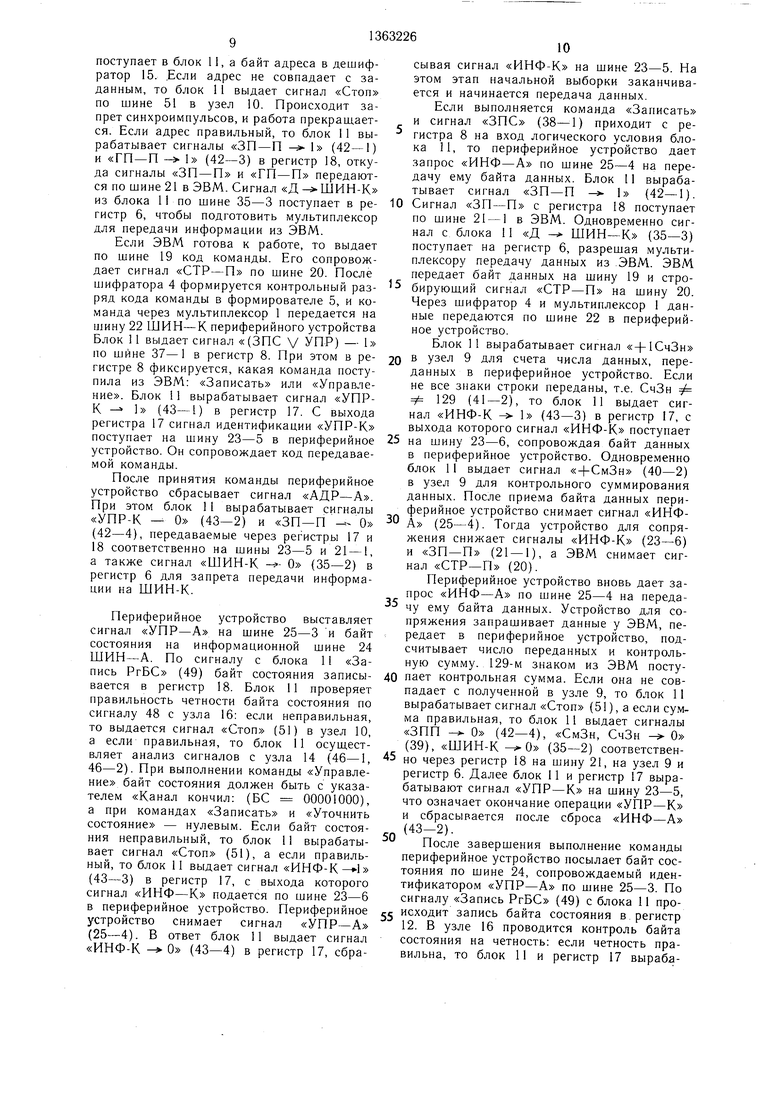

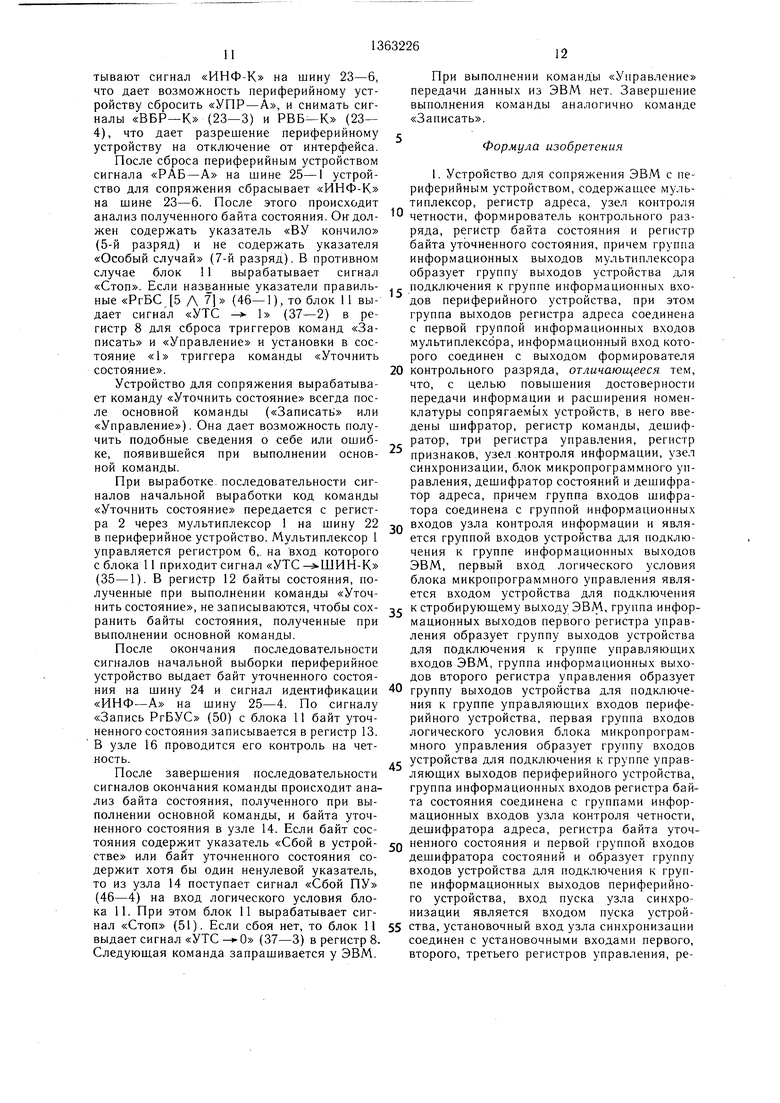

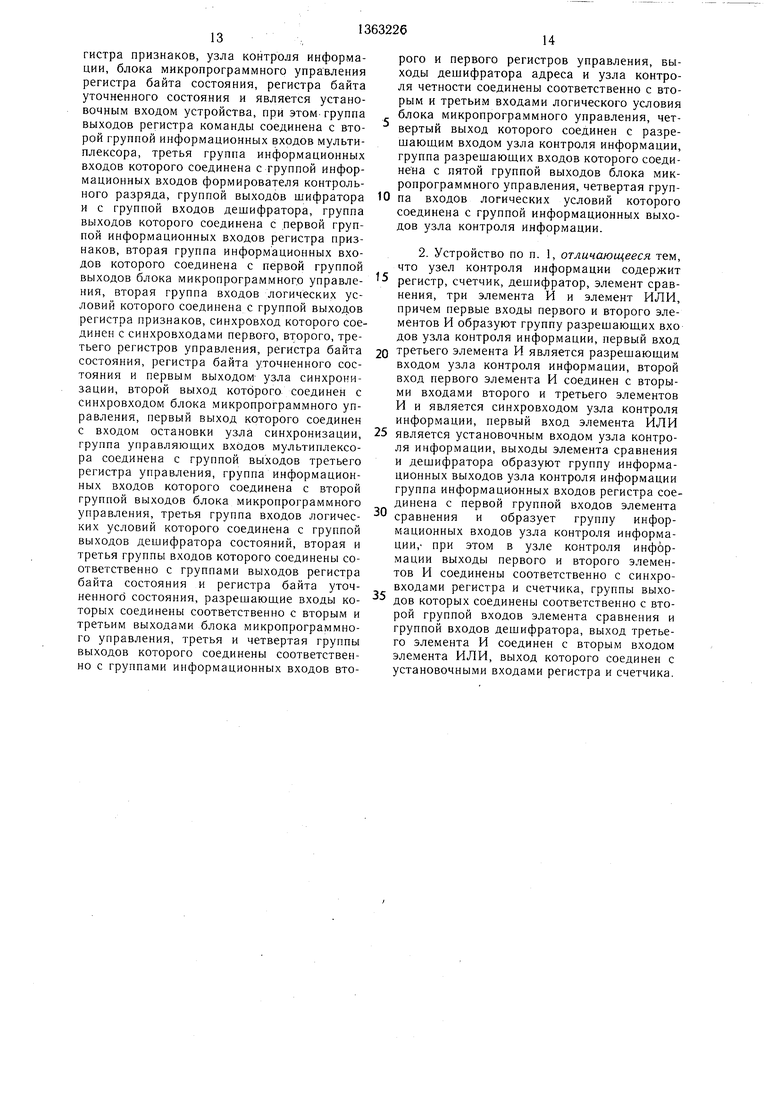

На фиг. 1 представлена блок-схема устройства для сопряжения ЭВМ с периферий- 20 выхода дешифратора 15, шину 48 выхода узным устройством; на фиг. 2 - функциональная схема блока микропрограммного управления; на фиг. 3 - функциональная схема узла синхронизации; на фиг . 4 - функциональная схема узла контроля информации; на фиг. 5 - функциональная схема третьего регистра управления; на фиг. 6 - функциональная схема регистра признаков; на фиг. 7 - функциональная схема регистра адреса; на фиг. 8 - функциональ25

ла 16, шину 49 разрешающего входа регистра 12, шину 50 разрешающего входа регистра 13 и шину 51 входа остановки узла 10.

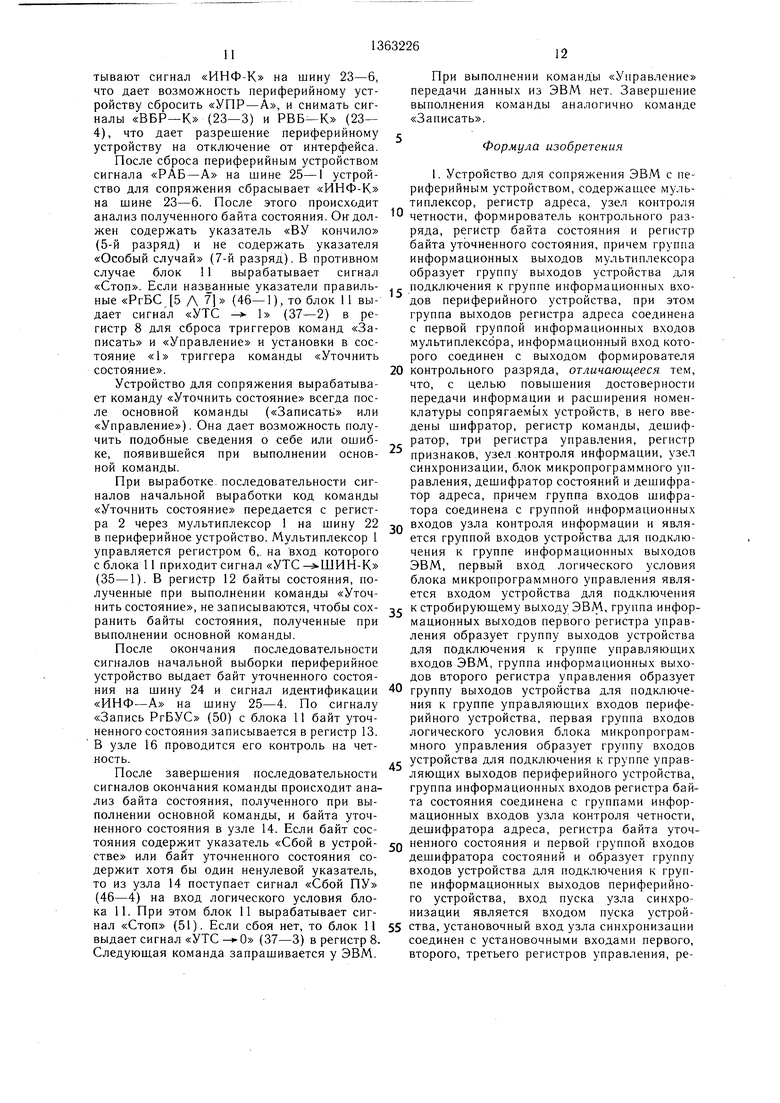

Блок 11 микропрограммного управления (фиг. 2) состоит из регистра 52, дешифратора 53, шифратора 54 переходов и элементов ИЛИ 55-63.

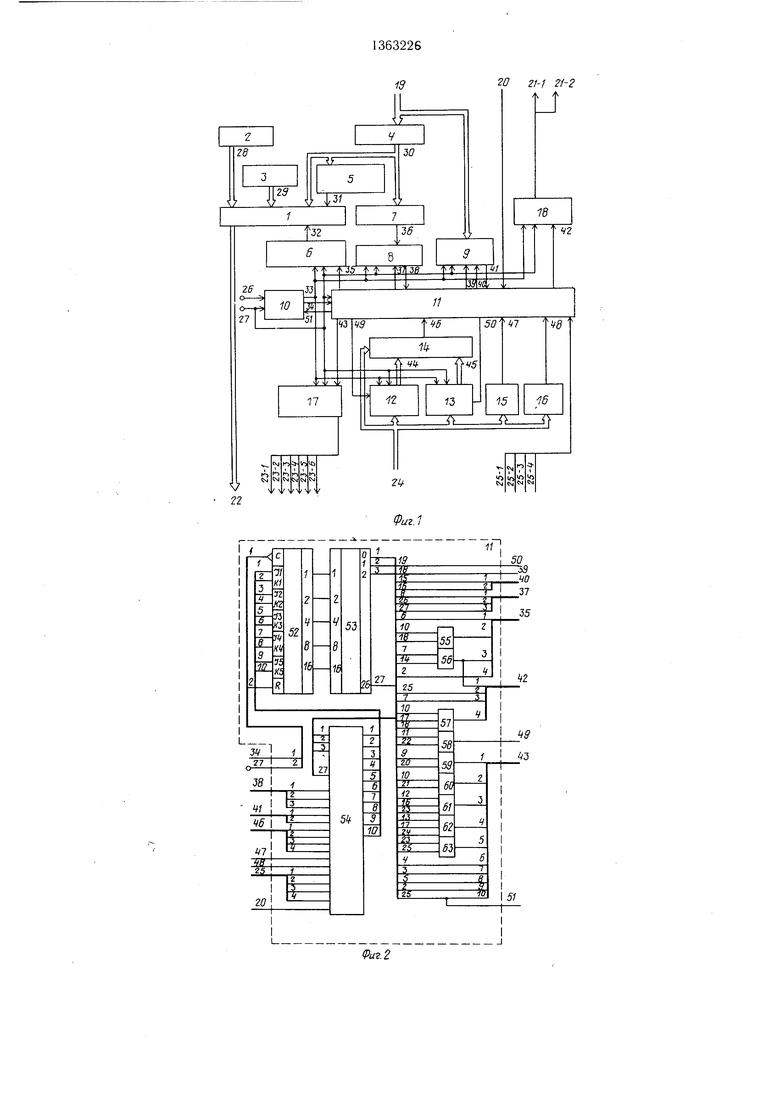

Узел 10 синхронизации (фиг. 3) выключает в себя генератор 64 импульсов, .тригная схема регистра команды; на фиг. 9 - on геры 65 и 66 и элементы И 67-70.

,ffVJ J

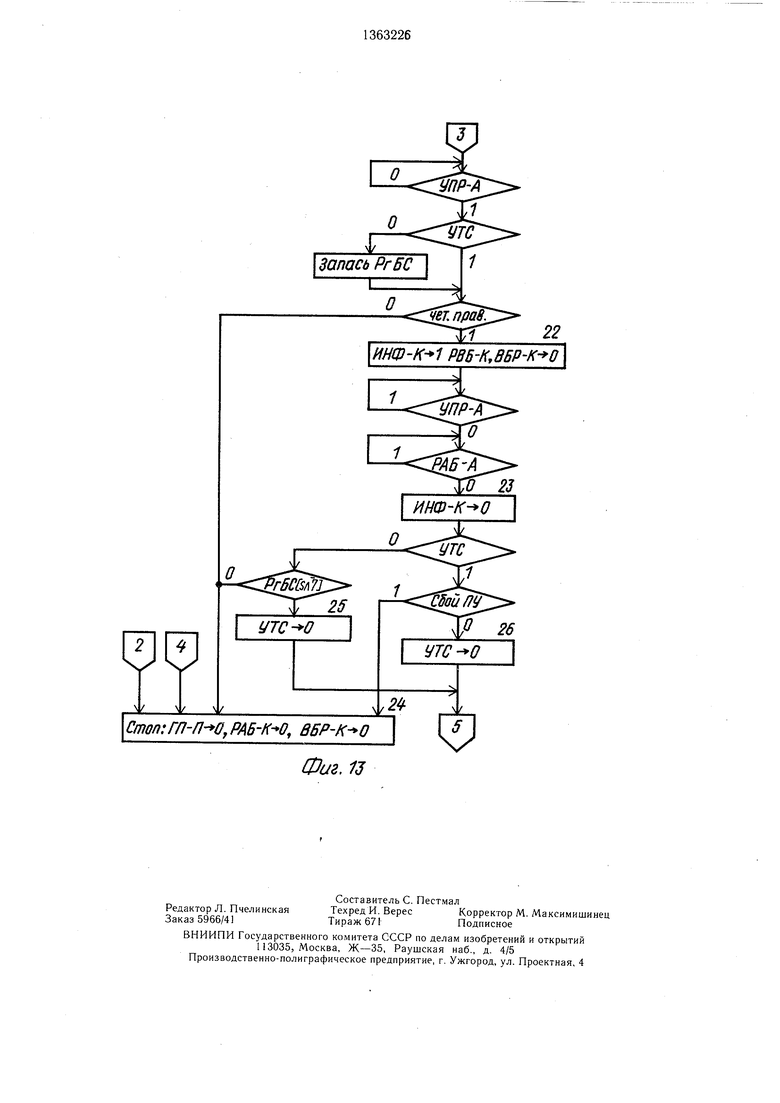

функциональная схема регистра байта состояния; на фиг. 10 - функциональная схема дешифратора состояния; на фиг. 11 - 13 - алгоритм работы блока микропрограммного управления.

Узел 9 контроля инфор.мации (фиг. 4) образуют регистр 71, элемент 72 сравнения, элемент И 73, счетчик 74, дешифратор 75, элементы И 76 и 77 и элемент ИЛИ 78.

Третий регистр 6 управления (фиг. 5)

Устройство для сопряжения ЭВМ с пери- -зг содержит триггеры 79 и 80 и элементы

Uо/I1 ттпт1Г11е- еп

ИЛИ 81 и 82.

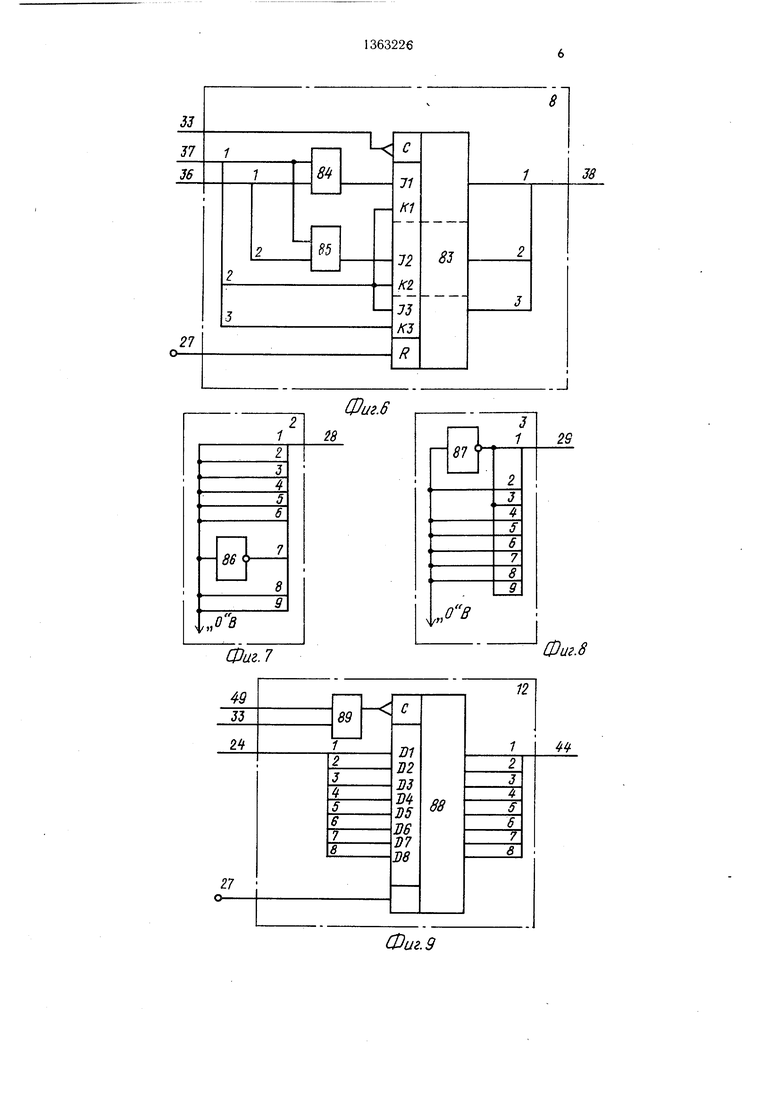

Регистр 8 признаков (фиг. 6) выполнен на регистре 83 и элементах И 84 и 85, регистр 2 команды (фиг. 7) - на элементе НЕ 86, регистр 3 адреса (фиг. 8) -

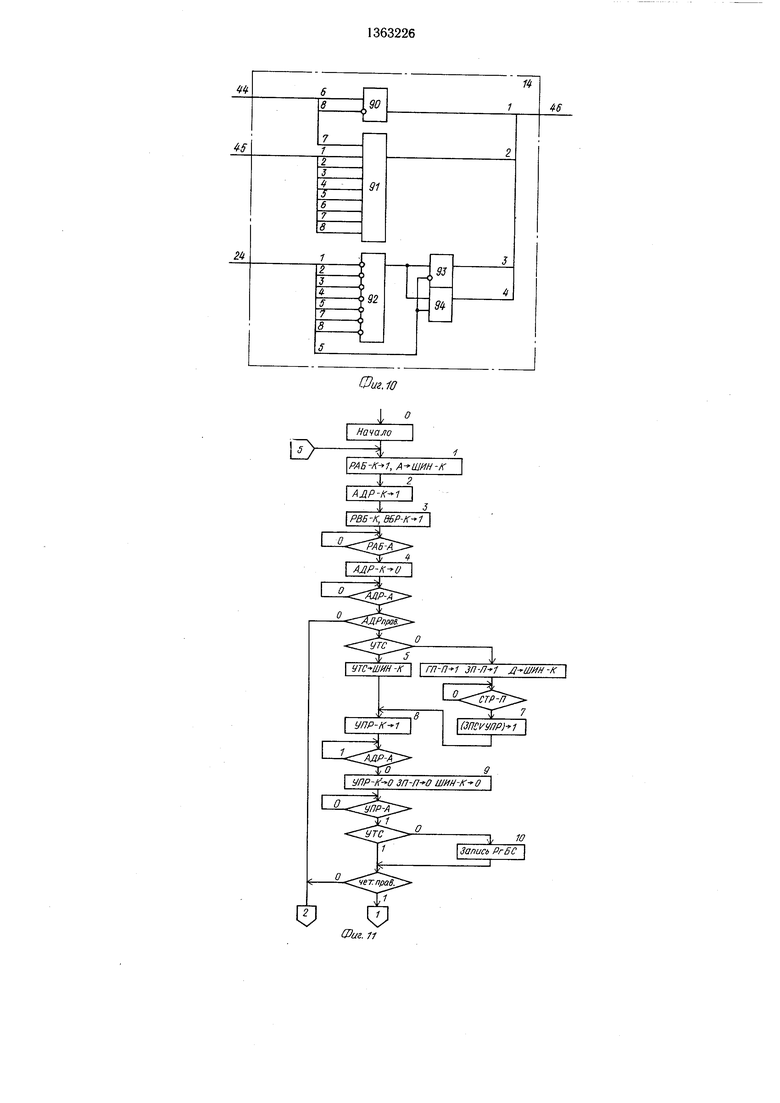

ков, узел 9 контроля информации, узел 10 40 на элементе НЕ 87, регистр 12 байта сое- синхронизации, блок 11 микропрограммного тояния (фиг. 9) - на регистре 88 и эле- управления, регистр 12 ба-йта состояния, регистр 13 байта уточненного состояния, дешифратор 14 состояний, дешифратор 15

ферийным устройством (фиг. 1) содержит мультиплексор 1, регистр 2 команды, регистр 3 адреса, шифратор 4, формирователь 5 контрольного разряда, третий регистр 6 управления, дешифратор 7, регистр 8 признаменте И 89 (регистр 13 выполнен аналогично) .

Дешифратор 14 состояний содержит

адреса, узел 16 контроля четности, второй ,, (фиг. 10) элемент И 90, элемент ИЛИ 91 и

17 и первый 18 регистры управления, шину 19 группы информационных входов устройства с ЭВМ, шину 20 управляющего входа с ЭВМ, шину 21 группы управляющих выходов устройства на ЭВМ, щи45

элементы И 92-94.

Мультиплексор 1 состоит из сдвоенных селекторов-мультиплексоров 4-1.

Шифратор 4 выполнен в виде програмну 22 группы информационных выходов jg мируемого постоянного запоминающего устустройства на периферийное устройство, шину 23 группы управляющих выходов устройства на периферийное устройство, шину 24 группы информационных входов устройства с периферийного устройства, шину

ройства, входные адреса которого представляют собой двоичные комбинации исходного кода, а содержимое ячеек по данным адресам является выходными кодами.

Дешифратор 15 адреса представляет со.25 группы управляющих входов устройства55 бой дещифратор, настроенный на определенс периферийного устройства, вход 26 «Пускный код.

устройства, установочный вход 27 устрой-Формирователь 5 контрольного разряда

ства, щину 28 группы информационных вы-и узел 16 контроля четности выполнены

ходов регистра 2, шину 29 группы информационных выходов регистра 3, шину 30 группы информационных выходов шифратора 4, шину 31 информационного выхода формирователя 5, шину 32 группы управляющих входов мультиплексора 1, шины 33 первого и 34 второго синхррвыходов узла 10, шину 35 группы информационных входов регистра 6, шину 36 первой группы информационных входов регистра 8, шину 37 второй группы информационных входов регистра 8, шину 38 группы выходов регистра 8, шину 39 разрешающего входа узла 9, шину 40 группы разрешающих входов узла 9, шину 41 группы выходов узла 9, шину 42 группы

информационных входов регистра 18, шину 43 группы информационных входов регистра 17, шину 44 группы информационных выходов регистра 12, шину 45 группы информационных выходов регистра 13, шину 46 группы выходов дешифратора 14, шину 47

20 выхода дешифратора 15, шину 48 выхода уз25

ла 16, шину 49 разрешающего входа регистра 12, шину 50 разрешающего входа регистра 13 и шину 51 входа остановки узла 10.

Блок 11 микропрограммного управления (фиг. 2) состоит из регистра 52, дешифратора 53, шифратора 54 переходов и элементов ИЛИ 55-63.

Узел 10 синхронизации (фиг. 3) выключает в себя генератор 64 импульсов, .триг on геры 65 и 66 и элементы И 67-70.

геры 65 и 66 и элементы И 67-70.

Узел 9 контроля инфор.мации (фиг. 4) образуют регистр 71, элемент 72 сравнения, элемент И 73, счетчик 74, дешифратор 75, элементы И 76 и 77 и элемент ИЛИ 78.

Третий регистр 6 управления (фиг. 5)

на элементе НЕ 87, регистр 12 байта сое- тояния (фиг. 9) - на регистре 88 и эле-

менте И 89 (регистр 13 выполнен аналогично) .

Дешифратор 14 состояний содержит

(фиг. 10) элемент И 90, элемент ИЛИ 91 и

,, (фиг. 10) элемент И 90, элемент ИЛИ 91 и

45

элементы И 92-94.

Мультиплексор 1 состоит из сдвоенных селекторов-мультиплексоров 4-1.

Шифратор 4 выполнен в виде програмройства, входные адреса которого представляют собой двоичные комбинации исходного кода, а содержимое ячеек по данным адресам является выходными кодами.

Дешифратор 15 адреса представляет собой дещифратор, настроенный на определенна восьмиразрядной схеме контроля четности М2.

На шинах, обозначенных на фиг. 1 -10, формируются сигналы следующего значения: шина 19 - информационная шина (ДО- Д7)-П, используемая для передачи команд и данных из ЭВМ; шина 20 «СТР-П (строб) - сигнал, указываюший на наличие байта информации на шине 19; шина 21 - 1

33 - синхроимпульсы 2; шина 34 - синхроимпульсы 1; шина 35 - сигналы управления узлом 6, обеспечиваюшие передачу на ШИН-К команды «Уточнить состояние (35-1) «УТС- ШИН-К, адреса (35-4) «А- ШИН-К, данных с ЭВМ (35-3) «Д- -ШИН-к и сброс триггеров узла 6 (35-2) «ШИН-К-- -0 ; шина 36 - признак поступления из ЭВЛ команды «Записать (36-1) или «Управление (36-2);

15

ЗП-П - сигнал запроса, указывающий Ю шина 37 - сигналы записи признака выпол- что устройство для сопряжения может принять байт информации из ЭВМ; шине 21-2 «ГП-П - сигнал готовности устройства для сопряжения к работе с ЭВМ; шина 22 - информационная шина ШИН-К (0...7К), служащая для передачи адреса, команд и данных в периферийное устройство; шина 23-1 «РАБ-К (работа) - сигнал управления, используемый для разрешения подключения периферийного устройства; шина 23-2 «АДР-К. - сигнал идентификации, указывающий, что на ШИН-К находится адрес периферийного устройства; шина 23-3 - «ВБР-К (выборка) - сигнал управления; шина 23-4 - «РВБ-К (разрешение выборки) - сигнал управления; шина 23-5 «УПР-К - сигнал идентификации, означающий выдачу байта команды на ШИН-К (как ответ на сигнал «АДР- А) или «Останов (как ответ на сигнал «ИНФ-А); шина 23-6 «ИНФ-К - сигнал идентификации, указывающий, что принят байт состояния периферийного устройства (как ответ на сигнал «УПР-А) или указывающий, что информация, передаваемая в периферийное устройство, находится на ШИН-К (как ответ на сигнал «ИНФ-

нения команд «Записать и «Управление «(ЗПС V УПР) 37-1), признака выполнения команды «Уточнить состояние «УТС 1 (37-2), сброс признака команды «Уточнить состояние (37-3); щина 38 - признак выполняемой команды: 38-1 - «Записать (ЗПС), 38-2 - «Управление (УПр), 38-3 - «Уточнить состояние (УТС); шина 39 - сигнал сброса счетчика и сумматора знаков «СчЗН, СмЗН

20 щина 40-1 - сигнал управления счетчиком знаков «+СчЗн ; шина 40-2 - сигнал управления сумматором «+СмЗн ; шина 41-2 - сигнал СчЗн шина 41 - 1 - сигнал «СмЗн правильная ; на 42 - запись управляющих сигналов для ЭВМ в регистр 18; щина 42-1 - «ЗП-П - - 1 - запись «1 в 1-й разряд; щина 42-2 - «ГП-П - О - запись «О во 2-й разряд; щина 42-3 - «ГП-П - 1 - запись «1 во 2-й разряд; щина 42-4 - ЗП-П- 0 - запись «О в 1-й разряд;

30

щина 43 - запись управляющих сигналов для периферийного устройства в регистр 17; щина 43-1 - «УПР-К - 1 - запись «1 в 1 -и разряд; щина 43-2 - «УПР-К запись «О в 1-й разряд; щина 43-3 -

А); шина 24 - информационная шина «ИНФК - Ь - запись «1 во 2-й разряд;

ШИН-А (0...7К), используемая для передачи адреса и информации о состоянии из периферийного устройства; щина 25-1 «РАБ-А - сигнал указывающий, что периферийное устройство с требуемым адресом подключилось; шина 25-2 «АДР-А - сигнал идентификации, указывающий, что на ШИН-А находится адрес периферийного устройства; шина 25-3 «УПР-А сигнал идентификации, указывающий, что на ШИН-А находится байт состояния периферийного устройства; шина 25-4 «ИНФ- А - сигнал идентификации, указывающий, что периферийному устройству требуется получить или передать байт информации; щина 26 - сигнал «Пуск ; щина 27 - сигнал «Установка ; щина 28 - информационная щина команды «Уточнить состояние, (0...7К); шина 29 - шина адреса периферийного устройства (0...7К); шила 30 - щина информации, полученной из ЭВМ, после преобразования; щина 31 - значение контрольного разряда информации щины 30; щина 32 - сигналы управления мультиплексором, 32-1 - первый управляющий вход, 32-2 - второй управляющий вход; шина

40

45

щина 43-4 - «ИНФ-К - О - запись «О во 2-й разряд; шина 43-5 - «РВБ-К, ВБР-К - О - запись «О в 3-й разряд; шина 43-6 - «РВБ-К, ВБР-К - 1 - запись «1 в 3-й разряд; шина 43-7 - «АДР-К Ь - запись «1 в 4-й разряд; шина 43-8 «АДР-К - О - запись «О в 4-й разряд; шина 43-9 «РАБ-К - 1 - запись «1 в 5-й разряд; шина 43-10 - «РАБ-К - О - запись «О в 5-й разряд; шина 44 - байт состояния Мтериферийно- го устройства РгБС (0...7); шина 45 - байт уточненного состояния периферийного устройства «РгБУС (0....7); шина 46-1 - как выполнения команды «РгБС 5 Л 7 шина 46-2 - сбой периферийного устрой- 50 ства, «Сбой шина 46-3 - «БС 00000000; шина 46-4 - «БС 00001000 ; шина 47 - признак правильного адреса «АДР прав.; шина 48 - признак правильной четности «Чет. шина 49 - сигнал записи байта состояния в регистр 12 «Запись щина - 50 сигнал записи байта уточненного состояния в регистр 13 «Запись РгБУС ; шина 51 - сигнал «Стоп.

55

33 - синхроимпульсы 2; шина 34 - синхроимпульсы 1; шина 35 - сигналы управления узлом 6, обеспечиваюшие передачу на ШИН-К команды «Уточнить состояние (35-1) «УТС- ШИН-К, адреса (35-4) «А- ШИН-К, данных с ЭВМ (35-3) «Д- -ШИН-к и сброс триггеров узла 6 (35-2) «ШИН-К-- -0 ; шина 36 - признак поступления из ЭВЛ команды «Записать (36-1) или «Управление (36-2);

шина 37 - сигналы записи признака выпол-

шина 37 - сигналы записи признака выпол-

нения команд «Записать и «Управление «(ЗПС V УПР) 37-1), признака выполнения команды «Уточнить состояние «УТС 1 (37-2), сброс признака команды «Уточнить состояние (37-3); щина 38 - признак выполняемой команды: 38-1 - «Записать (ЗПС), 38-2 - «Управление (УПр), 38-3 - «Уточнить состояние (УТС); шина 39 - сигнал сброса счетчика и сумматора знаков «СчЗН, СмЗН

щина 40-1 - сигнал управления счетчиком знаков «+СчЗн ; шина 40-2 - сигнал управления сумматором «+СмЗн ; шина 41-2 - сигнал СчЗн шина 41 - 1 - сигнал «СмЗн правильная ; шина 42 - запись управляющих сигналов для ЭВМ в регистр 18; щина 42-1 - «ЗП-П - - 1 - запись «1 в 1-й разряд; щина 42-2 - «ГП-П - О - запись «О во 2-й разряд; щина 42-3 - «ГП-П - 1 - запись «1 во 2-й разряд; щина 42-4 - ЗП-П- 0 - запись «О в 1-й разряд;

щина 43 - запись управляющих сигналов для периферийного устройства в регистр 17; щина 43-1 - «УПР-К - 1 - запись «1 в 1 -и разряд; щина 43-2 - «УПР-К запись «О в 1-й разряд; щина 43-3 -

«ИНФК - Ь - запись «1 во 2-й разряд;

«ИНФК - Ь - запись «1 во 2-й разряд;

0

5

щина 43-4 - «ИНФ-К - О - запись «О во 2-й разряд; шина 43-5 - «РВБ-К, ВБР-К - О - запись «О в 3-й разряд; шина 43-6 - «РВБ-К, ВБР-К - 1 - запись «1 в 3-й разряд; шина 43-7 - «АДР-К Ь - запись «1 в 4-й разряд; шина 43-8 «АДР-К - О - запись «О в 4-й разряд; шина 43-9 «РАБ-К - 1 - запись «1 в 5-й разряд; шина 43-10 - «РАБ-К - О - запись «О в 5-й разряд; шина 44 - байт состояния Мтериферийно- го устройства РгБС (0...7); шина 45 - байт уточненного состояния периферийного устройства «РгБУС (0....7); шина 46-1 - как выполнения команды «РгБС 5 Л 7 шина 46-2 - сбой периферийного устрой- 0 ства, «Сбой шина 46-3 - «БС 00000000; шина 46-4 - «БС 00001000 ; шина 47 - признак правильного адреса «АДР прав.; шина 48 - признак правильной четности «Чет. шина 49 - сигнал записи байта состояния в регистр 12 «Запись щина - 50 сигнал записи байта уточненного состояния в регистр 13 «Запись РгБУС ; шина 51 - сигнал «Стоп.

5

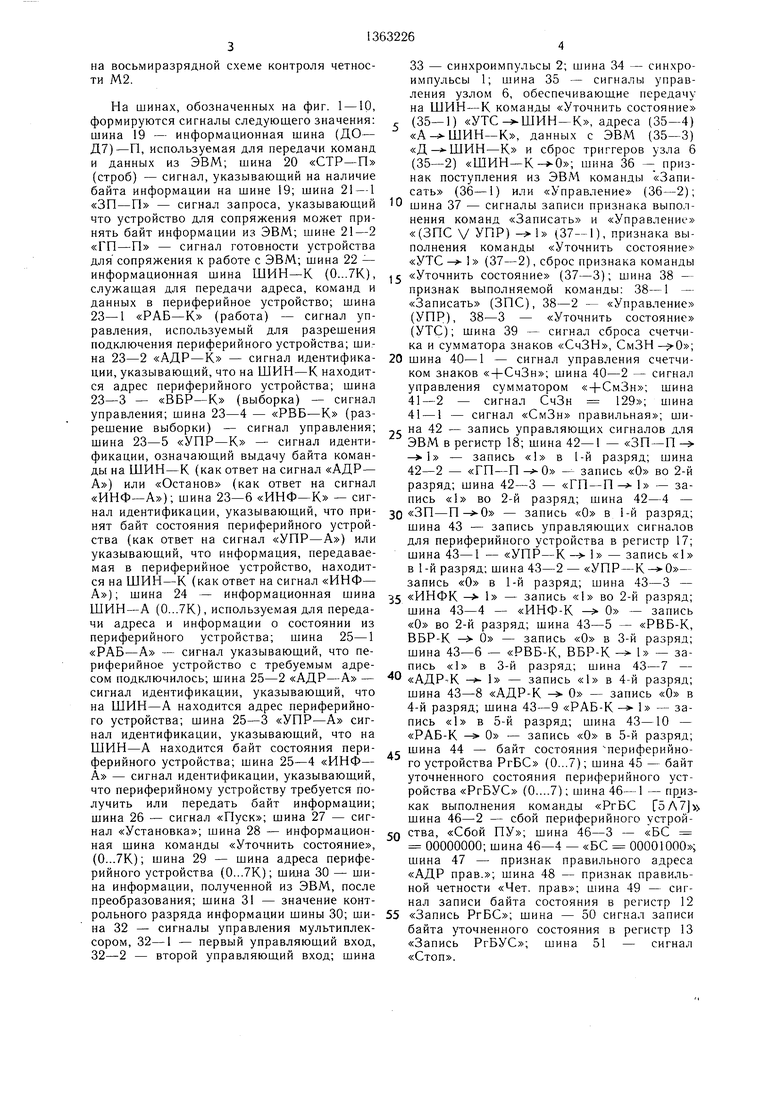

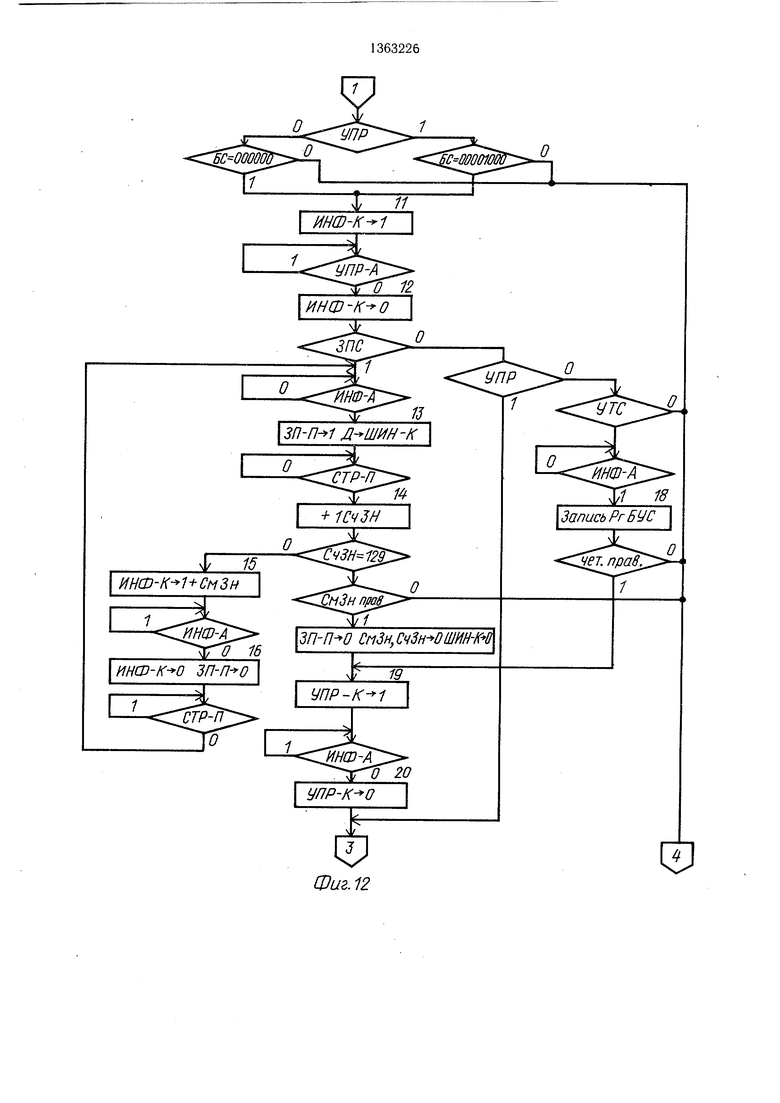

Блок 11 микропрограммного управления (фиг. 2) предназначен для управления работой узлов и регистров предлагаемого устройства. Он функционирует в соответствии с алгоритмом, приведенным на фиг. 11 -13. Входы логических условий блока 11 представлены на схеме алгор итма в виде ромбиков, а микрокоманды в виде прямоугольников. Каждой микрокоманде ставится в соответствие

хождение синхроимпульсов с генератора 64 через элемент И 68 на схему делителя частоты, выполненную на триггере 66 и элементах И 69 и 70. Синхроимпульсы 1 по шине 34 поступают на регистр 52 блока 11, а синхроимпульсы 2, сдвинутые относительно синхроимпульсов 1, служат для стробирования выходных сигналов блока 11. Формирование синхроимпульсов продолжается до поступления по шине 51 сигнала

определенное состояние регистра 52 микро- 10 «Стоп через элемент И 67, служаш.ий

команд. Для реализации 27 состояний требуется 5 разрядов регистра. Эти состояния дешифратора совпадают с нумерацией состояний регистра микрокоманд. Кодирование состояний может быть различным. Шифдля стробирования, на триггер 65.

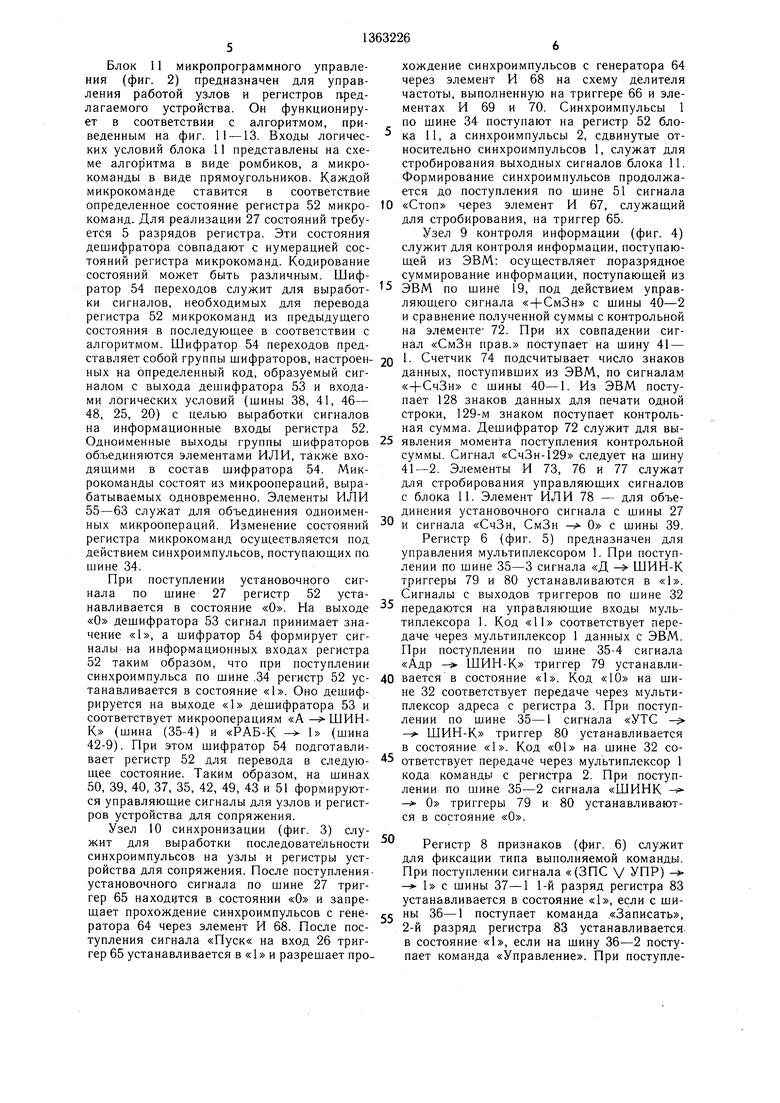

Узел 9 контроля информации (фиг. 4) служит для контроля информации, поступающей из ЭВМ: осуществляет поразрядное суммирование информации, поступающей из

ратор 54 переходов служит для выработ- ЭВМ по шине 19, под действием управ- ки сигналов, необходимых для перевода ляющего сигнала «+СмЗн с шины 40-2 регистра 52 микрокоманд из предыдущего и сравнение полученной суммы с контрольной состояния в последующее в соответствии с на элементе- 72. При их совпадении сиг- алгоритмом. Шифратор 54 переходов пред- нал «СмЗн прав. поступает на щину 41 - ставляет собой группы шифраторов, настроен- 20 Счетчик 74 подсчитывает число знаков ных на определенный код, образуемый сиг- данных, поступивших из ЭВМ, по сигналам налом с выхода дешифратора 53 и входа- «+СчЗн с шины 40-1. Из ЭВМ посту- ми логических условий (шины 38, 41, 46- пает 128 знаков данных для печати одной 48, 25, 20) с целью выработки сигналов строки, 129-м знаком поступает контрольна информационные входы регистра 52. ная сумма. Дешифратор 72 служит для вы- Одноименные выходы группы шифраторов 25 явления момента поступления контрольной объединяются элементами ИЛИ, также вхо- суммы. Сигнал «СчЗн-129 следует на шину дящими в состав шифратора 54. Мик- 41-2. Элементы И 73, 76 и 77 служат рокоманды состоят из микроопераций, выра- для стробирования управляющих сигналов батываемых одновременно. Элементы ИЛИ с блока 11. Элемент ИЛИ 78 - для объе- 55-63 служат для объединения одноимен- динения установочного сигнала с шины 27 ных микроопераций. Изменение состояний и сигнала «СчЗн, СмЗн - О с шины 39. регистра микрокоманд осуществляется подРегистр 6 (фиг. 5) предназначен для

управления мультиплексором 1. При поступлении по шине 35-3 сигнала «Д - ШИН-К триггеры 79 и 80 устанавливаются в «1. Сигналы с выходов триггеров по шине 32 передаются на управляющие входы мультиплексора 1. Код «11 соответствует передаче через мультиплексор 1 данных с ЭВМ. При поступлении по щине 35-4 сигнала «Адр - ШИН-К триггер 79 устанавлисинхроимпульса по щине .34 регистр 52 ус- 40 вается в состояние «1. Код «10 на щи- танавливается в состояние «1. Оно дешиф- не 32 соответствует передаче через мульти- рируется на выходе «1 дещифратора 53 и плексор адреса с регистра 3. При поступ- соответствует микрооперациям «А ШИН- лении по щине 35-1 сигнала «УТС - К (шина (35-4) и «РАБ-К - 1 (шина-а- ШИН-К триггер 80 устанавливается

42-9). При этом шифратор 54 подготавли- в состояние «1. Код «01 на шине 32 со- вает регистр 52 для перевода в следую- 45 ответствует передаче через мультиплексор 1 щее состояние. Таким образом, на щинах кода команды с регистра 2. При поступ- 50, 39, 40, 37, 35, 42, 49, 43 и 51 формируют- лении по шине 35-2 сигнала «ШИНК - ся управляющие сигналы для узлов и регист- - О триггеры 79 и 80 устанавливают- ров устройства для сопряжения.ся в состояние

Узел 10 синхронизации (фиг. 3) служит для выработки последовательности синхроимпульсов на узлы и регистры устройства для сопряжения. После поступления- установочного сигнала по шине 27 триггер 65 наход1 тся в состоянии «О и запредеиствием синхроимпульсов, поступающих по шине 34.

При поступлении установочного сигнала по щине 27 регистр 52 устанавливается в состояние «О. На выходе «О дещифратора 53 сигнал принимает значение «Ь, а щифратор 54 формирует сигналы на информационных входах регистра 52 таким образом, что при поступлении

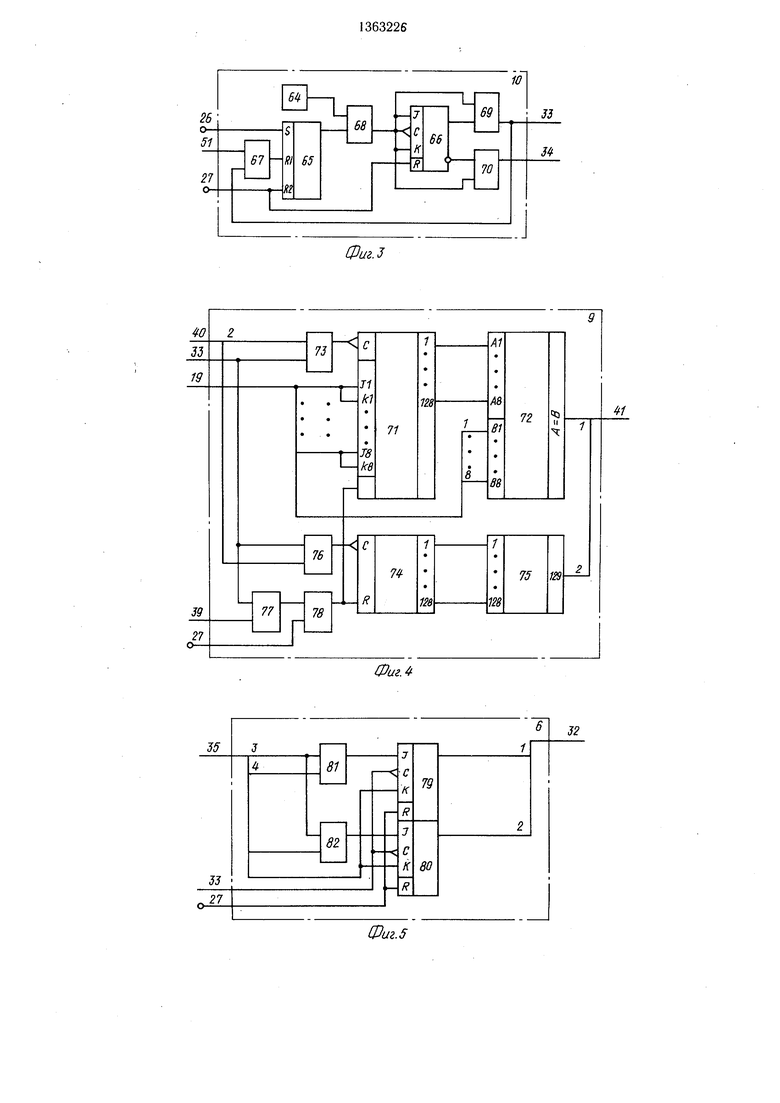

Регистр 8 признаков (фиг. 6) служит для фиксации типа выполняемой команды. При поступлении сигнала «(ЗПС V УПР) - - 1 с щины 37-1 1-й разряд регистра 83 устанавливается в состояние «1, если с щищает прохождение синхроимпульсов с гене- « ны 36-1 поступает команда «Записать, ратора 64 через элемент И 68. После пос- 2-й разряд регистра 83 устанавливается тупления сигнала «Пуск« на вход 26 триггер 65 устанавливается разрещает пров состояние «1, если на щину 36-2 поступает команда «Управление. При поступлехождение синхроимпульсов с генератора 64 через элемент И 68 на схему делителя частоты, выполненную на триггере 66 и элементах И 69 и 70. Синхроимпульсы 1 по шине 34 поступают на регистр 52 блока 11, а синхроимпульсы 2, сдвинутые относительно синхроимпульсов 1, служат для стробирования выходных сигналов блока 11. Формирование синхроимпульсов продолжается до поступления по шине 51 сигнала

«Стоп через элемент И 67, служаш.ий

«Стоп через элемент И 67, служаш.ий

для стробирования, на триггер 65.

Узел 9 контроля информации (фиг. 4) служит для контроля информации, поступающей из ЭВМ: осуществляет поразрядное суммирование информации, поступающей из

ЭВМ по шине 19, под действием управ- ляющего сигнала «+СмЗн с шины 40-2 и сравнение полученной суммы с контрольной на элементе- 72. При их совпадении сиг- нал «СмЗн прав. поступает на щину 41 - Счетчик 74 подсчитывает число знаков данных, поступивших из ЭВМ, по сигналам «+СчЗн с шины 40-1. Из ЭВМ посту- пает 128 знаков данных для печати одной строки, 129-м знаком поступает контрольная сумма. Дешифратор 72 служит для вы- явления момента поступления контрольной суммы. Сигнал «СчЗн-129 следует на шину 41-2. Элементы И 73, 76 и 77 служат для стробирования управляющих сигналов с блока 11. Элемент ИЛИ 78 - для объе- динения установочного сигнала с шины 27 и сигнала «СчЗн, СмЗн - О с шины 39. Регистр 6 (фиг. 5) предназначен для

Регистр 8 признаков (фиг. 6) служит для фиксации типа выполняемой команды. При поступлении сигнала «(ЗПС V УПР) - - 1 с щины 37-1 1-й разряд регистра 83 устанавливается в состояние «1, если с щины 36-1 поступает команда «Записать, 2-й разряд регистра 83 устанавливается

ы 36-1 поступает команда «Записать, -й разряд регистра 83 устанавливается

в состояние «1, если на щину 36-2 поступает команда «Управление. При поступлеНИИ сигнала «УТС по шине 37-2 3-й разряд регистра 83 устанавливается в состояние «1, а 1-й и 2-й разряды - в состояние «О. Запись в регистр осуществляется при поступлении синхроимпульса 2 по шине 33. Признаки выполняемых команд по шине 38 поступают на входы логических условий блока 11.

Регистр 2 команды (фиг. 7) служит для генерации кода команды «Уточнить состояФормирователь 5 формирует контрольный разряд информации, поступаюш,ей с шифратора 4. Контрольный разряд дополняет сумму разрядов информации до нечетности.

Дешифратор 15 служит для контроля адреса, поступаюшего из периферийного устройства по шине 24. Если его код совпадает с заданным, то сигнал «Адр прав. выдается по шине 47 на блок 11.

Узел 16 предназначен для контроля

ние. С выхода регистра информация посту- 10 четности информации, поступаюшей из пери- пает по шине 28 на мультиплексор 1.- Регистр 3 адреса (фиг. 8) предназначен для генерации адреса периферийного устройства. С выхода регистра 3 информация поступает по шине 29 на мультиплексор 1.

Регистр 12 (фиг. 9) используется для хранения байта состояния, поступившего с периферийного устройства по шине 24. Запись в регистр осуществляется по сигналу «Запись РгБС с шины 49, стробируемо- му на элементе 89 И синхроимпульсами 2, поступающими с шины 33.

Регистр 13 служит для хранения байта уточненного состояния, поступившего с периферийного устройства по шине 24. Структура регистра аналогична регистру 12. Запись в регистр 13 осуществляется по сигналу «Запись РгБУС с шины 50.

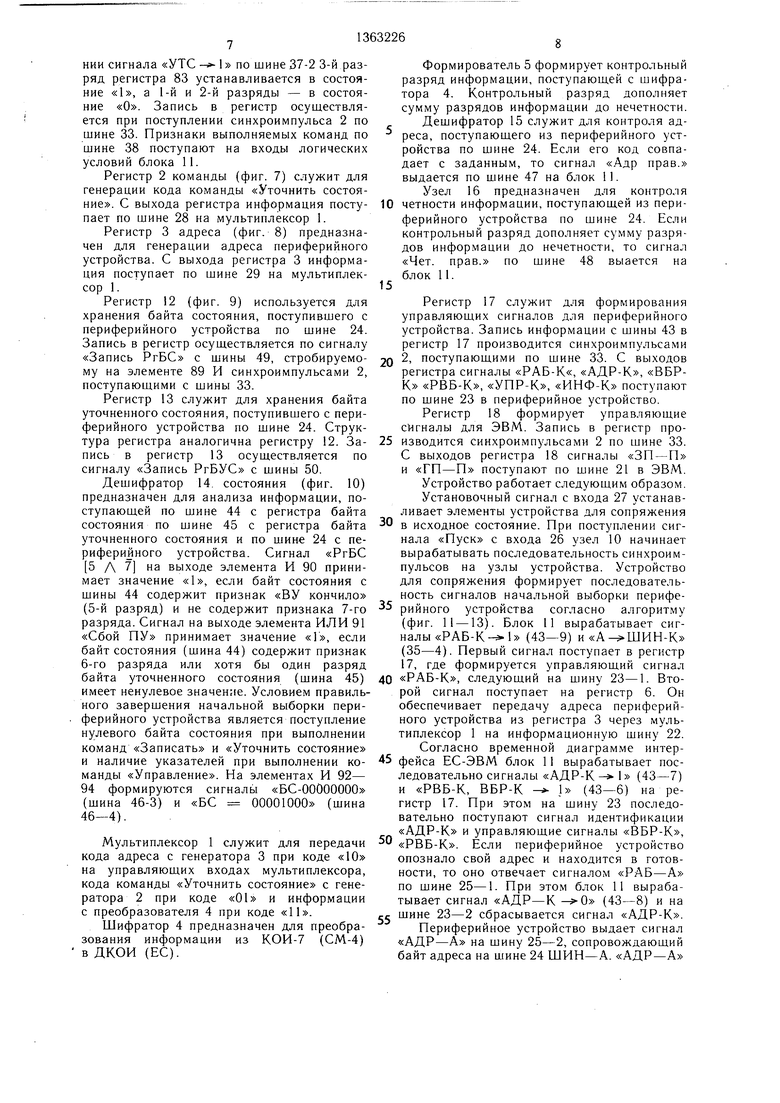

Дешифратор 14. состояния (фиг. 10) предназначен для анализа информации, поступаюшей по шине 44 с регистра байта

ферийного устройства по шине 24. Если контрольный разряд дополняет сумму разрядов информации до нечетности, то сигнал «Чет. прав. по шине 48 выается на

блок 11. 15

Регистр 17 служит для формирования управляющих сигналов для периферийного устройства. Запись информации с шины 43 в регистр 17 производится синхроимпульсами 20 2, поступающими по шине 33. С выходов регистра сигналы «РАБ-К«, «АДР-К, «ВБР- К «РВБ-К, «УПР-К, «ИНФ-К поступают по шине 23 в периферийное устройство.

Регистр 18 формирует управляющие сигналы для ЭВМ. Запись в регистр производится синхроимпульсами 2 по шине 33. С выходов регистра 18 сигналы «ЗП-П и «ГП-П поступают по шине 21 в ЭВМ.

Устройство работает следуюшим образом.

Установочный сигнал с входа 27 устанавливает элементы устройства для сопряжения

25

35

состояния по шине 45 с регистра байта в исходное состояние. При поступлении сиг- уточненного состояния и по шии€ 24 с пе-

риферийного устройства. Сигнал «РгБС 5 Л 7 на выходе элемента И 90 принимает значение «1, если байт состояния с щины 44 содержит признак «ВУ кончило (5-й разряд) и не содержит признака 7-го разряда. Сигнал на выходе элемента ИЛИ 91 «Сбой ПУ принимает значение «Г, если байт состояния (шина 44) содержит признак 6-го разряда или хотя бы один разряд байта уточненного состояния (щина 45) имеет ненулевое значение. Условием правильного заверщения начальной выборки периферийного устройства является поступление нулевого байта состояния при выполнении команд «Записать и «Уточнить состояние

нала «Пуск с входа 26 узел 10 начинает вырабатывать последовательность синхроимпульсов на узлы устройства. Устройство для сопряжения формирует последовательность сигналов начальной выборки периферийного устройства согласно алгоритму (фиг. 11 -13). Блок 11 вырабатывает сигналы «РАБ-К- 1 (43-9) и«А ШИН-К (35-4). Первый сигнал поступает в регистр 17, где формируется управляющий сигнал 40 «РАБ-К, следующий на шину 23-1. Второй сигнал поступает на регистр 6. Он обеспечивает передачу адреса периферийного устройства из регистра 3 через мультиплексор 1 на информационную шину 22. Согласно временной диаграмме интерналичие указателей при выполнении ко- 5 фейса ЕС-ЭВМ блок 11 вырабатывает поси

манды «Управление. На элементах И 92-

94 формируются сигналы «БС-ОООООООО

(шина 46-3) и «БС 00001000 (шина

46-4).

Мультицлексор 1 служит для передачи кода адреса с генератора 3 при коде «10 на управляющих входах мультиплексора, кода команды «Уточнить состояние с генератора 2 при коде «01 и информации с преобразователя 4 при коде «11.

Шифратор 4 предназначен для преобразования информации из КОИ-7 (СМ-4) в ДКОИ (ЕС).

50

55

ледовательно сигналы «АДР-К- 1 (43-7) и «РВБ-К, ВБР-К 1 (43-6) на регистр 17. При этом на шину 23 последовательно поступают сигнал идентификации «АДР-К и управляющие сигналы «ВБР-К, «РВБ-К. Если периферийное устройство опознало свой адрес и находится в готовности, то оно отвечает сигналом «РАБ-А по шине 25-1. При этом блок 11 вырабатывает сигнал «АДР-К -0 (43-8) и на шине 23-2 сбрасывается сигнал «АДР-К. Периферийное устройство выдает сигнал «АДР-А на шину 25-2, сопровождающий байт адреса на шине 24 ШИН-А. «АДР-А

Формирователь 5 формирует контрольный разряд информации, поступаюш,ей с шифратора 4. Контрольный разряд дополняет сумму разрядов информации до нечетности.

Дешифратор 15 служит для контроля адреса, поступаюшего из периферийного устройства по шине 24. Если его код совпадает с заданным, то сигнал «Адр прав. выдается по шине 47 на блок 11.

Узел 16 предназначен для контроля

четности информации, поступаюшей из пери- - четности информации, поступаюшей из пери- - ферийного устройства по шине 24. Если контрольный разряд дополняет сумму разрядов информации до нечетности, то сигнал «Чет. прав. по шине 48 выается на

блок 11.

Регистр 17 служит для формирования управляющих сигналов для периферийного устройства. Запись информации с шины 43 в регистр 17 производится синхроимпульсами 2, поступающими по шине 33. С выходов регистра сигналы «РАБ-К«, «АДР-К, «ВБР- К «РВБ-К, «УПР-К, «ИНФ-К поступают по шине 23 в периферийное устройство.

Регистр 18 формирует управляющие сигналы для ЭВМ. Запись в регистр производится синхроимпульсами 2 по шине 33. С выходов регистра 18 сигналы «ЗП-П и «ГП-П поступают по шине 21 в ЭВМ.

Устройство работает следуюшим образом.

Установочный сигнал с входа 27 устанавивает элементы устройства для сопряжения

в исходное состояние. При поступлении сиг-

35

в исходное состояние. При поступлении сиг-

нала «Пуск с входа 26 узел 10 начинает вырабатывать последовательность синхроимпульсов на узлы устройства. Устройство для сопряжения формирует последовательность сигналов начальной выборки периферийного устройства согласно алгоритму (фиг. 11 -13). Блок 11 вырабатывает сигналы «РАБ-К- 1 (43-9) и«А ШИН-К (35-4). Первый сигнал поступает в регистр 17, где формируется управляющий сигнал 40 «РАБ-К, следующий на шину 23-1. Второй сигнал поступает на регистр 6. Он обеспечивает передачу адреса периферийного устройства из регистра 3 через мультиплексор 1 на информационную шину 22. Согласно временной диаграмме интер 5 фейса ЕС-ЭВМ блок 11 вырабатывает пос 5 фейса ЕС-ЭВМ блок 11 вырабатывает пос50

55

ледовательно сигналы «АДР-К- 1 (43-7) и «РВБ-К, ВБР-К 1 (43-6) на регистр 17. При этом на шину 23 последовательно поступают сигнал идентификации «АДР-К и управляющие сигналы «ВБР-К, «РВБ-К. Если периферийное устройство опознало свой адрес и находится в готовности, то оно отвечает сигналом «РАБ-А по шине 25-1. При этом блок 11 вырабатывает сигнал «АДР-К -0 (43-8) и на шине 23-2 сбрасывается сигнал «АДР-К. Периферийное устройство выдает сигнал «АДР-А на шину 25-2, сопровождающий байт адреса на шине 24 ШИН-А. «АДР-А

поступает в блок 11, а байт адреса в дешифратор 15. ,Если адрес не совпадает с заданным, то блок 11 выдает сигнал «Стоп по шине 51 в узел 10. Происходит запрет синхроимпульсов, и работа прекраш.ает- ся. Если адрес правильный, то блок 11 вырабатывает сигналы «ЗП-П - 1 (42-1) и «ГП-П - 1 (42-3) в регистр 18, откуда сигналы «ЗП-П и «ГП-П передаются по шине 21 в ЭВМ. Сигнал «Д - ШИН-К

сывая сигнал «ИНФ-К на шине 23-5. На этом этап начальной выборки заканчивается и начинается передача данных.

Если выполняется команда «Записать и сигнал «ЗПС () приходит с регистра 8 на вход логического условия блока 11, то периферийное устройство дает запрос «ИНФ-А по шине 25-4 на передачу ему байта данных. Блок 11 вырабатывает сигнал «ЗП-П 1 (42-1).

из блока 11 по шине 35-3 поступает в ре- 10 Сигнал «ЗП-П с регистра 18 поступает

гистр 6, чтобы подготовить мультиплексор для передачи информации из ЭВМ.

Если ЭВМ готова к работе, то выдает по шине 19 код команды. Его сопровождает сигнал «СТР-П по шине 20. После

по шине 21 - 1 в ЭВМ. Одновременно сигнал с блока 11 «Д - ШИН-К (35-3) поступает на регистр 6, разрешая мультиплексору передачу данных из .ЭВМ. ЭВМ передает байт данных на шину 19 и стро20

ные передаются по шине 22 в периферийное устройство.

Блок 11 вырабатывает сигнал «+1СчЗн в узел 9 для счета числа данных, переданных в периферийное устройство. Если не все знаки строки переданы, т.е. СчЗн t 129 (41-2), то блок 11 выдает сигнал «ИНФ-К - 1 (43-3) в регистр 17, с выхода которого сигнал «ИНФ-К поступает

шифратора 4 формируется контрольный раз- бируюший сигнал «СТР-П на шину 20. ряд кода команды в формирователе 5, и ко-Через шифратор 4 и мультиплексор 1 данманда через мультиплексор 1 передается на шину 22 ШИН-К периферийного устройства Блок 11 выдает сигнал «(ЗПС V УПР) - Ь по шине 37-1 в регистр 8. При этом в регистре 8 фиксируется, какая команда поступила из ЭВМ: «Записать или «Управление. Блок 11 вырабатывает сигнал «УПР- К - 1 (43-1) в регистр 17. С выхода регистра 17 сигнал идентификации «УПР-К

поступает на шину 23-5 в периферийное 25 на шину 23-6, сопровождая байт данных устройство. Он сопровождает код передавае-в периферийное устройство. Одновременно

блок 11 выдает сигнал « + СмЗн (40-2) в узел 9 для контрольного суммирования данных. После приема байта данных периферийное устройство снимает сигнал «ИНФ- 0 А (25-4). Тогда устройство для сопряжения снижает сигналы «ИНФ-К (23-6) и «ЗП-П (21 - 1), а ЭВМ снимает сигнал «СТР-П (20).

Периферийное устройство вновь дает запрос «ИНФ-А по шине 25-4 на переда- чу ему байта данных. Устройство для сопряжения запрашивает данные у ЭВМ, передает в периферийное устройство, подсчитывает число переданных и контрольную сумму. 129-м знаком из ЭВМ поступись РгБС (49) байт состояния записы- 40 пает контрольная сумма. Если она не сов- вается в регистр 18. Блок 11 проверяет падает с полученной в узле 9, то блок 11 правильность четности байта состояния по вырабатывает сигнал «Стоп (51), а если сум- сигналу 48 с узла 16: если неправильная, ма правильная, то блок 11 выдает сигналы

«ЗПП - О (42-4), «СмЗн, СчЗн - О (39), «ШИН-К 0 (35-2) соответственвляет анализ сигналов с узла 14 (46-1, 45 но через регистр 18 на шину 21, на узел 9 и 46-2). При выполнении команды «Управле- регистр 6. Далее блок 11 и регистр 17 вырабатывают сигнал «УПР-К на шину 23-5, что означает окончание операции «УПР-К и сбрасывается после сброса «ИНФ-А (43-2).

После завершения выполнение команды периферийное устройство посылает байт состояния по шине 24, сопровождаемый идентификатором «УПР-А по шине 25-3. По сигналу «Запись РгБС (49) с блока 11 про- в периферийное устройство. Периферийное « исходит запись байта состояния в регистр устройство снимает сигнал «УПР-А 12. В узле 16 проводится контроль байта (25-4). В ответ блок 11 выдает сигнал состояния на четность: если четность пра- «ИНФ-К О (43-4) в регистр 17, сбра- вильна, то блок 11 и регистр 17 вырабамои команды.

После принятия команды периферийное устройство сбрасывает сигнал «АДР-А. При этом блок 11 вырабатывает сигналы «УПР-К -- О (43-2) и «ЗП-П - О (42-4), передаваемые через регистры 17 и 18 соответственно на шины 23-5 и 21 - 1, а также сигнал «ШИН-К О (35-2) в регистр 6 для запрета передачи информации на ШИН-К.

Периферийное устройство выставляет сигнал «УПР-А на шине 25-3 и байт состояния на информационной шине 24 ШИН-А. По сигналу с блока 11 «Зато выдается сигнал «Стоп (51) в узел 10, а если правильная, то блок 11 осущестние байт состояния должен быть с указателем «Канал кончил: (БС 00001000), а при командах «Записать и «Уточнить состояние - нулевым. Если байт состояния неправильный, то блок 11 вырабатывает сигнал «Стоп (51), а если правильный, то блок 11 выдает сигнал «ИНФ-К- -1 (43-3) в регистр 17, с выхода которого сигнал «ИНФ-К подается по шине 23-6

50

сывая сигнал «ИНФ-К на шине 23-5. На этом этап начальной выборки заканчивается и начинается передача данных.

Если выполняется команда «Записать и сигнал «ЗПС () приходит с регистра 8 на вход логического условия блока 11, то периферийное устройство дает запрос «ИНФ-А по шине 25-4 на передачу ему байта данных. Блок 11 вырабатывает сигнал «ЗП-П 1 (42-1).

Сигнал «ЗП-П с регистра 18 поступает

по шине 21 - 1 в ЭВМ. Одновременно сигнал с блока 11 «Д - ШИН-К (35-3) поступает на регистр 6, разрешая мультиплексору передачу данных из .ЭВМ. ЭВМ передает байт данных на шину 19 и стро бируюший сигнал «СТР-П на шину 20. Через шифратор 4 и мультиплексор 1 дан20

ные передаются по шине 22 в периферийное устройство.

Блок 11 вырабатывает сигнал «+1СчЗн в узел 9 для счета числа данных, переданных в периферийное устройство. Если не все знаки строки переданы, т.е. СчЗн t 129 (41-2), то блок 11 выдает сигнал «ИНФ-К - 1 (43-3) в регистр 17, с выхода которого сигнал «ИНФ-К поступает

бируюший сигнал «СТР-П на шину 20. Через шифратор 4 и мультиплексор 1 дан 25 на шину 23-6, сопровождая байт данных в периферийное устройство. Одновременно

45

«

50

тывают сигнал «ИНФ-К на шину 23-6, что дает возможность периферийному устройству сбросить «УПР-А, и снимать сигналы «ВБР-К (23-3) и РВБ-К (23- 4), что дает разрешение периферийному устройству на отключение от интерфейса.

После сброса периферийным устройством сигнала «РАБ-А на шине 25-1 устройство для сопряжения сбрасывает «ИНФ-К на шине 23-6. После этого происходит анализ полученного байта состояния. Ок должен содержать указатель «ВУ кончило (5-й разряд) и не содержать указателя «Особый случай (7-й разряд). В противном случае блок 11 вырабатывает сигнал «Стоп. Если названные указатели правильные «РгБС 5 Л 7 (46-1), то блок 11 выдает сигна л «УТС 1 (37-2) в регистр 8 для сброса триггеров команд «Записать и «Управление и установки в состояние «1 триггера команды «Уточнить состояние.

Устройство для сопряжения вырабатывает команду «Уточнить состояние всегда после основной команды («Записать или «Управление). Она дает возможность получить подобные сведения о себе или ошибке, появившейся при выполнении основной команды.

При выработке, последовательности сигналов начальной в-ыработки код команды «Уточнить состояние передается с регистра 2 через мультиплексор 1 на шину 22 в периферийное устройство. Мультиплексор 1 управляется регистром 6,. на вход которого с блока 11 приходит сигнал «УТС - ШИН-К (35-1). В регистр 12 байты состояния, полученные при выполнении команды «Уточнить состояние, не записываются, чтобы сохранить байты состояния, полученные при выполнении основной команды.

После окончания последовательности сигналов начальной выборки периферийное устройство выдает байт уточненного состояния на шину 24 и сигнал идентификации «ИНФ-А на шину 25-4. По сигналу «Запись РгБУС (50) с блока 11 байт уточненного состояния записывается в регистр 13. В узле 16 проводится его контроль на четность.

После завершения последовательности сигналов окончания команды происходит анализ байта состояния, полученного при выполнении основной команды, и байта уточненного состояния в узле 14. Если байт состояния содержит указатель «Сбой в устройстве или байт уточненного состояния содержит хотя бы один ненулевой указатель, то из узла 14 поступает сигнал «Сбой ПУ (46-4) на вход логического условия блока 11. При этом блок 11 вырабатывает сигнал «Стоп (51). Если сбоя нет, то блок 11 выдает сигнал «УТС (37-3) в регистр 8. Следуюш,ая команда запрашивается у ЭВМ.

При выполнении коман.аы «Управление передачи данных из ЭВМ нет. Завершение выполнения команды аналогично команде «Записать.

Формула изобретения

1. Устройство для сопряжения ЭВМ с периферийным устройством, содержаш,ее мультиплексор, регистр адреса, узел контроля

четности, формирователь контрольного разряда, регистр байта состояния и регистр байта уточненного состояния, причем группа информационных выходов мультиплексора образует группу выходов устройства для

подключения к группе информационных входов периферийного устройства, при этом группа выходов регистра адреса соединена с первой группой информационных входов мультиплексора, информационный вход которого соединен с выходом формирователя

0 контрольного разряда, отличающееся тем, что, с целью повышения достоверности передачи информации и расширения номенклатуры сопрягаемых устройств, в него введены шифратор, регистр команды, дешифратор, три регистра управления, регистр признаков, узел контроля информации, узел синхронизации, блок микропрограммного управления, дешифратор состояний и дешифратор адреса, причем группа входов шифратора соединена с группой информационных

Q входов узла контроля информации и является группой входов устройства для подключения к группе информационных выходов ЭВМ, первый вход логического условия блока микропрограммного управления является входом устройства для подключения

5 к стробируюшему выходу ЭВМ, группа информационных выходов первого регистра управления образует группу выходов устройства для подключения к группе управляющих входов ЭВМ, группа информационных выходов второго регистра управления образует

0 группу выходов устройства для подключения к группе управляющих входов периферийного устройства, первая группа входов логического условия блока микропрограммного управления образует группу входов

- устройства для подключения к группе управляющих выходов периферийного устройства, группа информационных входов регистра байта состояния соединена с группами информационных входов узла контроля четности, дешифратора адреса, регистра байта уточ0 ненного состояния и первой группой входов дешифратора состояний и образует группу входов устройства для подключения к группе информационных выходов периферийного устройства, вход пуска узла синхронизации является входом пуска устрой5 ства, установочный вход узла синхронизации соединен с установочными входами первого, второго, третьего регистров управления, регистра признаков, узла контроля информации, блока микропрограммного управления регистра байта состояния, регистра байта уточненного состояния и является установочным входом устройства, при этом-группа выходов регистра команды соединена с второй группой информационных входов мультиплексора, третья группа информационных входов которого соединена с группой информационных входов формирователя контрольного разряда, группой выходов шифратора и с группой входов дешифратора, группа выходов которого соединена с первой группой информационных входов регистра признаков, вторая группа информационных входов которого соединена с первой группой выходов блока микропрограммного управления, вторая группа входов логических условий которого соединена с группой выходов регистра признаков, синхровход которого соединен с синхровходами первого, вт орого, третьего регистров управления, регистра байта состояния, регистра байта уточненного состояния и первым ВЫХОДОМ узла синхронизации, второй выход которого соединен с синхровходом блока микропрограммного управления, первый выход которого соединен с входом остановки узла синхронизации, группа управляющих входов мультиплексора соединена с группой выходов третьего регистра управления, группа информационных входов которого соединена с второй группой выходов блока микропрограммного управления, третья группа входов логических условий которого соединена с группой выходов дешифратора состояний, вторая и третья группы входов которого соединены соответственно с группами выходов регистра байта состояния и регистра байта уточненного состояния, разрешающие входы которых соединены соответственно с вторым и третьим выходами блока микропрограммного управления, третья и четвертая группы выходов которого соединены соответственно с группами информационных входов второго и первого регистров управления, выходы дешифратора адреса и узла контроля четности соединены соответственно с вторым и третьим входами логического условия блока микропрограммного управления, четвертый выход которого соединен с разрешающим входом узла контроля информации, группа разрешающих входов которого соеди- не на с пятой группой выходов блока микропрограммного управления, четвертая груп- па входов логических условий которого соединена с группой информационных выходов узла контроля информации.

2. Устройство по п. 1, отличающееся тем, что узел контроля информации содержит

регистр, счетчик, дешифратор, элемент сравнения, три элемента И и элемент ИЛИ, причем первые входы первого и второго элементов И образуют группу раарешающих вхо дов узла контроля информации, первый вход

0 третьего элемента И является разрещающим входом узла контроля информации, второй вход первого элемента И соединен с вторыми входами второго и третьего элементов И и является синхровходом узла контроля информации, первый вход элемента ИЛИ

5 является установочным входом узла контроля информации, выходы элемента сравнения и дещифратора образуют группу информационных выходов узла контроля информации группа информационных входов регистра соединена с первой группой входов элемента сравнения и образует группу информационных входов узла контроля информации,- при этом в узле контроля инфбр- мации выходы первого и второго элементов И соединены соответственно с синхровходами регистра и счетчика, группы выходов которых соединены соответственно с второй группой входов элемента сравнения и группой входов дешифратора, выход третьего элемента И соединен с вторым входом элемента ИЛИ, выход которого соединен с установочными входами регистра и счетчика.

0

5

19

0 2Н 21-2

26 о

51

67

KI

65

27 окг

33

66

31Фиг.6

Фиг. 9

««

1 3 ii

т; б

7 8

П

24

L

Шиг. 10

i Начало

РАБ-К 1, А- ШИН-К

АМР-К 1 I J,

I упр-/ - о зп-п- о щин-к о

10

J/7-/7- / Д- ШИН-К

СпЗн СчЗн ОШИНЩ

УПР-К- 1

МФ-А

Т 13

3anucbPr БУС

19

I

СтотГП-П- О РАБ-К О, ВБР-К- 0

Фиг, 13

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подготовки данных | 1988 |

|

SU1617429A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| Микропрограммное устройство сопряжения | 1984 |

|

SU1179359A1 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Адаптер канал-канал | 1983 |

|

SU1144114A1 |

| Адаптер канал-канал | 1983 |

|

SU1112361A2 |

Устройство относится к вычислительной технике и может быть использовано для сопряжения электронных вычислительных машин, имеюш.их общесистемный интерфейс типа «Общая шина, с периферийным устройством, имеющим интерфейс ЕС ЭВМ. Целью изобретения является повышение достоверности передаваемой информации. Устройство содержит блок микропрограммного управления, мультиплексор, узел контроля информации, дешифратор состояний, три регистра управления, регистр адреса, регистр команды, шифратор, формирователь контрольного разряда, дешифратор, регистр признаков, регистр байта состояния, регистр байта уточненного состояния, дешифратор адреса, узел контроля четности, узел синхронизации. 1 з.п. ф-лы, 13 ил. со О5 оо 1чЭ ю 05

| Устройство для сопряжения двух вычислительных машин | 1983 |

|

SU1144113A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| 0 |

|

SU71118A1 |

Авторы

Даты

1987-12-30—Публикация

1986-06-30—Подача