группой информационных входов регистра байта состояния, вторые входы элементов И группы первого и второго полуадаптеров подключены

соответственно к соответствующим выходам групп выходов дешифраторов команд второго и первого полуадаптеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер канал-канал | 1985 |

|

SU1259276A1 |

| Адаптер канал-канал | 1979 |

|

SU851391A1 |

| Адаптер канал-канал | 1981 |

|

SU1037235A1 |

| Адаптер канал-канал | 1982 |

|

SU1067492A1 |

| Адаптер канал-канал | 1983 |

|

SU1112361A2 |

| Адаптер канал-канал | 1988 |

|

SU1509861A2 |

| Адаптер канал-канал | 1987 |

|

SU1425694A1 |

| Адаптер канал-канал | 1982 |

|

SU1049895A2 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Адаптер канал - канал | 1988 |

|

SU1608677A2 |

АДАПТЕР КАНАЛ-КАНАЛ,, содержащий два полуадаптера, каждый из которых включает регистр команд, дешифратор команд, регистр адреса, схему сравнения адресов, блок управления, узел коммутации выходных сигналов, буферный регистр и регистр байта состояния, причем первые входы регистров команд первого и второго полуадаптеров являются соответственно первьм и вторым информационными входами адаптера, в каждом полуадаптере первый вход регистра команд подключен к первым входам схемы сравнения адресов и буферного регистра, второй вход которого подключен кпервому выходу блока управления, второй вход регистра команд соединен с вторьм выходом блока управления, выход регистра команд подключен к входу дешифратора команд, первьй выход которого соединен с первьм входом блока управления, третий выход блока управления подключен к второму входу схемы сравнения адресов, третий вход которой соединен с выходом регистра адреса и информационным входом узла коммутации выходных сигналов, управляющий вход которого подключен к четвертому выходу блока управления, второй и третий входы которого соединены соответственно с соответствующим управляющим входом адаптера и выходом схемы сравнения адресов, пятый выход блока управления , подключен к соответствующему управляющему выходу адаптера, группа выходов блока управления подключена к первой группе информационных входов регистра байта состояния, вход сброса которого соединен с шестым выходом блока управления, выход регистра байта состояния (/) подключен к третьему входу узла коммутации выходных сигналов,выходы буферных регистров второго и первого полуадаптеров подключены соответственно к четвертым входам узлов коммутации выходных сигналов первого и второго полуадаптеров,вы4 4 ходы которых являются соответственно первым и вторым информационные выходами адаптера, седьмой выход и четвертый вход блока управления первого полуадаптера соединены соответственно с четвертым входом и седьмым выходом блока управления второго полуадаптера, отличающийся тйч, что„ с целью сокращения аппаратурных затрат в ; каддый полуадаптер введена группа элементов И, причем в каждом полуадаптере первые входы элементов И группы соединены с первьм разрядным выходом группы выходов блока управления, а выходы - с второй

Изобретение относится к вычисли тельной технике и может использоваться как системное устройство для связи цифровых вычислительных машин (ЦВМ) в многомашинном вычислительном комплексе. Известны системные устройства для связи ЦВМ в многомашинном вычислительном комплексе, состоящи из буферного регистра, входами и выходами подключенного к двум иден тичным блокам связи с каналом,каждый из которых обслуживает канал, подключенный к нему через интерфейс ввода-вывода J.1J Недостаток этих устройств состоит ,в низком быстродействии, I Наиболее близким к предлагаемому по технической сущности являетс адаптер канал-канал, состоящий из буферного регистра, входами и выхо дами подключенного к двум идентичным блокам связи с каналом (полуадаптером), блок сравнения команд, входами и выходом подключенньй соответственно к выходам и входам полуадаптеров,и блок задания режи ма, причем каждый полуадаптер соде жит регистр адреса, регистр команд дешифратор команд, схему сравнения адресов, блок управления, узел выходных сигналов, регистр байта сос тояния и узел входных сигналов, причем первый вход регистра команд соединен.с первыми входами буферно го регистра, cxeNfti сравнения адресов и угла выходных сигналов и через узел входных сигналов с информационным входом полуадаптера, выход регистра команд через дешифратор, а вход непосредственно подключены соответственно к первом входу и выходу блока управления,вт рые вход и выход которого соединен Соответственно с выходом и вторым входом схемы сравнения адресов, третьи вход и выход блока управления являются соответственно управляющими входом и выходом полуадап- тера, четвертые вход и выход блока управления первого полуадаптера соединены соответственно с четвертыми выходом и входом блока зшравления второго полуадаптера, группа выходов блока управления подключена к группе входов регистра байта состояния, выход которого соединен с вторым входом узла выходных сигналов, а вход - с выходом регистра команд другого полуадаптера 2 . Недостаток известного устройства СОСТОИТ- в больших аппаратурных затратах. Цель изобретения - сокращение аппаратурных затрат. Поставленная цель достигается тем, что в адаптер канал-канал,содержащий два по; уадаптера, каждьш из которых включает регистр команд, дешифратор команд, регистр адреса, схему сравнения адресов, блок управления, узел коммутации выходных сигналов, буферньй регистр и регистр байта состояния, причем первые входы регистров команд первого и второго полуадаптеров являются соответственно первым и вторым информационными входами адаптера, в каждом полуадаптере первьй вход регистра команд подключен к первым входам схемы сравнения адресов и буферного регистра, второй вход которого -подключен к первому выходу блока управления, второй вход регистра команд соединен с вторым выходом блока управления, выход регистра команд подключен к входу дешифратора команд, первый выход которого соединен с первьм входом блока управления, третий выход блока управления подключен к второму входу схемы сравнения адресов,

третий вход которой соединен с выходом регистра адреса и информационным входом узла коммутации выходных сигналов, управляющий вход которого подключен к четвертому выходу блока управления, второй и третий входы которого соединены соответственно с соответствующим управляювщм входом адаптера и выходом схемы сравнения адресов,пятый выход блока управления подключен к соответствующему управляющему выходу адаптера, группа выходов блока управления подключена к первой группе инфорйаиионных входов регистра байта состояния, вход сброса которого соединен с шестым выходом блока управления, выход регистра байта состояния подключен к третьему входу узла коммутации выходных сигналов, выходы буферных регистров второго, и первого полуадаптеров подключены соответственно к четвертым входам узлов коммутации выходных сигналов первого и второго полуадаптеров, выходы которых являются соответственно первьм и вторьм информационными выходами адаптера, седьмой выход и четвертый вход блока управления первого полуадаптера соединены соответственно с четвертым входом и седьмым выходом блока управления второго попуадаптера,в каждый полуадаптер введена группа элементов И, причем в каждом полуадаптере первые входы элементов И группы соединены с первьм разрядным выходом группы выходов блока, управления, а выходы - с второй группой информационных входов регистра байта состояния, вторые входы элементов И группы первого и второго полуадаптеров подключены соответственно к соответствующим выходам групп выходов дешифраторов команд второго и первого полуадаптеров.

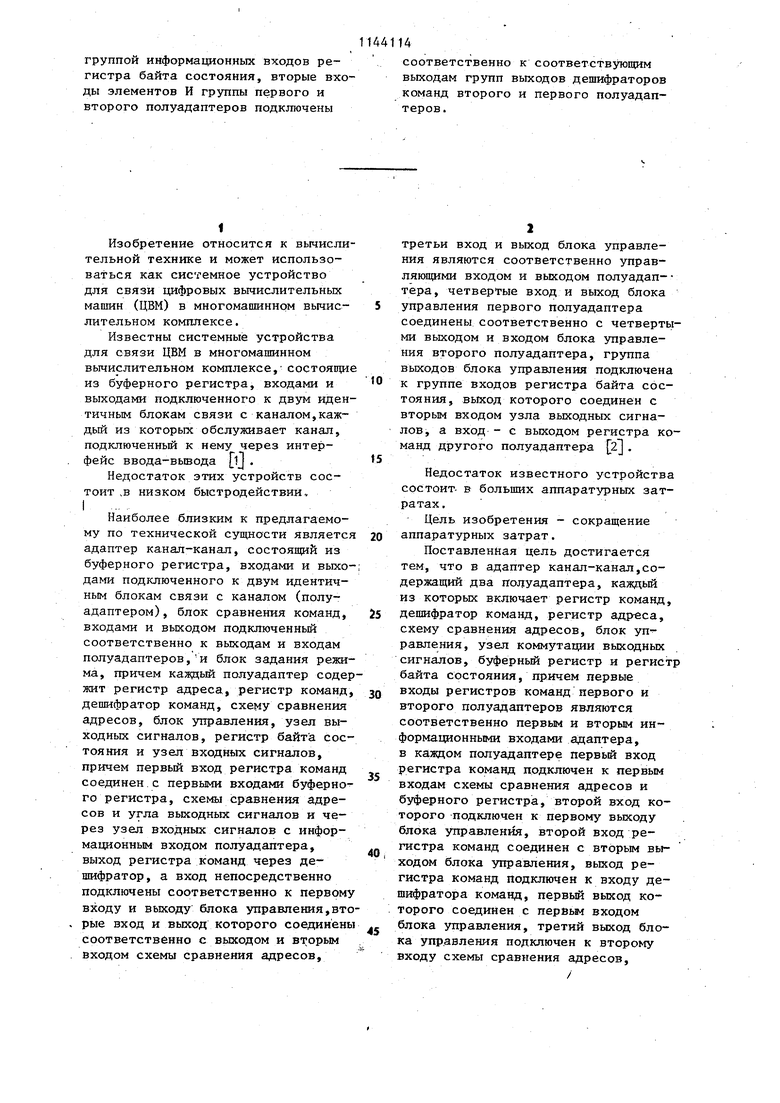

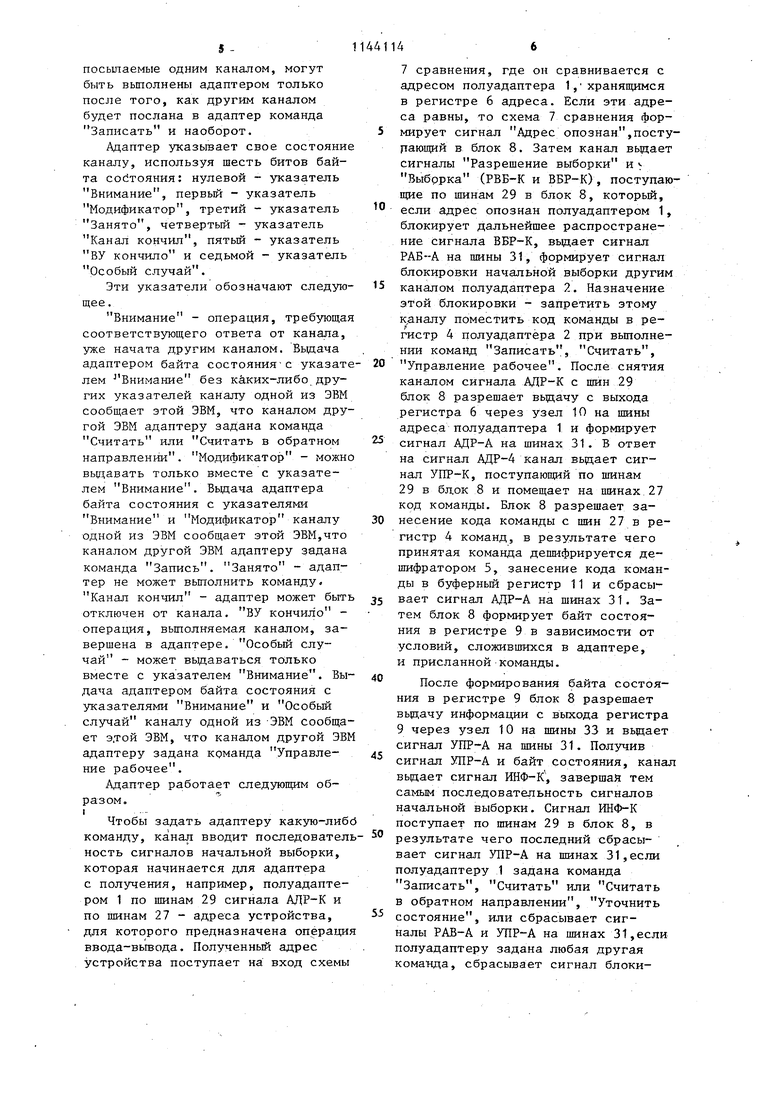

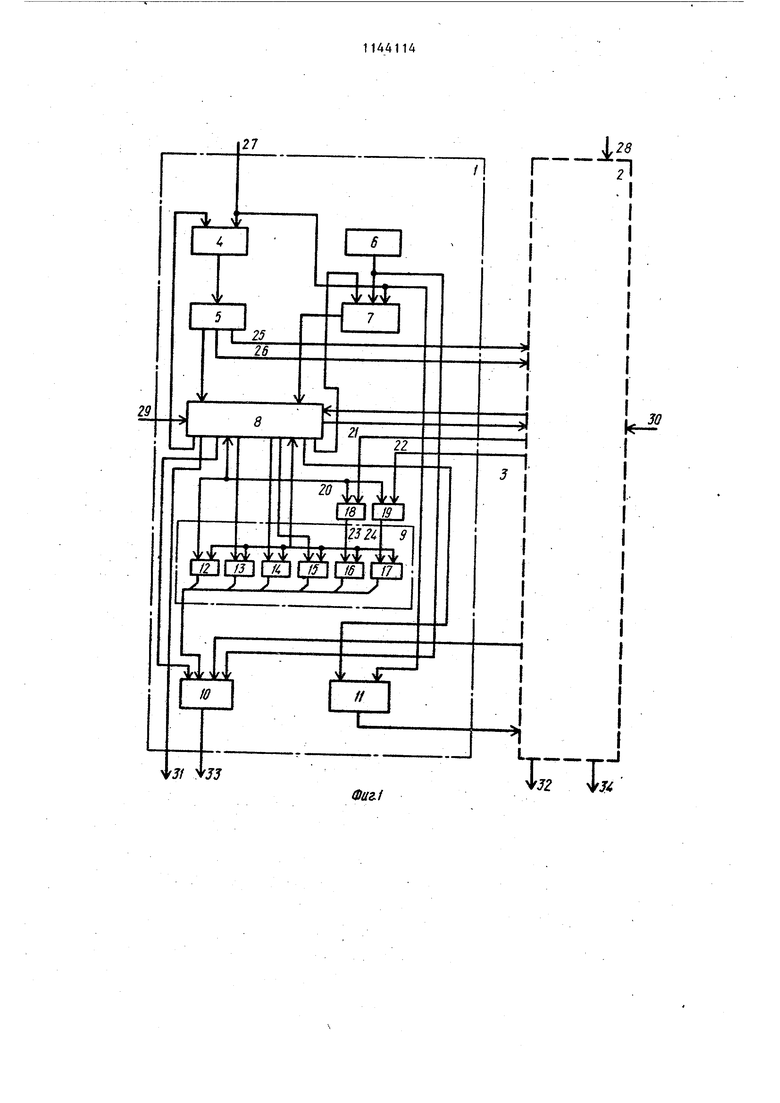

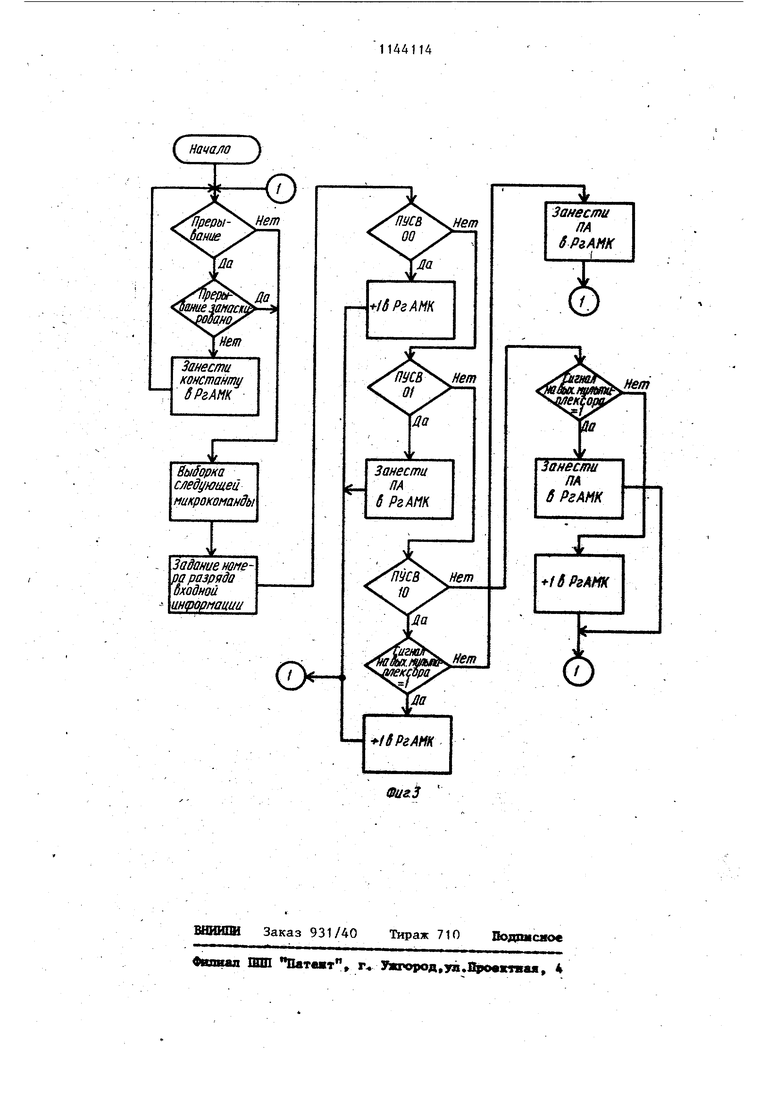

На фиг.1 приведена блок-схема предлагаемого адаптера, на фиг.2 функциональная схема блока управления; на фиг.З - блок-схема алгоритм работы блока управления.

Адаптер канал-канал (фиг.1) состоит из двух идентичных полуадаптеров 1 и 2, соединенных между собой шинами 3 и содержанщх регистр 4 команд, дешифратор 5 команд, регистр 6 адреса, схему 7 сравнения адресов, блок 8 управления, регистр

144

9 байта состояния, узел 10 коммутации выходных сигналов и буферньй регистр 11, триггеры 12-17 регистра 9, которые хранят указатели.состояния Внимание, Модификатор, Занято, Канал кончил, Внешнее устройство (ВУ) кончило, Особый случай, элементы И 18 и 19 группы, шины 20-22 входов элементов И 18 и 19, шины 23 и 24 выходов элементов И 18 и 19, шины 25 и 26 групп выходов дешифраторов 5.

Адаптер связан с сопрягаемыми каналами шинами 27 и 28 первого и второго информационных входов и шинами 29 и 30 первого и второго управляющих выходов и шинами 33 и 34 первого и второго информационных выходов.

Блок 8 управления (фиг.2) представляет собой синхронный цифровой автомат, состоящий, например, из генератора 35 синхросигналов, мультиплексора 36 входных сигналов, регистров адреса микрокоманды 37 и постоянной памяти 38, и вьфабатьгаающий функциональные сигналы, обеспечивающие работу адаптера в соответствии с заложенным алгоритмом и входными сигналами, поступающими с выхода дешифратора 5 команд, схемы 7 сравнения адресов, блока 8 управления другого полуадаптера, и управЛЯЮ11Р1МИ сигналами канала, поступающими по шинам 29.

Генератор 35 синхросигналов состоит из задающего генератора -и распределителя тактовых импульсов.

Узел 10 коммутаг ин выходных сигналов состоит из группы элементов И-ИЛИ, входы которых подключены к входам узла 10, выходы этих элементов образуют информахщонный выход узла 10.

Адаптер расшифровывает и вьполня ет следующие команды канала: Считать, Считать в обратном направлении, Записать, Управление фиктивное, Управление рабочее, Уточнить состояние, Проверить ввод-вывод.

Некоторые команды, посыпаемые каналом в адаптер, выполняются только в том случае, если другой канал, с которым связан адаптер, посыпает соответствующую команду. Например, команды Считать и Считать в обратном направлении.

посылаемые одним каналом, могут быть вьшолнены адаптером только после того, как другим каналом будет послана в адаптер команда Записать и наоборот.

Адаптер указьгоает свое состояние каналу, используя шесть битов байта состояния: нулевой - указатель Внимание, первьй - указатель Модификатор, третий - указатель Занято, четвертый - указатель Канал кончил, пятый - указатель ВУ кончило и седьмой - указатель Особый случай.

Эти указатели обозначают следующее.

Внимание - операция, требующая соответствующего ответа от канала, уже начата другим каналом. Выдача адаптером байта состояния-с указате лем Внимание без кйких-либо. других указателей каналу одной из ЭВМ сообщает этой ЭВМ, что каналом другой ЭВМ адаптеру задана команда Считать или Считать в обратном направлении. Модификатор - можно выдавать только вместе с указателем Внимание. Вьщача адаптера байта состояния с указателями Внимание и Модификатор каналу одной из ЭВМ сообщает этой ЭВМ,что каналом другой ЭВМ адаптеру задана команда Запись. Занято - адаптер не может выполнить команду. Канал кончил - адаптер может быть отключен от канала. ВУ кончило операция, вьшолняемая каналом, завершена в адаптере. Особый случай - может вьщаваться только вместе с указателем Внимание. Выдача адаптером байта состояния с указателями Внимание и Особый случай каналу одной из -ЭВМ сообщает э.той ЭВМ, что каналом другой ЭВМ адаптеру задана команда Управление рабочее.

Адаптер работает следующим образом. I

Чтобы задать адаптеру какую-либ

команду, канал вводит последовател ность сигналов начальной выборки, которая начинается для адаптера с получения, например, полуадаптером 1 по шинам 29 сигнала АДР-К и по шинам 27 - адреса устройства, для которого предназначена операци ввода-вьгоода. Полученный адрес устройства поступает на вход схемы

7 сравнения, где он сравнивается с адресом полуадаптера 1, хранящимся в регистре 6 адреса. Если эти адреса равны, то схема 7 сравнения формирует сигнал Адрес опознан,поступающий в блок 8. Затем канал вьщает сигналы Разрешение выборки и Выбррка (РВБ-К и ВБР-К), поступающие по шинам 29 в блок 8, который, если адрес опознан полуадаптером 1 блокирует дальнейшее распространение Сигнала ВБР-К, вьщает сигнал РАБ--А на щины 31, формирует сигнал блокировки начальной выборки другим каналом полуадаптера 2. Назначение этой блокировки запретить этому каналу поместить код команды в регистр 4 цолуадаптёра 2 при выполнении комайд Записать, Считать, Управление рабочее. После снятия каналом сигнала АДР-К с шин 29 блок 8 разрешает вьщачу с выхода регистра 6 через узел 10 на шины адреса полуадаптера 1 и формирует сигнал АДР-А на шинах 31. В ответ на Сигнал АДР-4 канал вьдает сигнал УПР-К, поступающими по шинам 29 в блок 8 и помещает на шинах 27 код команды. Блок 8 разрешает занесение кода команды с шин 27 в регистр 4 команд, в результате чего принятая команда дешифрируется дешифратором 5, занесение кода команды в буферный регистр 11 и сбрасывает сигнал АДР-А на шинах 31. Затем блок 8 формирует байт состояния в регистре 9 в зависимости от условий, сложившихся в адаптере, и присланной команды.

После формирования байта состояния в регистре 9 блок 8 разрешает вьщачу информации с выхода регистра 9 через узел 10 на шины 33 и вьщает сигнал УПР-А на шины 31. Получив сигнал УПР-А и байт состояния, кана вьдает сигнал ИНФ-К, завершая тем самым последовательность сигналов начальной выборки. Сигнал ШФ-К поступает по шинам 29 в блок 8, в результате чего последний сбрасывает сигнал УПР-А на шинах 31,если полуадаптеру 1 задана команда Записать, Считать или Считать в обратном направлении, Уточнить состояние, или сбрасывает сигналы РАВ-А и УПР-А на шинах 31,если полуадаптеру задана любая другая команда, сбрасывает сигнал блокировки начальной выборки полуадаптера 2, запрещает вьдачу информации через узел 10, сбрасывает регистр 9. Кроме того, если полуадаптеру 1 задана команда Записать, Счи.тать, Считать в обратном направлении, Управление рабочее, то блок 8 формирует сигнал Ожидание согласования, вьщаваемьй на шины 3 в полуадаптере 2, в результате чего полуадаптер 2 формирует запрос в свой канал на обслуживание байта состояния и вводит последовательность сигналов подключения к каналу по требованию абонента, которую выполняет следующим образом. С шин 3 полуадаптера 2 сигнал Ожидание согласования поступает в блок 8, в результате чего последний организует вьщачу сигнала ТРБ-4 на шины 32. Затем при получении сигнала ВБР-К по шинам 30 блок 8 снимает сигнал ТРБ-А на шинах 32, выставляет на этих шинах сигналы РАБ-А, АДР-А и разрешает вьщачу информадни (адреса) с выхода регистра 6 через узел 10 на шины 34.

Получив от канала сигнал УПР-К по шинам 30, блок 8 сбрасывает сигнал АДР-А па шинах 32, запрещает прохождение информации с выхода регистра 6 через узел 10 на шины 34, формирует сигнал Установка указателя внимание, устанавливающий в единичное состояние триггер 12 Внимание и поступает по шине 20 на первые входы элементов И 18 и 19.

Сигнал Записать по шине 25 с выхода дешифратора 5 полуадаптера 1 поступает на второй вход элемента И 18 полуадаптера, который формирует сигнал Установка указателя модификатор, поступающий по шине 23, на установку триггера 16 в единичное состояние.

При наличии сигнала Управление рабочее, поступающего по шине 26 с выхода дешифратора 5 полуадаптера 1 на второй вход элемента И 1 который формирует сигнал Установк указателя особый случай, поступающий по шине 24 на установку тригера 17 в единичное состояние.

После сброса каналом сигнала УПР-К на шинах 30 блок 8 разрешает вьщачу сформированного в регистре байта состояния информации через

узел 10 на шины 34 и формирует сигнал УПР-А, вьщаваемый на шины 32

При получении по шинам 30 сигнала ИНФ-К блок 8 запрещает вьщачу информации через узел 10, сбрасывае регистр 9 байта состояния и сигналы РАБ-А и 5Т1Р-4 на шинах 32. На этом полуадаптер 2 заканчивает выполнение последовательности сигналов подключения к каналу по требованию абонента.

ЭВМ, получившая от полуадаптера 2 байт состояния, должна задать ему команду Записать, если ею получен байт состояния с указателем Внимание, команду Считать или Считать в обратном направлении, если ею получен байт состояния с указателями Внимание и Модификатор, и команду Уточнить состояние при получении байта состояния с указателями Внимание и Особый случай. Задание команды происходит путем введения каналом, подключенным к полуадаптеру 2, последовательности начальной выборки, которая выполняется полуадаптером 2 аналогично выполнению последовательности начальной выборки полуадаптером 1, за исключением того, что в этом случае не формируется сигнал блокировки начальной выборки полуадаптером 1 и вместо сигнала Ожидание согласования формируется сигнал Согласующиеся команды, вьщаваемый из блока 8 полуадаптера 2 в блок 8 полуадаптера 1. После этого начинается согласованная работа блоков 8 обоих полупериодов по вьдаче . сигналов ИНФ-А на шины 31 и 32 и обмен данными.

В случае, если полуадаптеру 1 задана команда Записать, а полуадаптеру 2 - Считать или Считать в обратном направлении, данные передаются с шин 27 через буферный регистр 11 полуадаптера 1 и через узел 10 полуадат;ера 2 на шины 34.Если же полуадаптеру 1 задана команда Считать или Считать в обратном направлении, а полуадаптеру 2 - команда Записать, то данные передаются с шин 28 на шины 33 по

аналогичному тракту.

k

При выполнении полуадаптером 2 команды Уточнить состояние один байт данных (код команды Управлени рабочее заданной полуадаптеру 1)

с выхода буферного регистра 11 полуадаптера 1 передается через узел 10 полуадаптера 2, Передача данных при выполнении команды Уточнить состояние полуадаптером 1 осуществляется с выхода буферного регистра 12 полуадаптера 2 на шины 33 по аналогичному тракту.

Блок 8 управления работает по микрокомандам, вьдаваемым из регистра 38 постоянной памяти.

Микрокоманда, под управлением которой происходит работа блоков 8 каждого полуадаптера, состоит из следующих полей.

Поле номера информационного сигнала (ПНИС), под управлением которого происходит вьдача того или иного информационного сигнала на выход мультиплексора 36 входных сигналов. Сигнал с выхода этого мультиплексора используется для организации ветвлений (условных переходов) в микропрограмме.

Поле управления способом ветвления в микропрограмме (ПУСВ), под управлением которого определяется способ задания адреса следующей микрокоманды в регистре 37 адреса микрокоманды.

Поле маскирования прерьшания

(пмп).

Поле адреса (ПА) используется для задания адреса перехода и применяется для организа1даи ветвлений в микропрограмме.

Поле константы управления (ПКУ) задает функциональные сигналы, обеспечивающие работу адаптера js соответствии с заложенным алгоритмом.

Микропрограмма, выполняемая блоком 8 управления, может бьггь прервана, при этом в регистр 37 адреса микрокоманды заносится константа, представляющая собой начальный адрес микропрограммы обработки прерьтания. Каждой причине прерывания соответствует своя константа. Прерывание может возникнуть при задании каналом ЭВМ последовательности сигналов Сброс системы, Селективный сброс, Отключение от интерфейса. Прерьшание может быть замаскировано путем установки разряда поля маскирования прерывания (фиг.З).

Таким образом предлагаемое устройство при меньших аппаратурньк затратах обеспечивает минимальное время вхождения в связь и сокращает время занятости каналов ввода-вывода операциями обмена.

i.2S

Л

V

1

I.

J2 J

Ж А ДА А А

n

т

5

«ч

S

Снача/го j

Занести константу ЗРгАМК

L

ВыЗорка

следующей

микрокоманды

Занести

Нет ПА

Нет

Зинеста

ПА в РгАМК

Задание нонервразрядадходной индзорнации

f 8 РгАМК

О

1- -г / РгАНК

ФигЗ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Адаптер канал-канал | 1979 |

|

SU851391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3599805/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-03-07—Публикация

1983-08-05—Подача