Изобретение относится к вычислительной технике и может быть использовано в аппаратуре передачи данных

Цель изобретения - повышение быс родействия преобразователя.

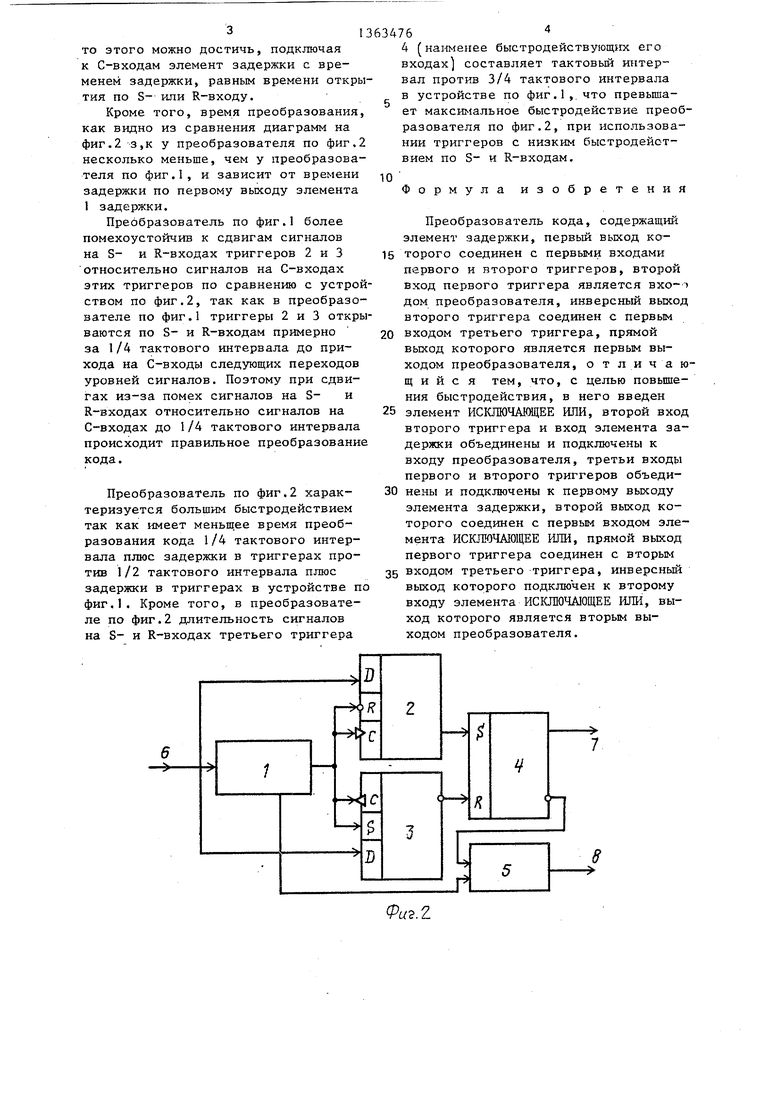

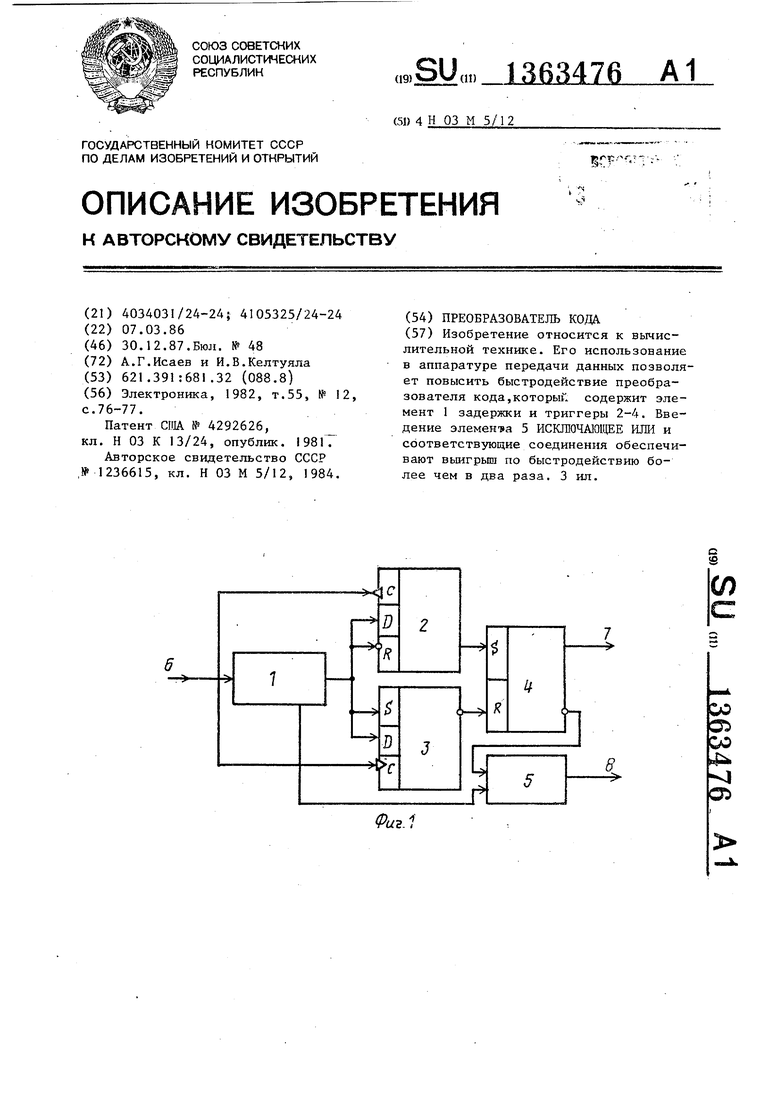

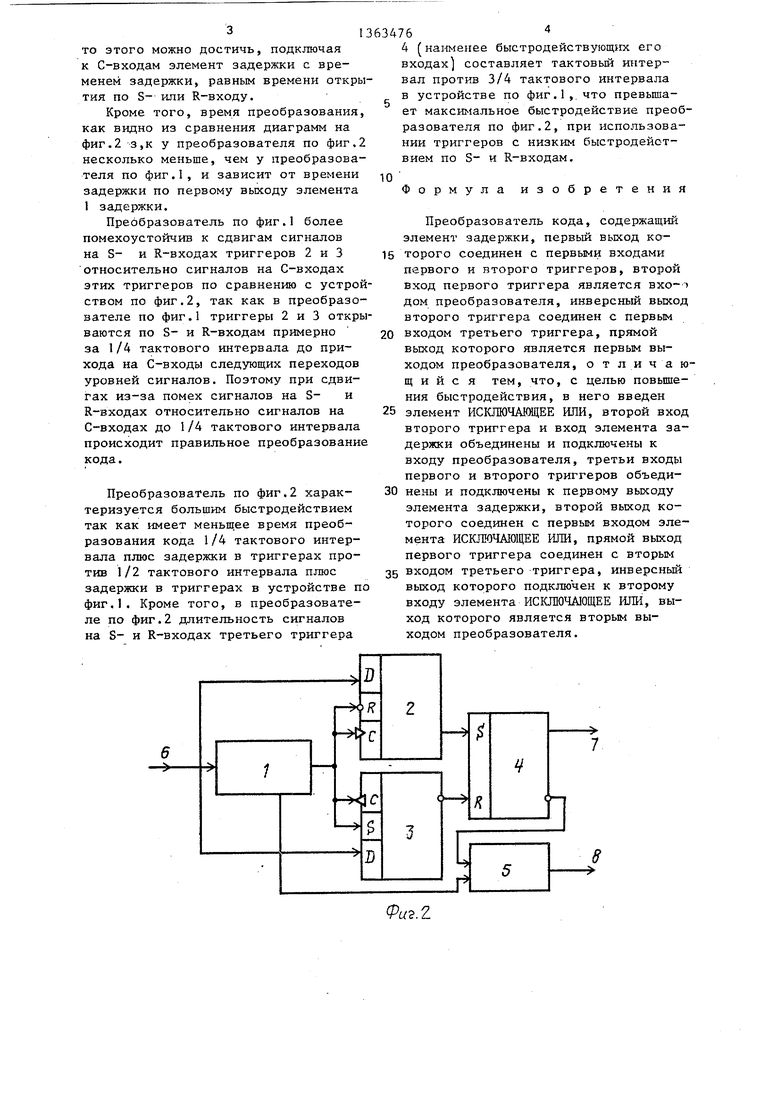

На фиг.1 и 2 представлен преобразователь кода, примеры исполнения на фиг.З - временные диаграммы его работы.

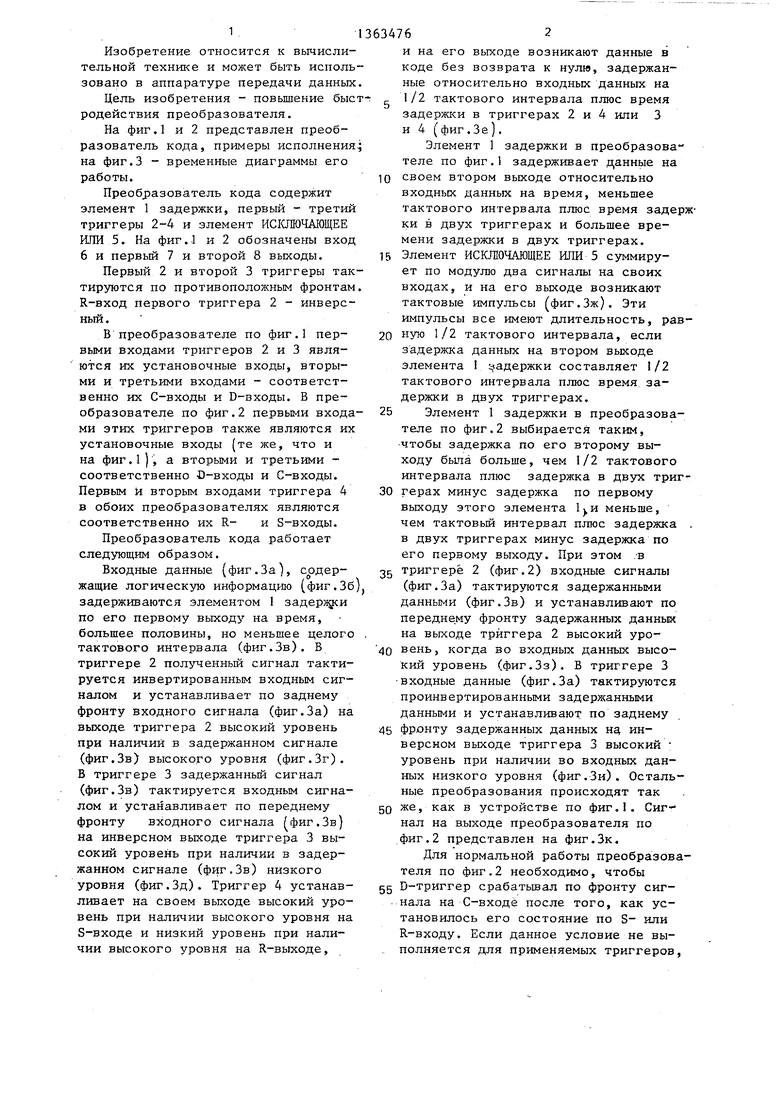

Преобразователь кода содержит элемент 1 задержки, первый - третий триггеры 2-4 и элемент ИС1ШЮЧАЮЩЕЕ ИЛИ 5. На фиг. и 2 обозначены вход 6 и первьм 7 и второй 8 выходы.

Первый 2 и второй 3 триггеры тактируются по противоположным фронтам R-вход первого триггера 2 - инверсный.

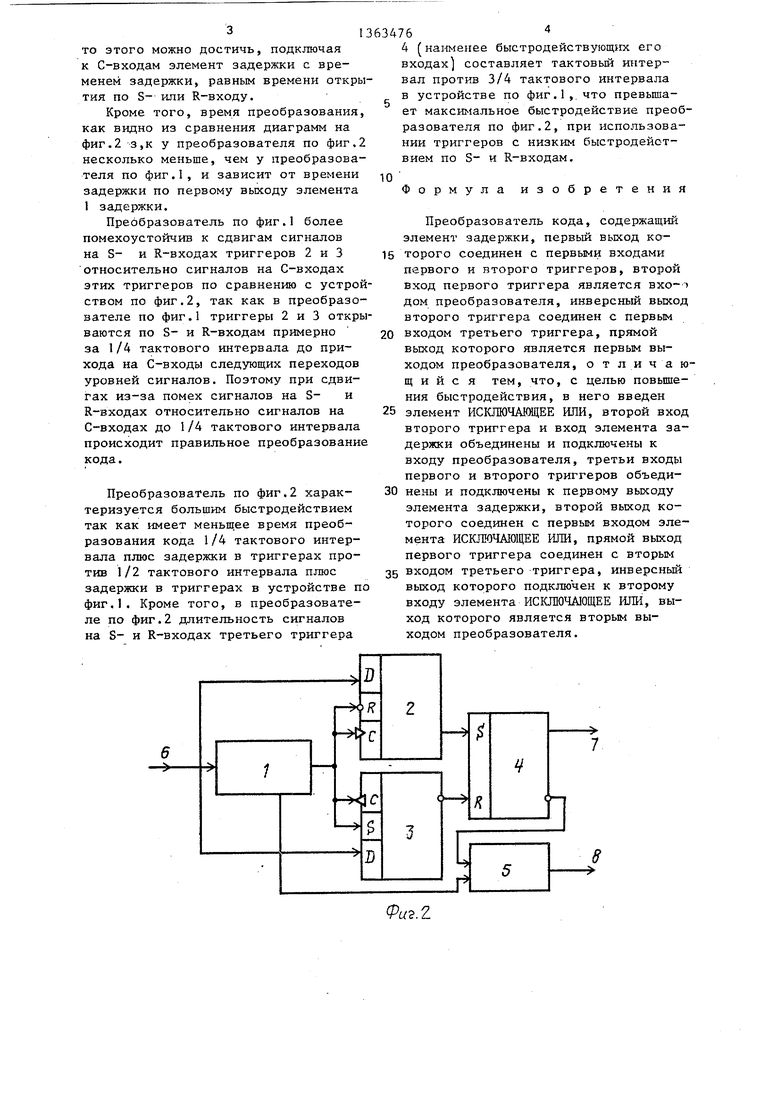

В преобразователе по фиг.1 первыми входами триггеров 2 и 3 являются их установочные входы, вторыми и третьими входами - соответственно их С-входы и D-входы. В преобразователе по фиг.2 первыми входами этих триггеров также являются их установочные входы (те же, что и на фиг.1), а вторыми и третьими - соответственно О-входы и С-входы. Первым и вторым входами триггера 4 в обоих преобразователях являются соответственно их R- и S-входы.

Преобразователь кода работает следующим образом.

Входные данные (фиг.За), с одер- жащие логическую информацию (фиг.Зб задерживаются элементом I задерндси по его первому выходу на время, большее половины, но меньшее целого тактового интервала (фиг.Зв). В триггере 2 полученньш сигнал тактируется инвертированным входным сигналом и устанавливает по заднему фронту входного сигнала (фиг.За) на выходе триггера 2 высокий уровень при наличии в задержанном сигнале (фиг.Зв) высокого уровня (фиг.Зг). В триггере 3 задержанный сигнал (фиг.Зв) тактируется входным сигналом и устанавливает по переднему фронту входного сигнала fфиг.Зв} на инверсном выходе триггера 3 высокий уровень при наличии в задержанном сигнале (фиг.Зв) низкого уровня (фиг.Зд). Триггер 4 устанавливает на своем выходе высокий уровень при наличии высокого уровня на S-входе и низкий уровень при наличии высокого уровня на R-выходе,

и на его выходе возникают данные в коде без возврата к нулю, задержанные относительно входных данных на

р. Г/2 тактового интервала плюс время задержки в триггерах 2 и 4 или 3 и 4 (фиг.Зе).

Элемент 1 задержки в преобразова теле по фиг.1 задерживает данные на

0 своем втором выходе относительно входньсх данных на время, меньшее тактового интервала плюс время задержки в двух триггерах и большее времени задержки в двух триггерах.

5 Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5 суммирует по модулю два сигналы на своих входах, и на его выходе возникают тактовые импульсы (фиг.Зж). Эти импульсы все имеют длительность, рав0 ную 1/2 тактового интервала, если задержка данных на втором выходе элемента 1 адержки составляет 1/2 тактового интервала плюс время задержки в двух триггерах.

5 Элемент 1 задержки в преобразователе по фиг.2 выбирается таким, чтобы задержка по его второму выходу была больше, чем 1/2 тактового интервала плюс задержка в двух триг0 герах минус задержка по первому выходу этого элемента меньше, чем тактовый интервал плюс задержка . в двух триггерах минус задержка по его первому выходу. При этом /в

5 триггере 2 (фиг.2) входные сигналы (фиг.За) тактируются задержанными данными (фиг.Зв) и устанавливают по переднему фронту задержанных данных на выходе триггера 2 высокий уро- 0 вень, когда во входных данных высокий уровень (фиг.Зз). В триггере 3 входные данные (фиг.За) тактируются проинвертированными задержанными данными и устанавливают по заднему

5 фронту задержанных данных н инверсном выходе триггера 3 высокий уровень при наличии во входных данных низкого уровня (фиг.Зи). Остальные преобразования происходят так

0 же, как в устройстве по фиг.1. Сигнал на выходе преобразователя по фиг.2 представлен на фиг.Зк.

Для нормальной работы преобразователя по фиг,2 необходимо, чтобы

5 D-триггер срабатьшал по фронту сиг- . нала на С-входё после того, как установилось его состояние по S- или R-входу. Если данное условие не выполняется для применяемых триггеров,

то этого можно достичь, подключая к С-входам элемент задержки с временем задержки, равным времени открытия по S- или R-входу.

Кроме того, время преобразования, как видно из сравнения диаграмм на фиг.2 3,к у преобразователя по фиг.2 несколько меньше, чем у преобразователя по фиг.1, и зависит от времени задержки по первому выходу элемента 1 задержки.

Преобразователь по фиг.1 более помехоустойчив к сдвигам сигналов на S- и R-входах триггеров 2 и 3 относительно сигналов на С-входах этих триггеров по сравнению с устройством по фиг.2, так как в преобразователе по фиг.1 триггеры 2 и 3 открываются по S- и R-входам примерно за 1/4 тактового интервала до прихода на С-входы следующих переходов уровней сигналов. Поэтому при сдвигах из-за помех сигналов на S- и R-входах относительно сигналов на С-входах до 1/4 тактового интервала происходит правильное преобразование кода.

Преобразователь по фиг.2 характеризуется большим быстродействием так как имеет меньшее время преобразования кода 1/4 тактового интервала плюс задержки в триггерах против 1/2 тактового интервала плюс задержки в триггерах в устройстве по фиг,1. Кроме того, в преобразователе по фиг.2 длительность сигналов на S- и R-входах третьего триггера

63476

4 (Hai-tMBHee быстродействующ1гх его входах составляет тактовый интервал против 3/4 тактового интервала в устройстве по фиг.1,. что превышает максимальное быстродействие преобразователя по фиг.2, при использовании триггеров с низким быстродействием по S- и R-входам.

Формула изобретения

Преобразователь кода, содержаш;ий элемент задержки, первый выход которого соединен с первыми входами первого и второго триггеров, второй вход первого триггера является вхо дом преобразователя, инверсный выход второго триггера соединен с первым

входом третьего триггера, прямой выход которого является первым выходом преобразователя, отличающийся тем, что, с целью повьше- ния быстродействия, в него введен

элемент ИСКЛЮЧАЩЕЕ ИЛИ, второй вход второго триггера и вход элемента задержки объединены и подключены к входу преобразователя, третьи входы первого и второго триггеров объединены и подключены к первому выходу элемента задержки, второй выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, прямой выход первого триггера соединен с вторым

входом третьего триггера, инверсный выход которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является вторым выходом преобразователя.

Фа.2.

а .5

фиг.З

LJ-TT

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода Миллера | 1987 |

|

SU1510092A1 |

| Преобразователь кода | 1986 |

|

SU1372624A1 |

| Преобразователь кода | 1986 |

|

SU1332536A1 |

| Преобразователь кода | 1985 |

|

SU1290533A1 |

| Преобразователь кода | 1987 |

|

SU1495998A1 |

| Преобразователь частотно-модулированного кода | 1990 |

|

SU1809538A1 |

| Преобразователь двоичного кода в трехпозиционный код | 1984 |

|

SU1317675A1 |

| Преобразователь кода | 1986 |

|

SU1325707A1 |

| Преобразователь информации | 1986 |

|

SU1322476A1 |

| Устройство для формирования сигналов суммарной и разностной частот | 1986 |

|

SU1450095A1 |

Изобретение относится к вычислительной технике. Его использование в аппаратуре передачи данных позволяет повысить быстродействие преобразователя кода,который содержит элемент 1 задержки и триггеры 2-4. Введение элемента 5 ИСКШОЧАЮиЩЕ ИЛИ и соответствующие соединения обеспечивают выигрыш по быстродействию более чем в два раза. 3 ил. US. 1

| Электроника, 1982, т.55, № 12, с.76-77 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-12-30—Публикация

1986-03-07—Подача