Изобретение относится к вычисли- тельной технике и может быть использовано в системах передачи и обработки сигналов.

редного тактового импульса (фиг.Зб) на выходах вшфратора 3 появляется код 1111 (ОООО) (.фиг, Зв) а Дешифрато 7 вырабатывает команду на перестро

Цель изобретения - повьшгение быст- j ку (,фиг,3е), которая поступает на

вход 26 блока 11 управления. По фр ту импульса (фиг.3г, поступающего на управляювдгй вход регистра Ь, ко N на выходе младших разрядов преродействня и точности преобразования.

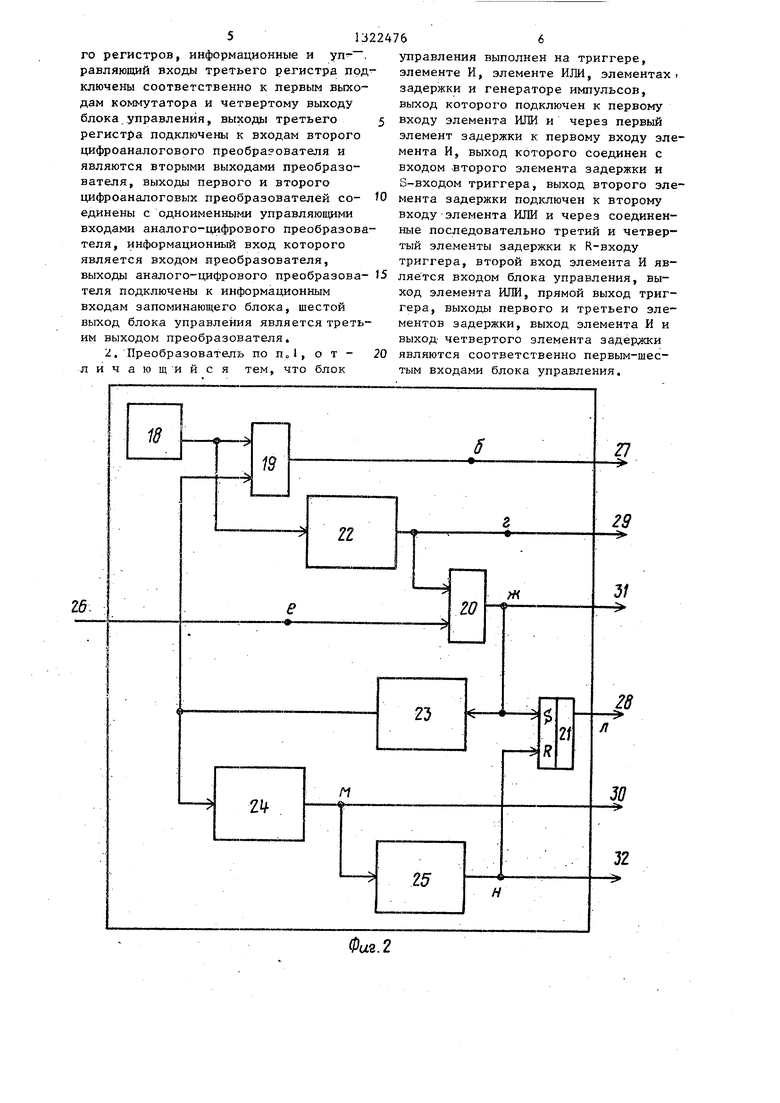

На фиг,1 приведена блок-схема преобразователя информации ; на фиг,2 блок управленияJ на фнг.З - временные диаграммы работы преобразо- 10 образователя (фиг,3д принимает значение 1111(0000;. Затем с выхода 31

вход 26 блока 11 управления. По фрон ту импульса (фиг.3г, поступающего на управляювдгй вход регистра Ь, код N на выходе младших разрядов превателя.

Преобразователь информации содержит аналого-цифровой преобразователь (,ЛЦП) 1, запоьшнающий блок 2, шифратор 3, коммутач ор Д, первый и второй цифроаналоговые преобразователи (ЦАП 5 и 6 , дешифратор 7, первый третий регистры соответственно У-10, блок II управления и сумматор 12, а также шину 13 логической единицы, вход 14, первые 15, вторые 16, третий

1 7 ВЫХОД}, ,

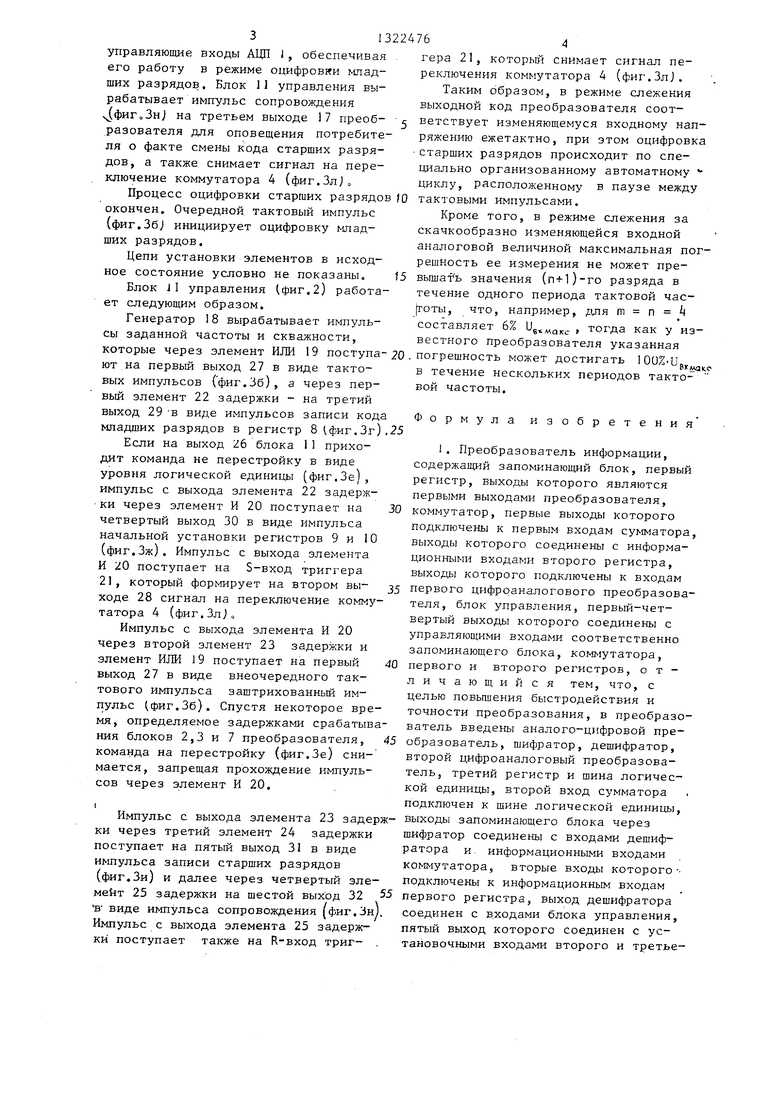

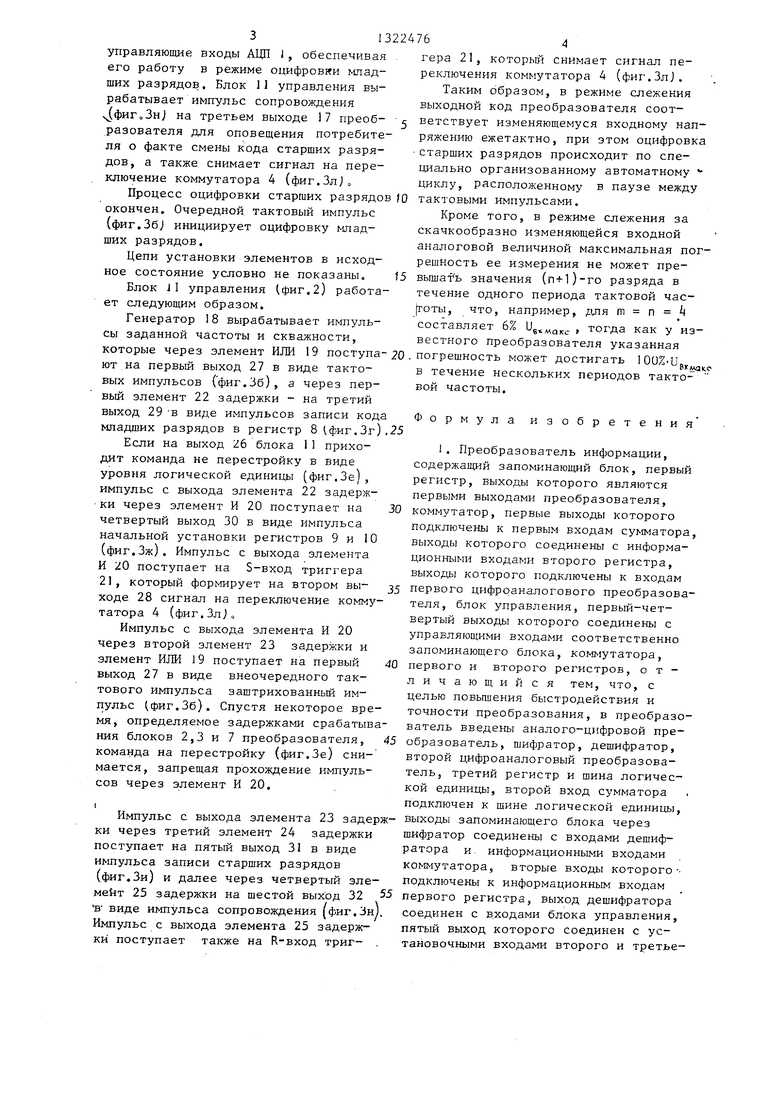

Блок 11 управления выполнен ( на генераторе 18 импульсов элементе ИЛИ 19, элементе И 20, триггере 21, первом-четвертом элементах 22-2Ь задержки. Блок 11 управления содержит вход 26 и первый-шестой выходы соответственно 27-32.

Преобразователь информации работает следующим образом.

Подаваемый на вход 14 аналоговый сигнал, например напряжение Ug,, ., ме- няю цееся в пределах О - U,, (фиг. За ; преобразуется в А1Щ i в параллель- НЬ1Й двоичный код ,, N, где М - код старших m разрядов; М - код младшихп разрядов, причем m п и равны, например ,4,

Если напряжение U изменяется

t5

блока 11 управления поступает импуль начальной установки (фиг.Зж) на уста новочные в:коды регистров 9 и 10, в результате чего на их выходах независимо от наличия сигналов на информационных входах устанавливаются коды и 0000 соответственно (), ЦДЛ Ь и 6 преобразуют указанные«коды

20

опо)ные напряжения U

П1

- Jg

и.

д„2 - t которые поступают на первый к второй управляющие входь AJJ,n 1 , 2г обеспечивая,, таким образом, его рабо ту в режиме оцифровки старших разрядов. Одновременно блок 11 управления на втором выходе 28 вырабатывает сиг нал на переключение коммутатора 4 (фиг,3л). Далее блок П управления вьфабатывает на первом выходе 27 внеочередной тактовый импульс (фиг.Зб по фронту которого в запоминающий блок 2 записывается новое значением (П11 или 0000) унитарного кода стар

35

40

ших разрядов с выходов АЦП 1,

Шифратор 3 преобразует унитарный код в двоичный (фиГ.Зв), который поступает на дешифратор 7 и коммутатор 4. Дешифратор 7 снимает команд на перестройку (фиг.Зе), а новое зна чение М кода старших разрядов через коммутатор 4 подается на информационные входы регистра 8 и сумматора 12, где к этому коду прибавляется единица, поступающая с шины 13. Код (M-f-l) подается на информационные входы регистра 9, Блок П управления выраба ты вает импульс записи старших разря- , по фронту которого в регистры 9 и 10 записываются коды (М+и и М соответственно, в результате чего на вторых выходах 16 преобразователя устанавливается код М стар ших разрядов. ЦАЛ 5 и 6 преобраз уют коды (M+J) и М в соответствующие

в таких пределах, что значение М const, АЦП работает в режиме оцифровки иладших разрядов. При этом по фронту калсдого тактового импульса (фиг.Зб в запоминающий блок 2 записвается очередное значение унитарного кода с выходов АЦП 1, Шифратор 3 преобразует унитарный код в двоичный

(фиг.Зв), который через коммутатор 4

поступает в первый регистр 8. По фро ту импульса (фиг.Зг), поступающего на первый управляющий вход этого регистра 8, измен51ется значение кода N (фиГоЗд) на первых выходах 15 преобразователя ,

Если напряжение Ug,( изменяется так, что значение М, например, увеличвается (уменьшается), по фронту оче

редного тактового импульса (фиг.Зб) на выходах вшфратора 3 появляется код 1111 (ОООО) (.фиг, Зв) а Дешифратор 7 вырабатывает команду на перестройку (,фиг,3е), которая поступает на

образователя (фиг,3д принимает знаение 1111(0000;. Затем с выхода 31

вход 26 блока 11 управления. По фронту импульса (фиг.3г, поступающего на управляювдгй вход регистра Ь, код N на выходе младших разрядов пре

блока 11 управления поступает импульс начальной установки (фиг.Зж) на установочные в:коды регистров 9 и 10, в результате чего на их выходах независимо от наличия сигналов на информационных входах устанавливаются коды и 0000 соответственно (), ЦДЛ Ь и 6 преобразуют указанные«коды

20

опо)ные напряжения U

П1

- Jg

и.

д„2 - t которые поступают на первый к второй управляющие входь AJJ,n 1 , г обеспечивая,, таким образом, его работу в режиме оцифровки старших разрядов. Одновременно блок 11 управления на втором выходе 28 вырабатывает сиг-. нал на переключение коммутатора 4 (фиг,3л). Далее блок П управления вьфабатывает на первом выходе 27 внеочередной тактовый импульс (фиг.Зб), по фронту которого в запоминающий блок 2 записывается новое значением (П11 или 0000) унитарного кода стар5

0

5

дов (.фиг.Зи)

5

ших разрядов с выходов АЦП 1,

Шифратор 3 преобразует унитарный код в двоичный (фиГ.Зв), который поступает на дешифратор 7 и коммутатор 4. Дешифратор 7 снимает команду на перестройку (фиг.Зе), а новое значение М кода старших разрядов через коммутатор 4 подается на информационные входы регистра 8 и сумматора 12, где к этому коду прибавляется единица, поступающая с шины 13. Код (M-f-l) подается на информационные входы регистра 9, Блок П управления выраба ты- вает импульс записи старших разря- , по фронту которого в регистры 9 и 10 записываются коды (М+и и М соответственно, в результате чего на вторых выходах 16 преобразователя устанавливается код М старших разрядов. ЦАЛ 5 и 6 преобраз уют коды (M+J) и М в соответствующие

опорные напряжения UQ, fe Ug и

которые подаются на первый и второй

управляющие входы АЦП 1, обеспечивая его работу в режиме оцифровки младших разрядов, БЛОК управления вырабатывает импульс сопровождения фиГoЗн на третьем выходе 17 преобразователя для оповещения потребителя о факте смены кода старших разрядов, а также снимает сигнал на переключение коммутатора 4 (фиг.

Процесс оцифровки старших разрядов (О тактовыми импульсами.

окончен. Очередной тактовый импульс {фиг,3б инициирует оцифровку младших разрядов.

Цепи установки элементов в исходное состояние условно не показаны.

Блок Jl управления (фиг.2) работает следующим образом.

Генератор 18 вырабатывает импульсы заданной частоты и скважности,

Кроме того, в режиме слежения за скачкообразно изменяющейся входной аналоговой величиной максимальная погрешность ее измерения не может пре- 15 Bbraiafb значения (п+1)-го разряда в течение одного периода тактовой час- готы, что, например, для m п 4 составляет 6% Ug , тогда как у известного преобразователя указанная которые через элемент ИЛИ 19 поступа-20. погрешность может достигать lOOZ-U

ВХмдкс

В течение нескольких периодов такто-

30

ют.на первый выход 27 в виде тактовых импульсов (фиг.Зб), а через первый элемент 22 задержки - на третий выход 29 В виде импульсов записи кода младших разрядов в регистр 8 (,фиг.3г),25

Если на выход 26 блока 11 приходит команда не перестройку в виде уровня логической единицы (фиг.Зе), импульс с выхода элемента 22 задерж- -ки через элемент И 20 поступает на четвертый выход 30 в виде импульса начальной установки регистров 9 и 10 (фиг.Зж). Импульс с выхода элемента И 20 поступает на S-вход триггера 21, который формирует на втором выходе 28 сигнал на переключение коммутатора 4 (фиг.

Импульс с выхода элемента И 20 через второй элемент 23 задержки и элемент ИЛИ 19 поступает на первый выход 27 в виде внеочередного тактового импульса заштрихованный импульс (фиг.Зб). Спустя некоторое вревои частоты.

Формула изобретения

i. Преобразователь информации, содержащий запоминаюцщй блок, первый регистр, выходы которого являются первыми выходами преобразователя, коммутатор, первые выходы которого подключень к первым входам сумматора, выходы которого соединены с информационными входами второго регистра, выходы которого подключены к входам

35 первого цифроаналогового преобразователя, блок управления, первый-чет- вертый выходы которого соединены с управляющими входами соответственно запоминающего блока, коммутатора, первого и второго регистров, отличающийся тем, что, с целью повышения быстродействия и точности преобразования, в преобразователь введены аналого-цифровой пре-

40

мя, определяемое задержками срабатывания блоков 2,3 и 7 преобразователя, команда на перестройку (фиг.Зе) снимается, запрещая прохождение импульсов через элемент И 20,

Импульс с выхода элемента 23 задерж- выходы запоминающего блока через ки через третий элемент 24 задержки шифратор соединены с входами дешиф- поступает на пятый выход 31 в виде ратора и. информационными входами импульса записи старших разрядов (фиг.Зи) и далее через четвертый элекоммутатора, вторые входы которого подключены к информационным входам

мейт 25 задержки на шестой выход 32 55 первого регистра, выход дешифратора Ъ виде импульса сопровождения (фиг.Зну. И тульс с выхода элемента 25 задержки поступает также на R-вход триг- .

соединен с входами блока управления пятый выход которого соединен с установочными входами второго и третье

гера 21, который снимает сигнал переключения коммутатора 4 (фиг.Зл).

Таким образом, в режиме слежения выходной код преобразователя соответствует изменяющемуся входному напряжению ежетактно, при этом оцифровка старших разрядов происходит по специально организованному автоматному циклу, расположенному в паузе между

Кроме того, в режиме слежения за скачкообразно изменяющейся входной аналоговой величиной максимальная погрешность ее измерения не может пре- Bbraiafb значения (п+1)-го разряда в течение одного периода тактовой час- готы, что, например, для m п 4 составляет 6% Ug , тогда как у извои частоты.

Формула изобретения

0

i. Преобразователь информации, содержащий запоминаюцщй блок, первый регистр, выходы которого являются первыми выходами преобразователя, коммутатор, первые выходы которого подключень к первым входам сумматора, выходы которого соединены с информационными входами второго регистра, выходы которого подключены к входам

5 первого цифроаналогового преобразователя, блок управления, первый-чет- вертый выходы которого соединены с управляющими входами соответственно запоминающего блока, коммутатора, первого и второго регистров, отличающийся тем, что, с целью повышения быстродействия и точности преобразования, в преобразователь введены аналого-цифровой пре-

5 образователь, шифратор, дешифратор, второй цифроаналоговый преобразователь, третий регистр и шина логической единицы, второй вход сумматора подключен к шине логической единицы.

0

выходы запоминающего блока через шифратор соединены с входами дешиф- ратора и. информационными входами

коммутатора, вторые входы которого подключены к информационным входам

первого регистра, выход дешифратора

соединен с входами блока управления, пятый выход которого соединен с установочными входами второго и третьего регистров, информационные и уп- . равляющий входы третьего регистра подключены соответственно к первым выходам коммутатора и четвертому выходу блока управления, выходы третьего регистра подключены к входам второго цифроаналогового преобразователя и являются вторыми выходами преобразователя, выходы первого и второго цифроаналоговых преобразователей со- единены с одноименными управляющими входами аналого-цифрового преобразователя, информационный вход которого является входом преобразователя, выходь: аналого-цифрового преобразова- теля подключены к информационным входам запоминающего блока, шестой выход блока управления является третьим выходом преобразователя.

Z. Преобразователь по По1, о т - личающ ийся тем, что блок

управления выполнен на триггере, элементе И, элементе ИЛИ, элементах задержки и генераторе импульсов, выход которого подключен к первому входу элемента ИЛИ и через первый элемент задержки к первому входу элемента И, выход которого соединен с входом .второго элемента задержки и S-входом триггера, выход второго элемента задержки подключен к второму входу элемента ИЛИ и через соединенные последовательно третий и четвертый элементы задержки к R-входу триггера, второй вход элемента И является входом блока управления, выход элемента ИЛИ, прямой выход триггера, выходы первого и третьего элементов задержки, выход элемента И и выход- четвертого элемента задердки являются соответственно первьм-шес- тым входами блока управления.

м

г,

-2926.

е

.

гцп

10

ж

3/

23

2f

28

л

4

25

н

Фм.2

И

X

Л

Hi

и

M-t-1

f1

М

н

Редактор И.Горная

Составитель О.Ревинский Техред А.Кравчук

Заказ 2878/55 Тираж 901Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 1J30J5, Москва, Ж-35, Раушская наб. , д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

л

л

X

////

XIZ

л

Х1/777 Х

X 0000 У.

/7

л

л

.а

Корректор С.Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для сортировки данных | 1989 |

|

SU1695290A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Цифроаналоговая система сбора и обработки информации | 1986 |

|

SU1363271A1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| Устройство для формирования сигналов датчика дистанционных синхронных передач | 1984 |

|

SU1223243A1 |

| Устройство для формирования временных интервалов | 1983 |

|

SU1246045A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Генератор многомерных случайных величин | 1982 |

|

SU1084791A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

Изобретение относится к вычислительной технике. Его использование в системах передачи и обработки сиг/ 9 налов позволяет повысить быстродействие и точность преобразования. Преобразователь информации содержит запоминающий блок 2j коммутатор 4, цнфроаналоговый преобразователь (ЦАП; 5, регистр 8, блок 11 управления и сумматор 12. Введение аналого-цифрового преобразователя 1, шифратора 3, ЦАП 6, дешифратора 7, регистров 9 и 10 и шины 13 логической единицы обеспечивает ежетактное слежение за входным сигналом с максимальной погрешностью, определяемой последним из старших- разрядов выходного кода. з.п. ф-лы, 3 ил.

| Дельта-кодер | 1981 |

|

SU953725A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 1149411, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| t | |||

Авторы

Даты

1987-07-07—Публикация

1986-02-06—Подача